BCD碼輸出靜態顯示電路圖如下圖所示。CD4511是BCD碼七段共陰譯碼/驅動IC; 4511是4線-7段鎖存/譯碼/驅動電路,能將BCD碼譯成7段顯示符輸出。圖中:4511 ABCD為0~9二進制數輸入端(A是低位),

2012-07-31 11:33:00 7579

7579

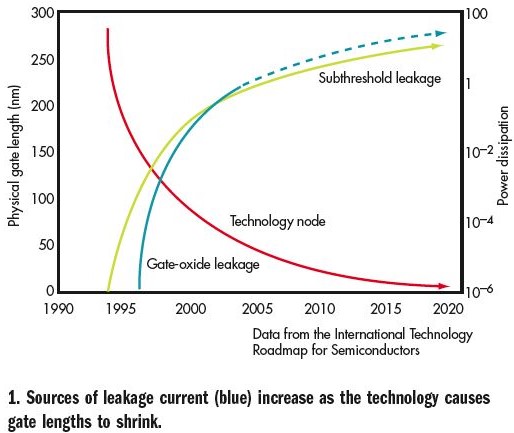

概念: Power/Ground Gating是集成電路中通過關掉那些不使用的模塊的電源或者地來降低電路漏電功耗的低功耗設計方法。該方法能降低電路在空閑狀態下的靜態功耗,還能測試Iddq。 理論

2020-09-16 16:04:15 10567

10567

以前,在做數字硬件電路設計的時候,總聽到說,CMOS數字電路靜態時,基本沒有功耗,但是當進行翻轉時,功耗就上來了。

2022-10-31 14:33:44 3934

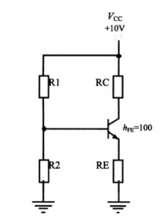

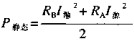

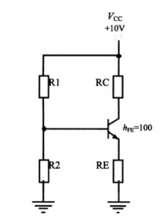

3934 未加信號時三極管的直流工作狀態被稱為靜態,也可以說成放大電路沒有輸入信號時的工作狀態,放大電路的質量與靜態值的關系很大。

2023-09-27 16:46:33 1379

1379

電路靜態工作點的定義 靜態工作點是指放大器在沒有輸入信號時的輸出電壓和電流值。在甲乙類功率放大電路中,靜態工作點通常指的是晶體管在靜態時的集電極電流和基極電壓。這個工作點對于放大器的性能和穩定性至關重要,因為

2023-12-14 17:24:19 671

671 推拉式氣墊運載平臺的行走理論研究國內外研究表明,氣墊技術與行走機構相結合可以明顯地減小車輛下陷,降低地面行駛阻力,是解決沼澤、濕地、海涂等軟濕地域運輸問題的有效途徑。本文在氣墊技術應用方面取得一定

2009-12-02 12:51:09

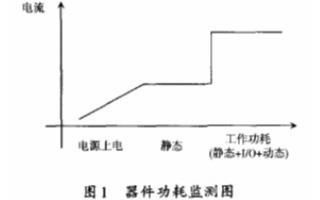

COMS電路中功耗分為兩部分:靜態功耗和動態功耗。靜態功耗是漏電流引起的功耗;動態功耗分為翻轉功耗和短路功耗,翻轉功耗也就是0與1翻轉所引發的功耗,而短路功耗則是由于PMOS和NMOS都導通時所

2021-11-11 08:06:48

FPGA已經被廣泛用于實現大規模的數字電路和系統,隨著CMOS工藝發展到深亞微米,芯片的靜態功耗已成為關鍵挑戰之一。文章首先對FPGA的結構和靜態功耗在FPGA中的分布進行了介紹。接下來提出了晶體管

2020-04-28 08:00:00

4個I/O Bank。在多電壓應用環境中比較有利,并且支持熱插拔和施密特觸發器。Actel在IGLOO系列產品的開發過程中,對靜態功耗的主要物理來源——漏電流方面做了改進。同時在生產過程中對產率、速度

2019-07-05 07:19:19

MCU的靜態功耗主要是跟什么因素有關系

2023-10-11 08:00:58

概述 ME6214系列是以CMOS?工藝制造的超低靜態功耗、低壓差線性穩壓器。穩壓器消耗電流約0.7uA,使能關斷后功耗為0.01uA(典型)。內置使能控制,限電路以及折返短路保護,并有使能控制輸出

2018-11-28 09:54:06

。可用在電源電壓為1.8V、2.5V、3.3V 和5V 的邏輯信號轉換系統中。當OE端為低電平時,所有 IO 端口為高阻態,這顯著降低了靜態功耗。當VCCA上電后,OE端內部集成了下拉電流源。為了確保在上電

2022-02-21 10:19:11

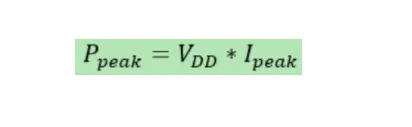

在CMOS電路中,功耗的來源主要有兩個方面(1)靜態功耗,即反向漏電流造成的功耗;(2)動態功耗,由電路作開關轉換時進入過渡區由峰值電流引起的暫態功耗,以及負載電容和芯片內寄生電容的充放電電流

2020-05-18 17:37:24

在低功耗用電的情況下,輸出同等的電壓電流,RC降壓電源、小功率變壓器、小功率開關電源這三種電源,靜態功耗(近乎靜態)最少的是哪一種?我意思是:像搖控接收器、光控器,不考慮體積、成本的情況下,用那一

2009-03-06 12:16:36

[/td][td]如果需要知道一個芯片比如op07或2252 在電路中的功耗,應該怎么計算?

pdf資料上給出的功耗Op07 125mW ,2252 800多mW

我用78L05給2252供電

2023-11-13 09:57:31

三極管放大電路中靜態工作點的重要性大家都知道三極管的主要作用是作無觸點開關和放大作用,作開關使用時很好理解,我在以前的文章中都講過了,那么它是怎么放大的呢?其實三極管是一個電流控制型器件,它根據基極

2019-08-06 09:03:29

嗨親愛的朋友請幫助我理解:什么條件我必須使用推拉配置輸出什么條件我必須使用開漏配置輸出謝謝 #推挽輸出或開漏輸出以上來自于谷歌翻譯以下為原文 Hi dear friend Please help

2019-06-25 13:34:17

以太網控制芯片W5500功耗問題,有幾十個mA,大家都是如何做節能降低靜態功耗的

2018-07-30 10:24:33

淺談電源芯片選型之低功耗硬件電路設計中電源芯片選型必不可少,電源芯片選型的好壞關系到系統的穩定性、電源的轉換效率等等,在低功耗產品設計中,更關系到系統睡眠或者低功耗模式時的系統總的耗電情況。低功耗

2021-11-11 06:49:32

前面的帖子提到過,CMOS電路中的功耗分為兩部分:靜態功耗和動態功耗;靜態功耗是由漏電流引起的功耗;動態功耗分為翻轉功耗和短路功耗,翻轉功耗也就是0與1翻轉所引發的功耗,而短路功耗則是由于PMOS

2021-11-11 06:03:31

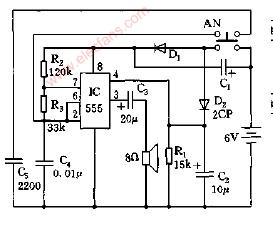

本文將具體介紹一種太陽能供電的高亮度白光LED燈閃光電路的設計方案,闡述供電電源的設計及電路靜態低功耗的實現方法,并討論設計過程中應該注意的問題。

2021-04-08 06:14:44

`分享一款超低靜態電流的同步整流升壓IC 超低功耗產品的電源如何設計,推薦一顆低功耗的同步整流升壓芯片 SY7072低靜態電流內置MOS同步整流升壓芯片在便攜式產品設計中,如何讓干電池和鋰電池供電

2018-06-22 16:56:24

單片機應用系統中的低功耗設計主要注意的問題(1)系統中單片機以外的其它電路器件盡可能選用靜態功耗低的器件,如選用CMOS電路芯片。(2)外部設備的選擇也要盡可能支持低功耗設計。(3)設計外部中斷喚醒

2013-08-22 13:35:08

www.jltcon.comFZZP推拉式防水航空插頭產品特點吉隆泰FZ系列產品采用推拉自鎖結構,具有IP67的防水功能;所生產的精密插拔自鎖連接器能有效的抗振動和沖擊,使用過程中安全可靠;應用于微電子

2017-08-02 16:57:38

減小動態和靜態功耗的方法有哪些?如何使FPGA設計中的功耗最小化?

2021-05-08 07:54:07

易失性FPGA的電源特性是什么?如何在進行板級設計時,降低系統的靜態與動態功耗?

2021-04-08 06:47:53

如何采用創新降耗技術應對FPGA靜態和動態功耗的挑戰?

2021-04-30 07:00:17

而形成,其表達式為: 式中:Vdd為電源電壓;C為被充放電的電容:α為活動因子;f為開關頻率。 (2)靜態功耗和動態功耗。當電路的狀態沒有進行翻轉(保持高電平或低電平)時,電路的功耗屬于靜態功耗

2014-01-21 11:22:57

推挽電路是兩個參數相同的三極管或MOSFET,以推挽方式存在于電路中,各負責正負半周的波形放大任務,電路工作時,兩只對稱的功率開關管每次只有一個導通,所以導通損耗小、效率高。輸出既可以向負載灌電流,也可以從負載抽取電流。推拉式輸出級既提高電路的負載能力,又提高開關速度。

2019-05-31 07:20:28

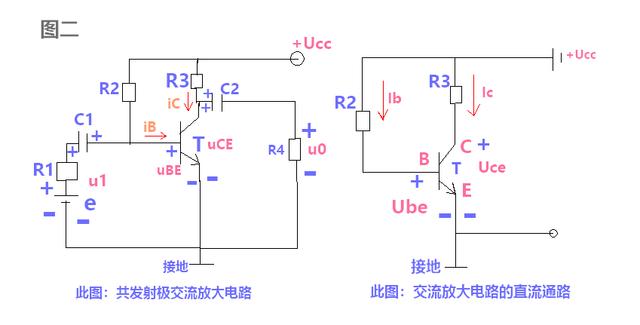

先大概對問題進行一下描述,共發射極基本交流放大電路如下圖。然后可以得到上面這幅圖的直流和交流通路如下面兩幅圖。下面是問題:靜態分析就是先根據左圖確定靜態工作點,然后用右圖在確定靜態工作點的前提

2017-01-13 15:27:50

分別為±1.5V、±2.5V、±5V時,靜態電流都隨溫度上升而變大。圖2.180ADA4807靜態電流與溫度靜態功耗(QuiescentPower,Pq)是指放大器輸出不驅動負載時,內部電路所消耗的功耗

2021-03-11 09:29:39

數顯推拉力計是一種用于推力及拉力測試的力學測量儀器。 數顯

2010-08-28 17:02:36

電源芯片的靜態電流是低功耗產品必須考慮的因素嗎

2021-10-13 08:13:15

篇文章說的靜態電流,通俗一點講,就是電源芯片直接輸出到地的電流,而不是供給負載的電流,也就是它自身消耗的電流。 因為電源芯片在電路中,只起到穩壓的作用,不參與電路板功能的實現,所以我們理想中,就希望

2018-11-30 17:18:07

你好!能推薦幾款極低靜態功耗的輸出4.5V2A(峰值)輸出DC/DC電路,由3.7V的電池通過此電路升壓到4.4V為GPRS/GSM通信模塊供電。峰值拔號時,電流峰值會達2A,成本要求低。不知道,LM4000 的靜態功耗是多大? 謝謝。

2019-03-11 10:57:50

的方法來控制靜態功耗以及UPF的實現方法,然后描述UPF在設計流程中的應用。 數字IC設計面臨的挑戰 制造工藝技術節點的發展比預期增加了更多的功耗。每一個新工藝都具有固有的更高的動態和漏電電流密度

2020-07-07 11:40:06

進行改善?比如硬件怎么改?或者說嵌入式軟件怎么改?2.鋰電池容量50mAH,產品靜態電流200uA(如何降低靜態功耗呢),如果幾天沒充電,電池很可能會過放。因為體積需要很小,保護電路沒有做在電池上。關于鋰電池0V充電功能是保護板的功能還是說鋰電池本身可以做到0V充電的功能?

2021-04-26 22:28:24

嗨,我在Xilinx中設計了一個加法器電路,并想知道它的功耗。我檢查了嵌入Xilinx ISE套件的XPA。我按照手冊pdf中給出的步驟進行操作。運行XPA之后,我收到了電源報告,但它只顯示了靜態功耗。我附上報告供您參考。請指導我如何計算動態功耗。提前致謝。xpa.docx 127 KB

2020-05-25 16:21:31

我想問一下關于運放的功耗估算問題,怎樣計算運放的功率,我在網上找過一些,有一個帖子是這個說的——“靜態電源電流就是運放中各級放大器的直流工作電流,有一定誤差但 data sheet 給出的是統計

2023-11-24 08:21:05

超低靜態功耗?最大300mA的輸出電流和高PSR。非常適合應用在多節電池產品中,如助力車,無人機,按摩儀,智能家居中的網關,插排,物聯網 等產品中。

2021-05-06 14:03:09

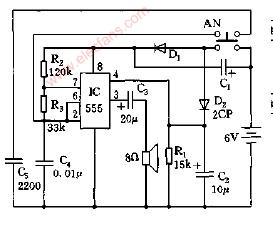

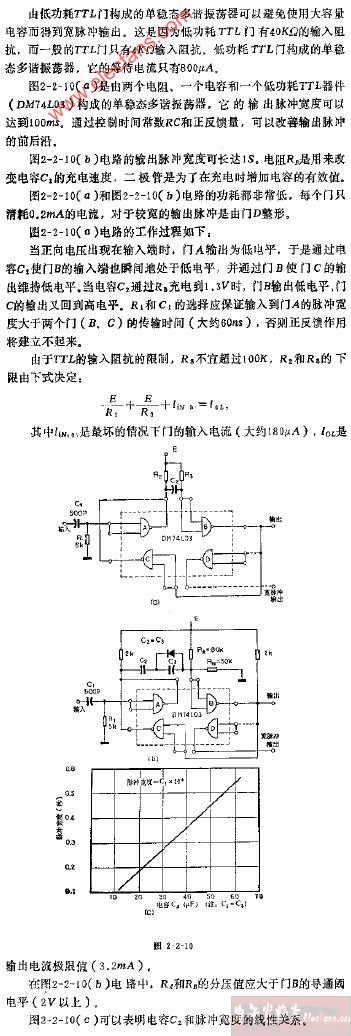

低功耗單穩電路:

如圖所示,電路包括一支四2輸入端與非門CD4011和一支CMOS型555,因而不管是靜態或輸出高電平定時期間,消耗功率極小。CD4011的門3、門4組成RS觸發器。由于

2007-06-15 10:05:45 63

63

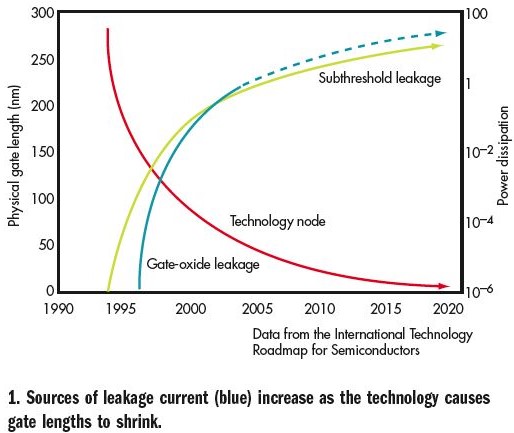

隨著工藝的發展,器件閾值電壓的降低,導致靜態功耗呈指數形式增長。進入深亞微

米工藝后,靜態功耗開始和動態功耗相抗衡,已成為低功耗設計一個不可忽視的因素

2009-09-15 10:18:10 18

18 隨著工藝的發展,器件閾值電壓的降低,導致靜態功耗呈指數形式增長。進入深亞微米工藝后,靜態功耗開始和動態功耗相抗衡,已成為低功耗設計一個不可忽視的因素。針對近

2009-09-15 10:18:10 26

26 放大電路靜態工作點的穩定問題

溫度對靜態工作點的影響

射極偏置電路

1. 基極分壓式射極偏置電路

2. 含有雙電源的射極偏置電路

2010-09-25 16:14:27 86

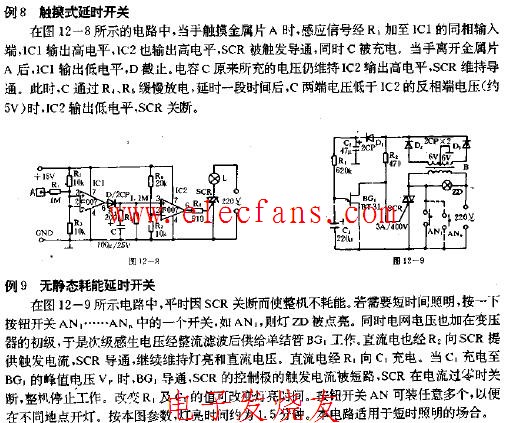

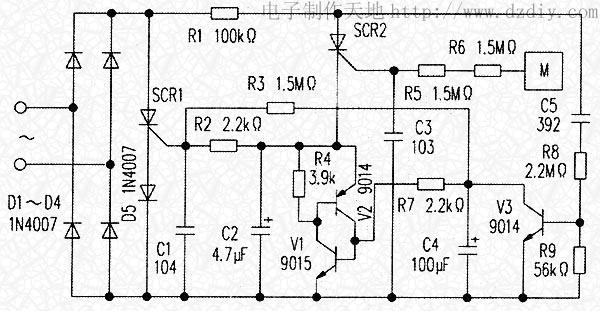

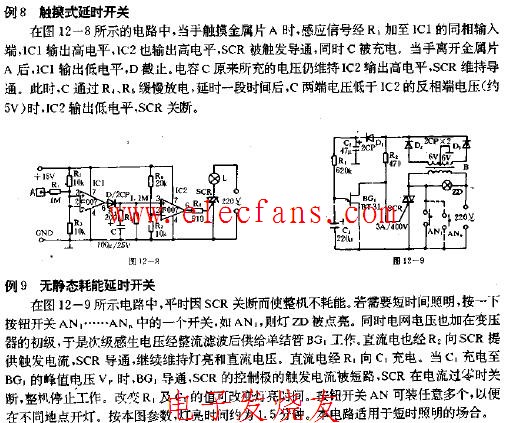

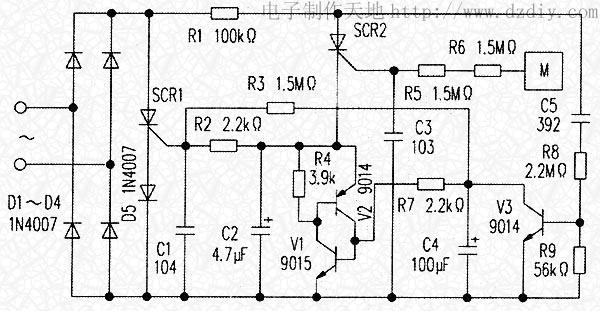

86 無靜態耗能延時開關電路圖:所示的電路中,當手觸摸金屬片A時,感應信號經R1加至IC1的同相輸入端,IC1輸出高電平,IC2也輸出高電平,SCR被觸發導通。

2007-12-13 22:43:30 557

557

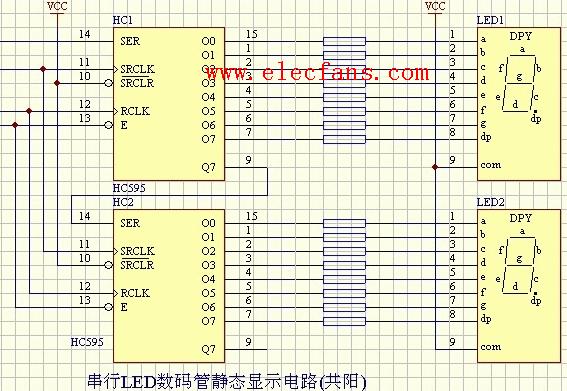

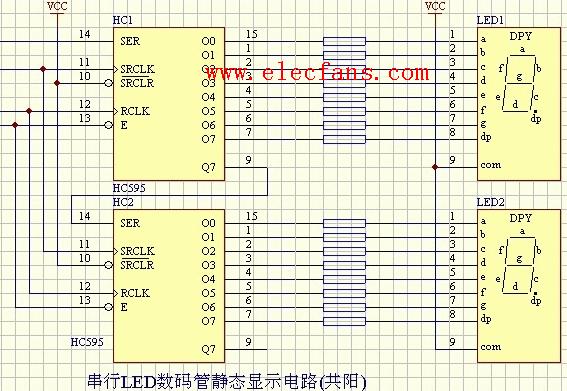

數碼管靜態顯示電路

2008-05-23 16:15:54 3617

3617

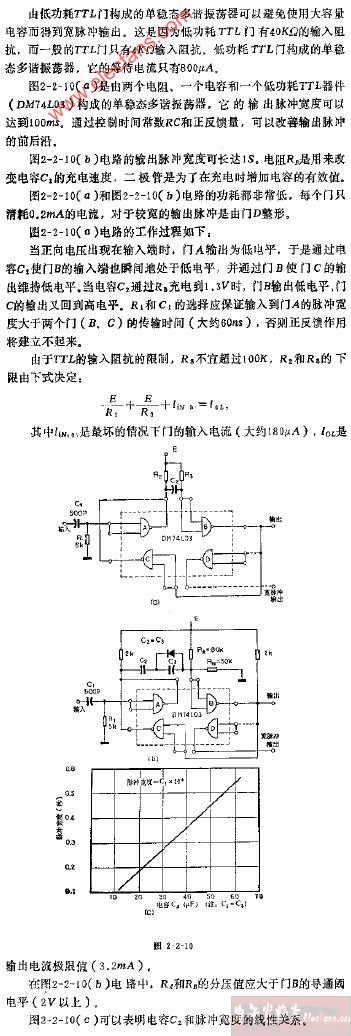

具有低功耗寬脈沖輸出的單穩態電路

2009-03-29 09:17:59 521

521

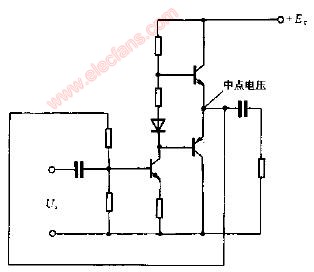

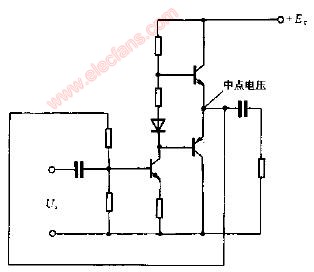

穩定靜態工作點的電路圖

2009-05-06 16:26:18 1493

1493

靜態微功耗雙音門笛電路圖

2009-05-21 13:33:37 595

595

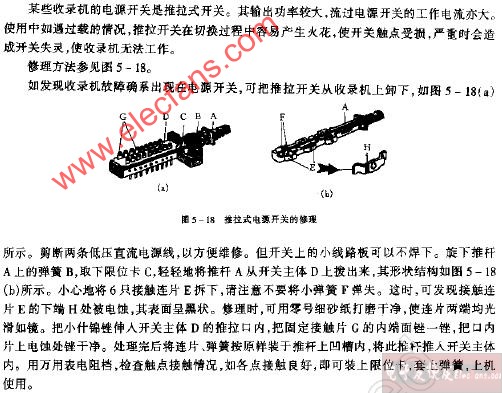

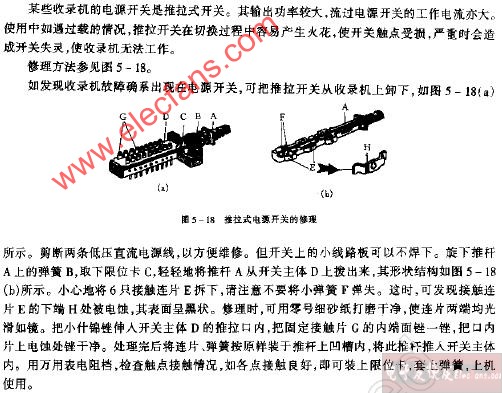

推拉式電源開關的修理

2009-08-22 16:28:41 2155

2155

模塊靜態電流設計電路

我們在設計模塊的時候總是會遇到靜態電流這個不可回避的問題,這在汽車電子和消費類電子(都是用電池的)是非

2009-11-21 13:50:24 529

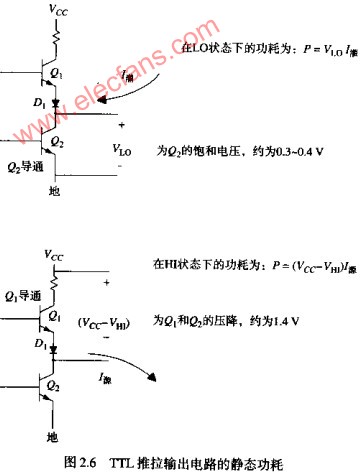

529 靜態功耗是指一個電路維持在一個或另一個邏輯狀態時所需的功率。可以通過觀察電路中每個電阻元件的電流I和壓降V來計算每個元件的功率VI,并求和得到總功率,

2010-05-31 16:28:30 13869

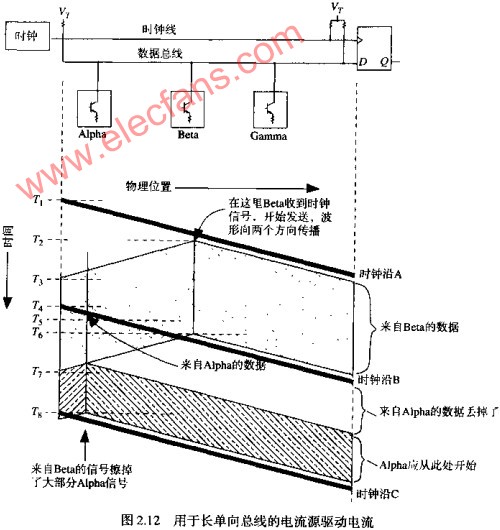

13869 設計者經常僅僅根據所接負載的直流輸入電流要求,冒險使推拉輸出電路的負載達到它的最大直流扇出能力。特別是當設計CMOS總線時這一想法尤其具有誘惑力,因為

2010-05-31 20:31:43 1229

1229

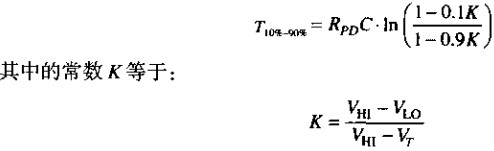

圖2.9舉例說明了一個ECL或GAAS射極跟隨器輸出電路。該電路在HI和LO兩個狀態都有電流流過。

2010-06-01 15:37:55 2123

2123

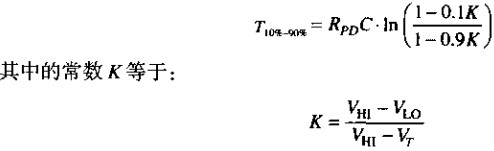

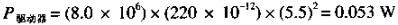

用來計算TTL集電極開路輸出電路靜態功耗的公式如下:

其中:VT=上拉電阻的有效

2010-06-01 16:17:42 2549

2549

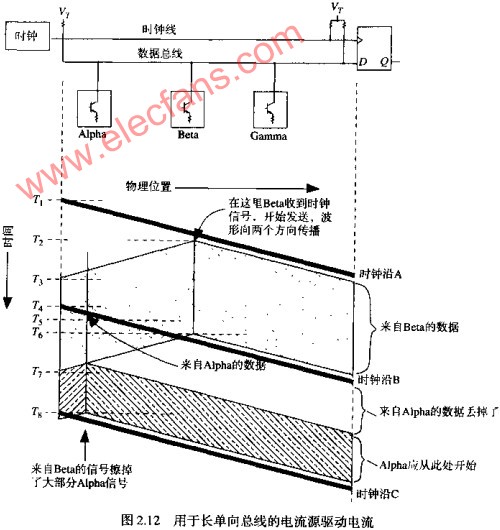

電流源輸出電路具有線性的優勢,通常在一些專門的總路線應用中采用。當驅動一個長的總線時,其電流輸出自然而然地相互疊加,與電壓源輸出中非線性方式的相

2010-06-01 16:53:24 1337

1337

插件板或系統的總功耗十分重要;系統內的每一個FPGA或ASIC開始被迫達到功耗預算。出于該擔憂以及應用高性能90納米FPGA增加靜態功耗的趨勢,Xilinx投入了大量的精力來降低Virtex-4 FPGA的

2011-05-14 18:15:53 24

24 差分放大電路中單端輸出是對地輸出,是不平衡輸出,而雙端輸出的輸出端可以浮地,這時可構成平衡輸出。還有就是雙端輸出的浮地阻抗比單端輸出大一倍。電路如右圖所示,為雙端輸入、單端輸出差分放大電路。由于電路參數不對稱,影響了靜態工作點和動態參數。

2017-11-18 09:27:14 186218

186218 本文介紹了放大電路靜態工作點的穩定問題,解析了溫度對靜態工作點的影響和射極偏置電路。

2017-11-23 11:02:38 19

19 分壓偏置式共射極放大電路即基極分壓式射極偏置電路。是BJT的放大電路的三種組態之一。基極電壓固定了,流過基極的靜態電流也就固定了,靜態工作的也固定了。

2017-11-29 08:46:34 95925

95925

功耗由靜態功耗和動態功耗組成。靜態功耗是FPGA在被編程目標文件(.pof)編程時、但時鐘不工作的狀態下所需的功耗。數字和模擬邏輯都消耗靜態功耗。在模擬系統中,靜態功耗主要包括由其接口模擬電路的靜態電流決定的功耗(圖2和表)。

2019-05-16 08:04:00 7725

7725

無靜態功耗觸摸延熄開關.電路如圖所示。由于在圖中的R8處,串聯了一個耐壓400V以上的小容量電容C5,平時沒有任何靜態電流。每次SCR1導通的時候,此小容量電容通過R1、R8、R9放電,延熄結束后,220V脈動直流電向此小容量電容快速充電。

2019-02-16 09:25:36 963

963

級分別采用PNP 管和NMOS 管作為上拉管和下拉管, 結合電路結構的改進使之具有軌到軌( r ail-to-r ail) 的輸出特性和很低的靜態電流。設計的電路具有開環增益大、靜態功耗小、帶寬較高等特點。此運放已在1. 5 um BCD 工藝下實現。測試結果表明,

2018-12-18 16:11:33 4

4 靜態功耗是指一個電路維持在一個或另一個邏輯狀態時所需的功率。可以通過觀察電路中每個電阻元件的電流I和壓降V來計算每個元件的功率VI,并求和得到總功率,這就是沒有負載的情況下的靜態功耗,也就是我們通常在數據手冊上看到的標稱值。

2019-07-16 14:41:02 9837

9837 對于放大電路來說,其放大作用的前提是要保證輸出波形不失真。但是,由于晶體管是一個非線性器件,由于靜態工作點設置不當或輸入信號過大等原因,可能會引起輸出波形失真。

2019-09-26 08:59:43 65285

65285

以共發射極放大電路為研究背景,在電路參數和負載電阻已經確定、并且深入分析T/J,信號放大電路的基礎上,利用放大電路輸出特性曲線,得到了放大電路輸出最大不失真幅度與靜態工作點設置估算值。以上結果對放大電路的設計、使用、調試均具有較大幫助,具備較好的實際應用價值。

2019-10-31 08:00:00 6

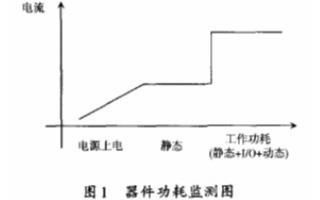

6 功耗一般由兩部分組成:靜態功耗和動態功耗。靜態功耗也稱為待機功耗,是指邏輯門沒有開關活動時的功率消耗,主要是由晶體管的漏電流引起,由源極到漏極的漏電流以及柵極到襯底的漏電流組成,圖1中靜態部分顯示

2020-01-16 09:46:00 7871

7871

推拉抽拉式SIM6P卡座原理圖

2022-01-05 09:42:33 19

19 超低功耗電源模塊DCDC降壓模塊高效率3.3V5V效率超LM2596低靜態電流,可用于低功耗手持設備,低功耗儀表等設備輸入電壓范圍:3-17V輸出電壓范圍:1-6V輸出電流:最大3A靜態電流:<

2022-01-05 15:02:35 8

8 SNO-1310

產品名稱:6+1PIN推拉式

操作方式:推拉式

溫度范圍:-40°C TO +80°C

操作壽命:5000Cycles

包裝方式:卷帶

最小包裝:1800/PCS

2022-09-26 16:39:47 0

0 的模塊設計理念讓配置更靈活,從而使之成為單一或多功能應用都具很高性價比的推拉力測試系統。LB-8600推拉力測試儀使得它已經成為半導體、光電和電路板組裝行業的理想測試設備。LB-8600推拉力測試機是一種多功能焊接強度測試儀,可執行所有推拉力和剪切力測試應用。 L

2022-10-20 18:09:28 791

791 ?這幾天,試驗機老二給大家介紹了推拉力試驗機相關的知識,有些粉絲事后咨詢試驗機老二,推拉力試驗機的推拉力測試是什么意思,接下來,試驗機老二便給大家說說推拉力試驗機之推拉力試驗相關的知識點。

2022-11-02 14:58:20 1080

1080

靜態工作點可以影響到三極管的輸出波形,導致輸出出現截止失真和飽和失真,所以在設計時需要考慮不要出現這種問題,根據經驗常常讓三極管c極靜態工作點VCQ=VCC/2,另外一個可以借鑒的經驗是讓Rc≈10RE。

2023-01-12 14:22:14 4962

4962

共射極放大電路的靜態分析是指對該電路在直流偏置下的電性能進行分析。靜態分析的目的是確定晶體管的靜態工作點,即晶體管在偏置電路下的電流和電壓值,從而保證電路在穩定工作的狀態下能夠有效放大輸入信號。

2023-02-27 11:10:31 7328

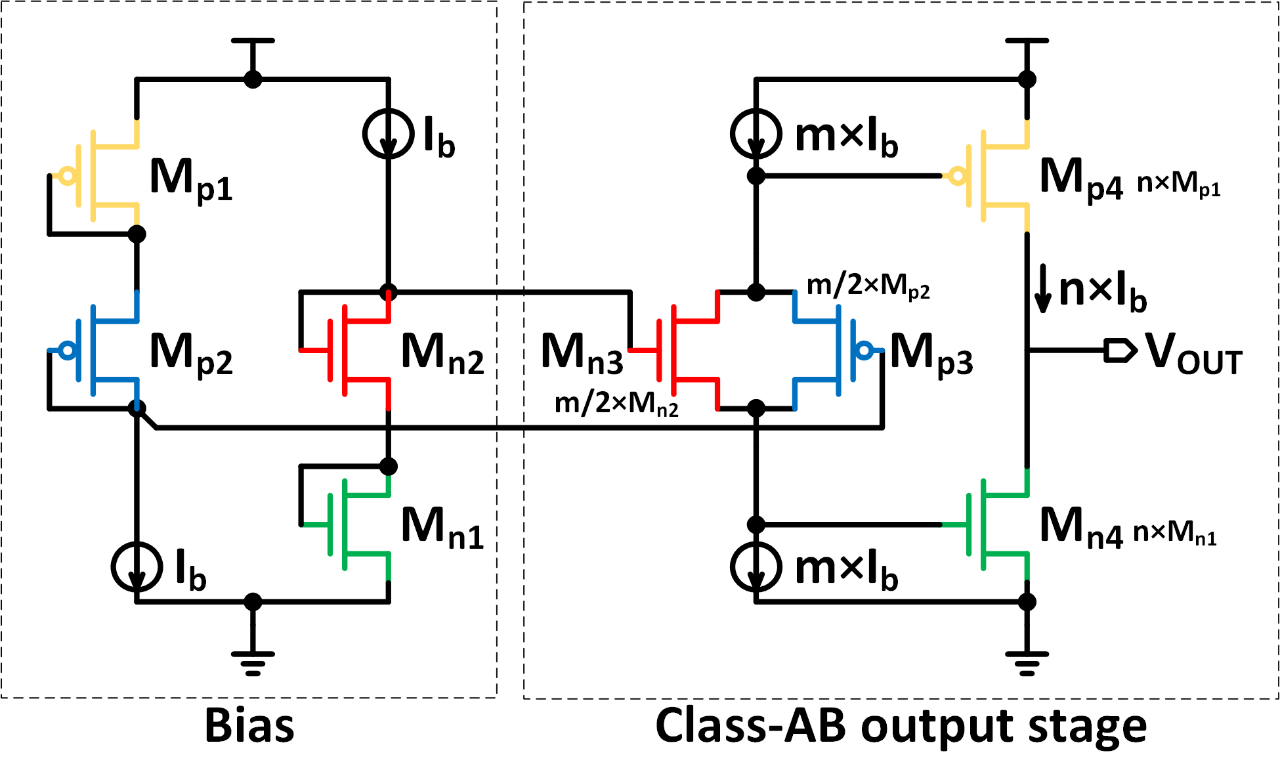

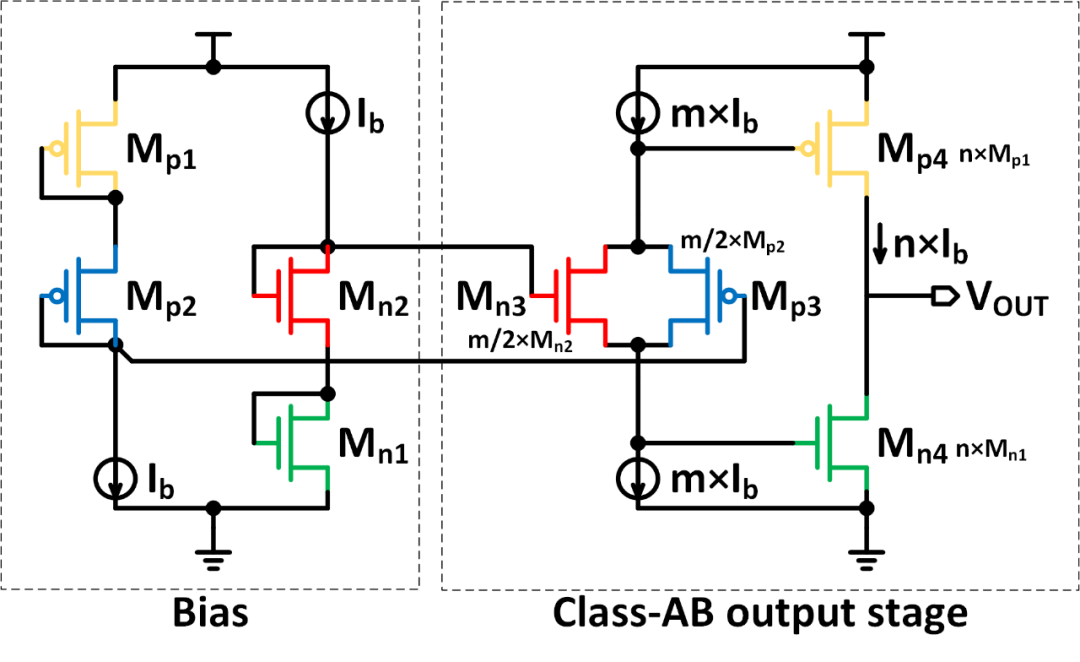

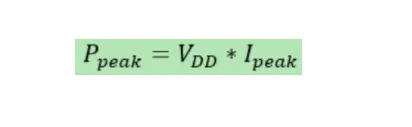

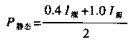

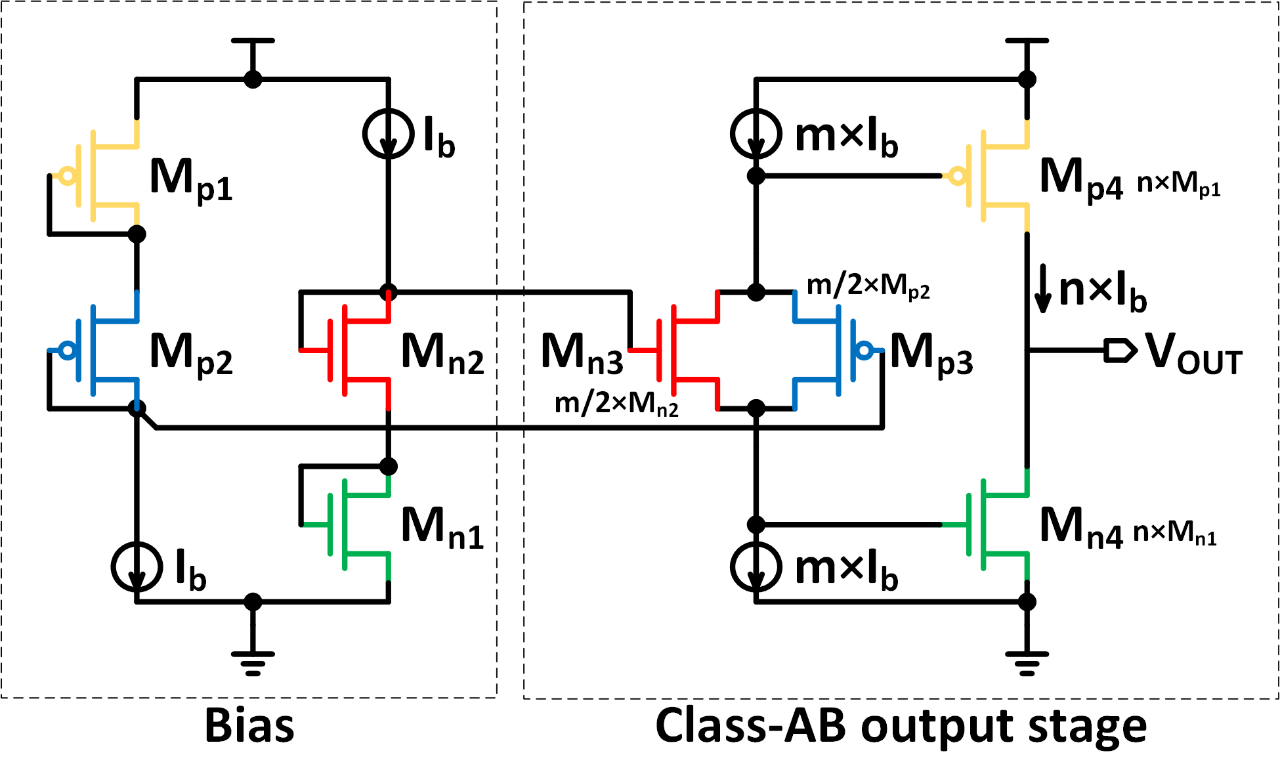

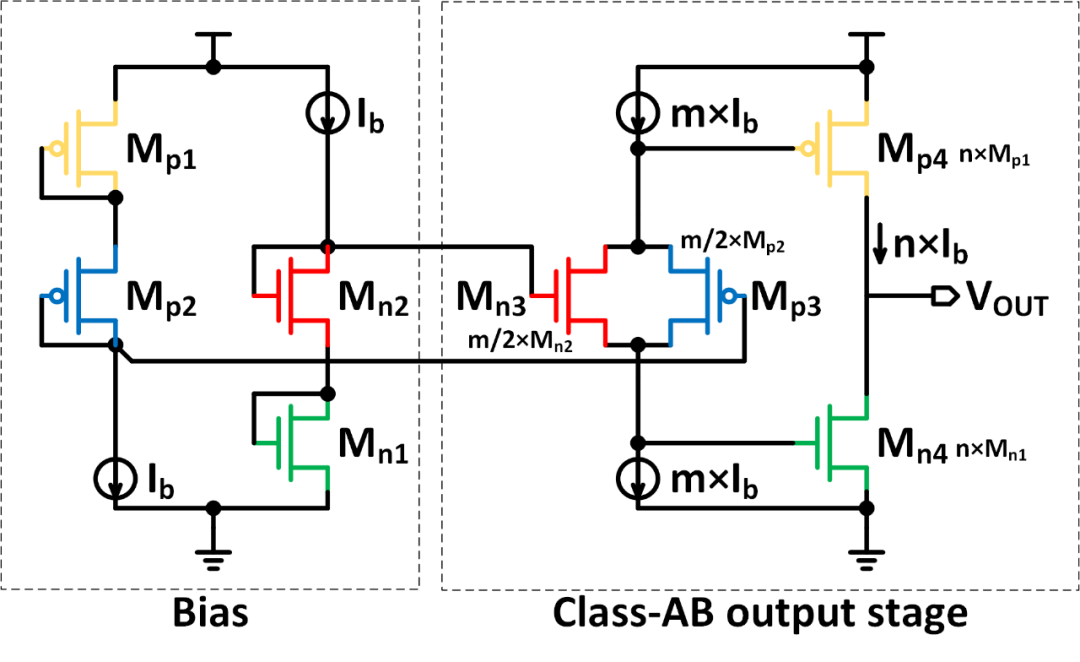

7328 和NMOS都受前級信號的控制,相比傳統結構輸出級只有PMOS或NMOS被前級輸入信號控制,其需要更為復雜的偏置或者說控制電路。在之前筆者的文章中,認為運放靜態工作點的設計幾乎等于電流鏡的設計,本文也將延續這一思路,對Class-AB輸出級靜態工作點的偏置設計進行淺析,若有不足,歡迎指正。

2023-04-10 14:57:01 6672

6672

金絲鍵合推拉力測試機應用

2023-05-16 14:32:55 564

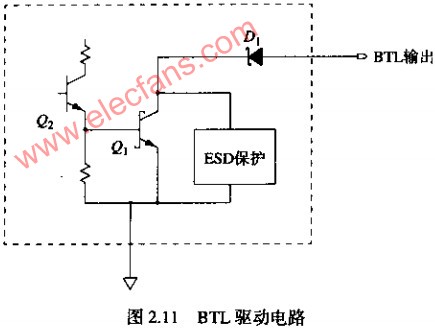

564 采用Class-AB輸出級設計的運放可在較低的靜態電流下實現軌對軌輸出,推挽的輸出方式使得其在大信號建立時的電流不受靜態電流的限制,可以實現更好的壓擺率。

2023-07-07 11:38:15 561

561

CMOS靜態功耗是指在CMOS電路中,當輸入信號不變時,電路中的電流仍然存在,這種電流被稱為靜態電流,也被稱為漏電流。CMOS靜態功耗是指在這種情況下,電路中的功率消耗。

2023-07-21 15:47:03 1523

1523

ttl電路中推拉輸出,集電極開路輸出,三態輸出有何不同?? TTL電路是一種常見的數字邏輯電路,在電路中經常出現推拉輸出、集電極開路輸出、三態輸出這些術語。這些輸出方式在不同的電路中具有不同的意義

2023-08-31 10:32:19 2131

2131 不能正確工作,甚至會損壞元件。本文將詳細介紹放大電路的靜態工作點的概念、作用及如何設置。 一、放大電路的靜態工作點的概念 放大電路是指將輸入信號放大后輸出的電路。其基本結構一般包括輸入端、輸出端和放大元件。放大

2023-09-13 14:15:37 4949

4949 靜態工作點對放大電路性能的影響? 靜態工作點是指電子元件的一種工作狀態,在電路中起著非常重要的作用。對于放大電路來說,靜態工作點的選取直接影響到放大電路的性能,它既不能太高也不能太低。下面我們將詳細

2023-09-13 14:15:41 6892

6892 為什么放大電路的靜態工作點要設計在Q點? 放大電路常常用于電子設備的設計中,它使得信號能夠被有效放大并且在信號傳輸中發揮極大的作用。為了使放大電路的工作成為可能,必須確定一個靜態工作點,在這

2023-09-13 14:16:42 1489

1489 基本放大電路中靜態值和靜態工作點一樣嗎?? 基本放大電路是指通常用于信號放大和增強的電路,它是電子工程中最基本的電路之一。在基本放大電路中,靜態值和靜態工作點都是非常重要的概念,但它們并不是完全相同

2023-09-13 14:17:50 1054

1054 類型。靜態電路主要指的是電子設備中沒有時序要求的電路,例如門電路、反相器電路、仲裁電路等;而動態電路指的是需要時序控制的電路,其主要包括計數器、觸發器、存儲器等。動態電路的主要特點是速度快、功耗低、產生噪聲和抖動

2023-09-17 10:47:32 2795

2795 靜態功耗也叫靜態電流,是指芯片在靜止狀態下的電流或者是指芯片在不受外界因素影響下自身所消耗的電流。靜態功耗是衡量芯片功耗與效率地重要指標。

2023-09-22 16:31:45 319

319

改變靜態工作點對放大電路有什么影響?如果輸出波形失真應該如何調整電路? 一、改變靜態工作點對放大電路的影響 靜態工作點是指放大器的直流輸入與輸出參數。在放大器電路中,靜態工作點的選擇非常重要,如果

2023-10-18 14:48:48 4584

4584 靜態工作點對放大器有什么影響?靜態工作點變化對放大器輸出波形的影響? 靜態工作點對放大器有著重要的影響,接下來就此展開討論。 什么是靜態工作點? 在放大器的輸入信號不變的情況下,放大器輸出的直流分量

2023-10-18 14:48:51 7542

7542 為什么需要芯片靜態功耗測試?如何使用芯片測試工具測試芯片靜態功耗? 芯片靜態功耗測試是評估芯片功耗性能和優化芯片設計的重要步驟。在集成電路設計中,靜態功耗通常是指芯片在不進行任何操作時消耗的功率

2023-11-10 15:36:27 1117

1117

電子發燒友App

電子發燒友App

評論