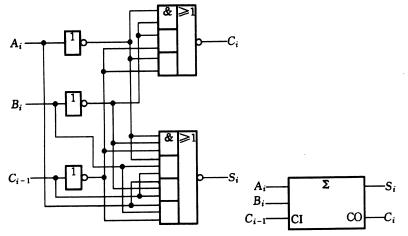

用5個繼電器互相連接構成的邏輯門電路,該邏輯門可執行二進制加法運算并求出總和的繼電器連接電路。輸入接VCC表示1,接GND表示0,通過繼電器電壓進行連接。全加器包括3個輸入端:進位輸入和2個加數,2

2016-07-14 20:36:37

組合邏輯:基本邏輯門Wirewire線型的基本描述已在筆記整理(1)中給出了。題目:實現輸入與輸出的連接。答案:module top_module ( input in, output out

2021-09-08 07:32:26

74LS125 1塊雙全加器 74LS183 1塊實驗報告要求1. 畫出實驗邏輯圖, 列出實驗數據表格, 填入實驗結果, 并寫出各種門電路的邏輯函數表達式或邏輯功能。2. 敘述在與非門、或非門、異或門、三態門實驗中用示波器觀察方波波形的結果,并說明原因。

2008-09-25 17:28:34

我們還看到,每個門分別具有與非門,或非門和緩沖器形式的相反或互補形式,并且這些門中的任何一個都可以連接在一起以形成更復雜的組合邏輯電路。我們還看到,在數字電子產品中,“與非”門和“或非”門都可以被

2021-01-27 08:00:00

真值表 除了邏輯表達式,邏輯函數的描述方法還包括真值表和邏輯門。針對邏輯函數所有可能的輸入組合一一列出輸出值,我們就可以得到真值表。對于組合邏輯電路,只要列出所有可能的輸入和對應的輸出值,就可以完整

2020-12-23 17:25:49

FPGA中組合邏輯門占用資源過多怎么降低呢?有什么方法嗎?

2023-04-23 14:31:17

FPGA小白一枚,個人理解的FPGA本質上或者核心就是查找表(LUT),即將所有的函數/方法 轉換為固定的查找表(使用DSP除外)。但是為什么所有的文章提到FPGA全部都注重邏輯門呢?其實FPGA本身內部也沒有多少物理的邏輯門吧?

2019-05-30 10:53:46

TTL邏輯門與普通邏輯門的區別在哪里為什么引入OC門?

2021-03-29 07:23:21

1 前言 52 典型電路的設計 52.1 全加器的設計 62.2 數據通路 62.2.1 四選一的多路選擇器 62.2.2 譯碼器 72.2.3 優先編碼器 82.3 計數器 92.4 算術操作

2017-12-08 14:42:07

請問大家,pspice的邏輯門模型,比如說與門7408,該怎樣修改其參數?我想修改7408的延遲時間,輸出電平等等,怎么弄?關于右鍵點擊然后edit pspice model的方法,我試過,只是出來

2014-06-24 10:09:17

FPGA數字邏輯電路的設計與分析,包含項目實例、全流程設計說明文檔,項目源代碼文件。

2021-03-30 14:48:05

“通用”門,因為它是最常用的邏輯門類型之一。NAND門還可用于產生任何其他類型的邏輯門功能,并且在實踐中,NAND門構成大多數實用邏輯電路的基礎。例如,通過以各種組合將它們連接在一起,可以僅使用“與非

2021-01-22 08:00:00

邏輯或門是一種數字邏輯電路,僅當其一個或多個輸入為高電平時,其輸出才變為邏輯電平1。“邏輯或門”的輸出Q僅在其所有輸入均為邏輯電平“ 0”時才再次返回“ LOW ”。換句話說,對于邏輯或門,任何“高

2021-01-21 08:00:00

邏輯或門是一種數字邏輯電路,僅當其一個或多個輸入為高電平時,其輸出才變為邏輯電平1。“邏輯或門”的輸出Q僅在其所有輸入均為邏輯電平“ 0”時才再次返回“ LOW ”。換句話說,對于邏輯或門,任何“高

2021-01-20 09:00:00

信號反相輸入反轉的氣泡符號NAND和NOR門等效例如,也可以使用標準的NAND和NOR門制作反相器或邏輯非門,方法是將其所有輸入連接到公共輸入信號。如圖所示,也可以僅使用單級晶體管開關電路來制造非常簡單

2021-01-21 09:00:00

一.TTLTTL集成電路的主要型式為晶體管-晶體管邏輯門(transistor-transistor logic gate),TTL大部分都采用5V電源.1.輸出高電平Uoh和輸出低電平UolUoh

2016-08-23 21:39:46

。五、邏輯電路 根據是否包含記憶元件課分為組合邏輯電路和時序邏輯電路。 組合邏輯電路:不包含記憶元件,某時間點的輸出僅僅取決于當時的輸入。有多個輸入輸出,內部用于基本邏輯函數的邏輯門,以及門電路間的連線

2019-12-10 20:32:03

用VHDL的人好少,哎……一位全加器的邏輯表達式是: S=A⊕B⊕Ci Co=AB+ACi+BCi 然后是代碼:[code]USE IEEE.STD_LOGIC_1164.ALL; USE

2014-12-09 22:16:51

門電路是由哪些元件組成的?TTL與非門的外特性及其參數有哪些?上拉電阻R對NMOS邏輯門電性能有何影響?

2021-11-05 09:08:47

Verilog數字系統設計四復雜組合邏輯實驗2文章目錄Verilog數字系統設計四前言一、什么是8位全加器和8為帶超前進位的全加器?二、編程1.要求:2.門級原語實現8位全加器:3.門級原語實現帶

2022-02-09 07:49:48

邏輯門是數字電路的基礎。各種多姿多彩的邏輯門組合在一起,形成了數字電路的大千世界。實際上,邏輯門反映的是邏輯代數的幾種基本運算,只要你能夠實現這樣的邏輯代數規則,你就能夠用其他設備來實現邏輯門的功能,看!

2019-07-23 07:03:30

加數,還有一個來自低位送來的進位數。這三個數相加,得出本位和數(全加和數)和進位數,這就是“全加”,表2是全加器的邏輯狀態表 全加器可用兩個半加器和一個或門組成,如圖2(a)所示。在第一個半加器中相加

2018-10-11 16:33:47

華為 邏輯電路設計規范自己選擇下載閱讀!

2015-08-04 14:46:14

介紹了模擬電路術語、邏輯門高速特性和標準高速電路測量方法和技巧等內容。這三章內容構成了本書的核心,應該包括在任何高速邏輯設計的學習中。其余章節,第4章——第12章,每一章都講述了一個高速邏輯設計中的專門

2018-01-22 17:32:54

1、集成邏輯門及其基本應用介紹本實驗涉及到的基本邏輯門有“與門”、“與非門”、“或門”、“或非門”、“異或門”和“同或門”,功能簡單,實驗時使用2個撥動開關模擬邏輯門的輸入信號,通過LED燈的點亮或

2022-07-01 15:18:51

電子設計的主流。VHDL語言作為可編程邏輯器件的標準語言描述能力強,覆蓋面廣,抽象能力強,應用越來越廣泛。VHDL語言具有多層次描述系統硬件功能的能力,可以從系統的數學模型直到門級電路,其高層次的行為

2018-11-20 10:39:39

集成電路編碼器和譯碼器的工作原理即邏輯功能是什么?如何利用邏輯門去實現一種集成電路編碼器呢?如何利用譯碼器進行組合邏輯電路的設計呢?

2021-11-03 06:55:24

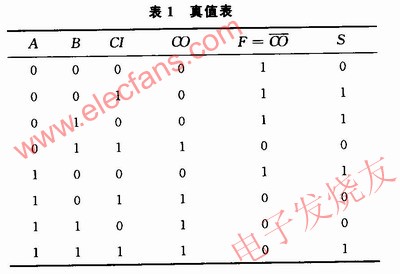

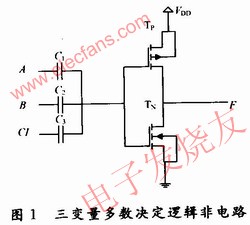

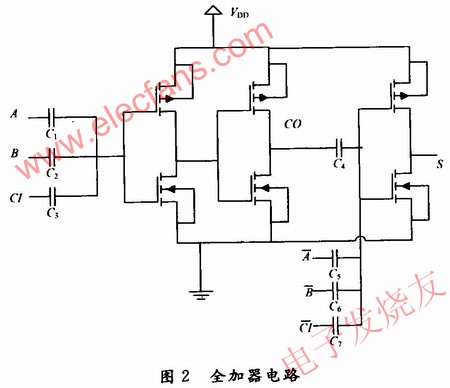

什么是多數決定邏輯非?求一種基于多數決定邏輯門的全加器電路設計?

2021-04-08 06:07:47

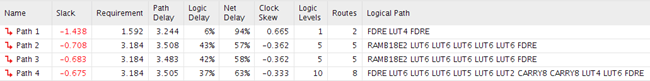

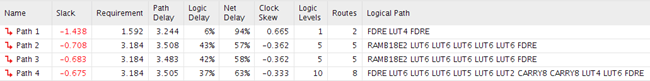

你好。我是在FPGA上設計系統的初學者。我的fpga是XC7K325T -2 FFG900(knitex - 7系列)我想計算基本15位2輸入加法器的邏輯延遲。如果我能檢查AND門或OR門的延遲等

2020-05-25 07:28:24

如何用兩片四位全加器和必要的邏輯門設計數制轉換電路 將輸入的十進制轉換成二進制 十進制輸入采用8421BCD碼表示

2016-07-04 14:52:00

怎么實現基于可編程邏輯器件的數字電路設計?

2021-05-06 08:36:18

請問怎么將無源器件連接到邏輯門?

2021-04-13 06:48:09

灌電流是什么?灌電流越大與邏輯門輸出端的低電平有何關系?拉電流是什么?拉電流越大與邏輯門輸出端的高電平有何關系?

2021-10-11 08:53:52

數字邏輯門可用于連接到外部電路或設備,但必須注意確保其輸入或輸出正確運行并提供預期的開關條件。現代數字邏輯門,IC和微控制器包含許多稱為“引腳”的輸入以及一個或多個輸出,這些輸入和輸出需要正確設置

2021-01-28 08:00:00

現在我需要一個邏輯門器件,與門和或門。要求是在輸入時間為100ns的脈沖信號(可調),兩個輸入,一個輸出。然后通過這個邏輯門器件之后可以用示波器檢測到。。。新人也不懂 啊,需要什么型號的器件呢?

2018-09-17 16:01:36

時序邏輯電路設計6.1 基本D觸發器的設計6.2 JK觸發器6.3 帶異步復位/置位端的使能T觸發器6.4 基本計數器的設計6.5 同步清零的計數器6.6 同步清零的可逆計數器6.7 同步預置數的計數器

2009-03-20 10:04:53

描述邏輯門學習套件在這個項目中,您將學習如何構建自己的邏輯門學習套件并了解所有關于不同邏輯門的知識。不是非門用于反轉信號。下面是邏輯門的真值表和繪圖。 和與門用于接收 2 個或更多信號,并且僅在

2022-09-08 07:42:05

組合邏輯電路實驗實驗三 組合邏輯電路一、 實驗目的1、 掌握組合邏輯電路的功能測試2、 驗證半加器和全加器的邏輯功能3、 學會

2009-03-20 18:11:09

組合邏輯電路的設計實驗 實驗三 組合邏輯電路的設計實驗

2009-10-24 19:19:30

自動門的電路設計需要考慮以下幾個因素: 電路功能指標:需要設計一個能夠實現自動開關門功能的電路,并且保證電路運行的安全性和穩定性。 控制電路:需要設計一個能夠控制自動門開關的電路,包括門鎖

2023-04-13 14:27:54

異成門邏輯符號圖/同或門邏輯符號圖

2019-10-23 03:49:43

用兩片四位全加器74283和必要的邏輯門設計一個數制轉換電路,實現將輸入的兩位十進制數轉換成二進制數,十進制數的輸入采用8421BCD碼來表示

2015-07-09 16:12:39

鐘控傳輸門絕熱邏輯電路和SRAM 的設計本文利用NMOS管的自舉效應設計了一種新的采用二相無交疊功率時鐘的絕熱邏輯電路---鐘控傳輸門絕熱邏輯電路,實現對輸出負載全絕熱方式充放電.依此進一步設計了

2009-08-08 09:48:05

(logic cell library),作為合成邏輯電路時的參考依據。硬件語言設計描述文件的編寫風格是決定綜合工具執行效率的一個重要因素。事實上,綜合工具支持的HDL 語法均是有限的,一些過于抽象的語法

2016-06-29 11:27:02

集成邏輯電路、組合邏輯電路實驗目的1. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態門的邏輯功能以及禁止狀態的判別方法。了解三態門的應用。3. 掌握組合邏輯電路的設計和實現方法

2008-12-11 23:36:32

基本邏輯電路: 組合邏輯電路、&

2008-09-12 16:35:29 40

40 組合邏輯電路設計一、實驗目的1. 熟悉組合邏輯電路的基本設計方法;2. 練習用門電路、譯碼器、數據選擇器設計組合邏輯電路。二、實驗設備1.

2008-09-12 16:41:23 0

0 時序邏輯電路的輸出不但和當前輸入有關,還與系統的原先狀態有關,即時序電路的當前輸出由輸入變量與電路原先的狀態共同決定。為達到這一目的,時序邏輯電路從某一狀態

2009-03-18 22:13:04 71

71 組合邏輯電路實驗分析一、實驗目的 1.掌握組合邏輯電路的分析方法與測試方法; 2.了解組合電路的冒險現象及消除方法; 3.驗證半加器、全加器的邏輯功

2009-07-15 18:35:50 0

0 用Protel 99實現邏輯電路設計:介紹可鳊程邏輯器件(PLD)應用和相應軟件的發展;使用EDA 工具Protel 99的PLD設計簡單邏輯電路的一般方法。關鍵詞Protel 99 PLD CUPL語言

眾所周知,

2009-11-01 10:13:34 0

0 VHDL硬件描述語言與數字邏輯電路設計:本書系統地介紹了一種硬件描述語言,即VHDL語言設計數字邏輯電路和數字系統的新方法。這是電子電路設計方法上一次革命性的變化,也是邁

2010-02-06 16:55:22 359

359 摘要:本文對數字邏輯電路關于同步時序邏輯電路設計的關鍵步驟中,引入代數理論輔助設計作了一些探討,并用實例表明這樣的努力使設計過程得到了大大的簡化。關鍵詞:同

2010-04-29 09:35:20 12

12 摘要:介紹了可以簡化邏輯電路設計的可蝙程邏輯器件EPLD.詳述了它的工作原理、開發工具舉例說明了應用IPLD設計電路的具體過程。

2010-04-30 10:21:03 35

35 講述組合邏輯電路設計基礎

2010-05-06 10:29:15 0

0 數字邏輯電路設計課程

數字邏輯電路的設計包括兩個方面:基本邏輯功能電路設計和邏輯電路系統設計。關于基本邏輯功能電路設計一般在《數字電路技術基礎

2010-05-24 16:05:50 0

0 基于單電子晶體管的I-V特性和傳輸晶體管的設計思想,用多柵單電子晶體管作為傳輸晶體管,設計了一個由5個SET構成的全加器,相對于靜態互補邏輯設計的全加器,本文設計的全加器在器

2010-07-30 16:54:22 18

18 全加器

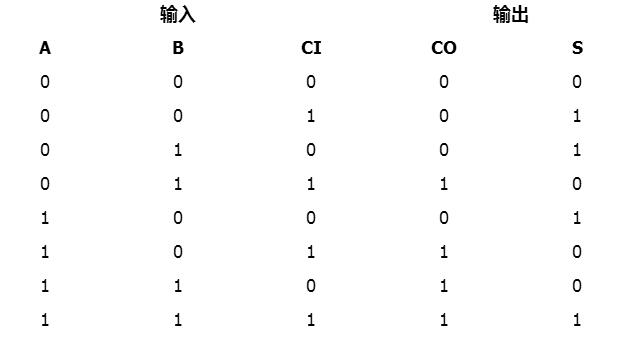

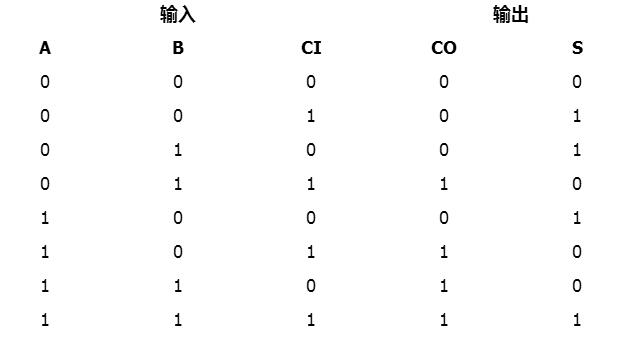

全加器能進行加數、被加數和低位來的進位信號相加,并根據求和結果給出該位的進位信號。 根據全加器的功能,可列出它的真值表:

2009-04-07 10:34:54 8646

8646

基于可編程邏輯器件的數字電路設計

0 引 言

可編程邏輯器件PLD(Programmable Logic De-vice)是一種數字電路,它可以由用戶來進行編程和進行配置,利用它可以

2009-11-16 10:46:41 1473

1473

全加器,全加器是什么意思

full-adder 用門電路實現兩個二進數相加并求出和的組合線路,稱為一個全加器。

2010-03-08 17:04:58 80275

80275 什么是一位全加器,其原理是什么

加器是能夠計算低位進位的二進制加法電路

一位全加器由2個半加

2010-03-08 17:13:33 73577

73577 實驗五 全加器、譯碼器及數碼顯示電路 一、實驗目的 1、掌握全加器邏輯功能,熟悉集成加法器功能及其使用方法。 2、掌握用七段譯碼器和七段數碼管顯示十進制數的方法。 3、掌握

2012-07-16 23:01:22 38

38 數字邏輯電路設計實踐_電工電子實驗中心實驗報告。

2015-10-29 16:25:13 0

0 定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計

2015-12-17 18:18:50 0

0 數字電子鐘邏輯電路設計,我自己編寫的,里面有橫多實用的東西

2016-06-22 16:12:01 54

54 VHDL硬件描述語言與數字邏輯電路設計,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 14:20:34 0

0 基于排序網絡的大數邏輯門電路設計_孫宇

2017-01-07 19:00:39 0

0 一種多數據集混合累加電路設計_胡浩

2017-01-07 20:49:27 4

4 一種基于互補型單電子晶體管的全加器電路設計

2017-02-07 16:14:56 8

8 一種基于包的邏輯內置自測試電路設計方法

2017-02-07 16:14:56 12

12 多數據融合的四軸飛行器硬件電路設計_高明

2017-03-19 11:41:39 3

3 引言 在全加器設計中運用PG邏輯是非常普遍的,本文在設計和研究全加器時,根據現有的PG邏輯公式推導出了一種新的邏輯公式,并論證了兩者之間的等價關系。這一新的公式能夠指導全加器設計中的連線方式,靈活

2017-11-06 11:49:57 0

0 本文為大家帶來五種三人表決器電路設計方案,包括兩款仿真電路及程序分析,三款邏輯電路設計的原理詳解。

2018-01-17 18:49:21 298033

298033

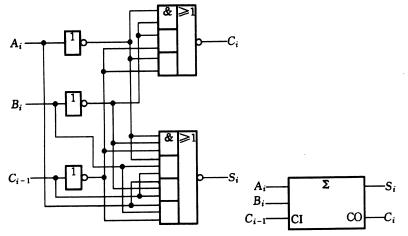

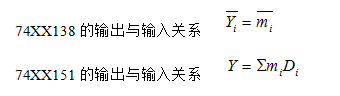

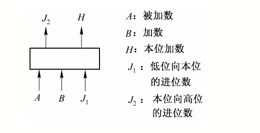

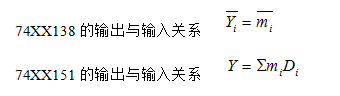

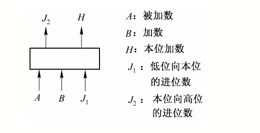

本文主要介紹了用74ls151實現全加器設計電路。根據全加器的定義可知:輸入為:A,B,Ci其中A,B為被加數和加數,Ci為低位進位數。輸出為:S,Co,其中S為本位和數,Co為高位進位數。其邏輯關系為:S=A⊕B⊕Ci;Co=AB+(A⊕B)Ci。

2018-05-07 09:52:22 111841

111841

加器是能夠計算低位進位的二進制加法電路。與半加器相比,全加器不只考慮本位計算結果是否有進位,也考慮上一位對本位的進位,可以把多個一位全加器級聯后做成多位全加器。

2018-07-25 11:15:53 68629

68629

全加器是一個能夠完成一位(二進制)數相加的部件。我們先來看一下兩個二進制數的加法運算是怎樣進行的。

2018-07-25 15:48:44 69729

69729

全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加并求出和的組合線路,稱為一位全加器。

2018-07-25 16:03:28 74844

74844 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-05-16 18:32:37 7636

7636

全面處理,提取了和麗數進位兩數優化函數式。根據最優化函數式,設計了高性能CMOS管級全加器單元電路。這種CM0S全加器電路與常用CMOS全加器電路相比,電路結構簡單、芯片面積小。電路傳輸延遲時間小,運算速度快。

2019-07-03 17:11:16 38

38 本文主要介紹了全加器邏輯表達式及全加器的邏輯功能。

2020-04-23 09:51:14 114221

114221

全加器的輸入端有三個,分別為A、B、C(低位的進位);兩個輸出S(和);C(運算產生的進位)。

2020-04-23 09:59:42 100473

100473

全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進位,并輸出本位加法進位,多個一位全加器進行級聯可以得到多位。全加器是形成三位算術和的組合電路,它由三個輸入和兩個輸出組成。

2021-06-29 09:14:46 56800

56800

Verilog數字系統設計四復雜組合邏輯實驗2文章目錄Verilog數字系統設計四前言一、什么是8位全加器和8為帶超前進位的全加器?二、編程1.要求:2.門級原語實現8位全加器:3.門級原語實現

2021-12-05 19:06:10 4

4 可規劃邏輯電路設計與實習報告

2021-12-23 17:28:52 5

5 避免常見的邏輯電路設計問題

2022-11-04 09:50:16 0

0 時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序邏輯電路的核心部分——計數器。

2023-05-22 17:01:29 1882

1882

在FPGA邏輯電路設計中,FPGA設計能達到的最高性能往往由以下因素決定。

2023-09-26 11:31:03 691

691

全加器是計算機中常用的一種邏輯電路,用于實現二進制加法運算。全加器接受兩個輸入位和一個進位位,并輸出一個和位和一個進位位。它的邏輯表達式可以通過推導和分析得出。 首先,讓我們回顧一下二進制加法的規則

2023-12-25 16:09:03 827

827

![]()

電子發燒友App

電子發燒友App

評論