引言

短波通信信道具有時(shí)變和色散的特性,并且容易受到噪聲干擾,所以模擬其傳輸特性,具有很高的實(shí)用價(jià)值。短波信道模擬器借助先進(jìn)的仿真技術(shù)手段實(shí)現(xiàn)在實(shí)驗(yàn)室環(huán)境下進(jìn)行通信試驗(yàn),因其具有有效性、經(jīng)濟(jì)性、安全性和直觀性等特點(diǎn),在通信試驗(yàn)中可廣泛使用。傳統(tǒng)的短波信道模擬器大部分停留在話音帶寬上,其主要不足是功耗過(guò)高、體積龐大、可控性不高及實(shí)時(shí)性不好。模數(shù)轉(zhuǎn)換器( A/ D)器件和數(shù)字信號(hào)處理理論的飛速發(fā)展,為研制寬帶短波信道模擬器奠定了堅(jiān)實(shí)的基礎(chǔ),但由于現(xiàn)有的數(shù)字信號(hào)處理器( DSP) 處理速度有限,往往難以對(duì)高速率A/ D 采樣得到的數(shù)字信號(hào)直接進(jìn)行實(shí)時(shí)處理,為了解決這一矛盾,需要采用數(shù)字下變頻( DDC) 技術(shù)。所以數(shù)字下變頻技術(shù)在寬帶短波信道模擬器的數(shù)字化和軟件化過(guò)程中起到了重要的作用。FPGA 具有較高的處理速度和很強(qiáng)的穩(wěn)定性,而且設(shè)計(jì)靈活、易于修改和維護(hù),同時(shí)可以根據(jù)不同的系統(tǒng)要求,采用不同的結(jié)構(gòu)來(lái)完成相應(yīng)的功能,大大提高系統(tǒng)的適用性及可擴(kuò)展性。因此,F(xiàn)PGA 逐漸成為實(shí)現(xiàn)DDC 的首選。

1 寬帶短波信道模擬器設(shè)計(jì)

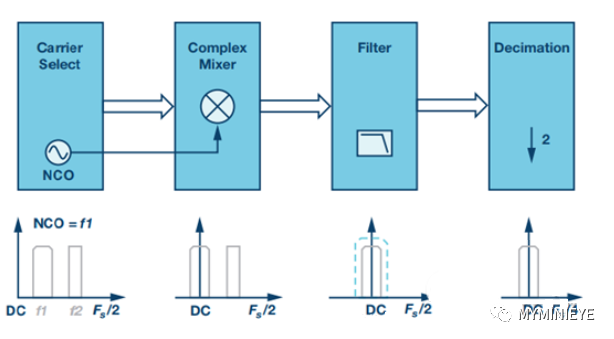

寬帶短波信道模擬器的輸入為短波調(diào)制信號(hào)( 3~ 30 MHz) ,首先經(jīng)過(guò)高速A/ D 直接進(jìn)行采樣,將模擬的調(diào)制信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),然后再通過(guò)數(shù)字下變頻技術(shù)分離出I、Q 兩路數(shù)字基帶信號(hào),以便于后續(xù)的數(shù)字信號(hào)處理。信號(hào)處理中通過(guò)顯示控制設(shè)備對(duì)信道參數(shù)進(jìn)行設(shè)置和輸出。最后處理好的信號(hào)再經(jīng)過(guò)D/ A 轉(zhuǎn)換后,通過(guò)低通濾波器、放大器和程控衰減等設(shè)備輸出最終所需的模擬信號(hào)。這樣就大大降低了ADC 和DSP 器件性能的要求,減輕了數(shù)字信號(hào)處理的負(fù)擔(dān),便于實(shí)現(xiàn)并有效降低成本。寬帶短波信道模擬器的體系結(jié)構(gòu)如圖1 所示。

?

圖1 寬帶短波信道模擬器的體系結(jié)構(gòu)圖

寬帶短波信道模擬器通過(guò)數(shù)字下變頻降低采樣數(shù)據(jù)率,減輕后續(xù)信號(hào)處理的壓力。數(shù)字下變頻在模擬器中起到前端ADC 和后端DSP 器件之間的橋梁作用。在數(shù)字下變頻部分中可以方便地對(duì)接收信號(hào)頻段和濾波器特性等進(jìn)行編程控制,極大地提高了寬帶短波信道模擬器的性能和靈活性,對(duì)于系統(tǒng)的升級(jí)或是兼容,都非常方便。

2 基于FPGA 的數(shù)字下變頻實(shí)現(xiàn)方案

寬帶短波調(diào)制信號(hào)的輸入頻率為3~ 30 MHz,根據(jù)帶通采樣理論,在工程實(shí)現(xiàn)上,信號(hào)采樣速率一般為模擬信號(hào)帶寬的2. 5 倍左右,考慮到在器件滿足要求的前提下可以盡量提高采樣頻率,選用了64 MHz 作為ADC 的采樣頻率。經(jīng)過(guò)數(shù)字下變頻的32 倍變頻,最終輸出到DSP 的信號(hào)帶寬為2 MHz。

該文中的DDC 實(shí)現(xiàn)不采用Altera 公司所提供的IP核,這樣可以降低成本,減少對(duì)國(guó)外技術(shù)依賴。

FPGA 器件采用cyclone III 器件,它是Altera 公司新一代采用SRAM 工藝低成本的FPGA,該系列器件的特點(diǎn)是低成本、低功耗和高性能。具有嵌入式乘法器,實(shí)現(xiàn)專門的乘法和乘加運(yùn)算,還可實(shí)現(xiàn)有限脈沖響應(yīng)( FIR) 濾波器; 最多有20 個(gè)全局時(shí)鐘,支持動(dòng)態(tài)時(shí)鐘管理以降低用戶模式時(shí)的功耗; 并且有4個(gè)鎖相環(huán)( PLL) 。根據(jù)該設(shè)計(jì)的數(shù)據(jù)處理要求,估算處理所需的資源,以及引腳封裝有利于制板的原則,選用EP3C40Q240C8N 型FPGA,并在開發(fā)工具Quartus II 上對(duì)信號(hào)發(fā)生器的設(shè)計(jì)、綜合及仿真。

NCO 是決定DDC 性能的主要因素之一。NCO的目標(biāo)是產(chǎn)生頻率可變的正交正、余弦樣本信號(hào)。

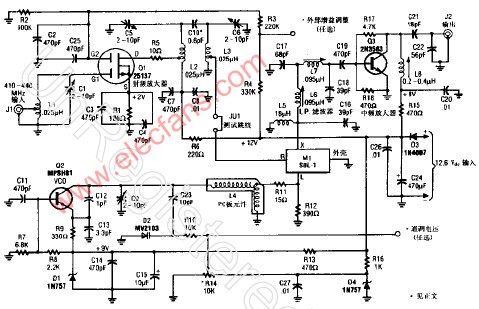

NCO 采用直接數(shù)字合成( DDS) 的方法實(shí)現(xiàn),目前常見的技術(shù)有查表法和CORDIC 計(jì)算法,在軟件無(wú)線電超高速的信號(hào)采樣頻率的情況下,NCO 實(shí)時(shí)的計(jì)算方法是很難實(shí)現(xiàn)的。此時(shí),NCO 產(chǎn)生的正弦樣本最有效和最簡(jiǎn)單的方法就是查表法,即事先根據(jù)各個(gè)NCO 正弦波相位計(jì)算好相位的正弦值,并按相位角度作為地址存儲(chǔ)該相位的正弦值數(shù)據(jù),其原理圖如圖2 所示。

?

圖2 基于查表法的NCO 原理圖

圖2 中,32 位累加器由一個(gè)32 位的加法器和一個(gè)32 位寄存器組成,在時(shí)鐘的作用下,加法器通過(guò)寄存器將輸出數(shù)據(jù)送入到加法器的一個(gè)輸入端,與32 位的頻率控制字進(jìn)行相加運(yùn)算,得到一個(gè)有規(guī)律的相位累加結(jié)果。查找表實(shí)際上是一個(gè)存儲(chǔ)了正弦信號(hào)抽樣點(diǎn)幅度編碼的只讀存儲(chǔ)器ROM,但ROM表的大小會(huì)隨地址位數(shù)的增加成指數(shù)遞增關(guān)系,因此,為了不減少查找表的地址位數(shù)而滿足信號(hào)性能,必須采用優(yōu)化方法來(lái)減小ROM 表的大小。根據(jù)正弦波的對(duì)稱特性,只需存儲(chǔ)四分之一周期的幅值,再通過(guò)相應(yīng)的轉(zhuǎn)換即可恢復(fù)出整個(gè)周期的幅值。同時(shí),由于余弦波和正弦波相位差為??/ 2,可以很容易地實(shí)現(xiàn)余弦信號(hào)。

完成DDC 的NCO 模塊設(shè)計(jì)后,將需要下變頻的輸入信號(hào)與NCO 產(chǎn)生的2 路正交本振信號(hào)進(jìn)行相乘,完成數(shù)字混頻正交變換,即完成頻譜搬移。

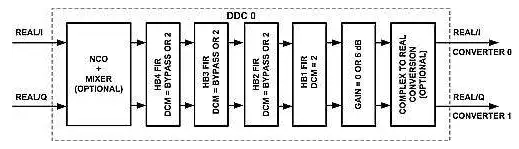

2. 2 CIC 濾波器設(shè)計(jì)

CIC 積分梳狀濾波器是實(shí)現(xiàn)高速抽取非常有效的單元。CIC 濾波器的單位沖激響應(yīng)為:

?

?

?

從式( 2) 可以看出CIC 濾波器由2 部分組成,即積分器和梳狀器級(jí)聯(lián)組成,其實(shí)現(xiàn)非常簡(jiǎn)單,只有加減運(yùn)算,沒有乘法運(yùn)算,F(xiàn)PGA 實(shí)現(xiàn)時(shí)可達(dá)到很高的處理速率。但是,單級(jí)CIC 濾波器的旁瓣電平只比主瓣低13. 46 dB,這就意味著阻帶衰減很差,一般是難以滿足實(shí)用要求的。為了降低旁瓣電平,可以采取多級(jí)CIC 濾波器級(jí)聯(lián)的辦法解決。

N 級(jí)CIC 濾波器級(jí)聯(lián)的帶內(nèi)容差是單級(jí)CIC 濾波器帶內(nèi)容差的N 倍,這意味著多級(jí)CIC 濾波器級(jí)聯(lián)增大阻帶衰減的同時(shí)也增大了帶內(nèi)容差。所以,CIC 濾波器的級(jí)聯(lián)數(shù)是有限的不宜超過(guò)5 級(jí)。

該設(shè)計(jì)中,CIC 濾波器需要完成16 倍的抽取,采用5 級(jí)級(jí)聯(lián)來(lái)實(shí)現(xiàn),輸入和輸出部分的位寬均為12 bit,在MATLAB 仿真的結(jié)果如圖3 所示。

?

圖3 CIC 濾波器幅度特性

經(jīng)過(guò)CIC 濾波器后,信號(hào)采樣速率經(jīng)過(guò)16 倍抽取后變?yōu)? MHz,從而實(shí)現(xiàn)了抽取功能,同時(shí)也降低了采樣速率。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論