?

本文針對藍牙系統,設計時考慮寄生電感的影響,采用TSMC 0.18μm CMOS工藝設計出了一個差分E類功率放大器,有效地抑制了寄生電感對系統性能的影響,同時給出了設計方法和設計過程。

CMOS工藝指互補金屬氧化物(PMOS管和NMOS管)共同構成的互補型MOS集成電路制造工藝,它的特點是低功耗。由于CMOS中一對MOS組成的門電路在瞬間看,要么PMOS導通,要么NMOS導通,要么都截至,比線性的三極管(BJT)效率要高得多,因此功耗很低。

在計算機領域,CMOS常指保存計算機基本啟動信息(如日期、時間、啟動設置等)的芯片。有時人們會把CMOS和BIOS混稱,其實CMOS是主板上的一塊可讀寫的RAM芯片,是用來保存BIOS的硬件配置和用戶對某些參數的設定。CMOS可由主板的電池供電,即使系統掉電,信息也不會丟失。CMOS RAM本身只是一塊存儲器,只有數據保存功能。而對BIOS中各項參數的設定要通過專門的程序。BIOS設置程序一般都被廠商整合在芯片中,在開機時通過特定的按鍵就可進入BIOS設置程序,方便地對系統進行設置。因此BIOS設置有時也被叫做CMOS設置。

1 理想射頻E類功放工作原理及設計方程

晶體管E類功率放大器由單個晶體管和負載網絡等組成。在激勵信號作用下,晶體管工作在開關狀態。當晶體管飽和導通時,漏端電壓波形由晶體管決定,即由晶體管的導通電阻決定。當晶體管截至時,漏端電壓波形由負載網絡的瞬態響應所決定。

E類功率放大器要保持高效率,其負載網絡的瞬態響應必須滿足以下3個條件:(1)晶體管截至時,漏端電壓必須延遲到晶體管"開關"斷開后才開始上升。(2)晶體管導通時,漏端電壓必須為零。(3)晶體管飽和導通時,漏端電壓對時間的導數必須為零。

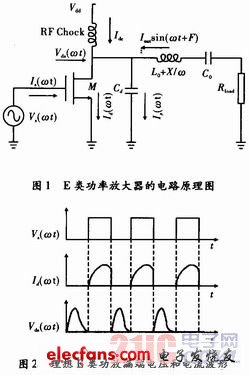

根據上述3點,具體分析E類功率放大器工作原理及其電路參數的計算。圖l為E類功率放大器的電路原理圖,其中Cd為MOS管寄生電容與片上電容的和,L1 為高頻扼流圈。L0,C0為串聯諧振網絡,Rload為等效負載。當晶體管飽和導通時,漏端電壓為零,由于負載網絡的影響,電流Ld(ωt)有一個上升和下降的過程。當晶體管截至時,漏端電壓則完全由負載網絡所決定。圖2所示為理想E類功放漏端電壓和電流時域波形,由圖可知所以Id(ωt)與 Vds(ωt)不同時出現,使放大器效率趨近于100%,該效率主要由負載網絡參數最佳設計來實現的。

?

由文獻可求得圖1所示電路中各個元件的值,即

?

2 射頻CMOS E類功率放大器非理想因素分析

分析了理想功放的設計方程,有載QL的選擇,負載網絡元器件的選取等,但是這些理論基礎都建立在理想情況下,而在實際設計中,必須考慮非理想的因素。非理想因素有多種:

(1)寄生電感的影響。

(2)有限的Chock電感。

(3)NMOS開關管有限的導通電阻。

(4)NMOS管寄生電容Cd的非線性。

(5)負載網絡的有限Q值。

(6)功率放大器阻抗匹配網絡的損耗。

其中寄生電感對功放的設計結果影響最大,因此將著重分析寄生電感的產生及其改進措施。

寄生電感分析與改進措施

功率放大器在實際應用中有3個主要的寄生源,分別為RF電路板、封裝和IC.具體表現在輸出級源級到地的寄生電感,它對功率放大器的輸出功率、PAE、穩定性等產生巨大的影響。寄生電感可以分為以下3個方面:

(1)在IC級,功率放大器一般用通孔結構或者鍵合線聯接到襯底地。在實際應用中,可使用多線鍵合減小地電感。

(2)在封裝級,通常用接到封裝底部的接地片,或通過封裝引線架的地連接實現接地。可用各種方法調整引線架,以減小地電感。

(3)在RF電路板級的地連接一般用通孔接到電路板中間層的專門接地平板。接地的質量由物理特性和與系統地的連接好壞確定。

接電源(地)的封裝線對電路的影響與高速電路中同步開關噪聲原理相似。交流電流在封裝線上引起的感應電勢為

?

其中,Le為電源和地封裝線的總等效電感。假設當Le=1 nH,交流電流幅度i為300 mA時,即可達300 mV,如果電感和寄生電容發生諧振,振蕩信號的幅度會更高,必然會對輸出信號形成干擾。電源(地)封裝線對電路的另一影響是信號或其諧波可能引起振蕩,這些影響是很難通過在電源和地之間接并聯大耦合電容得到抑制的。因此采用合理的電路結構才能減輕寄生電感對系統的影響。

3 射頻CMOS E類功率放大器設計

功率放大器的輸出級是電路最關鍵、最復雜的部分,因為它的輸出是芯片射頻接口,除了器件的非線性特性外,還必須要考慮Pad、輸出功率管漏端到地的寄生電感、封裝結構、輸出電壓擺幅、MOS器件擊穿和輸出端口的阻抗匹配等多種因素的影響。在這些因素中,輸出功率管漏端到地的寄生電感對功放性能影響最嚴重,包括鍵合線電感、PCB板級電路寄生電感等的影響。

3.1 應用理想方程的功放級設計

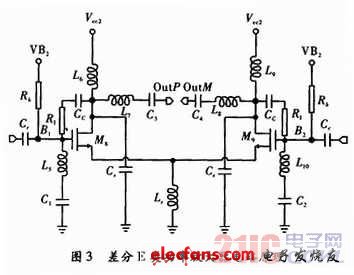

功放內核電路如圖3所示,采用偽差分E類功率放大器,為簡化分析過程,分析右半邊電路圖,L5為片上平面螺旋電感,L6,L7,Ls為鍵合線電感。輸出級為E類功放,Choke電感L6阻止交流信號通過,并給晶體管提供直流電流Idc.反饋網絡Cs和Rs增強功率放大器的穩定性和降低輸出電壓駐波比。 L7、C3組成一個串聯LC網絡,包括一個諧振網絡和部分剩余電感,當該諧振網絡的品質因子足夠高時,流過該網絡的電流為理想的正弦型信號,所有的諧波成分都被濾除。并聯電容Cs由兩部分組成,一部分是晶體管的寄生電容,另一部分是實際引入的電容。

?

在設計之初,先利用理想設計方程,估算E類功率放大器的各個參數,再采用諧波平衡法(HarmONic Balance)適當地調整參數。其中Pout=24 dBm,電源電壓VDD=1.8 V,取Qt=5,根據之前給出的設計方程得出

?

以上參數選取依賴于理想設計方程參數,只考慮到最佳負載為實部的情況,考慮到一些非理想因素,利用ADS軟件,采用Load Pull技術適當地調整參數。

3.2 應用Load Pull技術的功放級設計

在功放級設計中,如何使輸出功率最大化是最主要的設計目標。

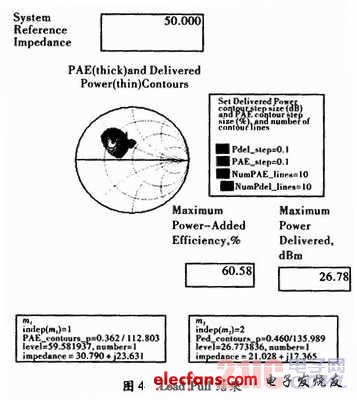

基本思路是通過CAD技術進行Load Pull仿真確定最佳的源和負載阻抗。所謂的Load Pull仿真,就是在負載阻抗很大范圍內掃描,逐點作諧波平衡分析計算出輸出功率,在圓圖上畫出等功率圓。因此根據設計目標的輸出功率,就能在圓圖上找到與之對應的一系列的輸出阻抗。

CAD即計算機輔助設計(CAD-Computer Aided Design) 利用計算機及其圖形設備幫助設計人員進行設計工作 .簡稱cad. 在工程和產品設計中,計算機可以幫助設計人員擔負計算、信息存儲和制圖等項工作。CAD還包含:電氣CAD、外貿結算CAD、加拿大元、冠狀動脈性心臟病、計算機輔助診斷、服裝CAD等含義。

計算機輔助設計指利用計算機及其圖形設備幫助設計人員進行設計工作,簡稱CAD. 在工程和產品設計中,計算機可以幫助設計人員擔負計算、信息存儲和制圖等項工作。在設計中通常要用計算機對不同方案進行大量的計算、分析和比較,以決定最優方案;各種設計信息,不論是數字的、文字的或圖形的,都能存放在計算機的內存或外存里,并能快速地檢索;設計人員通常用草圖開始設計,將草圖變為工作圖的繁重工作可以交給計算機完成;由計算機自動產生的設計結果,可以快速作出圖形顯示出來,使設計人員及時對設計作出判斷和修改;利用計算機可以進行與圖形的編輯、放大、縮小、平移和旋轉等有關的圖形數據加工工作。

4 仿真結果與分析

根據負載牽引仿真結果得到負載的最佳阻抗值,下面就是采用適當的匹配形式(集總參數或分布參數)實現輸出匹配網絡,并將該輸出匹配網絡加入到電路中進行源負載牽引仿真,以便得到源的最佳輸入阻抗。

這樣通過兩次負載牽引得到最佳輸入輸出阻抗,并選擇適當的匹配電路將50 Ω變化到所需的阻抗。圖4結果表明,將負載匹配到31+j24時,該結構具有最大輸出功率26.78 dBm,最大PAE為60.56%.采用L型匹配網絡實現輸入、輸出阻抗的匹配。

?

表1的Load Pull結果是有一定條件完成的,其前級驅動信號并不是理想的開關信號,而是輸入信號為O dBm,經過Cascode驅動級放大后的信號。利用理想設計方程得到的結果比較差的原因是,得出理想方程的假設條件和實際應用條件不一樣,具體有:

(1)驅動信號并不是理想的具有足夠驅動能力的占空比為50%的方波信號。

(2)仿真時在輸出級功率管的源端加入了1.5 nH的寄生電感。

(3)RFC電感并不是無窮大。

(4)輸出級功率管的導通電阻并不為O,需要一定的導通時間。

(5)負載諧振網絡Q值也是有限的。

?

5 結束語

分析比較了CMOS工藝和GaAs工藝的優缺點,以及設計過程中所要考慮的非理想因素,著重分析寄生電感的產生,對功放性能的影響,以及如何抑制寄生電感對功放的影響。最終采用理想設計方程和Load Pull技術,基于0.18μm CMOS工藝實現了一個差分的E類功放,ADS仿真結果表明采用差分結構較好地抑制了漏端電感對功率放大器性能的影響,提高功放的PAE,為實現單片集成發射機奠定了基礎。

電子發燒友App

電子發燒友App

評論