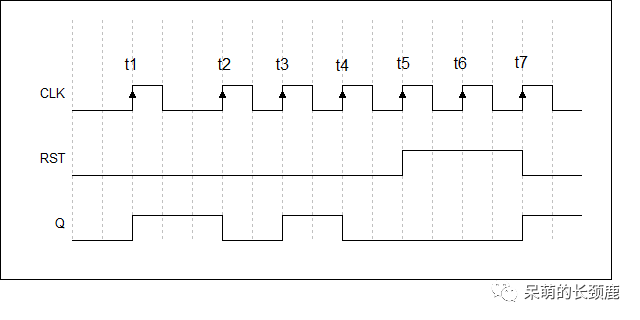

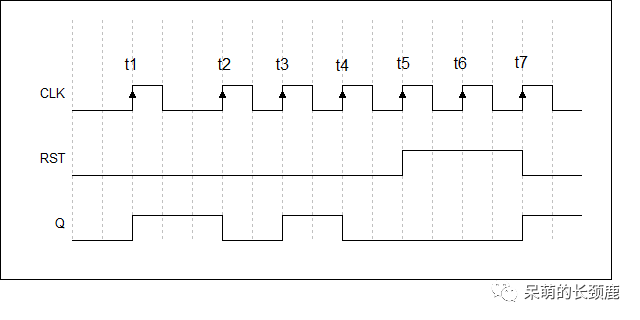

T觸發(fā)器(Toggle Flip-Flop)Toggle是一個(gè)邊緣觸發(fā)的切換觸發(fā)器,輸出Q在輸入CLK的每個(gè)上升沿時(shí)發(fā)生變化,在輸入CLK的上升沿時(shí)翻轉(zhuǎn)輸出Q。輸入RST為1時(shí)輸出Q輸出值為0且保持不變。

2023-12-04 15:20:15 1524

1524

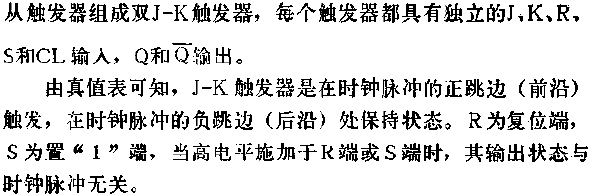

,呵呵。。。上半年,由于Boss項(xiàng)目,學(xué)習(xí)了FPGA,學(xué)的有點(diǎn)急,也斷斷續(xù)續(xù)的,才過(guò)幾個(gè)月,似乎知識(shí)已經(jīng)遠(yuǎn)去,打開電腦,速覽以前的資料,記憶又回來(lái)了。。。簡(jiǎn)單記錄下這道題,權(quán)當(dāng)回憶。。。//基本D觸發(fā)器

2012-02-22 13:54:40

D觸發(fā)器中PRN、CLRN區(qū)別在Quartus II當(dāng)中查看RTL視圖會(huì)有PRN和CLRN(CLR)兩個(gè)引腳的區(qū)別PRN是異步置位,可以將輸出Q置為輸入D(輸出Q立馬變成輸入D)CLRN(CLR)是異步復(fù)位,將輸出Q置地。

2022-01-11 06:43:53

本帖最后由 gk320830 于 2015-3-7 11:16 編輯

Ti的

D觸發(fā)器SN74LVC2G74,想做一個(gè)按鍵開關(guān)機(jī)電路,即二分頻電路,但是調(diào)試過(guò)程中老是有問(wèn)題,請(qǐng)大家?guī)兔Ψ治龇治?/div>

2013-10-30 15:44:27

D觸發(fā)器實(shí)現(xiàn)二分頻電路(D觸發(fā)器構(gòu)成的2分頻電路)

2020-03-02 11:05:49

做了一個(gè)仿真:key_in作為D觸發(fā)器的輸入,led_out作為觸發(fā)器輸出,時(shí)鐘周期20ns,key_in每10ns隨機(jī)變化一次,這樣的設(shè)置下,key_in信號(hào)的變化沿有時(shí)會(huì)和時(shí)鐘上升沿重合,根據(jù)

2022-01-25 22:41:02

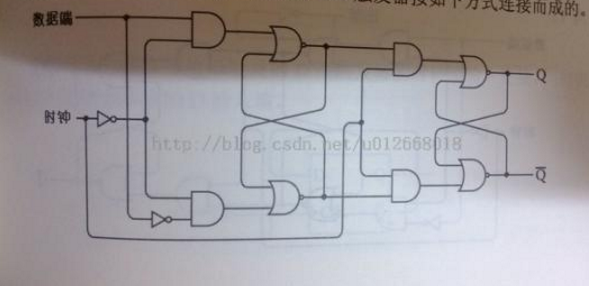

`如圖所示,圖中第一個(gè)觸發(fā)器D接第二個(gè)觸發(fā)器的非Q端,這個(gè)時(shí)序圖,整不明白啊,我的看法是:當(dāng)?shù)谝粋€(gè)時(shí)鐘信號(hào)高電平來(lái)的時(shí)候,第一個(gè)觸發(fā)器的輸出狀態(tài)Q是不能判斷的啊,因?yàn)?b class="flag-6" style="color: red">D接在第二個(gè)觸發(fā)器的非Q端。求大佬指點(diǎn)一下 這個(gè)圖,是如何工作的?`

2019-01-16 11:50:35

有什么辦法降低施密特觸發(fā)器輸出的方波幅值嗎除了降低施密特觸發(fā)器VCC的大小

2016-05-06 14:58:47

D觸發(fā)器都是邊沿觸發(fā)器么,有人幫忙解釋一下么,謝謝了!!!

2016-05-03 20:24:57

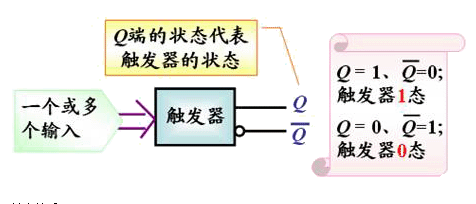

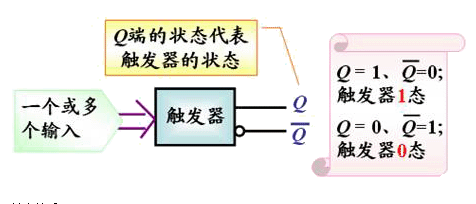

不變。所以,觸發(fā)器可以記憶1位二值信號(hào)。根據(jù)邏輯功能的不同,觸發(fā)器可以分為RS觸發(fā)器、D觸發(fā)器、JK觸發(fā)器、T和T′觸發(fā)器;按照結(jié)構(gòu)形式的不同,又可分為基本RS觸發(fā)器、同步觸發(fā)器、主從觸發(fā)器和邊沿觸發(fā)器。

2009-09-16 16:06:45

一、實(shí)驗(yàn)的目的1、掌握觸發(fā)器功能的測(cè)試方法。2、掌握基本RS觸發(fā)器的組成及工作原理。3、掌握集成JK觸發(fā)器和D觸發(fā)器的邏輯功能及觸發(fā)方式。4、掌握幾種主要觸發(fā)器之間相互

2009-10-10 11:32:55

觸發(fā)器實(shí)驗(yàn)1)熟悉常用觸發(fā)器的邏輯功能及測(cè)試方法。2)了解觸發(fā)器邏輯功能的轉(zhuǎn)換。三.實(shí)驗(yàn)內(nèi)容及步驟 (1) 基本RS觸發(fā)器邏輯功能測(cè)試(2) JK觸發(fā)器邏輯功能測(cè)試(3) D觸發(fā)器邏輯功能的測(cè)試

2009-03-20 10:01:05

按邏輯功能不同分為:RS觸發(fā)器、D觸發(fā)器、JK觸發(fā)器、T觸發(fā)器。按觸發(fā)方式不同分為:電平觸發(fā)器、邊沿觸發(fā)器和主從觸發(fā)器。按電路結(jié)構(gòu)不同分為:基本RS觸發(fā)器和鐘控觸發(fā)器。按存儲(chǔ)數(shù)據(jù)原理不同分為:靜態(tài)

2012-06-18 11:42:43

觸發(fā)器輸入電路二極管D的作用是只把負(fù)的尖脈沖輸入觸發(fā)器,還可用來(lái)組成加速電路。

2009-09-22 08:28:30

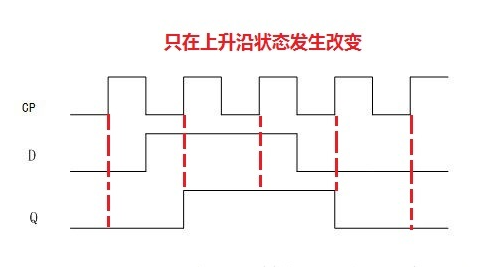

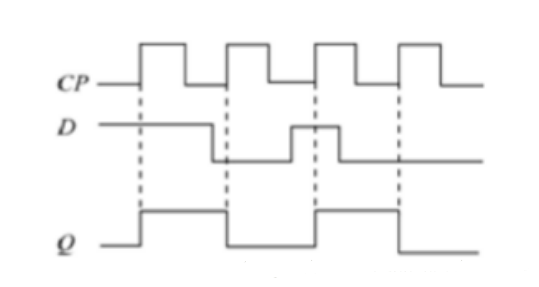

在學(xué)習(xí)verilog之前,我們先學(xué)習(xí)一下D觸發(fā)器以及它的代碼。FPGA的設(shè)計(jì)基礎(chǔ)是數(shù)字電路,因此很多同學(xué)會(huì)認(rèn)為我們要先學(xué)好數(shù)字電路之后,才學(xué)習(xí)FPGA。但是,數(shù)字電路教材的內(nèi)容很多.例如:JK觸發(fā)器

2018-09-20 15:09:45

如圖, 將j-k觸發(fā)器用D觸發(fā)器代替,剛?cè)腴T 求教

2014-01-09 20:56:31

JK觸發(fā)器和D觸發(fā)器所使用的時(shí)鐘脈沖能否用邏輯電平開關(guān)提供?為什么?

2023-05-10 11:38:04

誰(shuí)能告訴我PRUTEUS 中D觸發(fā)器在哪?怎么找啊?

2013-01-16 09:23:05

jk觸發(fā)器是什么原理jk觸發(fā)器特性表和狀態(tài)轉(zhuǎn)換圖

2021-02-26 08:18:24

jk觸發(fā)器設(shè)計(jì)d觸發(fā)器,根據(jù)原理圖實(shí)現(xiàn)模8加1計(jì)數(shù)器,來(lái)源于西電慕課貌似這個(gè)軟件只有5.0和5.12兩個(gè)版本。在win10下拖曳器件會(huì)發(fā)生殘影的現(xiàn)象,而且無(wú)法修改連線。雖然有自動(dòng)連線功能但感覺(jué)線連

2021-07-22 08:39:47

求助誰(shuí)能教設(shè)計(jì)一個(gè)D觸發(fā)器

2014-12-24 22:54:35

在學(xué)習(xí)verilog之前,我們先學(xué)習(xí)一下D觸發(fā)器以及它的代碼。FPGA的設(shè)計(jì)基礎(chǔ)是數(shù)字電路,因此很多同學(xué)會(huì)認(rèn)為我們要先學(xué)好數(shù)字電路之后,才學(xué)習(xí)FPGA。但是,數(shù)字電路教材的內(nèi)容很多.例如:JK觸發(fā)器

2017-06-20 09:56:47

2020.3.26_學(xué)習(xí)筆記兩個(gè)D觸發(fā)器? 最近發(fā)現(xiàn)一個(gè)問(wèn)題,代碼中會(huì)特地的新建一個(gè)D觸發(fā)器用來(lái)鎖存信號(hào),讓很多人都比較疑惑,明明一個(gè)D觸發(fā)器就可以檢測(cè)輸入是上升沿和下降沿。?兩個(gè)觸發(fā)器的目的主要

2021-07-30 06:44:48

兩個(gè)非門電路是如何組成一個(gè)D觸發(fā)器的?即可通俗說(shuō)明下D觸發(fā)器嗎?

2023-05-10 10:32:03

”,分別稱為置“1”端和置“0”端。常見(jiàn)的觸發(fā)器有R-S觸發(fā)器、D觸發(fā)器和J-K觸發(fā)器等三種,下面簡(jiǎn)單說(shuō)明它們的工作原理。類型種類按邏輯功能不同分為:RS觸發(fā)器、D觸發(fā)器、JK觸發(fā)器、T觸發(fā)器。按觸發(fā)

2019-12-25 17:09:20

單路D型觸發(fā)器有何功能呢?有哪些引腳?如何利用單路D型觸發(fā)器去設(shè)計(jì)一種自鎖開關(guān)?

2022-02-28 08:06:24

做個(gè)單穩(wěn)態(tài)電路、后端做個(gè)雙穩(wěn)態(tài)電路,按下并松開一次按鍵實(shí)現(xiàn)輸出狀態(tài)翻轉(zhuǎn)一次。現(xiàn)在有個(gè)問(wèn)題:按下去馬上松開按鍵,很正常;但假如按下去的時(shí)間比較長(zhǎng),超過(guò)單穩(wěn)態(tài)電路中,電容積分復(fù)位第一個(gè)D觸發(fā)器的時(shí)間,在松開

2014-09-25 16:47:34

觸發(fā)器沒(méi)有使用相同的時(shí)鐘信號(hào),需要分析哪些觸發(fā)器時(shí)鐘有效哪些無(wú)效分析步驟和同步時(shí)序電路一樣,不過(guò)要加上時(shí)鐘信號(hào)有關(guān)D觸發(fā)器的例題抄自慕課上的一個(gè)題目,注意第二個(gè)觸發(fā)器反相輸出端同時(shí)連接到復(fù)位端JK

2021-09-06 08:20:26

存器,延遲觸發(fā)器,D型雙穩(wěn)態(tài),D型觸發(fā)器,或者簡(jiǎn)稱為D觸發(fā)器,通常稱為D觸發(fā)器。的d觸發(fā)器是迄今最重要的時(shí)鐘控制的觸發(fā)器,因?yàn)樗_保確保輸入S和R從未等于一在同一時(shí)間。D型觸發(fā)器由門控SR觸發(fā)器構(gòu)成

2021-02-03 08:00:00

新課第五章 觸發(fā)器5.1 概述1、觸發(fā)器具有“記憶”功能,它是構(gòu)成時(shí)序邏輯電路的基本單元。本章首先介紹基本RS觸發(fā)器的組成原理、特點(diǎn)和邏輯功能。然后引出能夠防止“空翻”現(xiàn)象的主從觸發(fā)器和邊沿觸發(fā)器。同時(shí),較詳細(xì)地討論RS觸發(fā)器、JK觸發(fā)器、D觸發(fā)器、T觸發(fā)器、T'觸發(fā)器的邏輯功能及其描述方法。

2009-04-02 11:58:41

本帖最后由 鄭青松001 于 2013-12-17 12:21 編輯

外部出入信號(hào)D觸發(fā)器濾波 對(duì)于外部輸出的信號(hào),特別是按鍵類的比如旋轉(zhuǎn)編碼器等,在外部手動(dòng)旋轉(zhuǎn)的時(shí)候會(huì)輸出的信號(hào)抖動(dòng)很大

2013-12-17 12:19:46

如何用D觸發(fā)器實(shí)現(xiàn)2分頻 原理在線等

2016-07-03 19:37:58

本帖最后由 gk320830 于 2015-3-5 20:47 編輯

如何用JK觸發(fā)器構(gòu)成D觸發(fā)器 電路圖來(lái)人給個(gè)圖吧..

2011-11-14 15:21:03

單片機(jī)內(nèi)部有大量寄存器, 寄存器是一種能夠存儲(chǔ)數(shù)據(jù)的電路, 由觸發(fā)器構(gòu)成。1.觸發(fā)器觸發(fā)器是一種具有記憶存儲(chǔ)功能的電路, 由門電路組成。 常見(jiàn)的觸發(fā)器包括: RS 觸發(fā)器、 D 觸發(fā)器和 JK觸發(fā)器

2022-01-20 07:13:51

怎樣去設(shè)計(jì)一種基于門電路的D觸發(fā)器呢?如何對(duì)基于門電路的D觸發(fā)器進(jìn)行仿真?

2021-09-14 06:21:42

怎樣去創(chuàng)建一個(gè)16路D觸發(fā)器?怎樣通過(guò)ena使能端去控制16路D觸發(fā)器呢?

2021-09-15 06:53:13

新建兩個(gè)D觸發(fā)器的目的是什么?何謂亞穩(wěn)態(tài)?解決亞穩(wěn)態(tài)的方法是什么?

2021-11-09 07:15:01

習(xí)時(shí)把這一章分為兩節(jié),它們分別是:§5、1 時(shí)序電路的概述§5、2 觸發(fā)器 5、1 時(shí)序電路的概述 這一節(jié)我們來(lái)學(xué)習(xí)一些關(guān)于時(shí)序電路的概念,在學(xué)習(xí)時(shí)要注意同步時(shí)序電路和異步時(shí)序電路的區(qū)別一:時(shí)序電路

2018-08-23 10:36:20

在學(xué)習(xí)verilog之前,我們先學(xué)習(xí)一下D觸發(fā)器以及它的代碼。FPGA的設(shè)計(jì)基礎(chǔ)是數(shù)字電路,因此很多同學(xué)會(huì)認(rèn)為我們要先學(xué)好數(shù)字電路之后,才學(xué)習(xí)FPGA。但是,數(shù)字電路教材的內(nèi)容很多.例如:JK觸發(fā)器

2019-01-17 17:24:19

Jack Kilby)和D(延遲)。典型的觸發(fā)器包括零個(gè)、一個(gè)或兩個(gè)輸入信號(hào),以及時(shí)鐘信號(hào)和輸出信號(hào)。一些觸發(fā)器還包括一個(gè)重置當(dāng)前輸出的明確輸入信號(hào)。第一個(gè)電子觸發(fā)器是在1919年由

2019-06-20 04:20:50

電后,與非門的1腳為低電平,故U1A輸出端第3腳為高電平,3腳與與非門的12腳相連,故12腳也為高電平。 2、電路剛上電時(shí),D觸發(fā)器的RD引腳通過(guò)電容C1,電阻R2上電復(fù)位,使D觸發(fā)器的輸出Q=D

2023-03-20 15:33:48

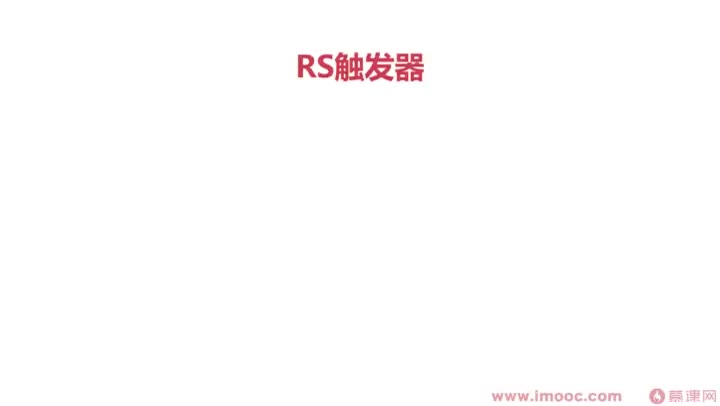

概述:CD4013是一款由兩個(gè)相同的、相互獨(dú)立的數(shù)據(jù)型觸發(fā)器構(gòu)成的置/復(fù)位雙D型觸發(fā)器。每個(gè)觸發(fā)器有獨(dú)立的數(shù)據(jù)、置位、復(fù)位、時(shí)鐘輸入和Q及Q輸出,此器件可用作移位寄存器,且通過(guò)將Q輸出連接到數(shù)據(jù)輸入,可用作計(jì)算...

2021-04-08 06:08:10

D觸發(fā)器結(jié)構(gòu)的五分頻器邏輯電路

2019-09-11 11:29:19

怎樣去設(shè)計(jì)一個(gè)基于數(shù)字電路的D觸發(fā)器?如何對(duì)基于數(shù)字電路的D觸發(fā)器進(jìn)行仿真?

2021-09-16 06:45:31

電平觸發(fā)的D觸發(fā)器型號(hào)有哪些?大部分都是邊沿觸發(fā)的,現(xiàn)在要用到電平觸發(fā)器,不知道具體型號(hào)沒(méi)法買到

2019-02-28 14:32:13

電平觸發(fā)器和邊沿觸發(fā)器符號(hào)

2019-10-18 09:01:09

了看觸發(fā)器這部分,隨便寫寫,當(dāng)做筆記好了,也希望各位大神給小弟糾糾錯(cuò),第一次學(xué)數(shù)電,還蠻好玩~太書面化的話我就不說(shuō)了啊,有些東西就像書上寫的,真的看著看著就想睡覺(jué)了,還是大白話直白哈。 1、關(guān)于觸發(fā)器

2015-04-07 17:47:42

5.1 基本RS觸發(fā)器5.2 時(shí)鐘控制的觸發(fā)器5.3 集成觸發(fā)器5.4 觸發(fā)器的邏輯符號(hào)及時(shí)序圖

2010-08-10 11:53:23 0

0 1、掌握鎖存器、觸發(fā)器的電路結(jié)構(gòu)和工作原理;

2、熟練掌握SR觸發(fā)器、JK觸發(fā)器、D觸發(fā)器及T 觸發(fā)器的邏輯功能;

3、正確理解鎖存器、觸發(fā)器的動(dòng)態(tài)特性

2010-08-18 16:39:35 0

0 D觸發(fā)器真值表分析:

1. D 觸發(fā)器真值表

Dn

2007-09-11 23:15:20 18427

18427 D觸發(fā)器

同步式D觸發(fā)器邏輯電路圖

D觸發(fā)器功能

2008-10-20 09:57:54 2222

2222

JK觸發(fā)器,JK觸發(fā)器是什么意思

1.主從JK觸發(fā)器主從結(jié)構(gòu)觸發(fā)器也可以徹底解決直接控制,防止空翻。這里以性能優(yōu)良、廣泛使用的主從JK觸發(fā)器為

2010-03-08 13:36:29 6142

6142 D觸發(fā)器,D觸發(fā)器是什么意思

邊沿D 觸發(fā)器: 電平觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP 高

2010-03-08 13:53:13 4395

4395 施密特觸發(fā)器,施密特觸發(fā)器是什么意思

施密特觸發(fā)器也有兩個(gè)穩(wěn)定狀態(tài),但與一般觸發(fā)器不同的是,施密特觸發(fā)器采用電位觸發(fā)

2010-03-08 14:14:56 1844

1844 觸發(fā)器的分類, 觸發(fā)器的電路

雙穩(wěn)態(tài)器件有兩類:一類是觸發(fā)器,一類是鎖存器。鎖存器是觸發(fā)器的原始形式。基本

2010-03-09 09:59:59 1554

1554 本次重點(diǎn)內(nèi)容:1、觸發(fā)器的概念和分類。2、同步觸發(fā)器、主從觸發(fā)器、邊沿觸發(fā)器的含義。

4.1.1 觸發(fā)器概述一、觸發(fā)

2010-08-19 08:57:47 19312

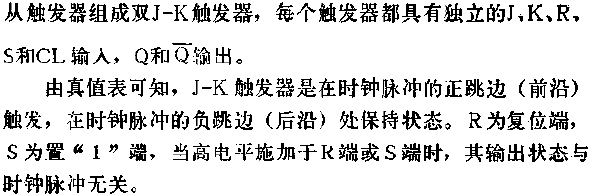

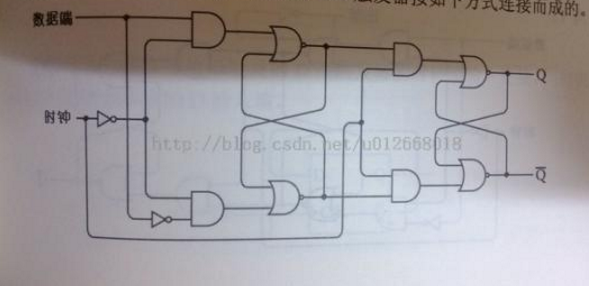

19312 J-K觸發(fā)器是一種多功能觸發(fā)器,它既具有R-S觸發(fā)器的功能,又具有D觸發(fā)器和T觸發(fā)器的功能,因此使用十分靈活

2010-09-24 00:12:06 1279

1279

圖中所示是用J-K觸發(fā)器組成的D觸發(fā)器電路。

從J-K觸發(fā)器的邏輯圖已知在D觸發(fā)器端增

2010-09-24 00:21:27 6900

6900

一份關(guān)于觸發(fā)器仿真的實(shí)驗(yàn)報(bào)告,有需要的可以自行觀看,千萬(wàn)別客氣。

2016-05-23 17:03:42 0

0 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料之常用觸發(fā)器

2016-09-02 14:30:26 0

0 JK觸發(fā)器是數(shù)字電路觸發(fā)器中的一種基本電路單元。JK觸發(fā)器具有置0、置1、保持和翻轉(zhuǎn)功能,在各類集成觸發(fā)器中,JK觸發(fā)器的功能最為齊全。在實(shí)際應(yīng)用中,它不僅有很強(qiáng)的通用性,而且能靈活地轉(zhuǎn)換其他類型的觸發(fā)器。由JK觸發(fā)器可以構(gòu)成D觸發(fā)器和T觸發(fā)器。

2017-12-25 17:30:03 178012

178012

邊沿觸發(fā)器,指的是接收時(shí)鐘脈沖CP 的某一約定跳變(正跳變或負(fù)跳變)來(lái)到時(shí)的輸入數(shù)據(jù)。在CP=l 及CP=0 期間以及CP非約定跳變到來(lái)時(shí),觸發(fā)器不接收數(shù)據(jù)的觸發(fā)器。具有下列特點(diǎn)的觸發(fā)器稱為邊沿觸發(fā)方式觸發(fā)器,簡(jiǎn)稱邊沿觸發(fā)器。

2018-01-31 09:02:33 69651

69651

觸發(fā)器分為電平觸發(fā)和邊沿觸發(fā)兩類。電平觸發(fā)的觸發(fā)器原理較簡(jiǎn)單,學(xué)習(xí)觸發(fā)器時(shí),一般先學(xué)習(xí)電平觸發(fā)。電平觸發(fā)的觸發(fā)器主要是基本RS觸發(fā)器基本RS觸發(fā)器由電平觸發(fā),并且有一個(gè)重要的約束條件:/SD和/RD不能同時(shí)為零。即:/SD+/RD=1。

2018-01-31 10:26:26 5830

5830

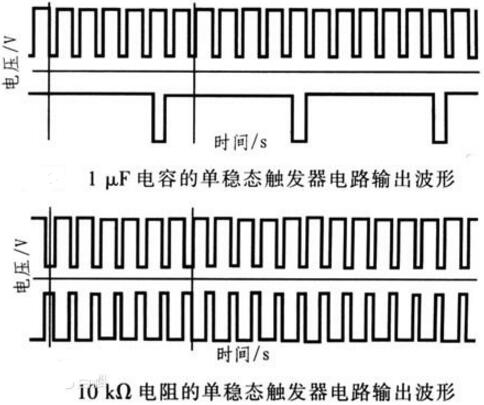

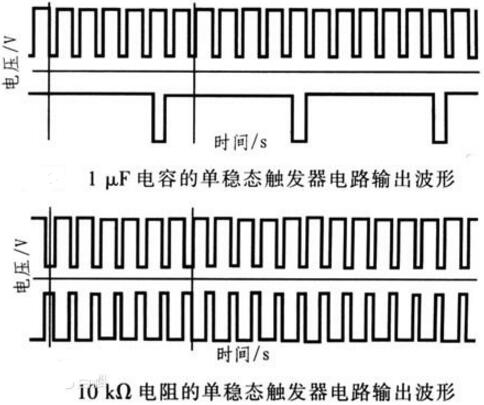

本文開始介紹了什么是單穩(wěn)態(tài)觸發(fā)器以及單穩(wěn)態(tài)觸發(fā)器的電路組成,其次闡述了單穩(wěn)態(tài)觸發(fā)器特點(diǎn)、門電路構(gòu)成的單穩(wěn)態(tài)觸發(fā)器、D觸發(fā)器構(gòu)成的單穩(wěn)態(tài)觸發(fā)器,最后詳細(xì)的闡述了時(shí)基電路構(gòu)成的單穩(wěn)態(tài)觸發(fā)器。

2018-03-27 09:24:23 71987

71987

本文開始介紹了單穩(wěn)態(tài)觸發(fā)器的概念,其次闡述了單穩(wěn)態(tài)觸發(fā)器工作特點(diǎn)和單穩(wěn)態(tài)觸發(fā)器的用途,最后介紹了單穩(wěn)態(tài)觸發(fā)器的應(yīng)用。

2018-03-27 10:16:25 30508

30508

本文開始介紹了觸發(fā)器的定義和觸發(fā)器的特點(diǎn),其次闡述了觸發(fā)器的分類和觸發(fā)器的作用,最后介紹了觸發(fā)器的工作原理。

2018-03-27 17:35:52 20675

20675 本文開始闡述了單穩(wěn)態(tài)觸發(fā)器工作特點(diǎn)和單穩(wěn)態(tài)觸發(fā)器的分類,其次闡述了單穩(wěn)態(tài)觸發(fā)器工作原理,最后介紹了常用的CD4098單穩(wěn)態(tài)觸發(fā)器。

2018-03-28 15:41:35 38999

38999

觸發(fā)器是一種用來(lái)保障參照完整性的特殊的存儲(chǔ)過(guò)程,它維護(hù)不同表中數(shù)據(jù)間關(guān)系的有關(guān)規(guī)則。當(dāng)對(duì)指定的表進(jìn)行某種特定操作(如:Insert,Delete或Update)時(shí),觸發(fā)器產(chǎn)生作用。觸發(fā)器可以調(diào)用存儲(chǔ)過(guò)程。

2019-07-12 10:05:42 23612

23612

電平觸發(fā)器的邏輯結(jié)構(gòu),只有CLK為高電平的時(shí)候才能接受輸入信號(hào),并按照輸入信號(hào)將觸發(fā)器輸出置成相應(yīng)的輸出。它是由一個(gè)SR觸發(fā)器和兩個(gè)與非門組成,又稱為同步SR觸發(fā)器。

2019-08-07 14:22:34 6974

6974 JK觸發(fā)器是數(shù)字電路觸發(fā)器中的一種基本電路單元。JK觸發(fā)器具有置0、置1、保持和翻轉(zhuǎn)功能,在各類集成觸發(fā)器中,JK觸發(fā)器的功能最為齊全。在實(shí)際應(yīng)用中,它不僅有很強(qiáng)的通用性,而且能靈活地轉(zhuǎn)換其他類型的觸發(fā)器。由JK觸發(fā)器可以構(gòu)成D觸發(fā)器和T觸發(fā)器。

2019-11-08 14:48:44 84376

84376

脈沖觸發(fā)器由兩個(gè)相同的電平觸發(fā)的SR觸發(fā)器組成,其中左SR觸發(fā)器成為主觸發(fā)器,右手側(cè)稱為從觸發(fā)器。

2021-02-11 10:56:00 7953

7953

鎖存器和觸發(fā)器有時(shí)組合在一起,因?yàn)樗鼈兌伎梢栽谄漭敵錾洗鎯?chǔ)一位(1或0)。與鎖存器相比,觸發(fā)器是需要時(shí)鐘信號(hào)(Clk)的同步電路。D 觸發(fā)器僅在時(shí)鐘從

2023-06-29 11:50:18 14168

14168

什么是觸發(fā)器?觸發(fā)器的作用是什么?觸發(fā)器的觸發(fā)方式 觸發(fā)器是一種在數(shù)據(jù)庫(kù)中執(zhí)行自動(dòng)化操作的工具。它是一種特殊的存儲(chǔ)過(guò)程,可以監(jiān)視數(shù)據(jù)庫(kù)表的變化,并在滿足特定條件時(shí)自動(dòng)觸發(fā)一系列操作。觸發(fā)器通常

2023-08-24 15:50:15 3677

3677 不同類型的觸發(fā)器可能有不同的執(zhí)行順序。例如,對(duì)于同一個(gè)表上的多個(gè)觸發(fā)器,插入觸發(fā)器(INSERT trigger)可能先于更新觸發(fā)器(UPDATE trigger)執(zhí)行。

2024-02-05 10:09:13 223

223

D觸發(fā)器的穩(wěn)態(tài) D觸發(fā)器是數(shù)字電路中常用的一種存儲(chǔ)元件,它有兩種穩(wěn)態(tài),即低電平穩(wěn)態(tài)和高電平穩(wěn)態(tài)。當(dāng)輸入D為低電平時(shí),輸出Q保持為低電平;當(dāng)輸入D為高電平時(shí),輸出Q保持為高電平。 D觸發(fā)器和RS觸發(fā)器

2024-02-06 11:32:41 423

423 觸發(fā)器是數(shù)字電路中常用的組合邏輯電路,在現(xiàn)代電子系統(tǒng)中有著廣泛的應(yīng)用。其中,最常用的兩種觸發(fā)器是T觸發(fā)器和JK觸發(fā)器。本文將詳細(xì)介紹T觸發(fā)器和JK觸發(fā)器的區(qū)別和聯(lián)系。 一、T觸發(fā)器 T觸發(fā)器是一種

2024-02-06 14:04:55 419

419 如何用JK觸發(fā)器構(gòu)成T觸發(fā)器 JK觸發(fā)器是一種基本的觸發(fā)器電路,由兩個(gè)輸入端J和K控制,以及兩個(gè)輸出端Q和Q'組成。JK觸發(fā)器的輸出可以持續(xù)性地保持其前一狀態(tài)或由輸入信號(hào)而改變。T觸發(fā)器是一種特殊

2024-02-06 14:11:11 425

425 電平觸發(fā)器、脈沖觸發(fā)器、邊緣觸發(fā)器有什么不一樣? 電平觸發(fā)器、脈沖觸發(fā)器和邊緣觸發(fā)器是數(shù)字電路中常用的觸發(fā)器類型,它們?cè)诠ぷ髟砗?b class="flag-6" style="color: red">觸發(fā)方式上存在著一些不同之處。下面將詳細(xì)介紹這三種觸發(fā)器的特點(diǎn)

2024-02-06 15:51:44 365

365

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論