1、引言

美國(guó)模擬器件公司(ADI)發(fā)布了一種創(chuàng)新的半導(dǎo)體制造工藝,這種工藝技術(shù)是將高電壓半導(dǎo)體工藝與亞微米CMOS和互補(bǔ)雙極型工藝相結(jié)合,并將該工藝命名為iCMOS(工業(yè)CMOS)。使諸如工廠自動(dòng)化和過程控制等高電壓應(yīng)用在性能、設(shè)計(jì)和節(jié)省成本方面均得到極大提升。iCMOS能把更多的信號(hào)鏈路功能集成在一個(gè)尺寸比以前小很多的芯片內(nèi),并且不犧牲性能,將數(shù)字邏輯電路與高速模擬電路集成在一起,并且采用前所未有的小尺寸封裝,提供更高的性能和更低的功耗。AD7656就是采用iC-MOS工藝制造的,是高集成度、6通道16-bit逐次逼近(SAR)型ADC,內(nèi)含1個(gè)2.5V基準(zhǔn)電壓源和基準(zhǔn)緩沖器。該器件的功耗比最接近的同類雙極型ADC降低了60%。AD7656在每通道250kS/s采樣速率下的精度(±4LSB最大值積分線性誤差)是同類產(chǎn)品的2倍。基于iCOMS技術(shù)制造的ADC可以滿足工業(yè)領(lǐng)域?qū)Ω叻直媛省⒍嗤ǖ馈⒏咿D(zhuǎn)換速率和低功耗的要求。

2、AD7656的特性及引腳功能

2.1 AD7656的特性

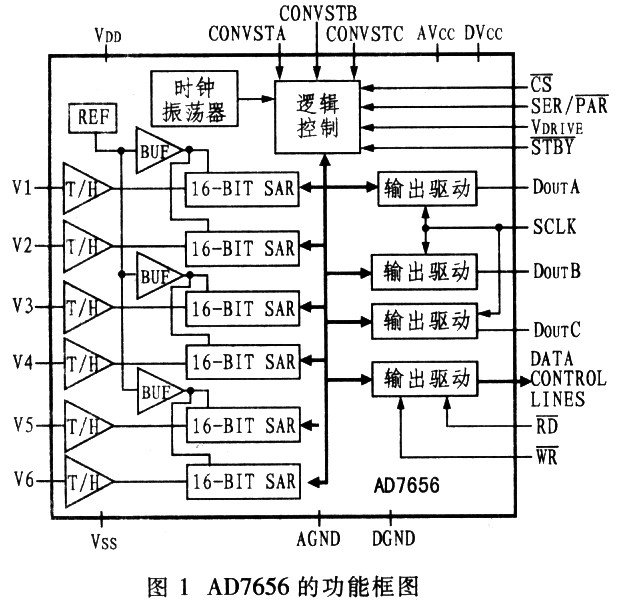

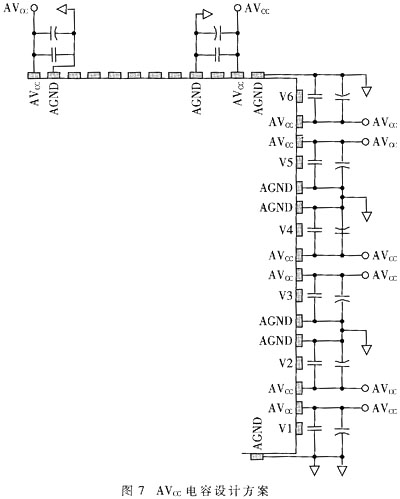

圖1示出AD7656的功能框圖。AD7656的主要特性如下:

●6通道16-bit逐次逼近型ADC;

●最大吞吐率為250kS/s;

●AVcc范圍為4.75V-5.25V;

●低功耗:在供電電壓為5V、采樣速率為250kS/s時(shí)的功耗為160mW;

●寬帶寬輸入:輸入頻率為50kHz時(shí)的信噪比(SNR)為85dB;

●片上有2.5V基準(zhǔn)電壓源和基準(zhǔn)緩沖器;

●有并行和串行接口;

●與SPI/QSPI/μWire/DSP兼容的高速串行接口;

●可通過引腳或軟件方式設(shè)定輸入電壓范圍(±10V,±5V);

●采用iCMOS工藝技術(shù);

●64引腳QFP。

2.2 AD7656的引腳功能

REFCAPA、REFCAPB、REFCAPC是參考電壓引腳,這幾個(gè)引腳應(yīng)該接去耦電容器來減小每1個(gè)ADC通道參考緩沖器的衰減。

V1一V6是模擬輸入1-6引腳,它們是模擬前端輸入,對(duì)應(yīng)通道的輸入范圍取決于RANGE引腳的定義。

AGND是模擬地,所有的模擬輸入信號(hào)和外部參考信號(hào)都要用AGND。

DVcc是5V數(shù)字電源端。

VDRIVE是邏輯電源輸入,該引腳的電壓取決于內(nèi)部參考電壓,應(yīng)接10μF或100μF的去耦電容器。

DGND是數(shù)字地,它是數(shù)字電路的參考點(diǎn)。

AVcc是模擬電壓輸入(4.5V-5.5V),它只給ADC的內(nèi)核供電。

CONVSTA/B/C是轉(zhuǎn)換使能邏輯輸入,每對(duì)有其相關(guān)的CONVST信號(hào),用來啟動(dòng)每對(duì)或每4個(gè)或6個(gè)ADC同步采樣。

CS是片選信號(hào),邏輯低電平時(shí)使能。

RD是讀信號(hào),邏輯低電平時(shí)使能。

WR/PEFEN/DIS是寫數(shù)據(jù)/參考使能/非使能。

BUSY是忙信號(hào)輸出,當(dāng)轉(zhuǎn)換開始時(shí)為高電平,并且在轉(zhuǎn)換結(jié)束前一直為高電平。

SER/PAR是串行/并行選擇輸入信號(hào)。低電平時(shí)選擇并行接口模式,高電平時(shí)選擇串行接口模式。

DB[0]/SEL A是數(shù)據(jù)0位/選擇輸出A路。

DB[1]/SEL B是數(shù)據(jù)1位/選擇輸出B路。

DB[2]/SEL C是數(shù)據(jù)2位/選擇輸出C路。

DB[3]/DCIN C是數(shù)據(jù)3位,C路為菊花鏈?zhǔn)健?/p>

DB[4]DCIN B是數(shù)據(jù)4位/B路為菊花鏈?zhǔn)健?/p>

DB[5]/DCIN A是數(shù)據(jù)5位/A路為菊花鏈?zhǔn)健?/p>

DB[6]/SCLK是數(shù)據(jù)6位/串行時(shí)鐘。

DB[7]/HBEN/DCEN是數(shù)據(jù)7位/高位使能/菊花鏈?zhǔn)绞鼓堋?/p>

DB[8]DOUTA是數(shù)據(jù)8位/串行數(shù)據(jù)輸出A。

DB[9]/DOUTB是數(shù)據(jù)9位/串行數(shù)據(jù)輸出B。

DB[10]/DOUTC是數(shù)據(jù)10位/串行數(shù)據(jù)輸出C。

DB[11]/DGND是數(shù)據(jù)11位/數(shù)字地。

DB[12]、DB[13]、DB[15]是數(shù)據(jù)12位、數(shù)據(jù)13位、數(shù)據(jù)15位。

DB [14]/REFBUFEN/DIS是數(shù)據(jù)14位/參考緩沖使能(低電平時(shí))/非使能(高電平時(shí))。

RESET是復(fù)位信號(hào)輸入。

RANGE是模擬輸入范圍選擇輸入信號(hào)。

VDO是正電源端。

Vss是負(fù)電源端。

H/S SEL是硬件/軟件選擇輸入引腳。

W/B是字或字節(jié)模式選擇。

3、AD7656的工作原理及系統(tǒng)構(gòu)成

3.1AD7656的工作原理

AD7656是逐次逼近型轉(zhuǎn)換器,包括1個(gè)比較器、1個(gè)模/數(shù)轉(zhuǎn)換器、1個(gè)逐次逼近寄存器(SAR)和1個(gè)邏輯控制單元。轉(zhuǎn)換中的逐次逼近是按對(duì)分原理由控制邏輯電路完成。其大致過程如下:?jiǎn)?dòng)轉(zhuǎn)換后,控制邏輯電路首先把逐次逼近寄存器的最高位置1,其他置0,逐次逼近寄存器的這個(gè)內(nèi)容經(jīng)過模/數(shù)轉(zhuǎn)換后得到約為滿量程輸出一半的電壓值。這個(gè)電壓值在比較器中與輸入信號(hào)進(jìn)行比較。比較器的輸出反饋到模/數(shù)轉(zhuǎn)換器,并在下一次比較前對(duì)其進(jìn)行修正。在邏輯控制電路的時(shí)鐘驅(qū)動(dòng)下,逐次逼近寄存器不斷進(jìn)行比較和移位操作,直到完成最低有效位(LSB)的轉(zhuǎn)換。這時(shí)逐次逼近寄存器的各位值均已確定,逐次逼近轉(zhuǎn)換完成。

由于逐次逼近型模/數(shù)轉(zhuǎn)換器在1個(gè)時(shí)鐘周期內(nèi)只能完成1位轉(zhuǎn)換,N位轉(zhuǎn)換需要N個(gè)時(shí)鐘周期,故這種模/數(shù)轉(zhuǎn)換器的采樣速率不高,輸入帶寬也較小。它的優(yōu)點(diǎn)是原理簡(jiǎn)單,便于實(shí)現(xiàn),不存在延遲問題.適用于中速率和分辨率較高的應(yīng)用場(chǎng)合。

AD7656包含1個(gè)低噪聲、寬帶跟蹤保持放大器來處理輸入頻率高達(dá)8MHz的信號(hào),還具有高速并行和串行接口,從而允許該器件與微處理器(MPU)或數(shù)字信號(hào)處理器(DSP)連接。在串行接口方式下,AD7656能提供菊花鏈功能,把多個(gè)ADC連接到1個(gè)串行接口上。它可以接收雙極性輸入信號(hào),RANGE引腳和RNG位為下次在±4xVREF-±2xVREF之間轉(zhuǎn)換選擇輸入范圍。當(dāng)3個(gè)CONVST引腳連接到一起時(shí),允許6個(gè)片上ADC同時(shí)采樣,6個(gè)ADC可以被分成3對(duì),每對(duì)有1個(gè)相關(guān)的CONVST信號(hào),用來啟動(dòng)每對(duì)或每4個(gè)或是全部6個(gè)ADC同步采樣,CONVSTA用來啟動(dòng)V1和V2的同步采樣,CONVSTB對(duì)應(yīng)的是V3和V4,CONVSTC對(duì)應(yīng)的是V5和V6。

跟蹤保持放大器可以保證模/數(shù)轉(zhuǎn)換器精確地轉(zhuǎn)換滿量程輸入的正弦波信號(hào),可以保證分辨率為16bit。跟蹤保持放大器的輸入帶寬比工作在最大吞吐率情況下的ADC的奈奎斯特速率還要大。AD7656可以處理頻率為8MHz的輸入信號(hào)。跟蹤保持放大器在CONVSTx的上升沿同步采樣各自的輸入信號(hào)。跟蹤保持的典型時(shí)間為20ns,這可以使6個(gè)ADC同步采樣。

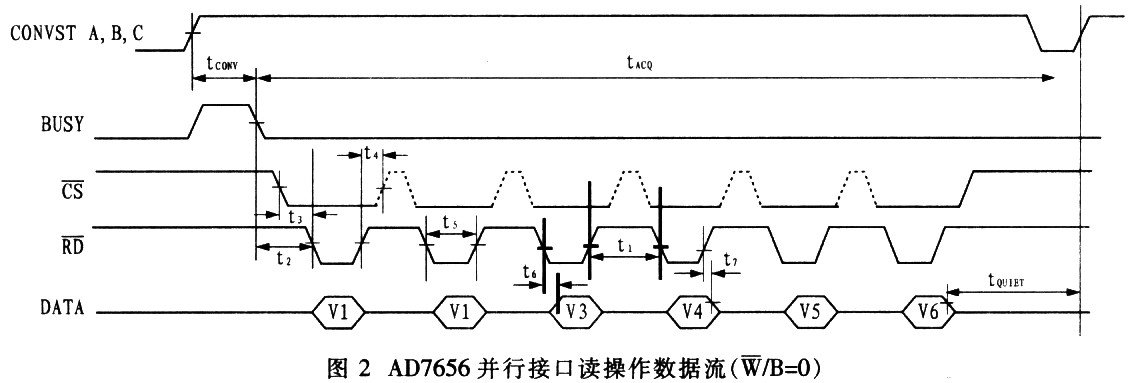

AD7656有2種工作模式:串行接口模式和高速的并行接口模式。本文主要介紹并行接口模式。并行接口模式以1個(gè)字的形式來操作(W/B=0),也可采用字節(jié)的形式(W/B=1)。從并行總線上讀數(shù)據(jù)時(shí),信號(hào)SER/PAR應(yīng)被置低電平。當(dāng)CS和RD均為低電平時(shí),數(shù)據(jù)線DBO-DB15將不再是高阻狀態(tài)。CS信號(hào)可以被永久地置低電平,RD用來訪問轉(zhuǎn)換的結(jié)果。BUSY信號(hào)為低電平時(shí)開始讀操作。

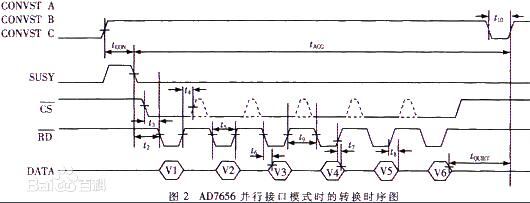

AD7656有1個(gè)用來執(zhí)行轉(zhuǎn)換的片上振蕩器,轉(zhuǎn)換時(shí)間tCONVER為3μS。轉(zhuǎn)換的開始是通過脈沖調(diào)制CONVSTx信號(hào)開始的,在CONVSTx的上升沿,被選中的ADC的跟蹤保持電路會(huì)被置為保持模式,轉(zhuǎn)換開始。在CONVSTx信號(hào)的上升沿后,BUSY信號(hào)會(huì)變化,這表示轉(zhuǎn)換正在進(jìn)行。轉(zhuǎn)換時(shí)鐘是由內(nèi)部產(chǎn)生的,轉(zhuǎn)換時(shí)間是從CONVSTx信號(hào)上升沿開始的3μS,BUSY信號(hào)會(huì)變?yōu)榈碗娖剑硎巨D(zhuǎn)換結(jié)束。在BUSY信號(hào)的下降沿,跟蹤保持電路將回到跟蹤模式。數(shù)據(jù)通過并行或串行接口從輸出寄存器中被讀出。圖2示出AD7656并行接口字模式下的讀操作數(shù)據(jù)流。

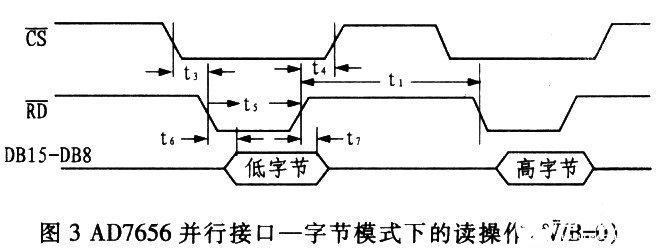

如果只有8bit總線被使用,那么AD7656的接口將以字節(jié)模式(W/B=I)操作,這種操作下的轉(zhuǎn)換結(jié)果將通過2次讀操作來訪問,每次讀操作通過DB15-DB8來訪問1個(gè)8bit的數(shù)據(jù),如圖3所示。其中,tCONV為轉(zhuǎn)換時(shí)間3μS,內(nèi)部時(shí)鐘tQUIET為總線的廢棄時(shí)間到下1個(gè)轉(zhuǎn)換開始之間所必需的最小等待時(shí)間,最小值為400ns;t1為讀操作時(shí)的最小時(shí)間20ns;t2為BUSY信號(hào)到RD信號(hào)之間的延遲時(shí)間(ns);t3為CS到RD之間的建立時(shí)間(ns);t4為CS到RD之間的保持時(shí)間(ns);t5為RD的脈沖寬度,最小值為30ns;t6為RD下降沿后的數(shù)據(jù)訪問時(shí)間,最大值為30ns;t7為RD上升沿之后的總線廢棄時(shí)間,最小值為15ns,最大值為25ns。

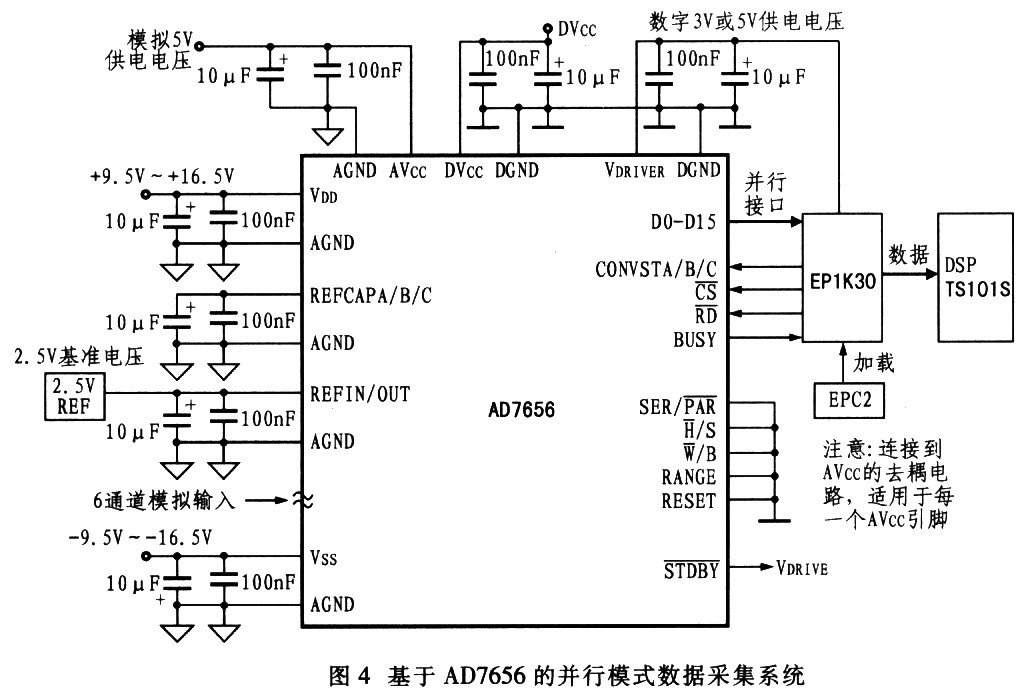

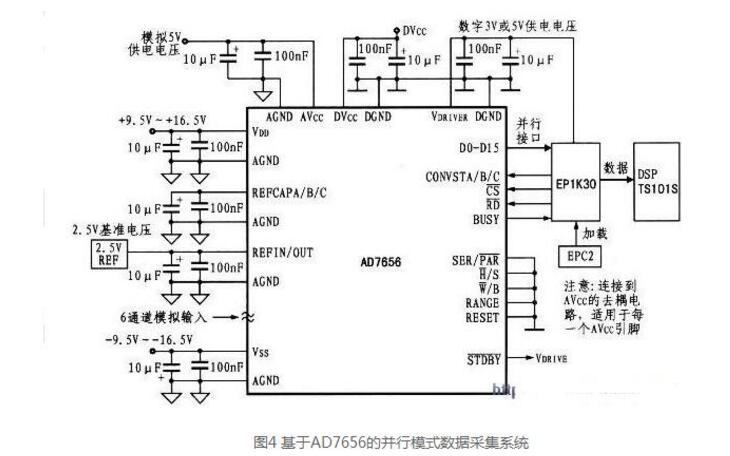

3.2系統(tǒng)組成

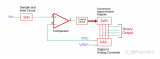

圖4所示是AD7656在并行接口狀態(tài)下的外圍電路連接。其中的DVcc和AVcc分別是數(shù)字電壓端和模擬電壓端,它們?cè)诮尤肭耙?jīng)過1個(gè)去耦電路,如圖4所示,每個(gè)供電電壓輸入引腳都要連接1個(gè)去耦電路,該電路由1只10μF和1只100nF的電容器組成。VDD、Vss和VDRIVE同樣要連接去耦電路。

AD7656的輸出接到FPGA中進(jìn)行數(shù)字信號(hào)的濾波處理,然后再送入數(shù)字信號(hào)處理器(DSP)進(jìn)行處理。用FPGA控制引腳CONVSTA/B/C、RD和CS的狀態(tài),可以用編程的方法或硬件連接的方式來實(shí)現(xiàn)。系統(tǒng)中的FPGA是ALTERA公司的EP1K30,DSP選用ADI公司的TS101S。此系統(tǒng)的外圍電路比較簡(jiǎn)單,比較容易實(shí)現(xiàn),具有真正的高速、高性能數(shù)字信號(hào)采集功能。

3.3應(yīng)用程序舉例

(1)A/D數(shù)據(jù)采集部分的初始化部分程序

4、注意事項(xiàng)

在繪制PCB版圖時(shí),要注意將AD7656的模擬和數(shù)字部分分開布局,并把它們放在板上的特定區(qū)域,這樣可以使地層比較容易分開,使用起來比較方便。數(shù)字地層和模擬地層應(yīng)該在板上的某一處連接到一起,可以用0Ω電阻器,也可以使用磁珠或直接用焊錫連接。建議在布線的時(shí)候不要將數(shù)據(jù)線布在該器件的下方,因?yàn)檫@樣做會(huì)使信號(hào)和噪聲混在一起。電源線應(yīng)該盡量粗一些,這樣可以盡量減小電源線的脈沖干擾。去耦電容器應(yīng)盡量地靠近器件,之間的連線要盡量短以減小感抗。電路的性能除了受核心ADC的影響外,還受到各種外圍輔助電路性能的影響。

5、結(jié)束語

本文介紹了采用先進(jìn)的工業(yè)CMOS(iCMOS)工藝制造的AD7656型模,數(shù)轉(zhuǎn)換器,并將它應(yīng)用在數(shù)字采集系統(tǒng)中。多通道模/數(shù)轉(zhuǎn)換器同步采樣技術(shù)提高了數(shù)字信號(hào)處理的速度和精度。AD7656的外圍電路配置簡(jiǎn)單,應(yīng)用領(lǐng)域也會(huì)越來越廣泛。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論