1、跨時鐘域與亞穩態

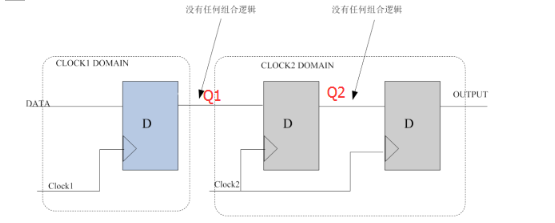

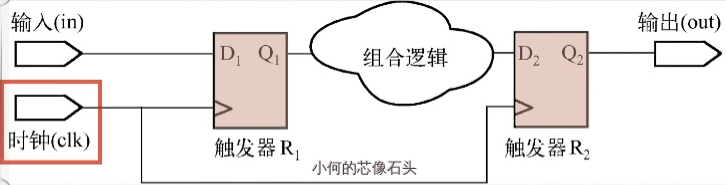

跨時鐘域通俗地講,就是模塊之間有數據交互,但是模塊用的不是同一個時鐘進行驅動,如下圖所示:

左邊的模塊1由clk1驅動,屬于clk1的時鐘域;右邊的模塊2由clk2驅動,屬于clk2的時鐘域。當clk1比clk2的頻率高時,則稱模塊1(相對于模塊2)為快時鐘域,而模塊2位為慢時鐘域。根據clk1和clk2是不是同步時鐘,可以將上面的跨時鐘域分為跨同步時鐘域(clk1與clk2是同步時鐘)和跨異步時鐘域(clk1和clk2不是同步時鐘)。根據信號是控制信號還是數據信號可以分為跨時鐘域的控制信號傳輸和數據信號的傳輸。

在跨時鐘域的信號傳輸過程中,可能出現亞穩態的情況,這個時候,需要同步器進行同步,減小亞穩態傳播下去的概率;注意這里的同步器只能減少亞穩態往下傳播的概率,如果產生亞穩態,亞穩態恢復穩定后的電平不一定是正確的電平,如果穩定后的電平是錯誤的,那么就很有可能引起后面的邏輯的錯誤,這是需要強調的;當然,一般情況下(我這里是說一般情況)很少發生亞穩態,不然后面的邏輯豈不是要掛?

根據上面的內容可知,跨時鐘域可能需要同步器來抑制亞穩態的往下傳播的概率,根據情況的不同需要不同的同步器,大致情況如下所示:

跨同步時鐘域快時鐘域到慢時鐘域控制信號傳輸

跨異步時鐘域慢時鐘域到快時鐘域數據信號傳輸

·跨同步時鐘域下,快時鐘域到慢時鐘域 的控制信號傳輸;

·跨同步時鐘域下,慢時鐘域到塊時鐘域 的控制信號傳輸;

·跨同步時鐘域下,快時鐘域到慢時鐘域 的數據信號傳輸;

·跨同步時鐘域下,慢時鐘域到塊時鐘域 的數據信號傳輸;

·跨異步時鐘域下,快時鐘域到慢時鐘域 的控制信號傳輸;

·跨異步時鐘域下,慢時鐘域到塊時鐘域 的控制信號傳輸;

·跨異步時鐘域下,快時鐘域到慢時鐘域 的數據信號傳輸;

·跨異步時鐘域下,慢時鐘域到塊時鐘域 的數據信號傳輸;

看著這八大類型,心里就虛,但是這里先劇透一下,在數據的傳輸(主要是多位數據的傳輸)里面,無論是跨同步還是跨異步,主要(注意是主要)都是使用比較大的同步隔離器,進行隔離緩沖數據,比如FIFO、RAM;因此一般就會分為控制信號(一般是1位信號)和數據這兩種情況設計同步器。跨時鐘域的數據傳輸我們放在最后講。今天主要整理跨時鐘域的控制信號傳輸。

我在前面的一篇博客中說到了同步電路與異步電路的區分:http://www.cnblogs.com/IClearner/p/6440488.html 。這里我們要隨機應變,在這里更新一下傳統同步時鐘的概念:系統中的多個時鐘,如果他們的邊沿相對的時間差固定(或者說相位固定),那么就屬于同步時鐘。它們可以是不同時鐘源產生的,但是通過鎖相環把它們之間的相位進行固定,因此是同步時鐘。它們可能是同一時鐘源產生的,但是經過分頻之后,它們之間的相位隨著初始相位和時間變化,這類時鐘可以叫他同步時鐘,但是從這個傳統的概念出發,這就是異步時鐘(這個與我上面的那篇博客不一樣,要注意),在處理上當做異步時鐘進行處理。好了,說了這么多,接下來我們就根據時鐘的分類來進行說說吧。

2、跨同步時鐘的控制信號傳輸

(1)同頻同相位的兩個同步時鐘:

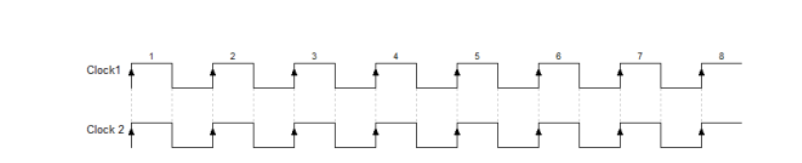

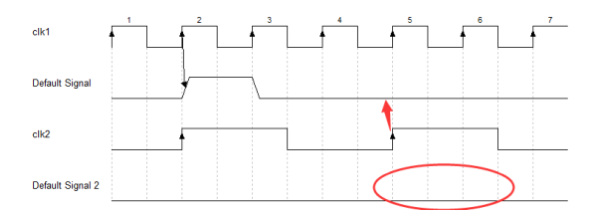

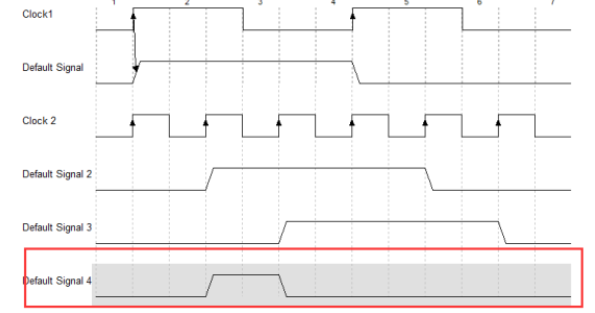

波形如下所示:

這兩個時鐘可以看做是同一個時鐘,也就是單時鐘設計,允許有1個時鐘的周期進行傳輸數據,因此只要滿足普通的同步電路設計要求(滿足建立時間和保持時間,控制信號的傳輸延時要在一定范圍內)就可以了,不會出現亞穩態,也不會出現數據丟失的情況,一般不需要同步器。

(2)同頻不同相位的兩個同步時鐘

波形如下所示:

這個固定的相位可以看成是時鐘的偏移,允許的傳輸時間小于一個時鐘周期,但是只要滿足控制信號的輸出是在clk1的控制下進行翻轉的,因此只要滿足同步設計的一般要求(滿足建立時間和保持時間,控制信號的傳輸延時要在一定范圍內),就可以滿足時序,不會出生亞穩態,也不會出現數據丟失的情況,因此一般不需要同步器。

(3)不同頻,但是存在整數倍的關系

假設沒有初始相位差(或者即使有初始相位差固定,也可以通過后期修復),clk1的時鐘頻率是clk2的3倍。

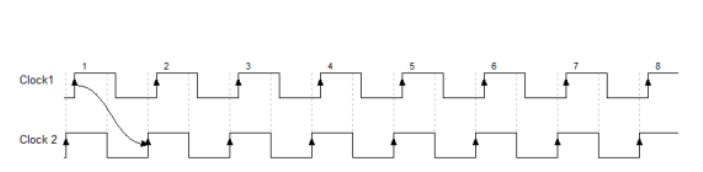

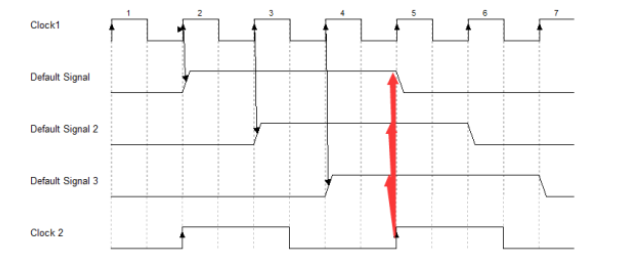

·當從快時鐘域跨到慢時鐘域時(也就是控制信號從clk1的模塊傳輸到clk2的模塊),波形如下所示:

如果是clk1在第2個上升沿進行發送信號,只要控制信號在3個clk1的周期內到達,就不會出現亞穩態;。。.如果clk1在第4個上升沿進行發送信號,就需要控制信號在1個clk1的周期內到達,就不會出現亞穩態。因此只要控制信號從發送時鐘域出發到達目的時鐘域的時間小于clk1的時鐘周期,就不需要同步器;一般情況下,控制信號是觸發器觸發,觸發器捕獲,一般滿足這個關系,如下所示:

然而需要注意的,這個是從快傳到慢,慢時鐘域可能會采樣不到控制信號從而丟失控制信號,也就是說,我控制信號在從clk1跑到clk2,并且保持一個時鐘(clk1)周期,但是你clk2的時鐘沿還沒有來,等到clk2的上升沿來了,我這個控制信號就已經更新(或者失效)了,上面恰好在時鐘clk2上升沿的前一個時鐘周期clk1發出信號才采到,如果不是那個時候發送,就會丟失控制信號,如下所示:

在第2個時鐘沿發送信號的時候,只持續了一個時鐘周期,因此clk2捕捉不到(這樣就是功能性錯誤了,不單單是時序上的亞穩態而已了);只有在第4個時鐘沿的時候發送控制信號,clk2才捕捉得到。因此我們就需要把這個控制信號的周期延遲到clk1周期的3倍,這個可以通過計數器或者狀態機進行實現,延長后的波形如下所示:

可見,這時候不論在上面時候進行發送數據,clk2都能捕捉得到。

因此一般情況下不需要同步器,但是需要把快時鐘域的控制信號根據進行延長合適的時間(根據時鐘之間的倍數關系進行確定,控制信號的長度要≥捕獲時鐘的周期,一般取1.5倍,上圖只是1倍),避免慢時鐘域丟失信號。

·當慢時鐘到快時鐘域時(也就是控制信號從clk2的模塊傳輸到clk1的模塊),波形如下所示:

很顯然,快時鐘能夠采樣得到慢時鐘的控制信號,而且采樣了三次,輸出為:

Clock2的控制信號就達到了clk2周期的3倍,如果只需要1個clk周期的控制信號,可以通過上升沿檢測電路實現,其輸出波形如下所示:

3、時鐘同源,周期之間非整數倍的跨時鐘域

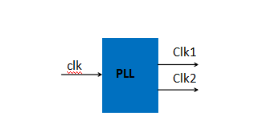

當兩個時鐘都來源于同一個時鐘,經過PLL分頻之后,產生兩個時鐘時鐘,一個時鐘是另外一個時鐘的非整數倍,相位是隨時間變化的。在這種情況下,我們可以把這兩個時鐘當做同步時鐘,也可以當做異步時鐘;在傳統的設計中,這樣的時鐘會當做異步時鐘進行處理。下面我們就來看看這樣的時鐘處理要不要加同步器吧。

假如時鐘源的時鐘頻率為clk,經過PLL后,產生一個時鐘clk1和一個時鐘clk2:

假設clk1是快時鐘,clk2是慢時鐘。由于控制信號僅僅在兩個時鐘域的觸發器之間傳輸,觸發器之間不存在任何邏輯,因此控制信號從發送觸發器到捕獲觸發器的時間很小,假設為t ps,當發送沿與捕獲沿之間的間距大于tps,就不會產生亞穩態(理論情況,不考慮時鐘偏移、翻轉等因素)。當clk1的頻率不是clk2的整數倍的時候,他們的相位是隨著時間的改變而改變的,在知道了clk1和clk2的頻率后,就可以知道理論下clk1和clk2的相位關系,那么就會有下面的情況:

(其實也就分為要不要加同步器的的情況)

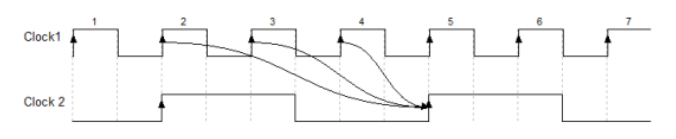

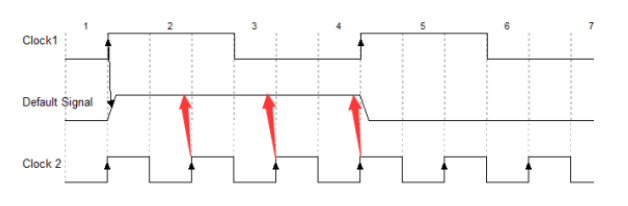

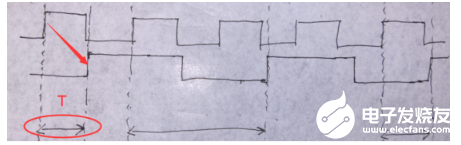

(1)(跨時鐘域無論是快到慢還是慢到快)兩個時鐘存在最小相位差,且最小相位差大于t。如下所示:

這里的這種情況下,時鐘最小最小的相位差T》t,也就是說,控制信號不會違反捕獲寄存器的建立時間和時間。需要注意的是,這是快時鐘到慢時鐘域的控制信號傳輸,要防止信號丟失的情況,也就是需要將控制信號延長到一定的長度。

從慢時鐘到時鐘的波形就不畫了, 但是主要符合兩個時鐘(無論是快到慢還是慢到快)存在最小相位差,且最小相位差大于t,就不會違反建立時間和保持時間,基本不會產生亞穩態。因此在這種情況下,是不需要同步器的。

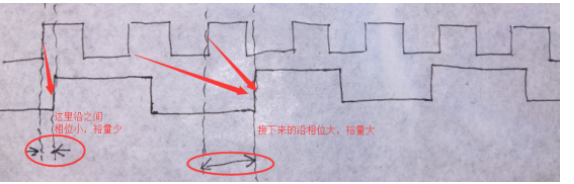

(2)(跨時鐘域無論是快到慢還是慢到快)兩個時鐘中,發送沿到接收沿的相位很窄,小于t,也就是違反捕獲寄存器的建立時間和保持時間,但是下一次的發送沿到接收沿的相位很大(不違反捕獲寄存器的建立時間和保持時間)的情況,如下所示:

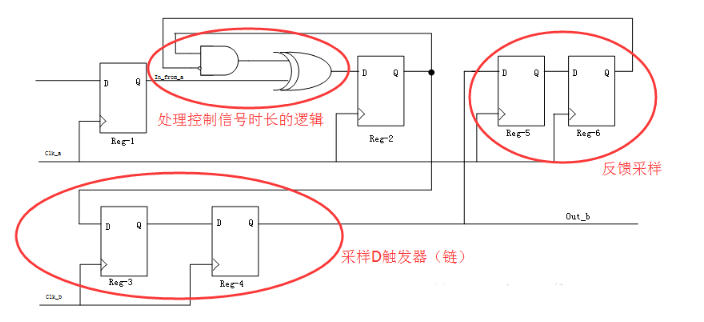

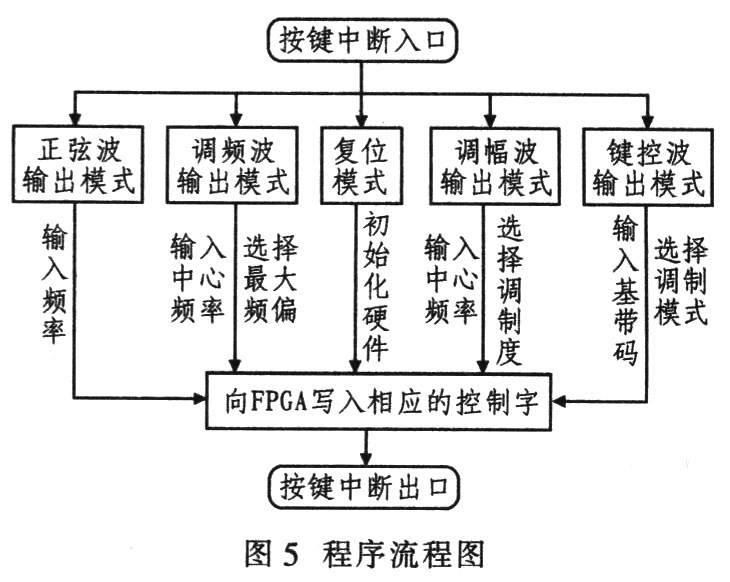

在相位小的地方,建立時間不足,引起了亞穩態,這時候就要上我們的同步器了,這里隆重推出我們的同步器——雙D觸發器,其電路圖如下所示:

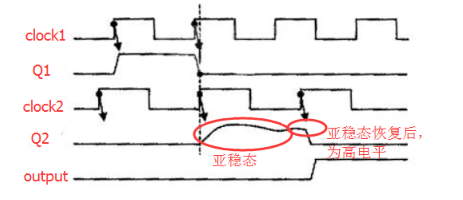

要注意,其中間不能有任何組合邏輯,電路圖與對于的時序關系如下所示(代碼就不寫了,電路簡單):

再次強調,雙D觸發器(觸發器鏈)只能抑制亞穩態往下傳輸(或者減小其往下傳輸的概率),并不一定能夠同步正確的控制信號的值,這與亞穩態穩定后的值有關,上圖中一級觸發器的亞穩態穩定后的值恰好是高電平,因此二級觸發器采樣后的輸出值為高電平。如果上圖中一級觸發器的亞穩態穩定后的值是低電平,那么二級觸發器采樣后的輸出值將為低電平,也就是輸出了錯誤的控制信號。

這里再啰嗦一下,在這種情況下(也就是有亞穩態的情況下),從慢到快,只有亞穩態的問題;而從快傳輸到慢,不僅有要抑制亞穩態往下傳播的問題,還有控制信號丟失的問題,這里就需要延長控制信號的長度或者采取其他措施(后面會講)。

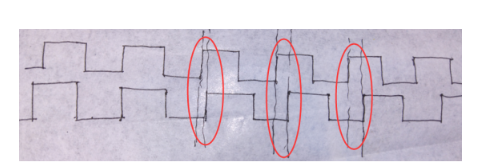

(3)兩個時鐘相鄰的幾次發送沿和接收沿的相位差都很小的情況,如下圖所:

這種情況可以說就基本是異步時鐘域之間的控制信號傳輸了,在這種情況下,必定要加觸發器鏈同步器,抑制亞穩態往下傳播。跟前面的情況一樣,從慢到快,只有亞穩態的問題;而從快傳輸到慢,不僅有要抑制亞穩態往下傳播的問題,還有控制信號丟失的問題,這里就需要延長控制信號的長度或者采取其他措施(后面會講)。

4、跨異步時鐘域的控制信號傳輸

其實跨異步時鐘域的波形跟前面的3.(3)類似,只不過兩個時鐘域的時鐘是完全沒有關系的時鐘而已。在這樣的情況下,我們可以采取跟前面類似的方法:首先觸發器鏈抑制亞穩態的傳輸一定是要的,然后是快時鐘到慢時鐘的問題,也就是采樣短脈沖的控制信號問題,除了對控制信號進行延長之外,我們還可以其他的方法,下面就來整理整理吧:

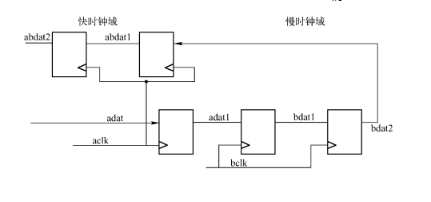

(1)握手/反饋機制

采用握手反饋機制,即可以抑制亞穩態的傳輸,又可以正確地傳輸控制信號。這種握手/反饋機制對所有的跨異步時鐘的控制信號都有用,不過主要用在快到慢時鐘、易產生亞穩態的情況。說了那么多,都沒有實在的,下面就來看點實在的吧——握手/反饋機制電路圖:

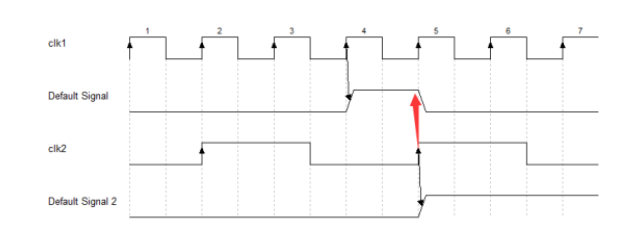

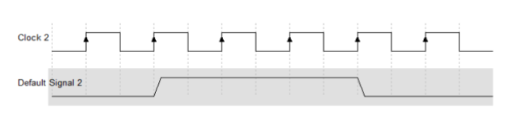

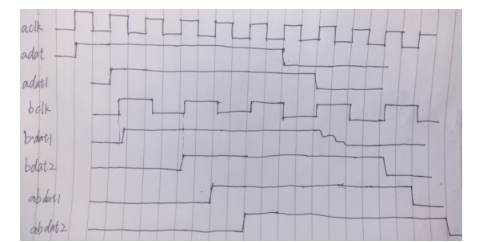

波形如下所示(手繪。。.。):

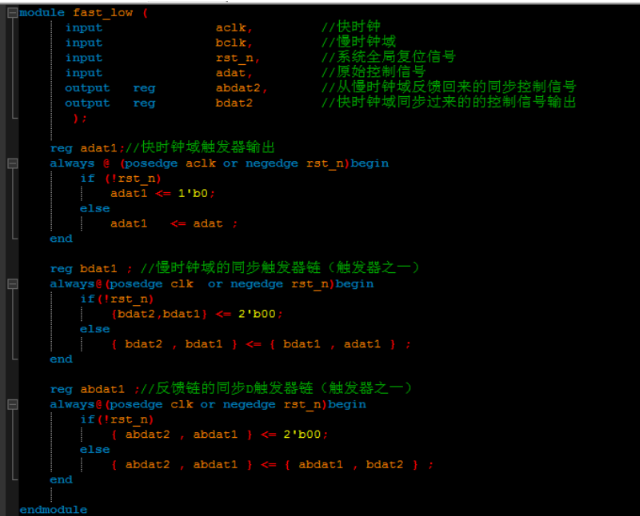

其實原理很簡單,當控制信號變高時(adat與adat1),慢時鐘域的觸發器鏈(bdat1和bdat2)進行采樣,采樣得到的高電平(bdat2)后,也就是確認采樣得到控制信號后,再通過觸發器鏈反饋給快時鐘域(abdat1和abdat2),讓快時鐘域把控制信號拉低(拉低的或者處理時長在后面有電路),就完成控制信號的正確跨時鐘傳輸。本來不想寫代碼了的,畢竟有電路了,但是想想還是貼一下代碼吧,畢竟最近整理過程中都沒有寫代碼了,感覺有點生疏了,代碼如下(如果有錯請指出):

當然,在慢時鐘域階段,我們也可以添加邊沿檢測(上升沿)電路,一方面讓輸出只有一個脈沖的控制信號,另一方面準確地進行控制,以防止亞穩態的干擾。

在上面的握手方案中,我們通過反饋信號進行控制信號的延時來讓慢時鐘域充分采樣得到控制信號,本質上是也是對控制信號的延時。這個延時的具體實現,需要對控制信號的產生邏輯進行處理,來滿足延時的要求,如下所示:

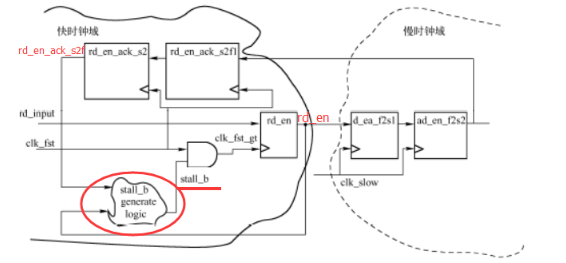

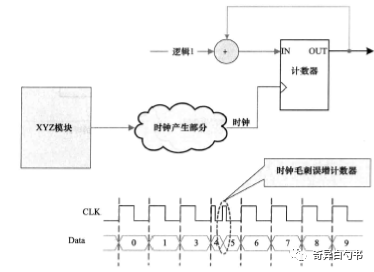

除了上面對控制信號處理之外,我們還可以對快時鐘域的時鐘動點手腳,具體電路如下所示:

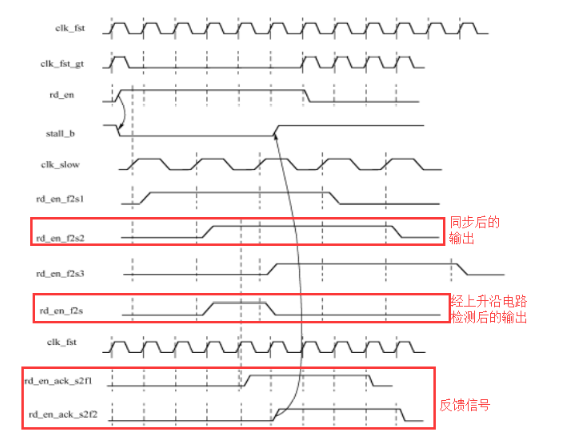

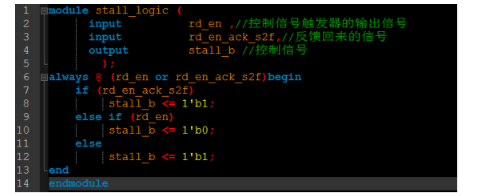

這里通過讓快時鐘域觸發器(特指rd_en觸發器)的時鐘停止工作的方式,讓控制信號保持一定的時間。時鐘停止之后,rd_en觸發器的輸出就會保持不變,等到反饋信號回來,告知慢時鐘域采樣得到高電平后,再恢復快時鐘域的時鐘,波形如下所示:

時鐘停止的邏輯電路(類門控電路)的代碼如下所示(代碼如果有錯,歡迎指出):

?

當然,這是一個組合電路。這樣子會令后面的輸出電路產生毛刺,類似于門控時鐘那樣,于是乎我們就可以使用門控時鐘那樣的技巧,防止輸出產生毛刺。這里就不詳細說明了。

(2)窄脈沖捕捉電路

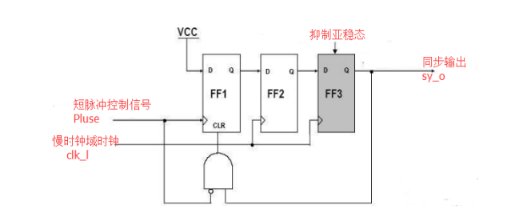

前面的控制信號,它都需要反饋信號來把有效拉為無效,可以說這個控制信號是不“自由”的。有時候,我們需要捕捉異步短脈沖控制信號,這個控制信號完全由前面的邏輯電路生成,與我后面的電路信號無關,也就是說沒有反饋信號,你也需要采樣到這個短脈沖控制信號。下面的窄脈沖捕捉電路可以捕捉到快時鐘域產生的異步窄脈沖控制信號,電路如下所示:

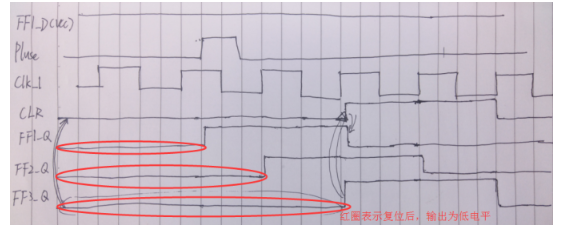

波形圖如下所示:

從波形圖中可以知道,這是利用了脈沖信號的上升沿進行輸出脈沖信號,然后通過后面反饋回來的信號進行清零,從而為下一次脈沖控制信號做好準備。需要注意的是,窄脈沖控制信號的產生頻率不能太快,也就是需要等到清零信號無效(三個觸發器的延時)后才能發出下一個脈沖控制信號,不然后面的慢時鐘域采樣電路無法識別兩次控制信號,而只當成一次控制信號處理。代碼根據電路圖寫就好了=。=。

控制信號的跨時鐘域傳輸到這里就講完了,下面進行總結一下:

·在跨時鐘域的時候,不一定需要跨時鐘域電路(同步器或者握手信號),接近異步時鐘或者就是異步時鐘的時候跨時鐘域就得加上了。

·在慢到快的時鐘域中,加上觸發器鏈基本上就可以了,主要是抑制亞穩態的傳播。

·但是在快到慢的時鐘域中,不僅需要觸發器鏈進行抑制亞穩態的傳播,還要防止慢時鐘域采不到快時鐘域的數據,因此就添加反饋/握手電路(這個反饋信號是指跨時鐘域的反饋信號)。

·在最后,介紹了窄脈沖控制信號捕捉電路,這個電路不需要添加反饋信號,也就是說只要控制信號的頻率不是快,只要有窄脈沖(不是毛刺),就可以捕捉得到,而不需要反饋信號控制脈沖寬度(這個反饋信號是指跨時鐘域的反饋信號,其實還是需要反饋清0的)。

編輯:hfy?

電子發燒友App

電子發燒友App

評論