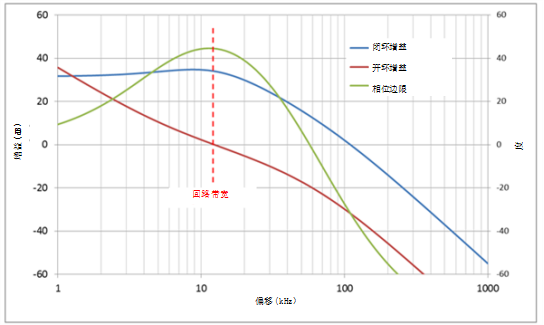

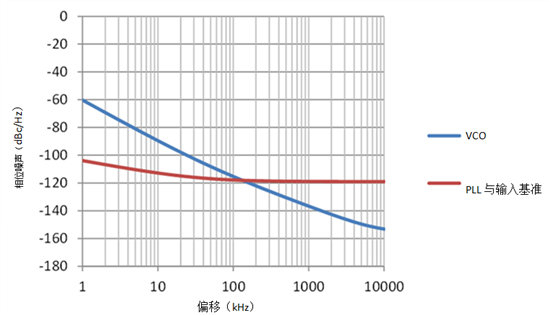

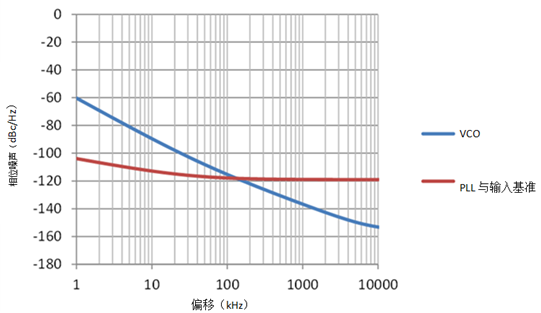

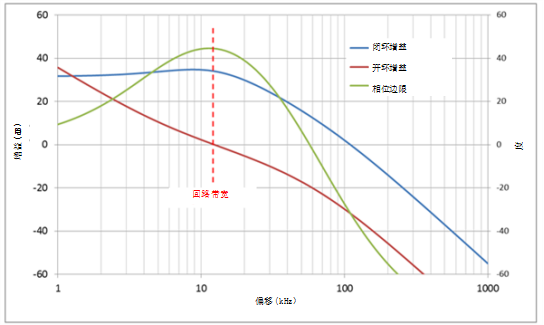

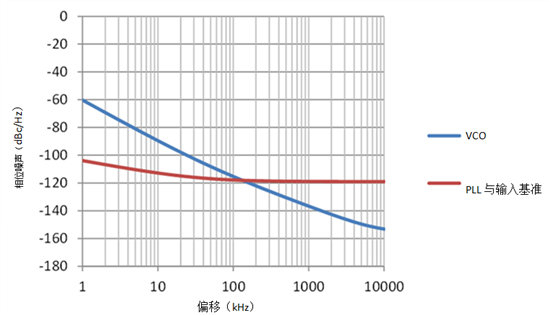

作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要做的仍是尋找最優環路帶寬。

2016-07-18 14:24:04 10326

10326

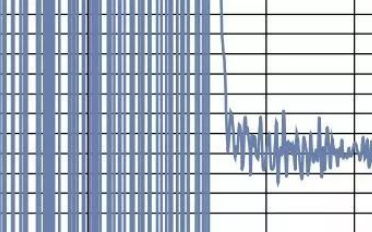

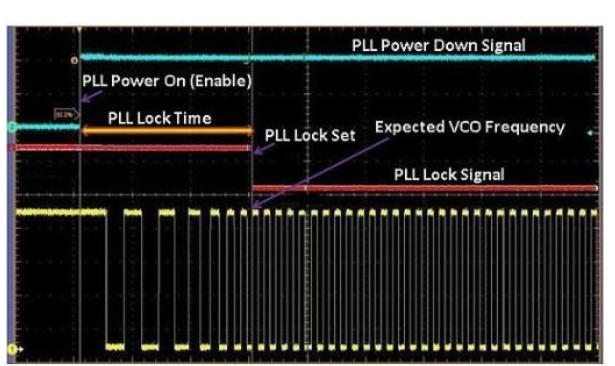

利用手動頻段選擇,鎖定時間可從典型值 4.5 ms 縮短到典型值 360 s。 本文以高度集成的解調器和頻率合成器 ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。 PLL

2018-06-13 09:33:21 4223

4223

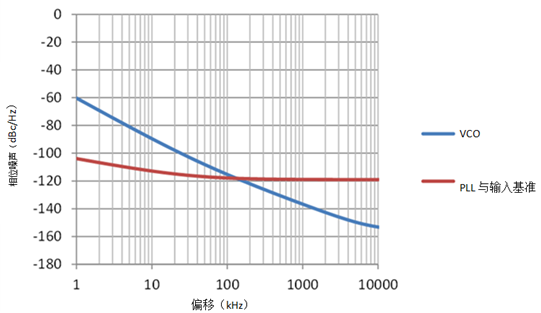

ADRF6820是一款高度集成的解調器和頻率合成器,非常適合用于高級通信系統。 它內置一個寬帶I/Q解調器、一個小數N/整數N分頻鎖相環(PLL)以及一個低相位噪聲多核壓控振蕩器(VCO)。

2018-06-26 17:00:45 6649

6649

本篇文章是關于相位鎖定環(PLL)頻率合成器的設計和分析,重點討論了相位噪聲和頻率噪聲的測量、建模和仿真方法。文章以設計一個假想的PLL頻率合成器為例,詳細介紹了設計過程和步驟。從規格選擇、電路配置

2023-10-26 15:30:51 483

483

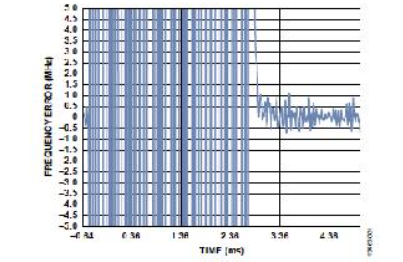

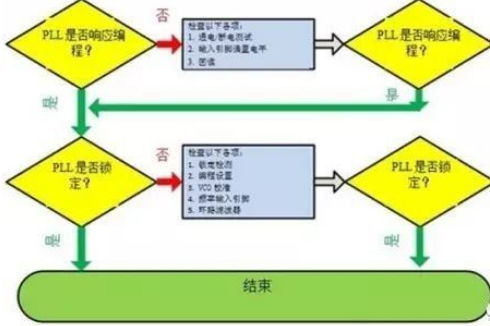

按照上述步驟校準完成后,PLL 的反饋操作使 VCO 鎖定于正確的頻率。鎖定速度取決于非線性周跳行為。PLL總鎖定時間包括兩個部分:VCO頻段校準時間和PLL周跳時間。VCO頻段校準時間僅取決于PFD頻率;PFD頻率越高,鎖定時間越短。

2018-05-18 08:35:20 5327

5327

本文以高度集成的解調器和頻率合成器 ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。

2018-05-22 09:00:04 4813

4813

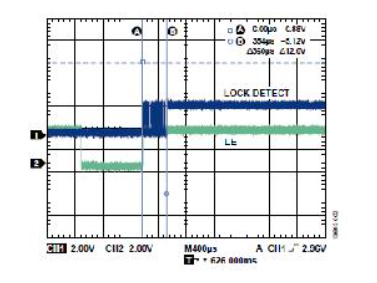

PLL鎖定指示電路該如何設計?

2019-07-30 07:40:35

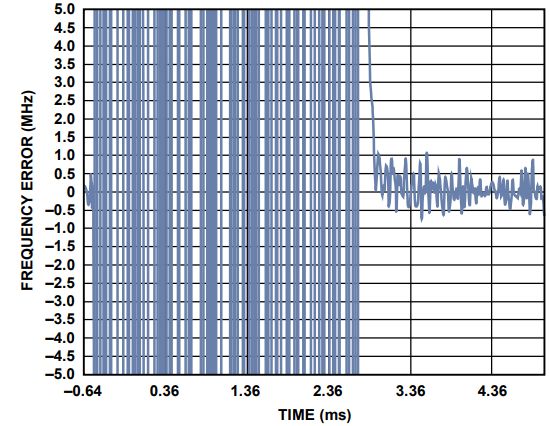

你知道嗎?利用手動頻段選擇,鎖定時間可從典型值 4.5 ms 縮短到典型值 360 μs。本文以高度集成的解調器和頻率合成器 ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間

2018-11-01 10:42:37

的雙頻率合成器電路LMX2335,其最高工作頻率1.1 GHz。3.2.2 工作頻率計算 以短波頻段(2 MHz~30 MHz)為例,第一本振輸出頻率為: 考慮到環路的鎖定時間,LMX2335

2011-07-16 09:09:54

PLL數字調臺的頻率穩定性是占絕對優勢的。因為它幾乎僅僅取決于基準頻率(晶體振蕩)的穩定性。 手動調諧的優點亦是顯而易見的:簡單!簡單到甚至不需電源就能做出收音機。至于產品的易用性則各有千秋

2010-12-25 10:26:40

作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要

2018-08-29 16:02:55

輸出? 問題2:回讀ox22c=0xe6,顯示PLL1未鎖定,各位原來9524的PLL1沒鎖定的,最后都是怎樣鎖定的?

2018-09-28 15:00:08

Vcm = 0.4V,REFCLK=120MHz,幅度680mV,8倍內插,PLL時鐘2不能鎖定,N1為4,N2為4,可能會是哪里的問題?reg08寫成自動模式,讀出數據為000000,始終不能鎖定,會是哪里的問題?

2024-01-26 07:50:02

Select'設置為6'b111111來啟動自動搜索功能;但內部PLL無法鎖定,再查詢0x08寄存器高6bit,顯示值又回到了6'b000000。

我手動將

2024-01-15 07:00:26

我參考時鐘100MHz,SYNC_CLK在旁路PLL時輸出6.25MHz,說明時鐘是沒問題的,但在使能PLL后輸出異常,SYNC_CLK輸出25MHz,推算VCO=25*16=400MHz,不合理

2023-12-06 06:27:34

Vp電壓=+5V,當ADF4001未鎖定時,CP輸出是什么,此時A點的電壓是多少?附件PLL無源濾波.bmp745.9 KB

2018-12-11 09:22:21

[/td][td]本人最近調試ADF4350,發現鎖定時間達不到要求,但是看數據手冊中的例子,發現理論上應該可以達到我的要求,(If a PLL has reference frequencies

2018-11-28 09:09:00

需要哪款資料,請移步至 https://ezchina.analog.com/thread/18148 取走解決方案:ADI 鋰離子電池測試設備解決方案應用筆記:手動選擇頻段以縮短PLL鎖定時間用于

2018-04-29 11:18:57

可以自己調整過來,并重新鎖定時鐘,獲得正確的時鐘輸出;但是,若PLL的輸入時鐘頻率較之原來設定的時鐘頻率變化較大時(比如,PLL輸入時鐘頻率由50MHz變為200MHz),PLL將無法重新鎖定時鐘,其輸出時鐘頻率將變為不確定的值。[hide][/hide]

2009-12-22 11:27:13

CC2530縮短發送時間間隔就失敗報錯,怎么解決?在調試CC2530的時候,采用協議棧中的SAMPLEAPP_SEND_PERIODIC_MSG_EVT事件定時發送。每次發送500字節。當我縮短

2016-03-29 10:19:42

(1.28Gbps))。所以我有6個PLL。我的GTP設計是完全對稱的。只有一個MGT_USRCLK模塊的PLL(PLL0)被鎖定,另一個(PLL1)被鎖定一小段時間,然后再被鎖定一小段時間再重新鎖定一小段時間等等

2019-06-19 11:27:42

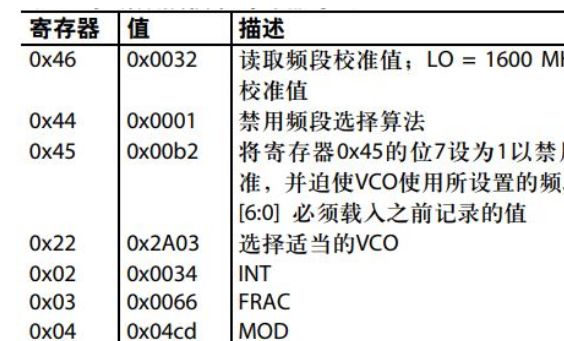

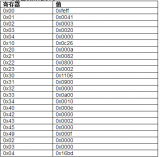

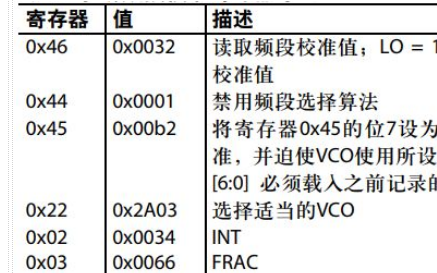

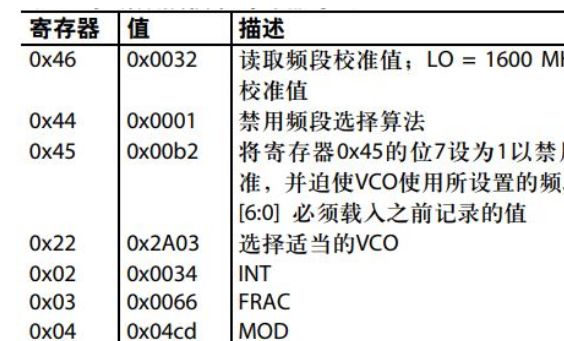

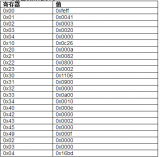

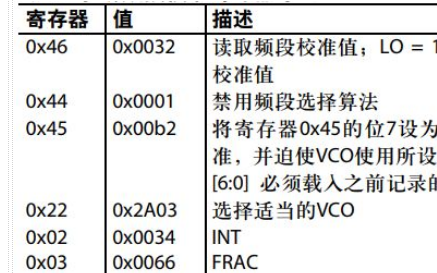

使用HMC830的快鎖功能,先自動鎖定,回讀出鎖定時對應的VCO段值,并記錄此時的調諧電壓。然后切換到手動鎖定模式,將自動鎖定回讀出的段值置入VCO的寄存器,再次記錄調諧電壓。發現在同一頻點同一

2018-08-22 09:53:46

”方法:以鎖定“導線”為例:按shift + F選擇任意導線,彈出“Find Similar Objects ”對話框(發現相似目標),設定好過濾參數,也即適用范圍等,點“應用”,可查看是否選擇正確

2016-01-12 20:30:17

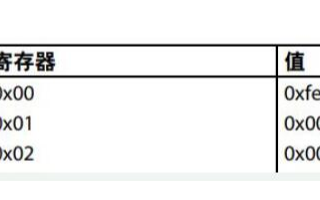

你好,我一直在用戶電路板設計上使用ST25RU3993,但尚未成功鎖定PLL。我試圖手動和使用auto命令設置VCO范圍。我嘗試了各種載波頻率/基頻/參考頻率設置的組合。在嘗試解決問題時,我注意到

2019-08-12 10:09:46

于相位噪聲、鎖定時間或雜散卻并非如此。表1給出了環路帶寬對這些性能指標的影響的大致參考。 性能指標最優帶寬備注抖動BWJIT最優值一般為BWJIT。在低集成限制更高的一些情況下,有時較窄的環路帶寬實際上效果更好。鎖定時間無限VCO鎖定時間隨著環路帶寬的增加而提高,但有時會受到VCO校準時間…

2022-11-16 07:56:45

eHi親愛的社區希望你們中的一些人還在身邊。有誰知道我在哪里可以找到有關Virtex-6GTX CDR PLL鎖定時間的信息?我試圖在一段時間內使用GTX暫停模式,這樣它只在需要時突發數據包。因此

2019-11-06 06:23:58

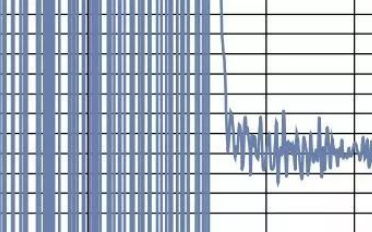

如何手動縮短PLL鎖定時間?你知道嗎?利用手動頻段選擇,鎖定時間可從典型值4.5 ms 縮短到典型值360 μs。本文以高度集成的解調器和頻率合成器ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。

2019-07-31 07:54:28

利用手動頻段選擇,鎖定時間可從典型值4.5 ms 縮短到典型值360 μs。本文以高度集成的解調器和頻率合成器ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。First,PLL

2018-08-04 15:00:17

發現代碼花費更多時間的函數是在 spi_device_polling_start() 調用的 spi_device_polling_start() 中啟動傳輸(由 spi_device_polling_transmit()。我的問題是,如何縮短事務之間的時間以獲得更高的采樣率?

2023-03-02 08:32:25

發現代碼花費更多時間的函數是在 spi_device_polling_start() 調用的 spi_device_polling_start() 中啟動傳輸(由 spi_device_polling_transmit()。我的問題是,如何縮短事務之間的時間以獲得更高的采樣率?

2023-04-14 06:58:22

基于PLL的XO進行頻率編程如何進行?如何為定時應用選擇合適的基于PLL的振蕩器?

2021-04-02 06:39:04

范圍。這一突破消除了為在特定頻率實現共振而切割和加工石英所需的材料加工工藝步驟。這一創新也使得對基于PLL的XO進行頻率編程成為可能并且實現極短交貨周期。那么,如何才能為定時應用選擇合適的采用PLL的振蕩器呢?

2019-07-31 06:49:45

矢量幅度(EVM),頻譜分析儀依賴于具有快速鎖定時間的本振來實現快速頻率掃描,高速轉換器需要低抖動時鐘以確保高SNR性能。圖1.(a) PLL、(b) 轉換環路、(c) DDS的簡化框圖ADI公司提供

2022-03-14 16:17:39

假設您已經通過迭代信息傳遞相位邊限和回路帶寬在鎖相環(PLL)上花費了一些時間。但遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數?

2019-07-31 07:26:15

親愛的大家,是否有人可以提供GTX火箭I / O鎖定時間的參考編號?謝謝羅伯托

2020-06-08 11:57:50

你知道測量PLL鎖定時間的方法有哪幾種嗎?

2021-05-10 07:11:05

輸出頻率的子帶。該過程需要切換時間,在此期間開環輸出頻率可以處于各種不同的頻率。該頻段選擇切換時間也被添加到PLL鎖定時間,PLL鎖定時間本身是PLL環路濾波器帶寬的函數。ADF4350在VCO之后

2018-10-26 11:48:38

本文將重點介紹瞬態分析功能在脈沖、跳頻及PLL頻率鎖定時間測試中的應用。

2021-06-17 10:37:30

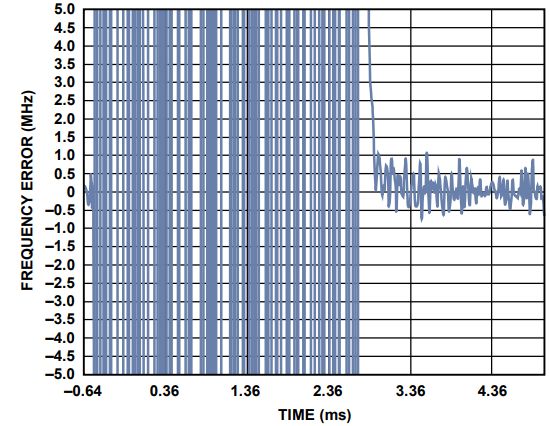

PFD頻率與環路帶寬的比值提高,周跳也會增加;對于給定PFD周期,提高環路帶寬會縮短周跳時間。因此,當使用自動校準模式時,總鎖定時間對某些應用來說可能太長。本應用筆記提出一種通過手動選擇頻段來顯著縮短

2018-10-31 10:16:46

最近單位有一個項目,打算使用AD9364,通信方式采用MF-TDMA,因此對AD9364的鎖定時間比較關心,查看了資料,發現AD9364資料中的鎖相環鎖定時間沒有提供,請問有知道AD9364的鎖定時間具體是多少么。我們要求鎖定時間最大不能超過200us,不知道AD9364能不能滿足要求呢,謝謝

2018-10-10 11:22:55

使用ADF4351設計了一個頻率源,頻率范圍1200M-2500M,步進1M,要求跳頻時間控制在50us內,通過實際測試只能到100us。現在想知道ADF4351最快的頻率鎖定時間是多少啊?如果可以達到的話,應如何設置寄存器?參考頻率100M,鑒相頻率25M,環路帶寬為250K。

2018-10-11 09:21:28

pcb板手動布線鎖定以后怎么解除鎖定

2019-07-04 05:35:12

大家好,目前客戶評估HMC830做快速跳頻源,目前評估的是HMC830的鎖定時間能否達到10uS。想咨詢一下HMC830的鎖定時間能夠達到10uS以內呢?我們手頭有HMC830的評估板,如何設置HMC830才能做到快速鎖頻呢?謝謝

2018-09-27 14:12:46

從ADF5355的芯片資料上看,其鎖定時間很長,超過2.75ms。不知道資料有沒有問題?請問各位用過該芯片的大佬,其實際頻率鎖定時間是否需要這么長?是否有辦法加快其鎖定?謝謝!

2018-09-27 11:15:02

[/td][td]本人最近調試ADF4350,發現鎖定時間達不到要求,但是看數據手冊中的例子,發現理論上應該可以達到我的要求,(If a PLL has reference frequencies

2023-11-27 07:20:06

手動選擇頻段以縮短 PLL 鎖定時間——ADRF6820

2021-01-21 06:24:47

本文對電荷泵型鎖相環(CPPLL)結構里傳統的固定電荷泵電流模式進行了改進,有效減少了鎖相環系統的鎖定時間。本文提出的PLL設計,在0.6μm標準CMOS工藝、3.3V工作電壓下,使用應用

2010-08-03 16:10:33 21

21 對2.5GHz PLL鎖定檢測電路進行一定層次的正向設計,在此

2010-10-29 17:07:27 0

0 電鎖定時自停報信電路圖:此電路的定時可接電鍍工藝要求進行調節,預置時間到,便自動停機,并發出報警衛音響,以便安排工作。

2007-12-14 08:08:30 472

472

本內容詳細介紹了三階電荷泵鎖相環鎖定時間的研究,歡迎大家下載學習

2011-09-16 16:37:49 21

21 ADF4xxx系列PLL頻率合成器的鎖定檢測

2011-11-29 15:37:17 38

38 假設您已經通過迭代信息傳遞相位邊限和回路帶寬在鎖相環(PLL)上花費了一些時間。但遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數?

2017-03-06 17:59:26 3142

3142

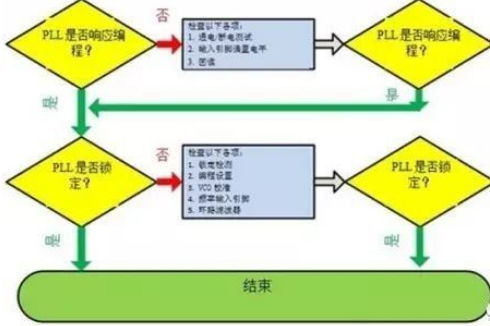

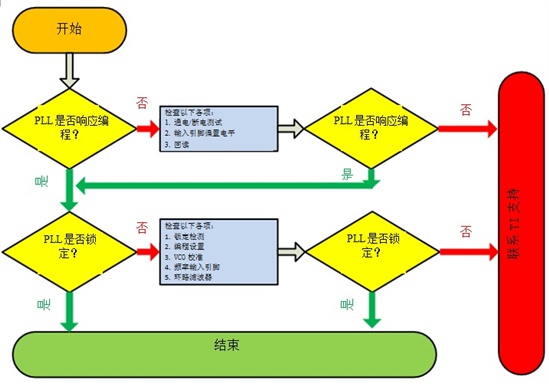

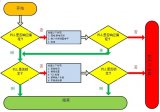

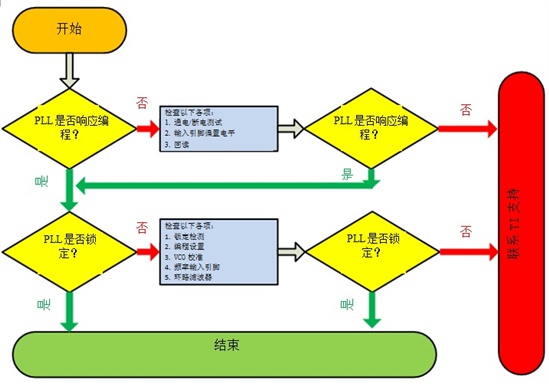

在嘗試將鎖相環(PLL)鎖定時,你是否碰到過麻煩?草率的判斷會延長調試過程,調試過程變得更加單調乏味。根據以下驗證通行與建立鎖定的程序,調試過程可以變得非常簡單。第 1 步:驗證通信 第一步是驗證PLL響應編程的能力。如果PLL沒有鎖定,無法讀回,則嘗試發送需要最小量硬件命令工作的軟件命令。

2017-04-08 01:56:13 881

881

在嘗試將鎖相環(PLL)鎖定時,你是否碰到過麻煩?草率的判斷會延長調試過程,調試過程變得更加單調乏味。根據以

2017-10-16 11:49:30 5147

5147

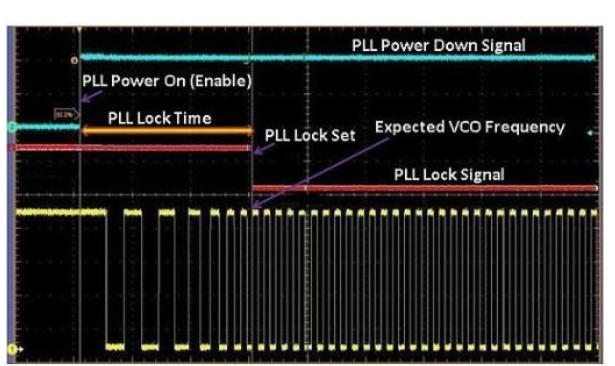

當PLL參考時鐘和PLL反饋時鐘的頻率和相位相匹配時,PLL則被稱為是鎖定狀態。達到鎖定狀態所需的時間稱為鎖定時間,這是PLL設計最關鍵的參數之一。

2018-03-14 15:17:00 6066

6066

PLL鎖定有那些檢測方法,它們特點是什么?一種是最為簡單的數字檢測,它利用輸入參考的分頻信號與VCO反饋的分頻信號,在PFD里鑒相的結果,通過連續結果時鐘周期檢測到鑒相的脈寬小于某值,作為鎖定的有效判決規則。這種檢測方式,判決方式簡單,判斷的結果只有鎖定和非鎖定兩種情況。

2018-03-14 16:37:00 4973

4973

校準完成后,PLL的反饋操作使VCO鎖定于正確的頻率。鎖定速度取決于非線性周跳行為。PLL總鎖定時間包括兩個部分:VCO頻段校準時間和PLL周跳時間。VCO頻段校準時間僅取決于PFD頻率;PFD頻率越高,鎖定時間越短。

2018-05-11 15:14:34 10847

10847

哈希鎖定模式是指用戶在規定的時間段對于哈希值的原值進行猜測來支付的一種機制。簡單講,就是在智能合約的基礎上,雙方先鎖定資產,如果都在有限的時間內輸入正確哈希值的原值,即可完成交易。

2019-09-10 10:56:55 3917

3917 你知道嗎?利用手動頻段選擇,鎖定時間可從典型值4.5 ms 縮短到典型值360 μs。本文以高度集成的解調器和頻率合成器ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間

2020-10-16 10:43:00 0

0 本文以高度集成的解調器和頻率合成器 ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。

2020-09-01 11:34:47 3041

3041

AN-873: ADF4xxx系列PLL頻率合成器的鎖定檢測

2021-03-21 09:34:20 6

6 時控開關鎖定屏幕:就是把屏幕給上鎖,無法對時控開關進行手動控制,以及修改刪除定時時間。

2021-10-18 17:21:07 847

847 在嘗試將鎖相環(PLL)鎖定時,你是否碰到過麻煩?草率的判斷會延長調試過程,調試過程變得更加單調乏味。根據以下驗證通行與建立鎖定的程序,調試過程可以變得非常簡單。

第1步:驗證通信

第一步是驗證

2021-11-26 16:32:38 5146

5146

作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要

2022-01-11 16:00:28 2150

2150 對開關進行無線控制,可以手動控制開、關,也可以設置定時時間實現自動開、關。設置定時時間范圍1秒鐘到168小時(一個星期),最多可以設置30組定時時間,且具有斷電記憶功能,斷電再次來電按照之前設置的定時進行開關,不用重

2022-04-22 16:31:41 10944

10944 ADRF6820是一款高度集成的解調器和頻率合成器,非常適合用于高級通信系統。 它內置一個寬帶I/Q解調器、一個小數N/整數N分頻鎖相環(PLL)以及一個低相位噪聲多核壓控振蕩器(VCO)。

2022-08-09 11:23:17 969

969

對定時器進行無線控制。可以控制手動開、關,也可以設置定時時間進行自動開、關。 時間定時器開關怎樣接線? 使用時間定時器開關控制功率小于1320W的用電器。 1.220V市電接入空氣開關,空氣開關火零線接在時間定時器開關左側的進線口

2022-09-28 11:47:53 6543

6543 發現抖動、相位噪聲、鎖定時間或雜散問題?請檢查鎖相環的環路濾波器帶寬

2022-11-02 08:16:24 15

15 作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要做的仍是尋找最優環路帶寬。

2023-04-12 10:32:17 1950

1950

pll鎖定時間按照頻率精度多少來計算? PLL鎖定時間是指當PLL嘗試將輸出頻率與輸入頻率相匹配時所需的時間。這個時間可以用來衡量PLL的性能,因為它決定了PLL能否快速、準確地鎖定頻率,并且

2023-09-02 15:12:23 811

811 鎖相環(PLL)基本原理 當鎖相環無法鎖定時該怎么處理的呢? 鎖相環(Phase Locked Loop, PLL)是一種電路系統,它可以將輸入信號的相位鎖定到參考信號的相位。在鎖相環中,反饋回路

2023-10-23 10:10:15 1354

1354 鎖相環鎖定時間取決于哪些因素?如何加速鎖定? 鎖相環(PLL)是一種常見的電路,用于穩定頻率。PLL中的關鍵是相鎖。相鎖發揮著將輸入頻率與參考頻率調整到相等的重要作用。在鎖相環設計中,鎖定時間

2023-10-30 10:51:18 899

899 到芯片邏輯的正確運行。在測試PLL IP時,通常會有多個測試項目,如頻率測試、相位噪聲、鎖定時間、穩定性、誤差和漂移等。 但在SoC的ATE測試中,CP階段通常只進行PLL頻率和鎖定測試。 那么DFT

2023-10-30 11:44:17 662

662

電子發燒友App

電子發燒友App

評論