現(xiàn)在有很多不同的模數(shù)轉(zhuǎn)換器 (A/D) 可用,您不必成為模擬信號鏈專家就可以選擇一個。嗯……也許也許不是。你的選擇是什么?

有獨立的(或離散的)A/D,通常從 8 位到 24 位不等,甚至還有一些 32 位選項。A/D 也集成到微控制器、FPGA、微處理器或 SoC 中。有逐次逼近寄存器 (SAR) A/D 和 sigma-delta 版本。當(dāng)需要最高采樣率時使用流水線 A/D。一些 A/D 的采樣速度約為 10 s/s,而一些則遠高于 1 Gs/s。A/D 的價格從不到 1 美元到 265 美元不等,甚至更高。

速度、力量和準(zhǔn)確性有多重要?為了幫助您為您的應(yīng)用選擇正確或最佳的 A/D,我們將仔細研究這些不同的類型并解釋它們的最佳操作條件。

SAR A/D——用于中等速度和快照數(shù)據(jù)

SAR A/D 提供廣泛的比特和速度。從 6 位或 8 位到多達 20 位,SAR A/D 通常在幾 ks/s 到多達 10 Ms/s 之間運行。SAR A/D 是電機控制、振動分析和系統(tǒng)監(jiān)控等中速應(yīng)用的理想選擇。這些不如流水線 A/D 快(下文討論),但它們通常比 delta-sigma A/D 快(也將在下文討論)。

SAR A/D 直接根據(jù)采樣率調(diào)整功耗。例如,在 1 Msps 時耗散 5 mW 的芯片通常在 1 ksps 時僅耗散 5 μW。因此,SAR A/D 非常靈活,客戶可以為多種應(yīng)用存儲一個零件編號。

SAR A/D 還有另一個優(yōu)勢:它們對模擬輸入信號進行“快照”。SAR 架構(gòu)只對一個時刻進行采樣。設(shè)計師什么時候會想要這個?當(dāng)您需要同時測量多個信號時,您可以使用多個單個 SAR A/D 進行同時采樣,或者使用帶有多個 A/D 或內(nèi)部多個跟蹤保持 (T/H) 內(nèi)核的同時采樣 A/D它。這允許系統(tǒng)同時測量多個模擬輸入。

電流和電壓互感器將 SAR ADC 用于保護繼電器應(yīng)用。在這里,客戶同時測量不同的電流和電壓相位。電力公司就是一個很好的例子。有了精確的快照數(shù)據(jù),公用事業(yè)公司就可以準(zhǔn)確地知道電線上的情況以及如何最有效地管理電網(wǎng)。

Sigma-Delta A/D——更高的準(zhǔn)確度

當(dāng)您需要更多采樣位的精度或確實需要最高有效位數(shù) (ENOB) 時,sigma-delta A/D 通常是最佳選擇,尤其是對于低噪聲精度應(yīng)用。當(dāng)速度不那么重要時,sigma-delta A/D 的過采樣和噪聲整形可提供非常高的精度。

隨著 SAR A/D 市場在 5 到 10 年前開始趨于飽和,許多模擬公司投資于多個 sigma-delta 內(nèi)核。今天的結(jié)果是非常好的高達 24 或 32 位的 A/D,采樣率在 10 s/s 到幾 Ms/s 之間。

哪些應(yīng)用可能需要 > 20 位的無噪聲分辨率?儀表裝置和氣相色譜儀或石油和天然氣行業(yè)是典型的應(yīng)用示例,它們通常需要盡可能多的位精度。這些系統(tǒng)應(yīng)用為精密模擬信號設(shè)定了基準(zhǔn),在這些應(yīng)用中,最終用戶必須絕對確定他們的數(shù)據(jù)——確切地說有 多少低硫原油或天然氣正在流動。

調(diào)制器與否?

最近,sigma-delta A/D 在速度和采樣率方面變得更加難以分類。傳統(tǒng)的 sigma delta 在內(nèi)部完成所有數(shù)字后處理(例如,使用 SINC/陷波濾波器、抽取和噪聲整形)。從那里,數(shù)據(jù)以非常好的 ENOB 串行發(fā)送出去。例如,如果您有一個 24 位 A/D,則數(shù)據(jù)輸出包括 24 位。第一位輸出是最高有效位 (MSB),第 24位 是最低位。您的數(shù)據(jù)輸出速率通常是串行時鐘速率除以 24。這些不是最快的,也不是最靈活的 A/D。

然而,在過去的 5 到 10 年中,sigma-delta 調(diào)制器變得越來越流行,特別是在需要大量速度(通常約為 1 Ms/s 或更高)的應(yīng)用中。sigma-delta 調(diào)制器不是等到完整的 24 位輸出被抽取,而是一次一位地輸出數(shù)據(jù),然后將數(shù)字濾波留給處理器或 FPGA 進行分析。

這種調(diào)制器的靈活性對于電機控制等應(yīng)用很有幫助,其中 12 到 16 位可能就足夠了。如果前 16 位提供足夠量的模擬測量,則電機控制器可能不需要或不想等待 24 位數(shù)據(jù)流中的最后 8 個 LSB。

選擇 SAR 與 sigma delta - 決定因素是速度

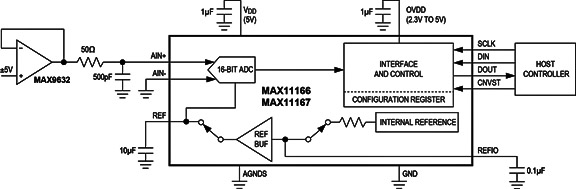

輸入過濾器是另一個重要的考慮因素。回想一下 SAR 架構(gòu)拍攝高速快照。當(dāng)應(yīng)用程序推動更高的采樣率時,輸入濾波器變得更加復(fù)雜。通常,需要一個外部緩沖器或放大器來驅(qū)動輸入電容器并在短時間內(nèi)穩(wěn)定下來,并且放大器必須具有足夠的帶寬。圖 1 顯示了使用 16 位、500 ks/s MAX11166 SAR A/D 的示例。位數(shù)越高,采樣率越快,輸入必須穩(wěn)定并獲得正確輸入讀數(shù)的時間常數(shù)就越短。

在圖 1 中,使用了具有 55 MHz 增益帶寬的 MAX9632 放大器,其后接一個簡單的 RC 濾波器。這種特殊的放大器提供 < 1nV/root-Hz 的噪聲,因此可以從系統(tǒng)中獲得每十分之一 dB 的 ENOB。

圖 1:SAR A/D 轉(zhuǎn)換器輸入濾波器示例顯示了具有 55 MHz 增益帶寬的 MAX9632 放大器驅(qū)動輸入。

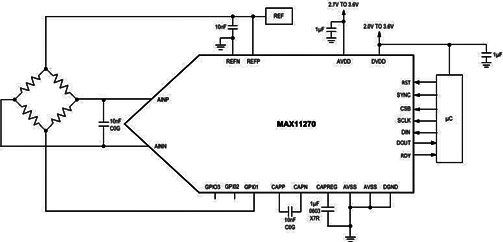

與 SAR A/D 相比,delta-sigma 中的輸入被過采樣多次,以至于抗混疊濾波器的要求沒有那么嚴格。通常,一個簡單的 RC 濾波器就足夠了。圖 2 是 MAX11270 24 位、64 ksps Σ-Δ A/D 示例。這里顯示了一個惠斯通電橋示例,差分輸入端有一個 10 nF 電容器。 ?

圖 2. Sigma-delta ADC (MAX11270) 輸入濾波器示例只需要一個簡單的外部 RC 濾波器。

流水線 A/D——用于超快速采樣

在介紹中,我們提到了流水線 A/D 對于最高采樣率(如射頻應(yīng)用和軟件定義無線電)的重要性。在過去的 10 年里,頂級模擬公司一直在大力投資研發(fā)流水線 A/D。

當(dāng)然,流水線 A/D 的前兩個品質(zhì)因數(shù)是速度和功率。采樣率在大約 10 Ms/s 到幾 Gs/s 之間,這些設(shè)備的接口變得非常關(guān)鍵。流水線 A/D 的下一個大戰(zhàn)場很可能是基于它們的數(shù)字輸出。并行數(shù)字接口一直是首選接口。串行 LVDS 接口已用于具有大量通道且采樣率在 50 到 65 Ms/s 之間的應(yīng)用中,例如超聲,歷來就足夠了。但是,有新的接口。

JESD204B 串行接口

JESD204B 串行接口是一種高達 12.5 Gbits/s 的高速串行標(biāo)準(zhǔn)。這種接口是近年來出現(xiàn)的,它使 A/D 制造商的采樣率越來越高,F(xiàn)PGA 和處理器公司的串行收發(fā)器(或 SerDes)也是如此。

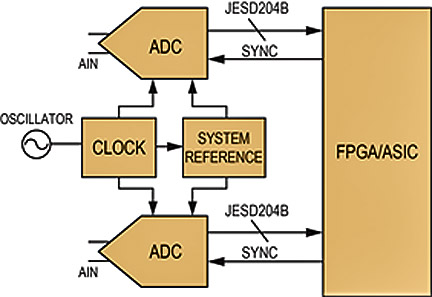

在具有許多并行 A/D 的多通道應(yīng)用中,A/D 和 FPGA/處理器之間的老鼠窩布線是一件很麻煩的事。使用 JESD204B 串行接口,數(shù)據(jù)線的數(shù)量顯著減少,電路板空間得以保留。圖 3顯示了該接口的單個??串行輸出對和一個同步輸入,這大大減少了所需的 I/O 引腳數(shù)量。

* 調(diào)制器輸出速度

圖 3:JESD204B 串行接口大大減少了 A/D 和 FPGA/處理器之間的數(shù)據(jù)線數(shù)量。

請注意,近年來有關(guān) JESD204B 的文章很多,更深入的細節(jié)最好在此處找到。

流水線 A/D 的關(guān)鍵功耗問題

現(xiàn)在,更多的 A/D 可以封裝在狹小的空間中,功耗就變得更加重要,領(lǐng)先的 A/D 制造商一直在努力降低功耗。一個好的規(guī)則是每 1 Ms/s 1 mW。如果您的 A/D 接近這一點,那么您有一個很好的起點。

針對 MCU、FPGA、CPU 和 SoC 優(yōu)化的 A/D

集成到微控制器中的 A/D 通常不是最高質(zhì)量的。從歷史上看,當(dāng) 12 位 A/C 嵌入到微控制器中時,就有效位數(shù) (ENOB) 或線性而言,它更有可能像 8 位 A/C 一樣執(zhí)行。為了確保足夠的 A/D 性能,用戶必須仔細查看規(guī)格并確定哪些是有保證的。僅看到典型規(guī)格或列出的條件不完整的最小和最大規(guī)格并不少見。

最近,積分非線性 (INL)、微分非線性 (DNL)、增益誤差和 ENOB 等 A/D 性能已經(jīng)提高到足以在 MCU 中實現(xiàn)質(zhì)量性能,并且集成 A/D 的微控制器數(shù)量大幅增長。如今,如果應(yīng)用需要 12 位或更少且只有幾個通道,MCU 可能是最具成本效益的解決方案。

FPGA 制造商也開始將 A/D 集成到他們的系統(tǒng)中。例如,Xilinx 在其所有 7 系列 FPGA 和 Zynq SoC 中提供 12 位、1 Ms/s A/D。MCU 或 SoC 在電路板上的位置至關(guān)重要。帶有 FPGA 或 SoC 的 CPU 模塊可能與模擬輸入信號相距甚遠——模擬輸入信號可能位于完全獨立的卡上,高速數(shù)字背板將兩者連接起來。您不想通過這樣的連接路由敏感模擬,因此在這種情況下集成 A/D 可能不是一個好主意。這就是您肯定想要一個好的離散 A/D 的地方,其中 24 位 sigma-delta A/D 是可編程邏輯控制器 (PLC) 等應(yīng)用中最常見的選擇。

以 PLC 為例,隔離是另一個需要考慮的因素。大多數(shù) PLC 模擬輸入包括某種形式的隔離,通常是數(shù)字的。許多模擬輸入模塊將集成低成本的微控制器以實現(xiàn)快速響應(yīng)和快速中斷。現(xiàn)在,隔離的位置決定了內(nèi)部 A/D 是否可行。如果隔離位于處理器(或 MCU)和背板之間,那么集成到微控制器中的 A/D 就是您的朋友。如果 MCU 需要與高壓輸入信號隔離,那么分立 A/D 和數(shù)字隔離器是最佳解決方案。

你最好的選擇是什么?

我們已經(jīng)討論了今天可用的幾種 A/D 選項,那么最初的問題呢:您正在測量的信號的速度、功率和精度有多重要?

如果您只需要一個簡單的低分辨率讀數(shù)來執(zhí)行管理功能,MCU、FPGA、處理器或 SoC 中的集成 A/D 可能就可以完成這項工作。如果您的應(yīng)用是低速(接近直流),例如緩慢移動的溫度信號,那么 sigma-delta A/D 可能是最好的。如果您有一個相當(dāng)快的信號,例如以 1,000 RPM 嗡嗡作響的電機的振動分析,那么 SAR A/D 可能是最好的。如果應(yīng)用程序必須測量世界上最快的模擬信號,那么流水線 A/D 是最佳選擇。

所有這一切的共同主題是“視情況而定”。沒有工程師喜歡聽到這個。如果您是負責(zé)挑選正確 A/D 的數(shù)字設(shè)計師或電源專家,您更喜歡更明確的說明。但 A/D 通常是復(fù)雜、細致入微的 IC,需要研究數(shù)據(jù)表和評估套件。表 1 總結(jié)了當(dāng)今市場上 A/D 的典型最小和最大規(guī)格。可以肯定的是,這是一個不斷變化的格局。明年我們將在這里改變什么?

表 1:典型 A/C 轉(zhuǎn)換器規(guī)格范圍

| A/D 架構(gòu)/規(guī)格 | 采樣率/速度 | 分辨率/位 | 價格 | 力量 |

| 特區(qū) | 直流至 10 毫秒/秒 | 8 到 20 | 低到中 | 最低每 ks/s |

| 西格瑪三角洲 | 直流至 20 毫秒/秒* | 16 至 32 | 低到中 | 低到中 |

| 管道 | 10 毫秒/秒至 5 克/秒 | 8 至 16 | 最高 | 最高 |

| 集成在 MCU/FPGA/SoC 中 | 直流至 1 毫秒/秒 | 8 至 16 | 最低 | 低到中 |

電子發(fā)燒友App

電子發(fā)燒友App

評論