眾所周知,ADC主要用于對模擬信號進行數字采集,以進行數據處理。 我們周圍的信號一般都是不斷變化的模擬量,如光、溫度、速度、壓力、聲音等。 然而,我們大多數人都使用數字設備。 如果我們想方便地使用和處理信息,就需要將模擬量轉換為數字量,并傳送到微控制器或微處理器。 那么ADC轉換是如何實現的呢? 這是一個什么樣的過程? 閱讀下面的筆記,你一定會對模數轉換器有更全面、更系統的了解。

各位同行們,大家好啊,今天又來給大家分享ADC方面的學習筆記啦,聽聞上一篇筆記大家都挺滿意呢,那么這一次還是希望大家喜歡哦。

一、ADC的參數

1、分辨率

就是最小能夠分辨的模擬電壓值,例如12位ADC,Vref為3.3V最小分辨率即:Vref/2的12次方=0.8mv。

2、轉換速度

即每秒轉換的數字量,例如100kSPS,也常表示為每個數字量的轉換時間如15us

3、輸出接口

有串行或者并行接口

4、工作電壓,基準電壓(內部或者外部基準),封裝。

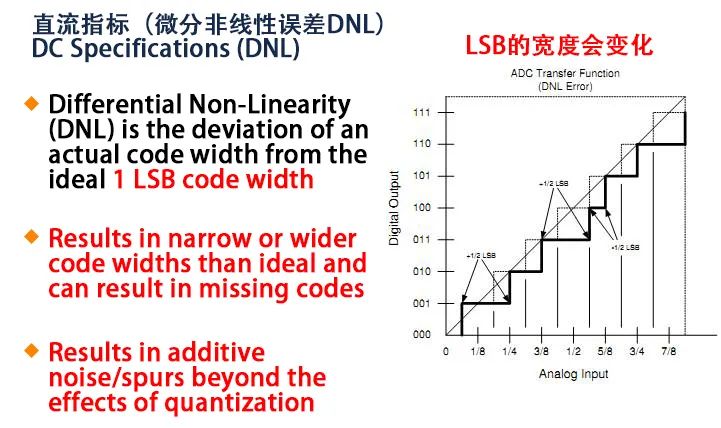

5、DNL 微分非線性誤差

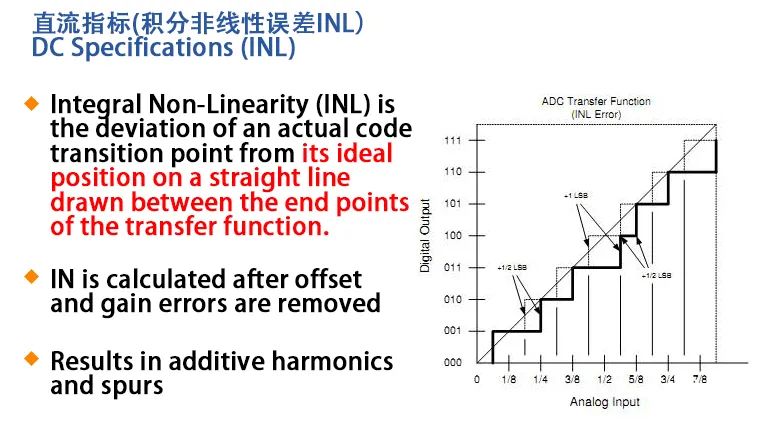

6、INL積分非線性誤差

這兩種誤差具有一定隨機性,因此ADC會出現誤碼。

7、幾種重要的交流參數

二、信噪失真比與有效位數 (ENOB)

采樣是利用模擬開關將連續變化的模擬量變成離散的數字量,由于經采樣后形成的數字量寬度較窄,經過保持電路可將窄脈沖展寬,形成梯形波。 量化是將階梯形模擬信號中各個電壓值轉化為某個最小單位的整數倍,便于用數字量來表示。 編碼是將量化的結果(即整數倍值)用二進制數碼來表示。 這個過程則實現了模數轉換。

分辨率與動態范圍

N, DR

ADC分辨率為用于表示模擬輸入信號的位數。

為了更準確地復現模擬信號,須提高分辨率,使用較高分辨率的ADC也降低了量化誤差。 但成本就上去了。

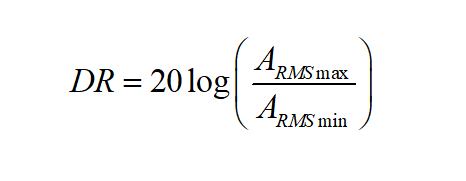

動態范圍(DR)定義為器件本底噪聲至其規定最大輸出電平之間的范圍,通常用dB表示。 ADC的動態范圍是指ADC能夠分辨的信號幅值范圍; ADC的分辨率位數(N)決定ADC的動態范圍,代表ADC可測量的輸入信號等級范圍,DR可定義為:

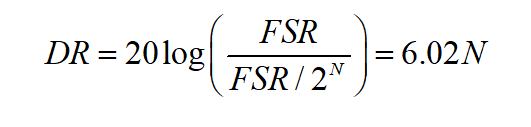

由于信號在給定時間視窗內的RMS幅值取決于信號幅值在該時間視窗內如何變化,因此ADC的DR變化取決于輸入信號特征。 對于其滿量程范圍(FSR)內的恒定DC輸入而言,理想的N位ADC可分別測量FSR和FSR/2N的最大及最小RMS幅值。 因此,ADC的DR為:

對于正弦波信號輸入而言,正弦波輸入信號的最小可測量RMS幅值受量化誤差的限制,正弦波輸入信號的理想ADC的DR是:

DR=6.02N+1.76dB

假設ADC的動態范圍為60dB,則其可分辨的信號幅值為x至1000x。 通常動態范圍非常重要,因為如果信號太大,則會造成ADC輸入過量程; 如果信號太小,則會被淹沒在轉換器的量化噪聲中。

信噪比與信噪失真比

信噪比, 信噪比

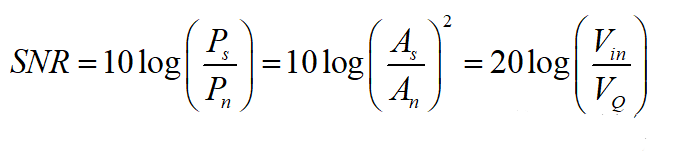

數模轉換器的信噪比(SNR)是指輸入信號功率與噪聲功率的比值,這里用來量化數據轉換器內的噪聲,SNR也能使用信號幅度和噪聲幅度的RMS值來衡量,以dB為單位。

在滿刻度正弦波輸入的條件下,ADC的理論最高SNR從量化噪聲推導而得,表達式為:

信噪比=6.02N+1.76dB

這里N是理想ADC的位數,對于理想的N位數據轉換器(不考慮諧波失真)的正弦波輸入,整個奈奎斯特帶寬上能達到的最佳SNR。

但對于實際的ADC,除了量化噪聲,數據轉換器的SNR也會受到自身熱噪聲和采樣時鐘相位噪聲的限制。 噪聲來自主要有三個源頭:

? 量化噪聲

? ADC熱噪聲

? 抖動或采樣不確定噪聲

信號與噪聲失真比(Signal to Noise And

Distortion,SINAD)指輸入正弦波時,RMS信號功率與總噪聲功率和輸出端(不含DC)的所有其他頻率分量功率加上所有其他諧波分量功率的RMS和的比值。

SNDR是用于衡量數據轉換器的動態性能的關鍵參數之一,它包含奈奎斯特帶寬上的所有噪聲和雜散。 SNDR的表達式為:

其中,信號功率是有用信號、噪聲和失真分量的平均功率。 SNDR的單位是分貝(dB),SNDR將所有不良頻率分量與輸入頻率做比較,反映的是輸入信號的質量,從總體上衡量數據轉換器的動態性能。 SNDR越大,輸入功率中的噪聲和雜散比率越小。

有效位數

伊諾布

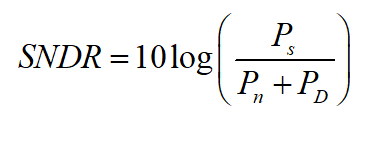

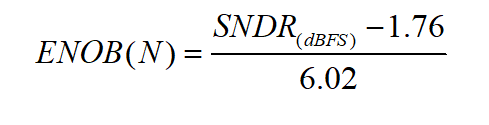

有效位數 (ENOB) 是用于衡量數據轉換器相對于輸入信號在奈奎斯特帶寬上的轉換質量(以位為單位)的參數。

這里的ENOB假定轉換器是擁有理論上完美性能,不發生失真,唯一產生的噪聲是量化噪聲,所以SNR 等于SNDR,即SNR(dBFS)=

6.02N+1.76dB。 因此,ENOB也是SNDR的另一種表達方式:

然而,對于非理想數據轉換器而言,SNDR和ENOB會發生劣化,包含噪聲和其他缺陷,例如器件熱噪聲、輸出代碼缺失、諧波、AC/DC非線性、增益/偏移誤差和孔徑時鐘相噪或抖動。 外部偏置基準源和電源軌上的噪聲也會降低ENOB。

總諧波失真(THD)測量信號的失真成分,用相對于基波的分貝(dB)表示。 對于ADC,總諧波失真(THD)是所選輸入信號諧波的RMS之和與基波之比。 測量時,只有在奈奎斯特限值之內的諧波被包含在內。

類似于THD因非線性原因隨輸入頻率增加而劣化,ENOB值也會隨頻率加大而劣化。 ENOB來自于SNDR,而SNDR又與THD以及SNR相關聯。 要了解數據轉換器的準確ENOB,需閱讀數據手冊中的詳細規格和規定的條件。

實際中的ENOB

大部分模擬數據轉換器IC廠商一般傾向于推廣理想條件下的ENOB,尤其是數據手冊標題所載的ENOB值。 然而,大量系統工程師和采購經理仍然好奇的是,為什么測量出的ENOB值和數據手冊所載的理想值不同?

實際使用中,由于ADC自身存在噪聲和誤差,其輸出不僅有量化噪聲,還有失真引起的高次諧波,因此從未能達到這一SNR值。 計算ADC的有效N:ENOB=(SNR–1.76)/6.02

dB。

假設器件是一款12位ADC,ENOB可能僅為10bit。 但需要注意的是這并不表示把ADC的后兩位刪掉就可以當成一個理想的10bit

ADC來使用,這里ENOB的意思是12bit非理想ADC的SNDR與理想的10bit ADC的SNR相等。

有關ENOB的一些理解要點:

? 一般數據轉換器數據手冊標題顯示的“位數”(12位或14位)指的是數字位或電壓分辨率。 這與ENOB無關。

? ENOB主要與噪聲、非線性和輸入頻率存在函數關系。

? ENOB會因多種外部不確定性因素(例如時鐘源、電源等)而劣化。

? ENOB是在整個奈奎斯特帶寬上(DC到fs/2)計算的。

知識點理解:無雜散動態范圍(SFDR)

大家在學習ADC的過程中一定有很多問題,我這邊也總結了一些學習中遇到的問題,現在分享給大家,希望能從中學習到一些有用的知識。

第一季度

對于ADC的參考電壓的rms噪聲要求是什么,是小于一個LSB就可以,還是跑train參考電壓noise vpp值小于一個LSB?

關于ADC的VREF的噪聲(或者波動),首先要區分是低頻還是高頻。 你們可以去看TI或者ADI的某些高精度(16Bit)ADC,VREF的溫度系數其實并不好,在全溫度范圍內VREF的偏差可能已經幾十個LSB了,這是為什么呢? 溫度對VREF的影響可以認為是一個低頻的噪聲源。 對于一個哪怕只有1MSPS的ADC,1s的時間,ADC將會處理100萬個數據。 “只要我的速度夠快,水晶的傷害就追不上我”。

對于高頻的噪聲,芯片內部很容易處理,濾波即可。 相較于噪聲,我們其實更加關注VREF的有限驅動能力,不管是片內BUFFER,還是外接VREF(封裝電感),VREF的有限驅動能力帶來的建立誤差的影響遠遠>VREF上噪聲的影響。

事實上,冗余的引入就是為了處理VREF以及CDAC網絡的有限建立精度問題的。

冗余和CDAC的開關序列(能耗)、CDAC陣列的具體情況(哪一步或者哪幾步需要的電荷較多)、比較器的轉換時間、VREF的驅動能力都息息相關,這些因素參雜在一起,相互制約

包括PVT Corner,不同的PVT下比較器的時間差異也很大,FF Corner下比較器的速度可能是SS

Corner下的50%都不到,比較器越快,對VREF的建立要求越高。 所以從VREF建立的角度,FF可能反而是最差PVT。

第 2 季度

異步的sar,說起來那么多好處,功耗低,速度快,面積也小。 那么pipeline還有什么競爭力呢? 那么同步sar的ADC目前在行業應用中又有什么前景呢?

>10bit的幾十M,幾百M的應用。 功耗面積肯定大很多。 高速SAR成熟以后,即便pipeline,最好也要pipeline-SAR吧高速SAR吃的是工藝進步的紅利,蠶食的是pipeline的部分應用領域。

第三季度

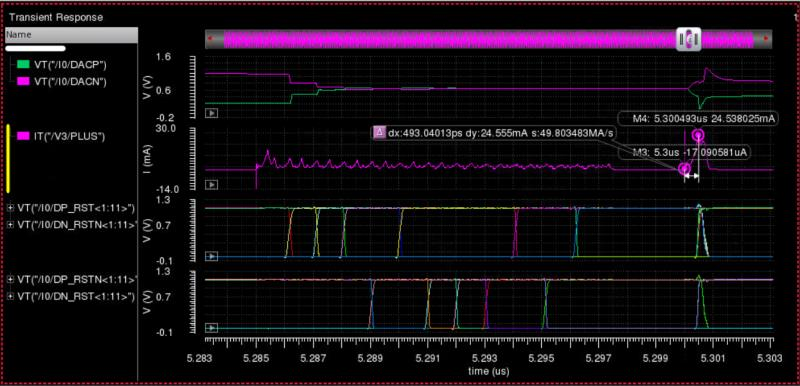

采樣開始,電容復位時,0.5ns內電源會被抽取25mA電流,采用內置LDO供電感覺有點困難吧,瞬態響應有點快。 對電源供電這塊是怎么考慮的呢?

不要光看毛刺電流,要看25mA毛刺電流持續的時間,或者說是電荷Q=I*t,這個電荷如果用一個電容C來提供,帶來的壓降是deltaV是多少. 電源地上加點decouple電容就行了,當然,電源上的ripple不可避免。

第 4 季度

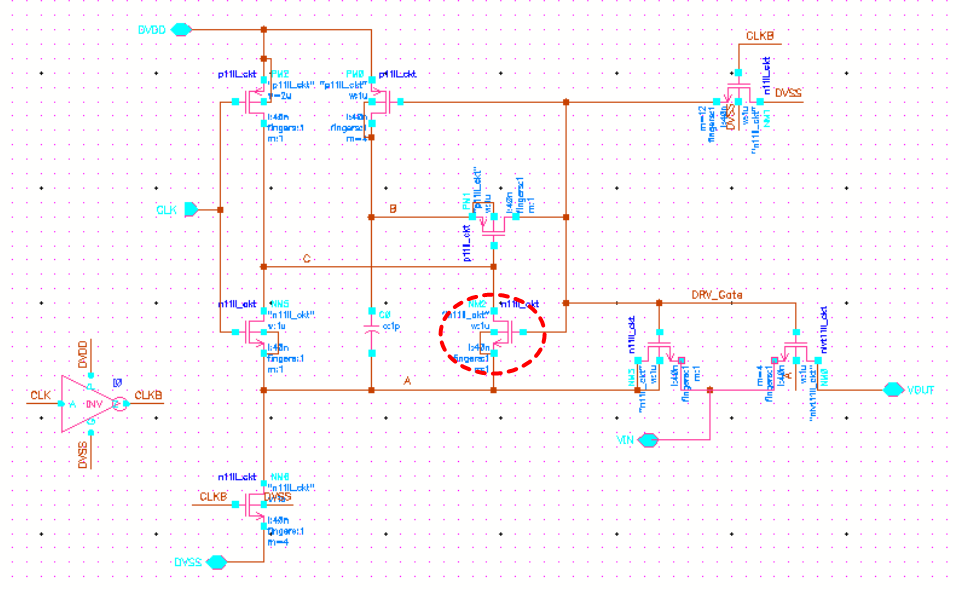

總感覺上圖紅圈中的器件沒啥用,對嗎?

這個管子的作用是當A點電位升高導致時NM5關斷時,能夠繼續給PM1提供導通電位。

我按照做好的電路搭了一個自己工藝的,感覺好像就可以工作了,我沒有使用帶DNW的工藝來做采樣開關,感覺也還行,我用的是0.18-5V的工藝,因為我主要是為了MCU的一個模塊用,不需要很高的速度,這個電路就跟老師說的,實在太小了,而且很多數字的電路,直接調數字單元庫也可以用。

問5a

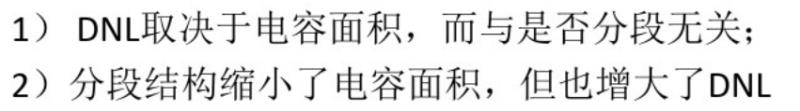

分段電容結構到底是改善了INL DNL還是惡化了,怎么對整個電容陣列進行建模?

分段并不會改善也不會惡化INL和DNL,前提是采樣電容不變的情況下,因為瓶頸在MSB上,分段本身不改變MSB的值,至于整個CDAC建模,把每個電容帶上隨機失配就可以了。

問5b

單位電容一定的情況下,分斷結構,降低了MSB總電容的個數,那么MSB電容總的偏差減小,按DNL INL提升了,這說法有問題嗎?

這個結論反了,如果單位電容一定的情況下,分段見笑了MSB電容個數,也就是減小了MSB電容的值,MSB的相對偏差變大,DNL和INL惡化,一般情況下,我們比較兩種情況下的DNL,需要基于一個前提,那就是MSB電容值不變。 有這個前提的話,DNL和分段不分段無關。

問6

2級latch相對于里維斯. 格雷增強型在原理上的優勢嗎?

THD 直接可以觀察vout-vin的差值,這個差值越小,說明THD越好,差值的分析和鎖相環里面的phase

noise很像。 輸入的導數很大時候,峰值很大,過零點一般最差。

電路中的AC開環曲線去需要和零極點仿真對應。 我舉例子了。 CMRR主要從匹配的角度出發去理解。 CMRR=| Adm|/| Acm| PSRR的是說,如果一個opamp是millier,cascode補償的形式,power

帶來的noise會直接在 VGS兩端bouncing。 然后穿過頻率補償電容導致惡化。 所以優化的方向時盡量避免這類補償的方式。

問7

加法器每位的gain是不是有問題? 還是說理解錯了?

A點電位升高,導致NM5關斷了,如果沒有這個管子,PM1的gate也就不再升高了,豈不是PM1更容易導通? 反而有了這個管子,導致PM1的gate始終隨著A點的升高也在不停的升高,反而不利于PM1的導通呢。

加法器增益和電容值要一一對應,統一大2倍和小2倍對仿真ENOB好像沒有影響,不知道對測試有沒有影響。 C4對應32,C8對應4。?NM5關斷后,PM1的gate主要靠NM1下拉。 如果沒有NM1,則PM1的gate為不定態,不一定為低。

A點電壓夠高,NM5才會關斷,B點電壓為(A點電壓加上一個VDD),如果沒有那個NMOS器件,PM1的gate確實是一個高阻點,這個高阻點電壓再高應該不會超過VDD(分壓原理)),因此把(A點電壓加上一個VDD)這個電壓傳過去,應該是沒有問題的。

電容一但充電到vdd,只要pm1使nm2形成自舉結構,nm5即使關掉也不影響了。

但是電容充電后,還是要靠nm5的打開pm1的第一次。

B點為高阻點,PM1導通不徹底,DRV_gate電壓不等于vin+

VDD,沒有實現輸入電壓自舉的目的,你可以看看NM0的柵源電壓,應該沒有維持恒定的VDD。

如果c電點位如果有高阻狀態,那么這個點首先容易被干擾,同時這個點會有幾種狀態的過度,對我覺得這樣會讓pm1的導通電阻變化,這會影響drv_gate的控制速度。 等于給自舉開關引入非線性。

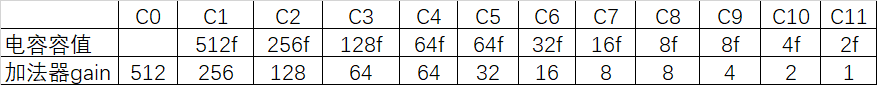

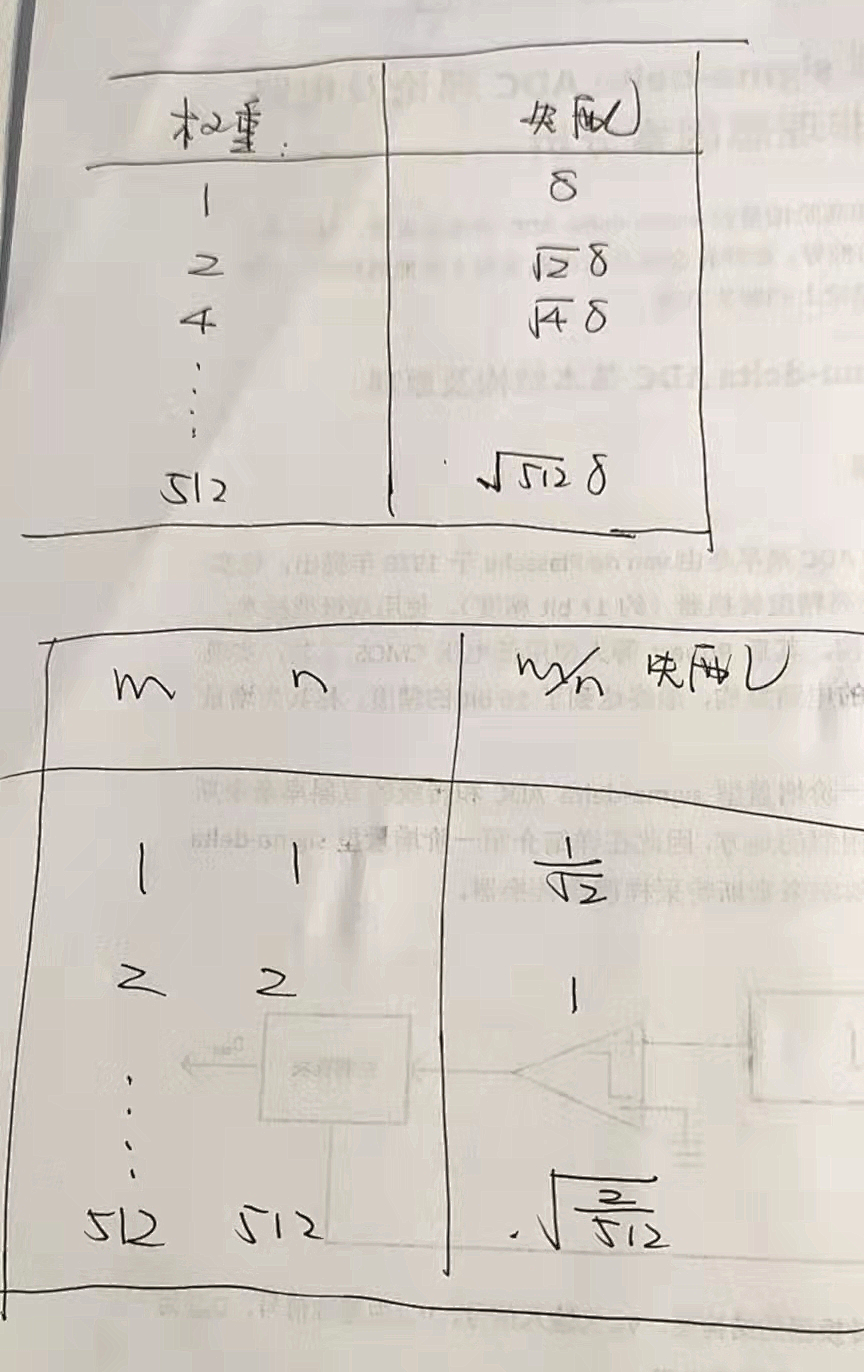

電容越大適配越大,但是這個比例會不一樣啊,就是電容每增大兩倍變成原來兩倍的時候,適配變為原來的跟二倍電容乘以四的時候就融資啊,其實面積也是乘四,這個時候呢,我們的適配會變成兩倍。

假設現在十個電容C1是512C2256,然后C1011,我們先做這個假設,那C1在CDC切換的時候,他做的動作是什么呢? 是C的下級板哪一個節約信號,那這個時候上級版的就等效為C1的512和剩余的512去做比,也就這個時候呢,M等于512

N也等于512兩個之間去比,然后這個出來的這個值啊,就說我們這個DC的輸出,其實就什么這兩個的比,其實就是M和N的這個相對配了,這個值是多少呢? 應該是根號,就是開方里面是多少,1/512加1/512,是這么一個值。

但是大家要記得就說我們出來的這個十位的扣的啊,第十位就最高位,最高位其實跟什么合時宜是對應的,對不對? 那對地位是和那個SP相對應的出來,這個十十個扣的地位是不一樣的,最高位的權重實際上要乘以512的,所以我們要把剛剛的時配要乘以它對應的權重,那對于MSD這邊呢,也就是根號下1/512加1/512,在乘以外面那個512,那這個時候等一下為多少呢。 等一下為根號下的1024,然后我們再看SBLS這邊LSB這邊呢,剛剛算的那個十倍是多少,貢獻的十倍是一嘛,對不對? 那它的權重也是一也是一,那一乘以一就是一,那這個時候就出現什么,大家會發現呢,就說MSB這邊的權,這這邊的適配雖然小,但是乘以它權重以后就顯得大。

這個為什么會這樣呢? 那就是因為我們這個權重是在二進制變化,然后隨著權重的提升,我們的適配在什么什么,它只是在以這個以跟二這種倍數在在在改變它就說這兩個比例會不一樣,所以就說電容越大的話,它那個就是其實相對精度,它是它是不夠的啊。

那這種理解是那種我認為相對比較那種稍微直觀一點的啊,這種或者感性的理解啊,那真正的需要的還是要去從那個DL的那個表達式里面去看,那那個理解可能更更嚴謹一些。

問8a

在跑蒙特卡羅的時候,器件model選帶mc的,這種和tt,ss,ff有什么區別,跑蒙特卡羅的時候有一個prosess和mismatch,這個process和corner角有什么區別。 我仿真出來的3segma的偏差是典型值的么

還是最大值?

總體而言,有電荷泵的電路壽命確實也會受到影響,或多或少而已,但這種差別一般是30年和20年的差別。 對于一般的民用產品,一個手機用幾年而已,輪不到器失效。 如果對產品壽命要求極高,需要謹慎評估相關電路結構。

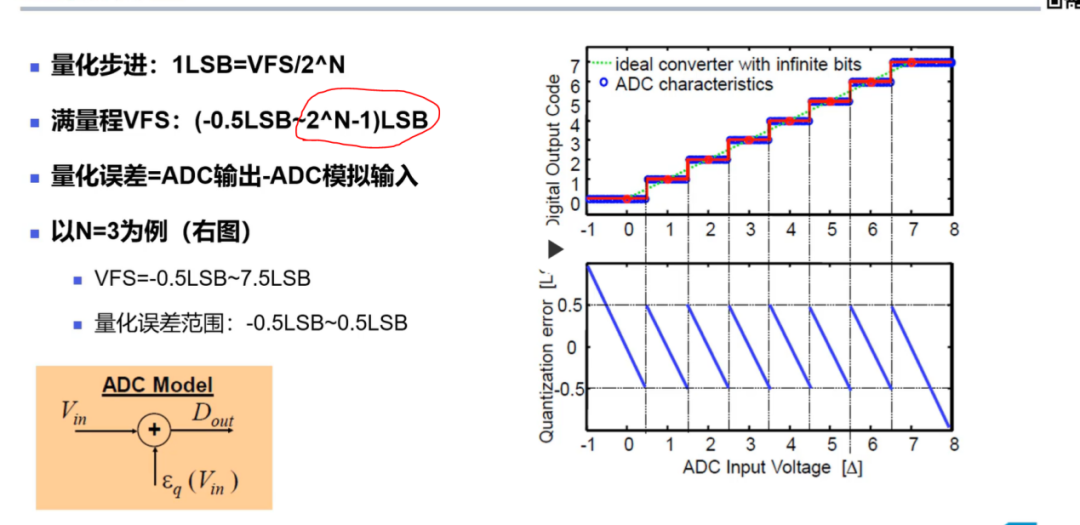

A:?是,你說的對,上下各偏移0.5

秋冬季節很干燥,我們手觸摸到物品也會發生尖端放電,這瞬間的電壓也是很高的,我們只是手麻那么一下,只是因為總能量太低了,不足以致死。 反而220V這種不高的電壓持續施加給人體,人會受不了。

總體而言,有電荷泵的電路壽命確實也會受到影響,或多或少而已,但這種差別一般是30年和20年的差別。 對于一般的民用產品,一個手機用幾年而已,輪不到器失效。 如果對產品壽命要求極高,需要謹慎評估相關電路結構。

問8b

這個地方是不是不對,應該是-0.5LSB~2^(N)-0.5

上下各偏移0.5。

問9

差分采樣是否就能很好的抑制時鐘饋通對信號的影響?

時鐘饋通說的是寄生電容的分壓,溝道電荷是MOS開啟時候溝道內的載流子在MOS關斷以后的再分配,一般是S和D各自分一點,具體怎么分還得看CLK的下降沿速度。

process就是同一個器件性能呈現出的概率分布,mismatch就是不同位置的同類型器件之間差異的分布。

小電容,電路帶寬高,高頻更容易通過。

差分減弱大部分,不能完全消除時鐘饋通和溝道電荷的影響。 因為仔細分析你會發現這2個效應和信號大小相關,而全差分信號在同一時刻信號大小是不一樣的。

如果簡單的全差分就能完全消除時鐘饋通和溝道電荷,那上級版采樣就不存在精度不高的問題了。

對于10bit以下的高速ADC來說,似乎全差分設計,就差不多夠用。

下極板采樣配合全差分才能真正做到高精度采樣

7~8bit,這么說可能也不太準確,還是要看具體設計

我們在SMIC

14nm和28nm工藝下的10Bit,對比了上極板采樣和下極板采樣,測試結果顯示速度能跑到100MHz+,ENOB在9.7Bit附近,和采樣技術沒啥關系。 主要瓶頸其實是在Latch比較器噪聲。

電子發燒友App

電子發燒友App

評論