本文詳細介紹了通常應用于IF和基帶的高速模數轉換器(ADC)的正確布板、元件選擇及元件布局。文中以高分辨率、高速數據轉換器MAX12555系列為例,介紹了優化電路設計、正確高速布板、旁路和去耦技巧、熱管理、元件選擇及布局。

本文可作為高速數據轉換器電路設計和布板建議的簡明資源,是對高速數據轉換器及其評估板數據資料中電路設計和PCB布板信息的補充。用戶應根據其特定應用,仔細閱讀所有可用資源,以使器件在特定應用中實現最優性能。文中以14位模數轉換器(ADC) MAX12555為例,這些型號分別針對65Msps/80Msps/95Msps的采樣速率進行了優化,適合所有IF和基帶應用。

本文分為三部分:一般性建議、電路設計建議、布板建議。

一般性建議概要介紹了如何在應用中發揮器件的最佳總體性能,討論了一般情況下器件外圍元件的最佳布局,提出了有關物理PCB本身的建議。

電路設計建議介紹了最關鍵和最敏感引腳處元件的推薦值。

布板建議中詳細介紹了外圍元件布局,指出哪些元件應放在頂層,哪些應放在底層,同時還提供了有關PCB的附加信息。

請參考:

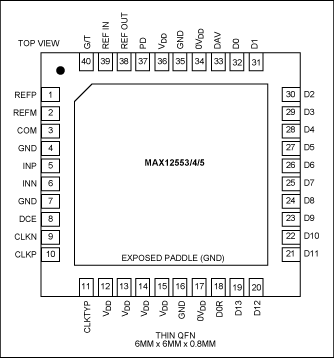

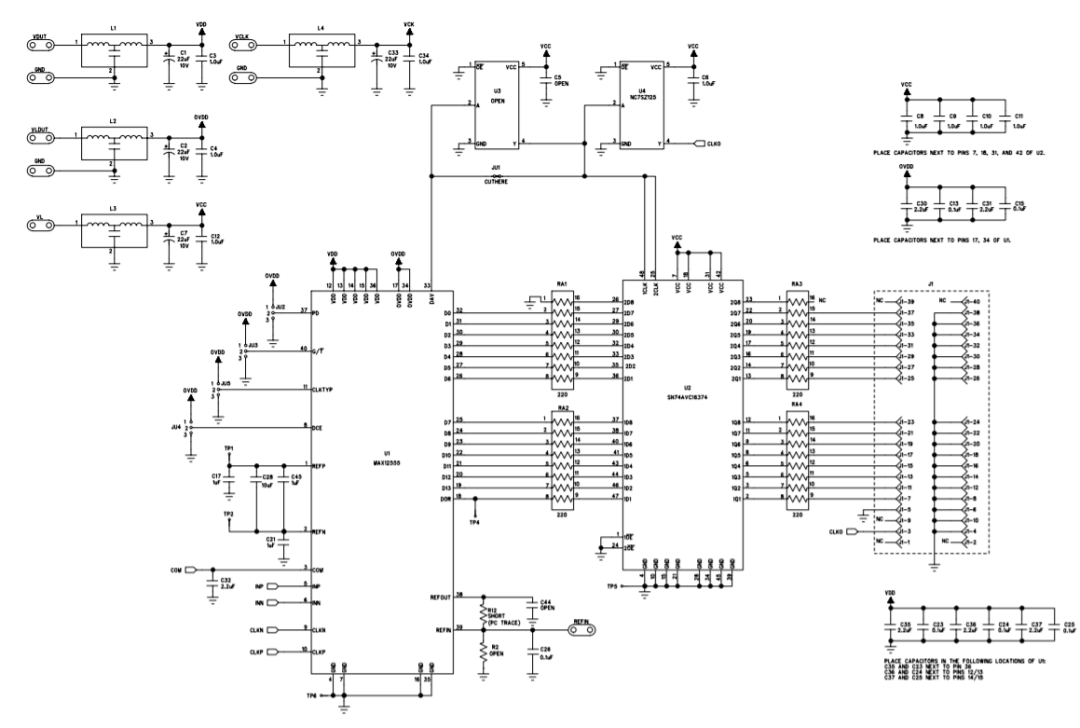

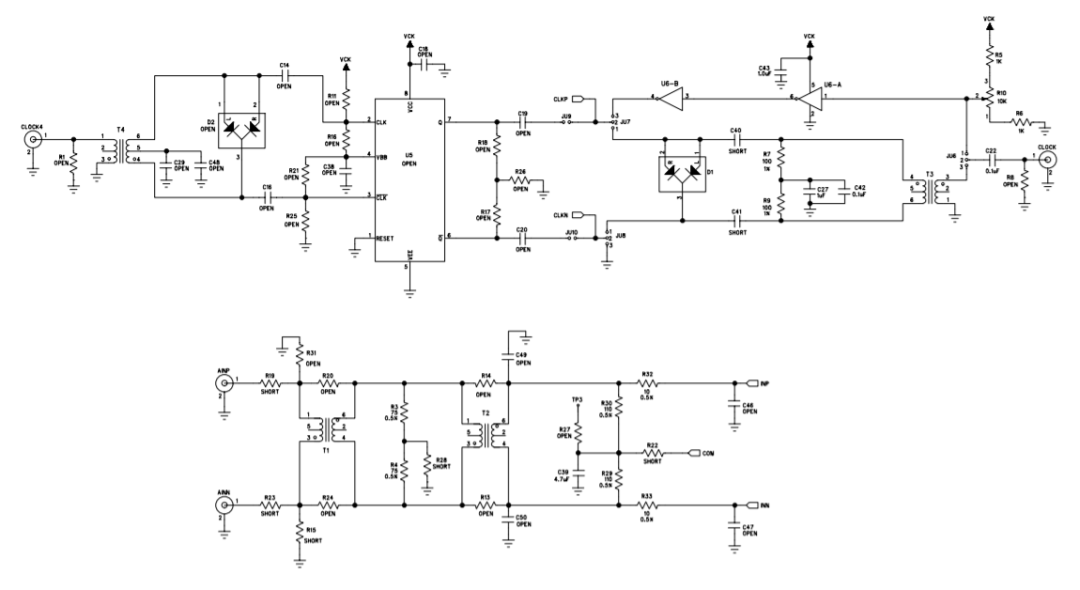

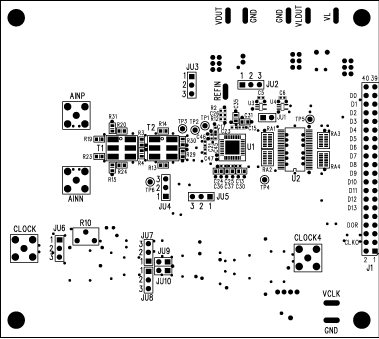

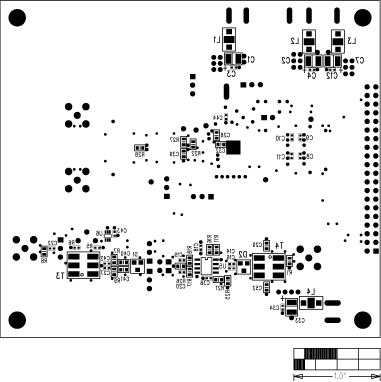

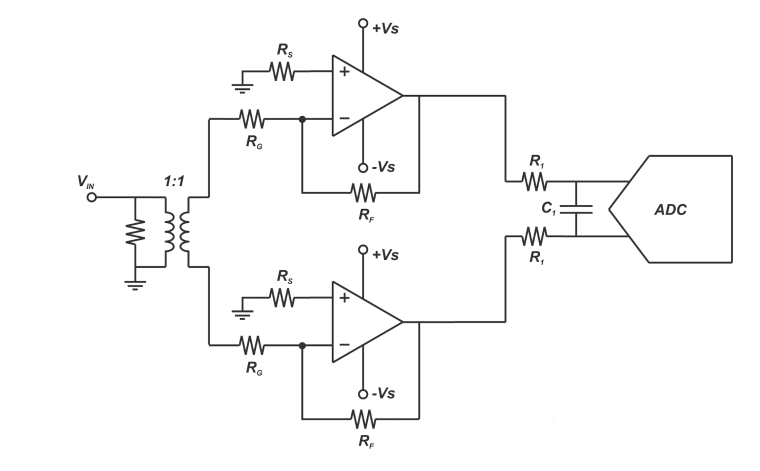

該系列ADC引腳排列見圖1,引腳功能說明見表1。評估(EV)板提供多種選擇,允許單端或差分時鐘輸入、單端或差分模擬信號輸入、內部/外部基準等,所以評估板(見圖2和圖3)使用的外圍元件和配置比正常應用中多。圖4和圖5為評估板頂層和底層的絲印及元件布局。

圖1. MAX12555的引腳排列

表1. 引腳說明

| 引腳 | 名稱 | 功能 |

| 1 | REFP | 正基準I/O。滿幅模擬輸入范圍為±(VREFP - VREFN) x 2/3,REFP通過一個0.1μF電容旁路至GND。REFP與REFN之間并聯一個1μF的電容和一個10μF電容。REFP和REFN間的1μF電容應與器件位于同一側,并盡可能靠近器件。 |

| 2 | REFN | 負基準I/O。滿幅模擬輸入范圍為±(VREFP - VREFN) x 2/3,REFN通過一個0.1μF電容旁路至GND。REFP與REFN之間并聯一個1μF的電容和一個10μF電容。REFP和REFN間的1μF電容應與器件位于同一側,并盡可能靠近器件。 |

| 3 | COM | 共模電壓I/O。COM通過一個2.2μF電容旁路至GND。將2.2μF COM至GND的旁路電容盡可能靠近器件,可以放置在PCB另外一側,通過1個過孔與ADC連接。 |

| 4, 7, 16, 35 | GND | 地。所有地引腳與EP相連。 |

| 5 | INP | 同相模擬輸入。 |

| 6 | INN | 反相模擬輸入。 |

| 8 | DCE | 占空比均衡器輸入。DCE接低電平(GND)禁止內部占空比均衡器。DCE接高電平(OVDD或VDD)使能內部占空比均衡器。 |

| 9 | CLKN | 反相時鐘輸入。在差分時鐘模式(CLKTYP = OVDD或VDD),差分時鐘信號接在CLKP與CLKN之間。在單端時鐘模式(CLKYP = GND),單端時鐘信號接CLKP,CLKN接GND。 |

| 10 | CLKP | 同相時鐘輸入。在差分時鐘模式(CLKTYP = OVDD或VDD),差分時鐘信號接在CLKP與CLKN之間。在單端時鐘模式(CLKYP = GND),單端時鐘信號接CLKP,CLKN接GND。 |

| 11 | CLKTYP | 時鐘模式定義輸入,CLKTYP接GND時為單端時鐘輸入。CLKTYP接OVDD或VDD時為差分時鐘輸入。 |

| 12-15, 36 | VDD | 模擬電源輸入。VDD連至3.15V至3.60V電源。VDD通過一個≥2.2μF的電容并聯一個0.1μF電容旁路至GND。所有VDD引腳連至相同電位。 |

| 17, 34 | OVDD | 輸出驅動器電源輸入。OVDD可連至1.7V至VDD的電源。OVDD通過一個≥2.2μF的電容并聯一個0.1μF電容旁路至GND。 |

| 18 | DOR | 數據超量程指示。DOR輸出用來指示模擬輸入電壓超量程。DOR為高電平時,表明模擬輸入電壓超出范圍。DOR為低電平時,表明模擬輸入電壓在量程以內。 |

| 19 | D13 | CMOS數字輸出,第13位(MSB)。 |

| 20 | D12 | CMOS數字輸出,第12位。 |

| 21 | D11 | CMOS數字輸出,第11位。 |

| 22 | D10 | CMOS數字輸出,第10位 |

| 23 | D9 | CMOS數字輸出,第9位。 |

| 24 | D8 | CMOS數字輸出,第8位。 |

| 25 | D7 | CMOS數字輸出,第7位。 |

| 26 | D6 | CMOS數字輸出,第6位。 |

| 27 | D5 | CMOS數字輸出,第5位。 |

| 28 | D4 | CMOS數字輸出,第4位。 |

| 29 | D3 | CMOS數字輸出,第3位。 |

| 30 | D2 | CMOS數字輸出,第2位。 |

| 31 | D1 | CMOS數字輸出,第1位。 |

| 32 | D0 | CMOS數字輸出,第0位(LSB)。 |

| 33 | DAV | 數據有效輸出。DAV是輸入時鐘經占空比補償校正后的單端輸出,DAV的典型應用是將ADC的輸出數據鎖存至后端的數字電路。 |

| 37 | PD | 關斷輸入。將PD強制置高,器件進入關斷模式。正常工作時PD置低。 |

| 38 | REFOUT | 內部基準電壓輸出。采用內部基準電壓時,REFOUT直接連至REFIN,或通過一個電阻分壓器設定REFIN輸入電壓。REFOUT通過一個≥0.1μF的電容旁路至GND。 |

| 39 | REFIN | 基準電壓輸入。在內部基準模式和帶緩沖的外部基準模式,REFIN通過一個≥0.1μF的電容旁路至GND。此時,VREFP - VREFN = VREFIN x 3/4。在無緩沖的外部基準模式下,REFIN連至GND。 |

| 40 | G/ /T | 輸出格式選擇輸入。G/ /T接GND為二元補碼格式輸出。G/ /T接與OVDD或VDD為格雷碼格式輸出。 |

| - | EP | 裸焊盤。通過裸焊盤實現與地的低電感連接。將EP連至GND以保證設計性能。PCB頂層和底層的地平面通過多個過孔連接。 |

一般性建議

一般而言,采用帶整體地層和電源層的多層PCB可獲得最佳信號完整性。

MAX12555需要高速布板技術,包括裸焊盤可靠接地。

保持MAX12555模擬部分的內層地平面完整性,空隙(void)必須最少。過孔交錯排列,保持非常小的過孔間隙,將空隙減少到最低程度。另外,在關鍵元件下方應布設完整的地,尤其是接引腳1和引腳2的REF電容、接引腳3 的COM旁路電容、接模擬信號輸入引腳5和引腳6的小電容。

將不同的輸入和輸出信號限定在不同的PCB層,如:所有模擬信號輸入位于X層、所有數字信號輸出位于Y層、所有時鐘信號位于Z層等。盡量將每一層夾在兩層地之間或使用微帶線。

使用與地相對的電源平面來減小信號感應,將總體噪聲降至最低。功率走線應寬一些,以降低IR壓降和電感。

對于GND和VDD (電源線),建議采用多個18mil規格的過孔。

MAX12555的所有GND和裸焊盤(EP)必須連至同一地平面。MAX12555依靠EP實現與地的低電感連接,通過多個過孔連至指定地層。所需的過孔數量取決于孔的尺寸。作為指導原則,Maxim建議采用5 x 5 (總共25個)矩陣的13mil規格的過孔。最少需要12個過孔。

MAX12555最關鍵的輸入、輸出是模擬信號輸入、基準引腳、時鐘和數字輸出。最關鍵的引腳是1、2、3、5、6、9、10、38和39。

ADC周圍連接旁路電容和關鍵電容的走線應盡可能的寬,以減小電阻和電感。建議采用寬度大于或等于10mil的走線。如果元件無法直接連至地平面,則其接地線應盡可能寬。這還應包括PCB設計中的接地熱焊盤。

如果旁路電容使用熱焊盤與GND連接,每個旁路電容使用兩個熱焊盤,GND端使用過孔以減小電感。

高速數字信號走線應遠離敏感的模擬信號線、時鐘線、REFP (引腳1)和REFN (引腳2)。

所有信號線(包括REFP和REFN)都應盡可能短并且避免90°折線。

確保差分模擬輸入網絡對稱,并且所有寄生效應是均衡的。

所有旁路電容應盡可能靠近器件,最好在PCB同側,可采用表貼器件減小電感(在下面的布板建議中有更詳細的介紹)

通常所有GND旁路過孔尺寸應為18mil。

為實現最佳性能,需要獨立的模擬和數字電源。

MAX12555可接受差分或單端時鐘輸入。

MAX12555可接受差分或單端模擬輸入,差分輸入可提供最佳性能。

EP作為器件的主要接地途徑,必須正確連接到指定地平面。

使用地線“隔離”ADC電路和PCB上的其它任何相鄰電路。例如:一個PCB上有多個ADC時,利用地平面將每個ADC的相關電路隔離開來。

電路設計建議

(引腳1,REFP):通過一個位于PCB頂層的高頻陶瓷電容(最大1.0μF)將REFP旁路至GND。所有REFP走線應盡可能短。

(引腳2,REFn):通過一個位于PCB頂層的高頻陶瓷電容(最大1.0μF)將REFP旁路至GND。所有REFP走線應盡可能短。

(引腳1,REFP和引腳2,REFN):REFP和REFN之間并聯兩個容值分別為10μF和1μF的高頻陶瓷電容。與引腳1和引腳2連接的任何電容都必須具有良好的高頻性能。

(引腳3,COM):COM通過一個高頻性能良好的2.2μF陶瓷旁路至GND。

(引腳5 & 6,INP & INN):為獲得最佳總體AC性能,這些引腳與地之間都應接并聯電容,容值依應用而定,范圍為5.6pF到12pF。這些電容值可被包含在任何驅動ADC的抗混疊濾波器諧振電路中,并且應被放在電路板頂層。

(引腳12-15,36,VDD):使用高頻性能良好的0.1μF和2.2μF陶瓷電容各一個并聯,將VDD旁路至GND。

(引腳17,34,OVDD):使用高頻性能良好的0.1μF和>2.2μF陶瓷電容各一個并聯,將OVDD旁路至GND。

(引腳19-32,D13-D0):包括數據輸出引腳與各自負載的串聯電阻。這些電阻可限制從輸出邏輯驅動器進入芯片內部GND的高頻邊沿電流。選定的阻值與負載電容一起產生的RC時間常數約為1ns。Maxim公司采用非常小而且低成本的電阻陣列,基本是多只0402電阻構成一組。評估板使用的是Panasonic公司的EXB-2HV-221J。

(引腳38,REFOUT):采用內部基準時,REFOUT直接與REFIN連接,或通過一個電阻分壓器設定REFIN輸入電壓。REFOUT通過一個高頻性能良好、≥0.1μF的陶瓷電容旁路至GND。

(引腳39,REFIN):在內部基準模式和帶緩沖的外部基準模式,REFIN通過一個 ≥0.1μF的電容旁路至GND。在無緩沖的外部基準模式下,REFIN連至GND。

圖2. 評估板器件原理圖

圖3. 評估板模擬部分原理圖

布板建議

將MX12555放置在PCB頂層。

接著,在引腳1與引腳2之間放置一個1μF電容。該電容應位于PCB頂層,并且盡量靠近這兩個引腳。REFP和REFN (引腳1、2)之間跨接的電容應在制造公差允許范圍內盡量靠近DUT。

下一步,放置引腳1至地和引腳2至地的旁路電容。這些電容應盡可能靠近共用的1μF電容,同時用過孔將電容的GND一端與指定模擬地相連(也與器件EP相連)。如果第二層有一個地平面,則該地平面應延伸到這三個器件的下方以減少引腳1和引腳2上的電感。對于REFP和REFN旁路電容的接地過孔,Maxim公司采用18mil的鉆孔直徑,選擇較大尺寸是因為過孔電鍍后會減小3mil。孔的最終尺寸應為約為15mil。

接下來,在引腳1與引腳2之間放置一個10μF電容。如果頂層沒有足夠空間安裝此電容,也可以像評估板那樣把它放在PCB底層,利用過孔傳輸信號。該電容與器件引腳間的走線總長應減至最小。

與引腳1和引腳2連接的走線應盡可能短,并且應當是匹配的。即:它們應當是對稱的,而且長度應相同。

接著,放置引腳3至GND的2.2μF電容,盡可能靠近器件。如果需要,該電容可放在PCB底層,采用13mil過孔與引腳3連接。走線應盡可能短。

所有GND引腳(引腳4、7、16和35)應與MAX12555器件下方的覆銅相連。

應遵循以下原則:正確連接MAX12555的EP與指定接地層(最好是第二層),需要使用足夠多的過孔以降低電感,過孔數量取決于孔的尺寸。作為指導原則,Maxim公司建議采用5 x 5 (總共25個)的13mil過孔矩陣,最小過孔尺寸應為12mil。

模擬輸入應是均衡的。也就是說,從驅動源(放大器和濾波器等)到差分輸入端的走線應該等長,元件布局應相互對稱,這樣,所有的寄生參數才會均衡。走線長度應盡可能短,以降低電感、減小干擾。

將輸入引腳5和引腳6的旁路電容放置在PCB頂層靠近器件引腳的位置,盡量減小走線長度。

應使用某一層(最好是第二層)作為可靠的模擬接地層,推薦使用過孔陣列將其與MAX12555的EP連接。

時鐘布線建議(引腳9和引腳10):

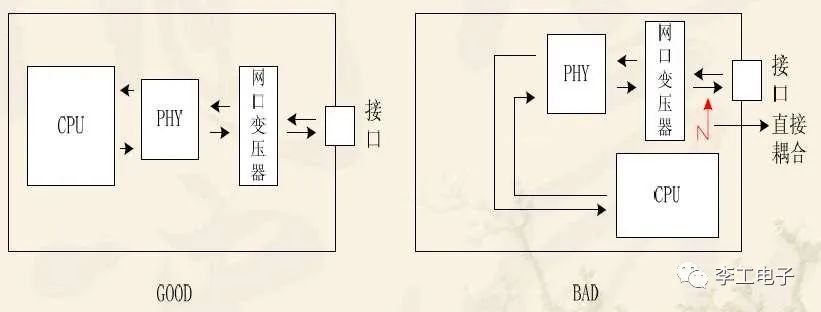

時鐘輸入與模擬輸入和基準一樣敏感。應像對待模擬信號那樣對時待時鐘信號。避免將時鐘線靠近任何數字輸出信號線。如果板上有多個ADC,則需隔離時鐘線對,以盡量降低噪聲并減小來自其它ADC的干擾。時鐘信號線不應與數字輸出信號線布在同一層。如果布在同一層,應盡量使這兩類信號線之間保持較大間距,并在這兩類信號線之間布隔離的GND,以降低可能產生的任何耦合。 建議采用典型值為1.4VP-P的差分時鐘輸入,這是器件的特性之一。但時鐘輸入信號擺幅的峰值并不是最重要的,保證快速上升和下降時間的擺率更重要。另外,內部差分放大器可提供增益,對信號進一步整形。評估板采用一個中心抽頭變壓器放大時鐘輸入,以確保快速上升和下降時間,然后再用二極管將擺幅限制在1.4VP-P。對于單端時鐘信號來說,邊沿應較陡,并且滿足數據資料規定的最高和最低電壓要求,即邏輯高電平最低為0.8VDD,邏輯低電平最高為0.2VDD。時鐘共模電壓(1/2VDD)由內部提供。推薦的接口電路/驅動器邏輯:任何邏輯輸入,包括CMOS、LVPECL、LVDS都可用于驅動時鐘輸入。對于高頻輸入信號的應用,建議采用非常高速的LVPECL時鐘分配電路,如MAX9320 PECL緩沖器。

引腳12-15,36,VDD:最好將0.1μF的旁路電容放在器件引腳旁。

引腳17,34,OVDD:最好將0.1μF的旁路電容放在器件引腳旁。

數據線(引腳19至引腳32):對于輸出數椐引腳,從ADC到緩沖器或負載IC的走線應盡量短。串聯電阻盡可能靠近ADC,為確保最佳性能,總負載電容應等于10pF。而保證緩沖器或負載IC的地與MAX12555的EP可靠連接,對于實現最佳的AC性能非常重要。如果將數椐線布在頂層或底層(采用微帶線技術),則相鄰層必須是地層,以形成有效傳輸線。如果將數據線布在內層(采用帶狀線技術),則其相鄰各層必須為地電位以形成有效傳輸線。數字信號輸出應緊密排列在單一總線內以控制電流回路。另外,盡量減小MAX12555與數字負載間的接地層空隙(由數字信號過孔產生),當數據線進入內層時,過孔應交錯排列。

REFOUT和REFIN (引腳38和引腳39)的旁路電容必須靠近器件引腳,使用短的走線直接與器件接地層相連。

圖4. 評估板頂層絲印和元件布局

圖5. 評估板底層絲印和元件布局 總結:本應文是器件和評估板數據資料的補充,用戶可在應用中根據提供的建議優化器件性能。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論