良好的專用集成電路 (ASIC) 可享受 90% >首次硅成功。您可能想知道為什么我們要討論“修復”此問題的方法?畢竟,ASIC幾乎可以工作,沒有時間旋轉它,仍然滿足市場窗口。聽起來很耳熟?不幸的是,墨菲定律1這句話說,“任何可能出錯的事情,都會在最糟糕的時候出錯,”在這里適用。無論我們如何仿真、構建現場可編程門陣列 (FPGA) 和原型設計,都會有驚喜。小事情需要改進。然后,就在你認為你正在接近的時候,銷售人員說如果沒有另一個“小”功能,他們就無法銷售該設備。當然,介紹的最后期限不能延長。這部劇并不陌生,它可能是ASIC設計師的噩夢。

數字電路相對容易修復,因為它們往往是黑白的,開或關。但是,當ASIC上出現模擬問題時會發生什么?這可能令人生畏。模擬問題包括幾乎正常工作的事情。只是有點吵;它需要更多的收益;它需要稍作調整來校準它,使其進入范圍,或補償另一個組件的公差。如果優化ASIC如此簡單,我們中的許多人會少喝咖啡,睡得更好。

我們一直在ASIC上看到模擬設計錯誤。我們拿起一塊板子,在角落里是一段“哎呀邏輯”,這個設計功能在當時看起來是正確的,但現在顯然不起作用。本文討論了修復“糟糕”的方法。我們提供了添加外部電路的提示和技巧,以使許多這些ASIC可用于原型設計,或者在許多情況下,可交付產品。我們展示了如何校正模擬電路中的噪聲、進行調整、校準增益和失調以及清潔電源。回報是每個人的目標:更快的上市時間,甚至避免額外的ASIC制造旋轉。

優化模擬以降低噪聲

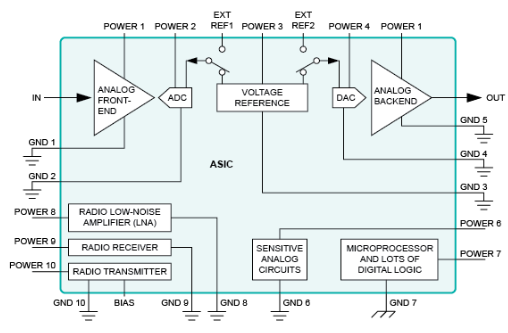

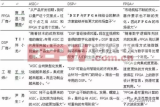

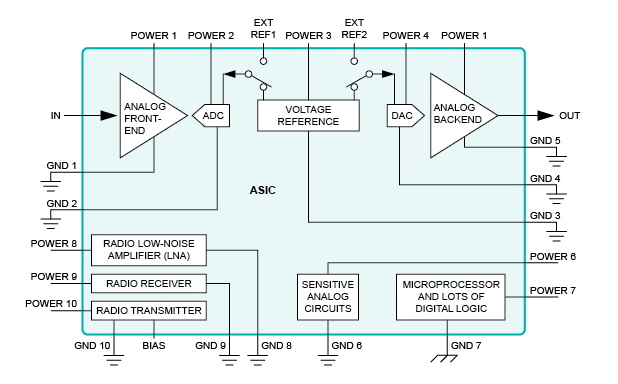

噪聲是混合信號ASIC的常見問題,主要是因為數字邏輯開關噪聲會進入敏感的模擬電路。圖1顯示了每個模塊都有自己的電源和接地引腳的最佳布局。盡管如此,數字電路的開關電流具有快速邊沿,這些邊沿會串擾和反彈接地和電源引腳。

圖1.ASIC框圖顯示了最佳情況下的布局,其中每個模塊都有自己的電源和接地。

如果同一封裝中有兩個芯片(一個模擬芯片和一個數字芯片),并且構建得很像混合體,則這種布局將是理想的選擇。這種配置將允許兩個真正獨立的接地,因為電路不會共享一個共同的硅襯底。唉,在現實世界中,這個ASIC是一個芯片,但擁有盡可能多的獨立電源和接地引腳仍然很重要。這為我們在故障排除和修復問題時提供了最大的靈活性。

現在讓我們看看優化該電路中某些模塊的方法。

微處理器和數字邏輯中的開關噪聲

我們從右下角開始檢查圖1電路,微處理器和其他數字邏輯,它們都是開關噪聲源。沒有經驗的設計師可能會說,“但時鐘只有1MHz。這是真的,但是完美方波的邊緣有延伸到無窮大的奇次諧波。實際上,能量最多的是前五到七個諧波。同樣在時鐘系統中,時鐘使邊沿重合,傳播延遲除外。最后,CMOS輸出在開關時間內吸收電流。圖2顯示了電流使用的兩種方式:一是充電下一級的電容;第二,在開關時間內為兩個晶體管部分供電。請參閱圖 3 中的數據。這是一個很小的電流,但是當有數百萬個晶體管切換時,它會加起來。

圖2.典型的CMOS輸入或輸出電路使用電流為下一級的電容充電,并在開關時間內為兩個晶體管部分供電。

圖3.CMOS輸入引腳上的電壓與電源電流的關系。數據為MAX5391數字電位器。

這讓我們何去何從?一些設計人員使用術語“模擬”和“數字”來區分電源域和接地域。我們分別更喜歡“干凈”和“骯臟”這兩個術語,因為它有助于思考過程。在ASIC內部,接地會反彈,從而將數字接地噪聲引入模擬電路。因此,這兩個接地域需要連接在一個系統星點上,以保持噪聲分離。2電源去耦電容器的選擇需要考慮電容器的自諧振。3數字邏輯中的閾值可消除噪聲,而模擬電路沒有閾值。4

提高ADC的信噪比

現在轉到為ADC供電的模擬前端(AFE)。它由多路復用器、放大器和濾波器組成。如果ADC信號有噪聲,我們會查看輸入信號的信噪比(SNR),以確定我們可以改進的地方。有幾個直截了當的問題要問。是否使用了ADC的全范圍?我們能否通過放大器和數字電位計增加增益或失調,以居中并優化信號范圍?如果輸入信號噪聲太大,我們是否可以清理電源的電源,甚至使用低噪聲參考為其供電?是否存在帶外 (OOB) 射頻干擾 (RFI) 或電磁干擾 (EMI)?我們是否可以屏蔽電路,添加雙絞線,使用差分輸入放大器,或添加低通濾波器以共模消除噪聲?5,6對這些問題的簡短回答是,是的。可以在 ASIC 輸入之前執行其中一項或多項操作。

另一個常見問題是進入AFE的信號源。假設傳感器不可用或需要更換為其他制造商的零件。情況變得更加復雜,因為替換部件可能具有不同的輸出質量;它可能需要使用外部放大器進行阻抗變換、增益或失調,以繼續類似的工作。AFE本身可能噪聲太大,那么我們是否可以更好地用串聯電感、電阻或鐵氧體磁珠去耦電源?低噪聲基準電壓源也可用作電源替代品。

在圖1的右側,我們看到一個基準電壓源,可以同時為ADC和DAC供電。還有一個開關選項,用于向ADC饋送一個外部較低噪聲基準電壓源。這個簡單的變化可以改善ADC的信噪比。如果使用可調或可調的基準電壓源,則可以調整ADC或DAC的滿量程幅度。

DAC輸出噪聲

現在請看圖1的右上方模塊,其中我們可以看到DAC后跟一個由放大器和濾波器組成的模擬后端。有一種快速評估DAC噪聲和輸出調理的方法:將DAC設置為在其范圍的10%、50%和90%處輸出三個直流電壓。我們選擇 10%、50% 和 90% 以避免削波或壓縮,并保持在線性信號區域。典型的DAC基準輸入連接到滿量程,零電平連接到地。因此,要了解噪聲源,請更改DAC DC值。(頻譜分析儀在這里非常有用。基準電壓源或電源的噪聲在接近滿量程時更為明顯;任何接地噪聲在接近零電平時普遍存在。在內部和外部基準電壓源之間切換可揭示該噪聲源的差異。此外,請注意ADC和DAC之間通過公共基準電壓源的相互作用。在ADC上用干凈的直流對DAC進行步進,會顯示通過基準電壓源路徑的串擾。

可能需要增加一個用于濾波的外部放大器,以及用于增益和失調調整以及阻抗轉換的數字電位計。

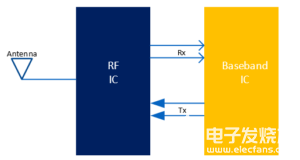

在不增加噪音的情況下為收音機供電

ASIC的左下角有三個無線電塊。無線電很有趣,因為發射器可以阻擋或使接收器脫敏。數字開關噪聲也可以做同樣的事情。這是一個真實世界的例子的好地方,說明可能出錯的地方,設計中一個非常具有破壞性的“哎呀”。

幾年前,一家公司提供了升級的手機,也允許電子郵件訪問。舊手機在我家工作,信噪比很好;新手機需要更多的信號才能工作。設計缺陷變得明顯:電子郵件功能的額外數字電路非常嘈雜,以至于電話接收器無法按預期運行。我們不得不在屋頂上安裝一個手機中繼器,在我的家庭辦公室重復信號,以使新手機正常工作。

現在回到我們的主要討論。我的故事對我們討論ASIC意味著什么?手機是雙工設備。也就是說,它們同時在不同的無線電頻率上發送和接收。稱為雙工器的專用濾波器允許雙工通信;它可以防止接收器被更高功率的發射頻率所混淆。但是,信號可能會在雙面打印器周圍泄漏并導致問題。根據定義,雙工器不能有效地消除數字開關噪聲。無線電接收器信號通過LNA發送。與大多數系統一樣,第一個放大器設置SNR,因為后面的放大器看到更高的信號。因此,它們對整體SNR的貢獻不大。

最敏感的電源是為LNA供電的電源。用低噪聲基準電壓源代替該電源可以創造改善接收器性能的奇跡。無線電發射器還可以使用外部MOS晶體管來增加所需的功率。此發射器可能需要校準,以滿足美國聯邦通信委員會 (FCC) 或其他國家/地區的無線電監管機構的最大功率輸出標準。例如,如果發射器中的元件容差允許功率變化±10%,則需要重置容差,以便無線電輸出可能在80%和100%之間。合法地說,輸出功率永遠不能超過100%;較低的功率意味著無線電的范圍將減小。在最終測試中對電源輸出進行簡單的校準可確保最大的無線電范圍和性能。校準允許對這些容差進行補償,連接到功率放大器偏置引腳的簡單數字電位計可確保全功率無線電輸出。7

現在請看圖1的最后一塊,即“敏感模擬電路”。我們不知道他們在這里是什么!所以,我們猜測:MEMS加速度計,觸摸屏,LCD顯示屏,麥克風輸入,音頻輸出,光傳感器,面部傳感器,露水或濕度傳感器,溫度傳感器,等等。我們生活在一個模擬世界中,我們需要感知它,將其轉換為數字,處理它,然后將其轉換為模擬來控制我們的模擬世界。如果制造商的電壓容差大于預期,或者需要使用兩個制造商的產品來滿足交付數量,則此示例至少需要添加一個數字電位計來校準LCD對比度。在工廠使用數字電位計校準LCD偏置,使現有的ASIC無需耗時的返工即可運行。

結論

我們可以通過不需要另一個完整布局通道的簡單修復來解決多少其他 ASIC 問題?在我們看到它們并嘗試之前,我們永遠不會知道。工程師們知道墨菲和他的“定律”總是潛伏在設計實驗室的陰影中。這就是為什么每個聰明的ASIC設計人員都需要一位經驗豐富的模擬工程師來預測問題并解決影響產品上市時間的模擬噪聲問題(“糟糕”)。

審核編輯:郭婷

電子發燒友App

電子發燒友App

評論