幾十年來,數(shù)據(jù)轉(zhuǎn)換器一直是模擬現(xiàn)實(shí)世界和數(shù)字世界之間的橋梁。從占用多個(gè)機(jī)架空間并消耗大量功率的分立元件開始(如 11 W 的 DATRAC 50 位 500 kSPS 真空管 ADC),它們已經(jīng)演變成高度集成的單片硅 IC [1]。自從第一個(gè)商用數(shù)據(jù)轉(zhuǎn)換器問世以來,對(duì)更快數(shù)據(jù)速率的永不滿足的需求意味著數(shù)據(jù)轉(zhuǎn)換器的開發(fā)必須跟上步伐。ADC的最新化身是RF采樣ADC,采樣速度在GHz范圍內(nèi)。

架構(gòu)開發(fā)的進(jìn)步加上半導(dǎo)體技術(shù)的快速發(fā)展,使單片硅形式的模數(shù)轉(zhuǎn)換器(ADC)得以實(shí)現(xiàn)。自1990年代以來,CMOS技術(shù)已經(jīng)能夠與構(gòu)成數(shù)據(jù)轉(zhuǎn)換器構(gòu)建模塊的分立模擬電路的質(zhì)量保持同步。將構(gòu)建模塊集成到單片硅片中可實(shí)現(xiàn)更節(jié)能和節(jié)省空間的設(shè)計(jì)。現(xiàn)在,摩爾定律不僅適用于數(shù)字IC設(shè)計(jì),也適用于模擬設(shè)計(jì)[2]。人們只需要觀察過去二十年(1990年代中期至今)就能看到技術(shù)的快速增長(zhǎng)。技術(shù)的這種增長(zhǎng)刺激了對(duì)更快數(shù)據(jù)轉(zhuǎn)換的需求,從而開發(fā)了帶寬越來越高的數(shù)據(jù)轉(zhuǎn)換器。

多年來,硅技術(shù)已經(jīng)足夠先進(jìn),現(xiàn)在可以經(jīng)濟(jì)地設(shè)計(jì)具有更強(qiáng)大數(shù)字處理功能的模數(shù)轉(zhuǎn)換器(ADC)。早期ADC設(shè)計(jì)使用的數(shù)字電路很少,主要用于糾錯(cuò)和數(shù)字驅(qū)動(dòng)器。新的GSPS(每秒千兆采樣)轉(zhuǎn)換器(也稱為RF采樣ADC)采用先進(jìn)的65 nm CMOS技術(shù),可以提供更多的數(shù)字處理能力,以增強(qiáng)ADC的性能。這使得數(shù)據(jù)轉(zhuǎn)換器能夠從1990年代中期和2000年代的ADC(大A,小D轉(zhuǎn)換器)轉(zhuǎn)變?yōu)锳DC(小A,大D轉(zhuǎn)換器)。這并不意味著模擬電路及其性能已經(jīng)縮小,但數(shù)字電路的數(shù)量急劇增加,以補(bǔ)充模擬性能。這些附加功能允許ADC在ADC芯片中快速進(jìn)行大量數(shù)字處理,并占用FPGA的部分?jǐn)?shù)字處理負(fù)載。這為系統(tǒng)設(shè)計(jì)人員開辟了許多其他可能性。現(xiàn)在,使用這些新型先進(jìn)GSPS ADC,系統(tǒng)設(shè)計(jì)人員只需為多個(gè)平臺(tái)設(shè)計(jì)一個(gè)硬件,并有效地使用軟件重新配置相同的硬件以適應(yīng)新應(yīng)用。

高速增強(qiáng)的數(shù)字處理

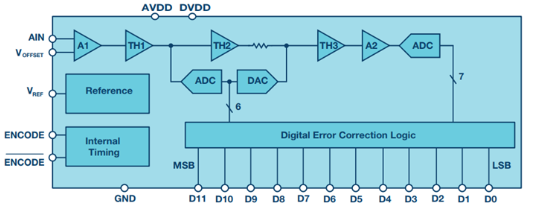

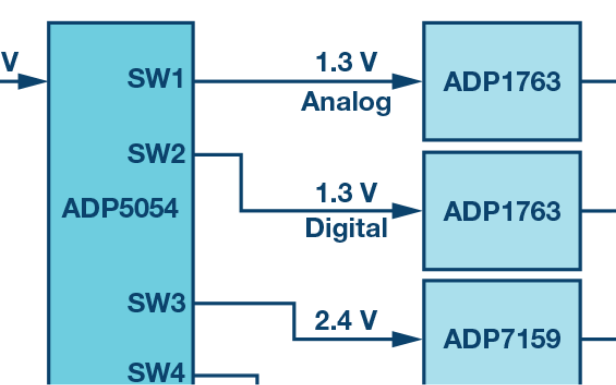

CMOS工藝中不斷縮小的幾何尺寸與先進(jìn)的設(shè)計(jì)架構(gòu)相結(jié)合,意味著ADC首次可以使用數(shù)字處理技術(shù)來提高其性能。這一突破是在1990年代初實(shí)現(xiàn)的,ADC設(shè)計(jì)人員自[1]以來就沒有回頭。隨著硅工藝的改進(jìn)(從0.5 μm,0.35 μm,0.18 μm和65 nm),轉(zhuǎn)換速度提高。但是,隨著幾何形狀的縮小,晶體管雖然越來越快(導(dǎo)致更高的帶寬),但在模擬設(shè)計(jì)(如GM(跨導(dǎo)))的性能方面提供了略差的特性。這可以通過添加越來越多的校正邏輯來補(bǔ)償。然而,硅仍然足夠昂貴,以至于ADC內(nèi)部的數(shù)字電路數(shù)量仍然相對(duì)適中。一個(gè)示例的框圖如圖 1 所示。

圖1.具有最少數(shù)字糾錯(cuò)邏輯的早期單芯片ADC。

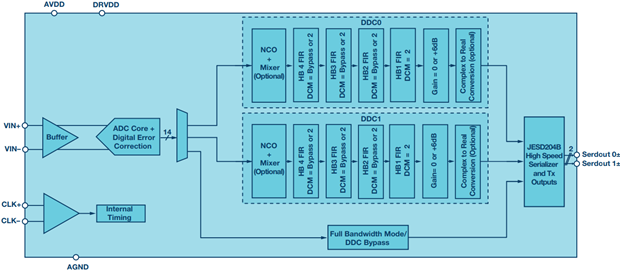

隨著硅技術(shù)向 65 nm 等深亞微米幾何形狀的進(jìn)步,規(guī)模經(jīng)濟(jì)使得在數(shù)據(jù)轉(zhuǎn)換器中添加大量數(shù)字處理成為可能,此外還可以更快地運(yùn)行內(nèi)核(1 GSPS 或更高)[2]。這是二次檢查的突破性進(jìn)展。通常,數(shù)字信號(hào)處理由ASIC或FPGA處理,具體取決于系統(tǒng)性能和成本要求。ASIC是針對(duì)特定應(yīng)用的,需要大量資金進(jìn)行開發(fā)。因此,設(shè)計(jì)人員通常會(huì)長(zhǎng)時(shí)間運(yùn)行ASIC設(shè)計(jì),以延長(zhǎng)ASIC開發(fā)的投資回報(bào)。FPGA是ASIC的更便宜的替代品,不需要龐大的開發(fā)預(yù)算。然而,由于FPGA試圖成為每個(gè)人的一切,其信號(hào)處理能力受到速度和功率效率的阻礙。這是可以理解的,因?yàn)樗鼈兲峁┝薃SIC無法提供的靈活性和可重構(gòu)性。圖2顯示了具有可配置數(shù)字處理模塊的RF采樣ADC(也稱為GSPS ADC)的框圖。

圖2.帶數(shù)字處理模塊的 GSPS ADC。

新一代GSPS ADC將徹底改變無線電設(shè)計(jì),因?yàn)樗鼈優(yōu)樵O(shè)計(jì)表帶來了很大的靈活性,其中一些將在下文中討論:

高速數(shù)字處理

早期的無線電將使用模擬混頻器和級(jí)聯(lián)數(shù)字下變頻器(DDC)的混合,以便將信號(hào)降低到基帶進(jìn)行處理。這涉及許多硬件(模擬混音)和電源(在ASIC/FPGA中的模擬和DDC中)。借助新一代RF采樣ADC,DDC可以使用完全自定義的數(shù)字邏輯在ADC內(nèi)部以一定速度運(yùn)行。這意味著處理更加節(jié)能。

通過 JESD204B 實(shí)現(xiàn) I/O 靈活性

新一代RF采樣ADC不僅具有GSPS采樣能力,而且還避開了高速串行接口的過時(shí)的LVDS輸出。新的JEDEC JESD204B規(guī)范允許通過CML(電流模式邏輯)以每通道高達(dá)12.5 Gbps的高通道速率傳輸數(shù)字輸出數(shù)據(jù)。這提供了高水平的 I/O 靈活性。例如,ADC可以在全帶寬模式下工作,并在多個(gè)通道上傳輸數(shù)字?jǐn)?shù)據(jù),或者使用一個(gè)可用的DDC并在一個(gè)通道上傳輸抽取和處理的數(shù)據(jù),只要輸出通道速率保持在每通道12.5 Gbps以下。

可擴(kuò)展的硬件設(shè)計(jì)

DDC 的使用在硬件設(shè)計(jì)方面提供了新的靈活性。系統(tǒng)設(shè)計(jì)人員現(xiàn)在可以凍結(jié)ADC和FPGA的硬件設(shè)計(jì),只需進(jìn)行最少的更改,就可以將系統(tǒng)重新配置為不同的帶寬,只要ADC能夠支持它。例如,無線電可以設(shè)計(jì)為全帶寬ADC(RF采樣ADC),或者使用可用的DDC設(shè)計(jì)為IF采樣ADC(中頻帶ADC)。系統(tǒng)中唯一的變化是在RF側(cè),IF ADC可能需要一些最小的額外混頻。大部分更改將發(fā)生在為新帶寬配置ADC所需的軟件中。但是,ADC + FPGA硬件設(shè)計(jì)幾乎可以保持不變。這提供了一種參考硬件設(shè)計(jì),可以滿足許多平臺(tái)及其要求,軟件是唯一的變量。

其他附加功能

深亞微米CMOS工藝允許的高集成度迎來了一個(gè)時(shí)代,越來越多的功能被內(nèi)置到ADC中。其中一些特性包括快速檢測(cè)CMOS輸出,可實(shí)現(xiàn)高效的AGC(自動(dòng)增益控制)和信號(hào)監(jiān)控(如峰值檢波器)。所有這些特性都有助于減少外部元件和設(shè)計(jì)時(shí)間,從而有助于系統(tǒng)設(shè)計(jì)。

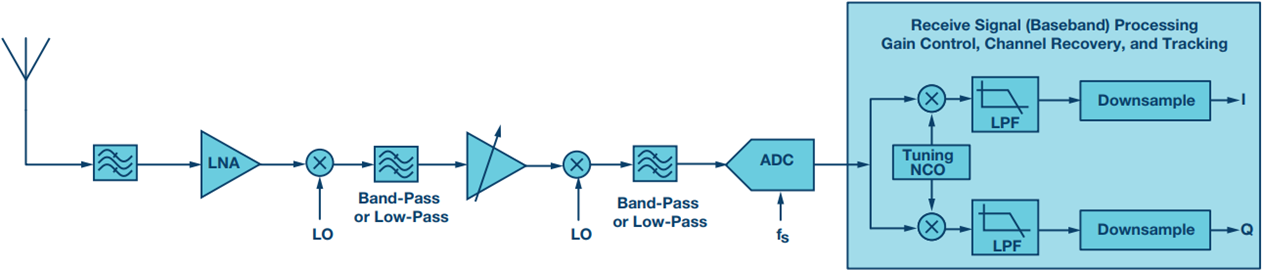

ADC的一個(gè)非常常見的用例是通信接收器系統(tǒng)設(shè)計(jì)。關(guān)于軟件定義無線電(SDR)和使用ADC的通信接收器已經(jīng)有許多出版物,這超出了本次討論的范圍。老一代無線電接收器的框圖如圖3所示[1]。

圖3.用于蜂窩無線電的寬帶數(shù)字接收器。

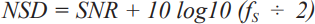

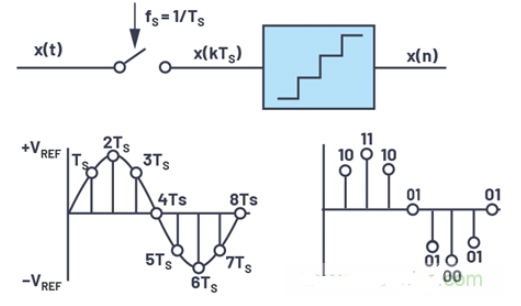

GSM 無線電接收器的正常規(guī)格要求 ADC 中的噪聲頻譜密度 (NSD) 至少為 153 dBFS/Hz 或更高。眾所周知,NSD通過以下公式[3]連接到ADC的SNR:

其中:

信噪比以dBFS

f為單位s= ADC 采樣速率

傳統(tǒng)軟件無線電設(shè)計(jì)

在寬帶無線電應(yīng)用中,一次采樣和轉(zhuǎn)換高達(dá)50 MHz的頻段的情況并不少見。為了正確數(shù)字化50 MHz頻段,ADC需要對(duì)至少五倍的帶寬或至少~250 MHz進(jìn)行采樣。 將這些數(shù)字代入上述公式,ADC達(dá)到–153 dBFS/Hz的NSD規(guī)范所需的SNR約為72 dBFS。

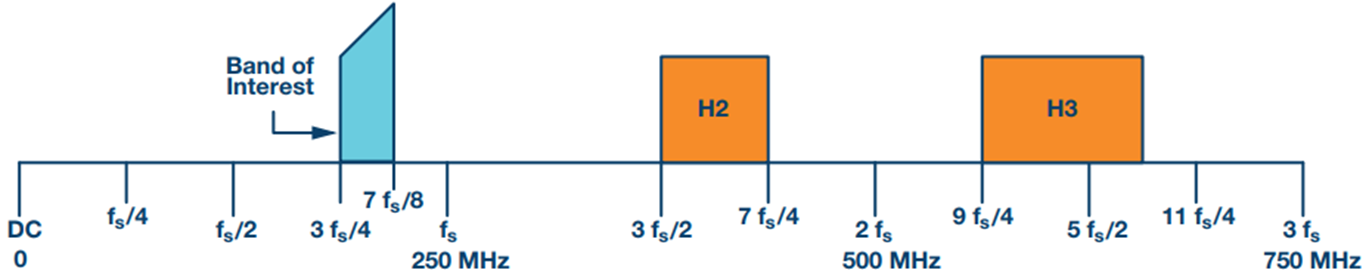

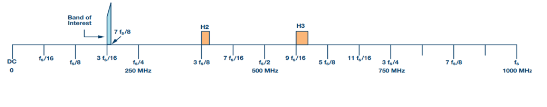

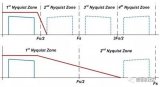

圖4顯示了使用50 MSPS ADC對(duì)250 MHz頻段進(jìn)行有效采樣的頻率規(guī)劃。該圖還顯示了第二和第三諧波帶的位置。

圖4.使用 50 MSPS ADC 的 250 MHz 寬帶無線電的頻率規(guī)劃。

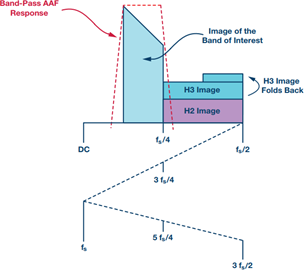

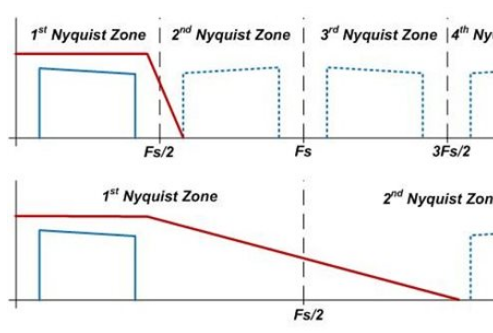

ADC的任何采樣頻率都將落在ADC的第一奈奎斯特(DC – 125 MHz)頻段。這種現(xiàn)象稱為混疊,因此包括目標(biāo)頻段在內(nèi)的頻率,其二次和三次諧波有效地折返或混疊到第一奈奎斯特頻段。如圖 5 所示,如下所示:

圖5.第一奈奎斯特所示的可用頻段,具有二次和三次諧波。

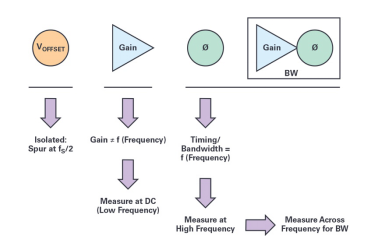

除NSD規(guī)范外,GSM、LTE和LTE-A等蜂窩通信標(biāo)準(zhǔn)對(duì)SFDR(無雜散動(dòng)態(tài)范圍)也有其他嚴(yán)格的要求。該規(guī)范給前端設(shè)計(jì)帶來了很大的壓力,因?yàn)榍岸嗽O(shè)計(jì)能夠在對(duì)目標(biāo)頻帶中的信號(hào)進(jìn)行采樣時(shí)衰減不需要的信號(hào)。

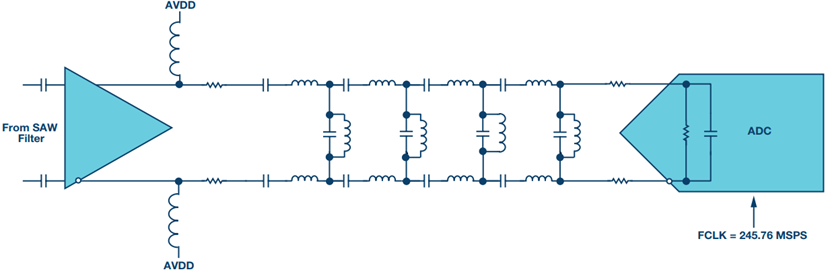

牢記SFDR規(guī)范,傳統(tǒng)無線電前端設(shè)計(jì)的抗混疊濾波器要求變得非常難以滿足。滿足SFDR規(guī)范的最佳抗混疊濾波器(AAF)解決方案是實(shí)現(xiàn)帶通濾波器。通常,這些帶通濾波器的數(shù)量級(jí)為五個(gè)或更高。能夠滿足此類應(yīng)用的SNR(或NSD)和SFDR要求的合適ADC是AD9467,16位、250 MSPS模數(shù)轉(zhuǎn)換器[4]。使用AD9467的蜂窩無線電應(yīng)用的前端設(shè)計(jì)如圖6所示。

圖6.前端設(shè)計(jì)顯示放大器、抗混疊濾波器和250 MSPS時(shí)的ADC。

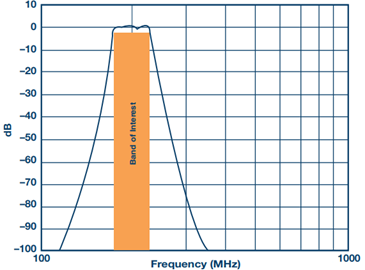

滿足SFDR要求的AAF的頻率響應(yīng)如圖7所示。該系統(tǒng)的實(shí)現(xiàn)并非不可能,但帶來了許多設(shè)計(jì)挑戰(zhàn)。帶通濾波器是最難實(shí)現(xiàn)的濾波器之一,因?yàn)樗婕霸S多組件。在這種情況下,元件選擇是關(guān)鍵,因?yàn)樵g的任何不匹配都會(huì)導(dǎo)致ADC輸出中出現(xiàn)不必要的雜散(SFDR)。除了復(fù)雜性之外,任何阻抗不匹配都會(huì)影響濾波器的增益平坦度。為了優(yōu)化該濾波器設(shè)計(jì)以滿足通帶平坦度和阻帶抑制要求,需要進(jìn)行大量的設(shè)計(jì)工作。

圖7.前端的帶通響應(yīng)如圖6所示。

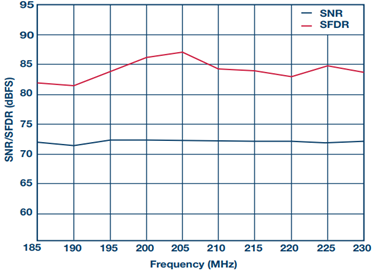

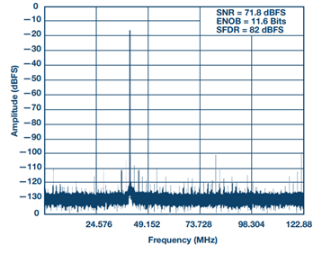

雖然這種無線電設(shè)計(jì)的前端實(shí)現(xiàn)可能很復(fù)雜,但確實(shí)可以工作,如跨頻率圖的SNR/SFDR性能所示(如圖8所示)。205 MHz時(shí)的FFT如圖9所示。但是,系統(tǒng)實(shí)現(xiàn)因以下原因而變得復(fù)雜:

過濾器設(shè)計(jì)。

FPGA必須專用I/O端口來捕獲LVDS數(shù)據(jù)(16對(duì)),這使得PCB設(shè)計(jì)變得復(fù)雜。

在FPGA中留出額外的處理能力用于數(shù)字信號(hào)處理。

圖8.圖16所示的250位、6 MSPS ADC設(shè)計(jì)的SNR/SFDR與頻率的關(guān)系。

圖9.205 MHz 時(shí)的 FFT,適用于圖 16 所示的 250 位、6 MSPS ADC 設(shè)計(jì)。

RF采樣ADC簡(jiǎn)化并加快設(shè)計(jì)

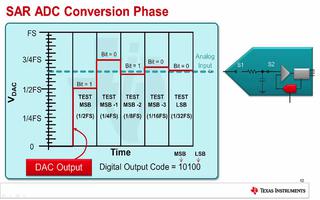

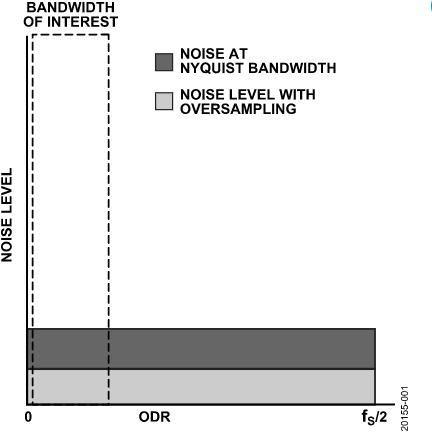

RF采樣ADC方法使用過采樣然后抽取數(shù)據(jù)以改善動(dòng)態(tài)范圍的技術(shù)[5]。深亞微米CMOS技術(shù)提供的速度優(yōu)勢(shì)與密集的數(shù)字集成能力相結(jié)合,催生了RF采樣ADC的新時(shí)代,它可以完成比普通模數(shù)轉(zhuǎn)換更多的繁重工作。這些ADC具有更多的數(shù)字電路,可以快速處理信號(hào)。

對(duì)于系統(tǒng)設(shè)計(jì)人員來說,這意味著易于實(shí)施和其他靈活性,而這些靈活性迄今為止一直是ASIC/FPGA領(lǐng)域的一部分。上述相同的無線電設(shè)計(jì)示例可以使用RF采樣ADC實(shí)現(xiàn)。AD9680(14位、1 GSPS JESD204B、雙通道ADC)是新一代RF采樣ADC之一,還具有額外的數(shù)字處理能力[6]。該ADC在全采樣速率(1 GSPS)下的NSD為~67 dBFS [3]。這個(gè)信噪比還不是一個(gè)問題,因?yàn)樗鼘⒃诤竺孀兊妹黠@。目標(biāo)頻段與以前相同,但RF采樣ADC奈奎斯特區(qū)的頻率規(guī)劃要簡(jiǎn)單得多,如圖10所示。這是因?yàn)榕c前面描述的示例(1 MHz)相比,該ADC的采樣頻率為250倍(<> GHz)。

圖 10.使用 50 GSPS ADC 的 1 MHz 寬帶無線電的頻率規(guī)劃。

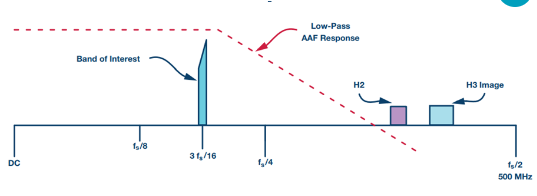

從頻率規(guī)劃中可以明顯看出,這是一個(gè)比圖4所示方案更簡(jiǎn)單的計(jì)劃。AAF 要求也放寬了,如圖 11 所示。在這種方法中,其思路是使用簡(jiǎn)單的模擬前端設(shè)計(jì),并將數(shù)字處理模塊留在RF采樣ADC內(nèi),以進(jìn)行繁重的信號(hào)處理。

圖 11.用于 1 GSPS ADC 的 AAF 植入。

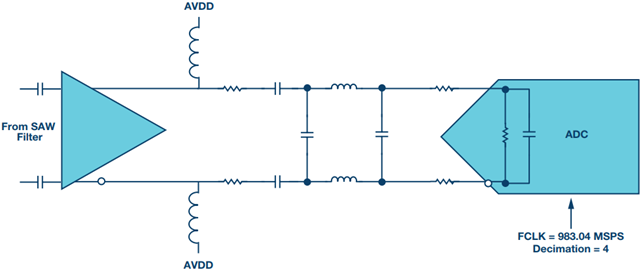

過采樣的好處基本上是將頻率規(guī)劃分散到奈奎斯特區(qū),比250 MSPS奈奎斯特區(qū)大四倍。這極大地放寬了濾波要求,與250 MSPS ADC實(shí)現(xiàn)中使用的帶通濾波器相反,一個(gè)簡(jiǎn)單的三階低通濾波器就足夠了。使用RF采樣ADC的簡(jiǎn)化AAF實(shí)現(xiàn)如圖12所示。

圖 12.前端設(shè)計(jì)顯示放大器、抗混疊濾波器和ADC,速率為1 GSPS。

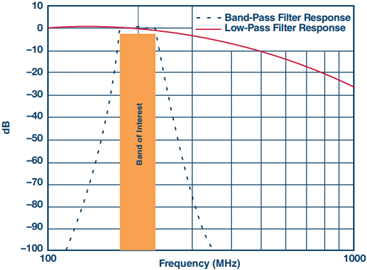

圖13顯示了低通濾波器響應(yīng)。帶通響應(yīng)也顯示為比較。低通濾波器實(shí)現(xiàn)了更好的通帶平坦度,并且在元件失配方面更易于管理。在匹配阻抗方面也更容易實(shí)現(xiàn)。此外,由于組件數(shù)量較少,系統(tǒng)的成本也降低了。前端設(shè)計(jì)的這種簡(jiǎn)單性可以縮短設(shè)計(jì)時(shí)間。

圖 13.250 MSPS ADC 和 1 GSPS ADC 的 AAF 比較。

現(xiàn)代RF采樣ADC具有更多的數(shù)字處理能力,這意味著數(shù)字處理可以在ADC內(nèi)部快速完成。如本文前所述,這可實(shí)現(xiàn)高能效和I/O效率設(shè)計(jì)。現(xiàn)在,系統(tǒng)設(shè)計(jì)人員可以使用他/她的FPGA中未使用的JESD204B收發(fā)器來處理來自其他RF采樣ADC的數(shù)據(jù),這些ADC已經(jīng)處理了數(shù)據(jù)(模數(shù)轉(zhuǎn)換、濾波和抽取)。這樣就可以有效地使用FPGA資源,同時(shí)增加無線電設(shè)計(jì)中的通道數(shù)量。

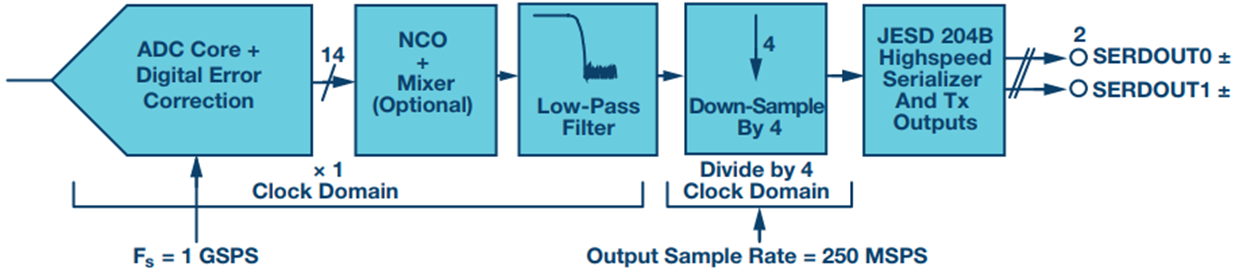

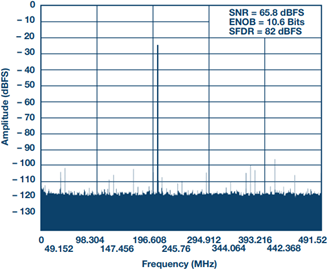

利用DDC,ADC可用作數(shù)字混頻器,以調(diào)諧至設(shè)計(jì)可能需要的任何IF。在此示例中,使用與上面討論的相同的頻率計(jì)劃。因此,使用具有實(shí)際混頻的抽取4選項(xiàng)來演示ADC的性能。如圖 14 所示。

圖 14.RF采樣速率為1 GSPS,DDC設(shè)置為抽取4。

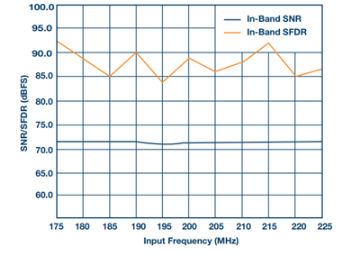

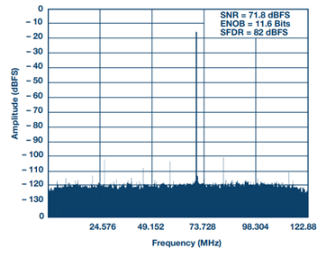

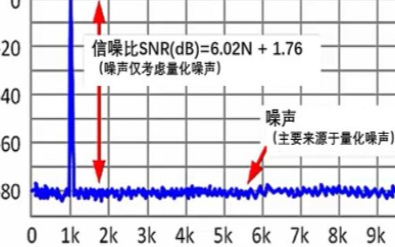

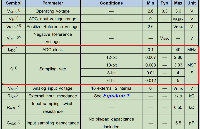

在正常或全帶寬模式下,AD9680的SNR約為66 dBFS至67 dBFS。但是,當(dāng)DDC運(yùn)行時(shí),抽取比設(shè)置為4時(shí),可以額外獲得6 dB的處理增益[3]。這可確保保持動(dòng)態(tài)范圍性能。由于RF采樣ADC的采樣速率為原始采樣速率的4×,因此諧波分散開來(如圖10所示)。RF采樣ADC中的DDC確保抽取濾波器以數(shù)字方式衰減不需要的信號(hào)。但是,落在目標(biāo)頻帶中的諧波(高階或其他)仍將顯示,因?yàn)镈DC允許它們通過。這可能是由放大器偽像或低通濾波器沒有足夠的衰減引起的。低通濾波器可以根據(jù)系統(tǒng)要求重新設(shè)計(jì),以滿足其他雜散性能。圖15顯示了1 GSPS ADC的SNR/SFDR與輸入頻率的關(guān)系。從數(shù)據(jù)中可以清楚地看出,使用DDC可將SNR提高6 dB(由于處理增益)和SFDR。在全帶寬模式下運(yùn)行時(shí),SFDR通常受到二次或三次諧波的限制,而在DDC模式下(抽取4),它是最差的其他諧波。

圖 15.圖14所示的1位、12 GSPS ADC設(shè)計(jì)的SNR/SFDR與頻率的關(guān)系。

抽取輸出的FFT如圖16所示。使用 DDC 時(shí),必須注意確保正確處理目標(biāo)頻帶。在這種情況下,NCO被調(diào)諧到200 MHz,以便感興趣的頻段落在抽取的奈奎斯特的中心。這降低了 FPGA 的處理開銷。為了進(jìn)行比較,AD9680在正常(全帶寬)工作下的FFT如圖17所示。

圖 16.205 GSPS ADC 上的 1 MHz FFT,抽取 4;NCO 調(diào)諧到 200 MHz。

圖 17.全帶寬模式下 205 GSPS ADC 上的 1 MHz FFT。

數(shù)據(jù)顯示,DDC除了改善帶內(nèi)噪聲性能外,還提供無次諧波的干凈頻譜。由于DDC對(duì)數(shù)據(jù)進(jìn)行濾波和抽取(至250 MSPS),因此它們還會(huì)降低輸出通道速率,從而為JESD204B串行接口提供靈活的選擇。這使系統(tǒng)設(shè)計(jì)人員可以在高通道速率(更昂貴)、低 I/O 數(shù) FPGA 或低通道速率(更便宜)、高 I/O 數(shù) FPGA 之間進(jìn)行選擇。

結(jié)論

RF采樣ADC在系統(tǒng)設(shè)計(jì)中具有獨(dú)特的優(yōu)勢(shì),這在幾年前是不可能的。業(yè)界正在尋求加速基礎(chǔ)設(shè)施的設(shè)計(jì)和實(shí)施,以應(yīng)對(duì)對(duì)更高帶寬的需求。設(shè)計(jì)時(shí)間和預(yù)算正在縮減,對(duì)更多軟件驅(qū)動(dòng)的可擴(kuò)展、可重新配置架構(gòu)的需求有助于成為新常態(tài)。對(duì)帶寬需求的增加也伴隨著對(duì)更高容量的需求。這給FPGA I/O帶來了額外的壓力,RF采樣ADC可以通過使用其內(nèi)部DDC來抵消壓力。

審核編輯:郭婷

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論