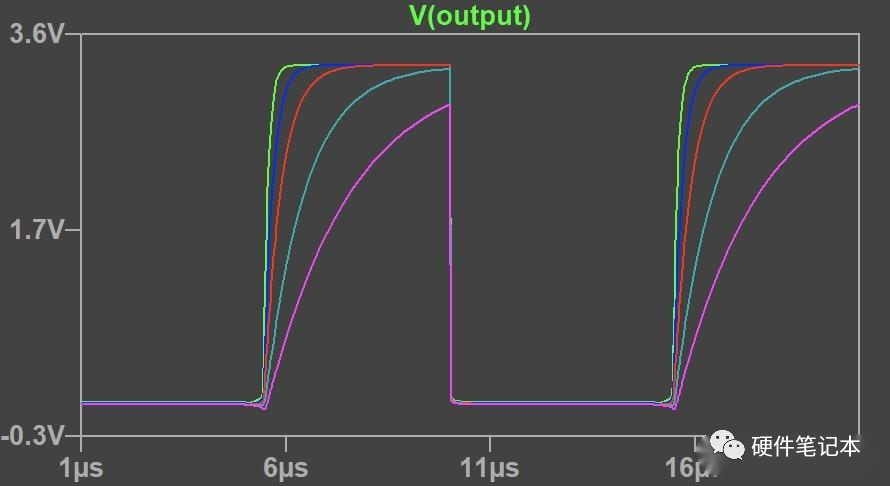

經(jīng)常會(huì)聽到MCU某I/O的驅(qū)動(dòng)能力是xxmA,那么到底什么是驅(qū)動(dòng)能力呢?如果某IO的驅(qū)動(dòng)能力是5mA,它就輸出不了超過5mA的電流了嗎?為什么IO的驅(qū)動(dòng)能力有差異呢?

2022-09-19 11:32:57 3958

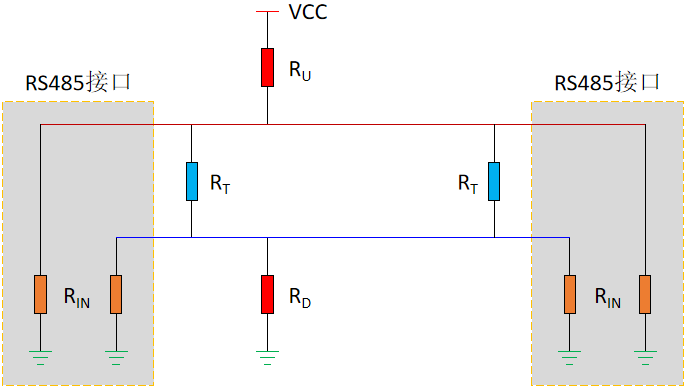

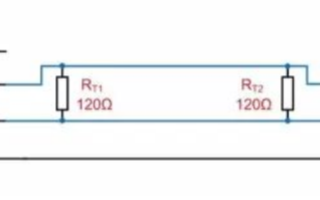

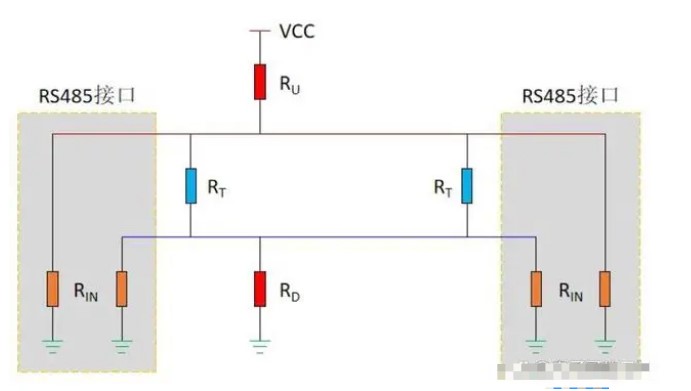

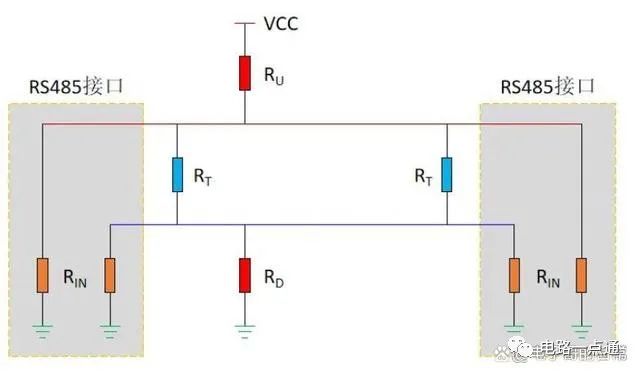

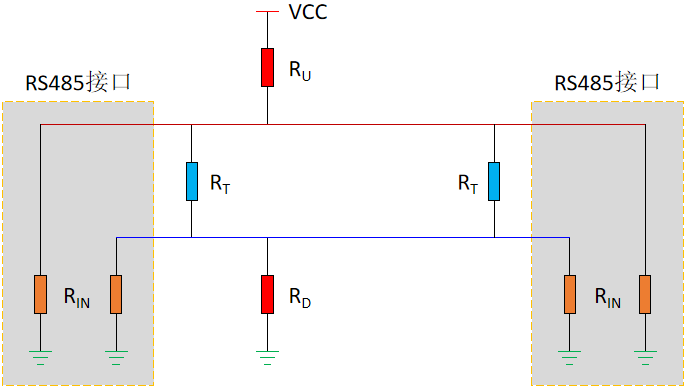

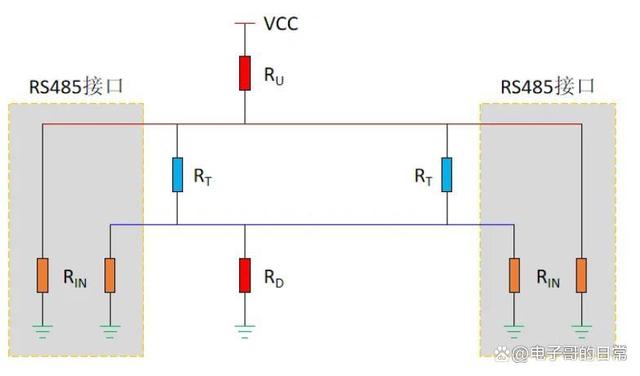

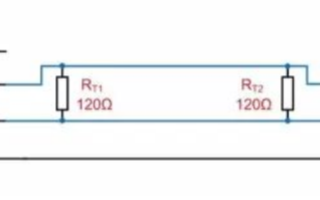

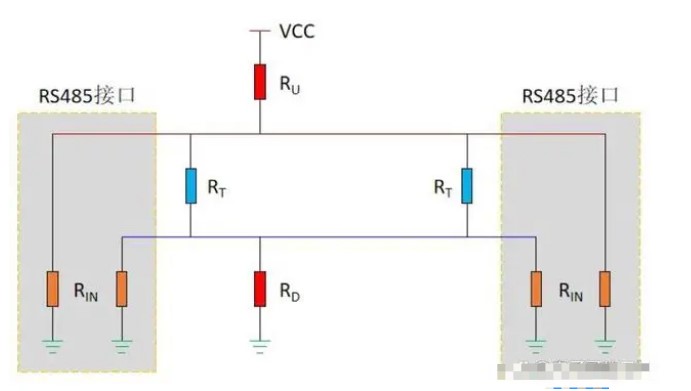

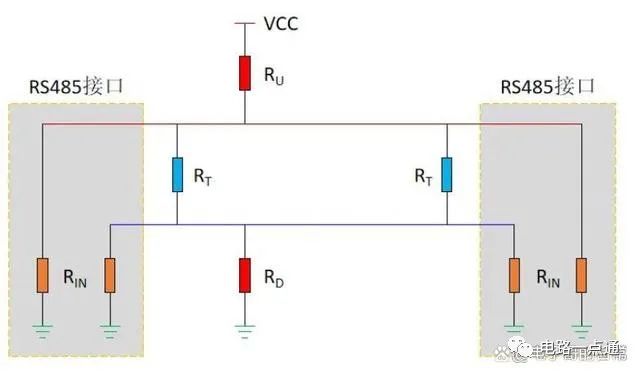

3958 RS485是一種常見的通訊接口方式,在我們的實(shí)際產(chǎn)品中也是多次使用。但我們平常并不會(huì)去過多考慮某一實(shí)現(xiàn)的細(xì)節(jié)問題,不過最近我們遇到了一個(gè)因如上下拉電阻的選擇問題而造成的通訊故障,所以在這一片中我們來討論一下RS485總線上下拉電阻的選擇問題。

2022-12-14 15:47:55 5006

5006

經(jīng)常會(huì)聽到MCU某I/O的驅(qū)動(dòng)能力是xxmA,那么到底什么是驅(qū)動(dòng)能力呢?如果某IO的驅(qū)動(dòng)能力是5mA,它就輸出不了超過5mA的電流了嗎?為什么IO的驅(qū)動(dòng)能力有差異呢?

2023-03-13 10:56:56 872

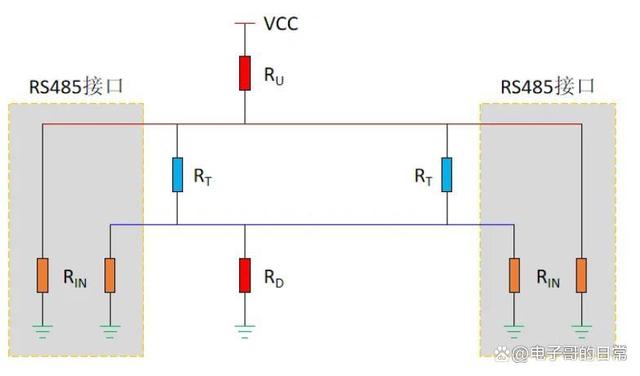

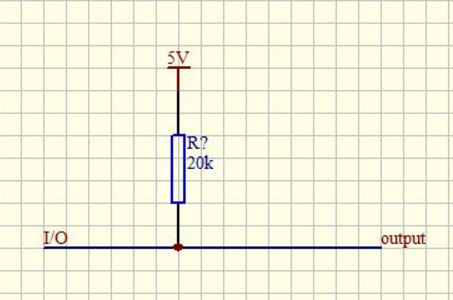

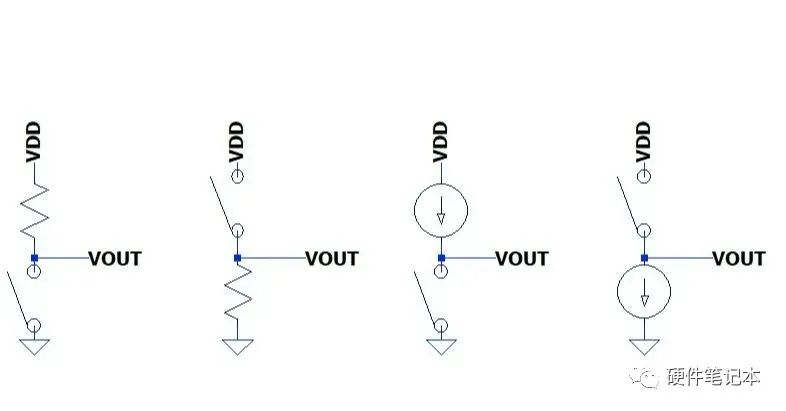

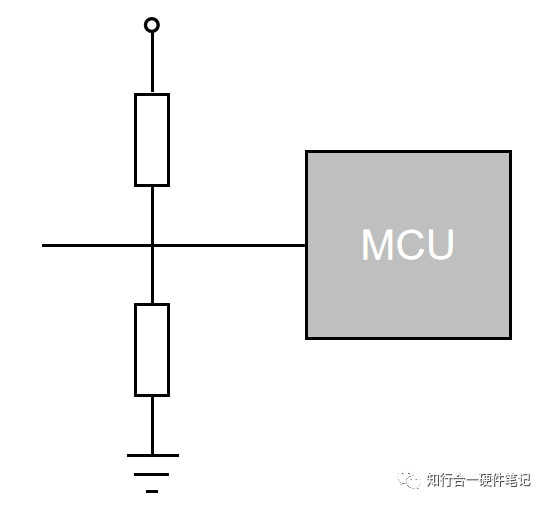

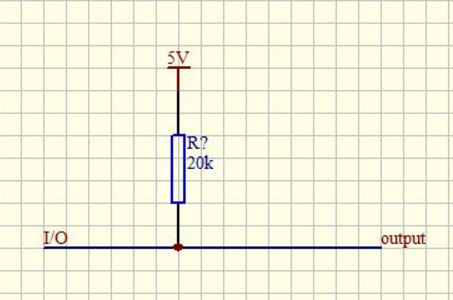

872 一、上下拉電阻介紹 ??上拉電阻:將一個(gè)不確定的信號(hào),通過一個(gè)電阻與電源VCC相連,固定在高電平。作用:上拉是對(duì)器件注入電流;灌電流;當(dāng)一個(gè)接有上拉電阻的IO端口設(shè)置為輸入狀態(tài)時(shí),它的常態(tài)為高電平

2023-04-21 09:49:34 6887

6887 電路設(shè)計(jì)中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會(huì)損壞電子器件。

2023-10-08 16:23:42 1186

1186

之前始終對(duì)維持確定的高低電平狀態(tài)沒有足夠深的理解,既然單片機(jī)自身是有輸出高低電平的能力,為什么還需要在外部上下拉,這不是浪費(fèi)能量嗎?

2023-11-06 15:37:13 611

611

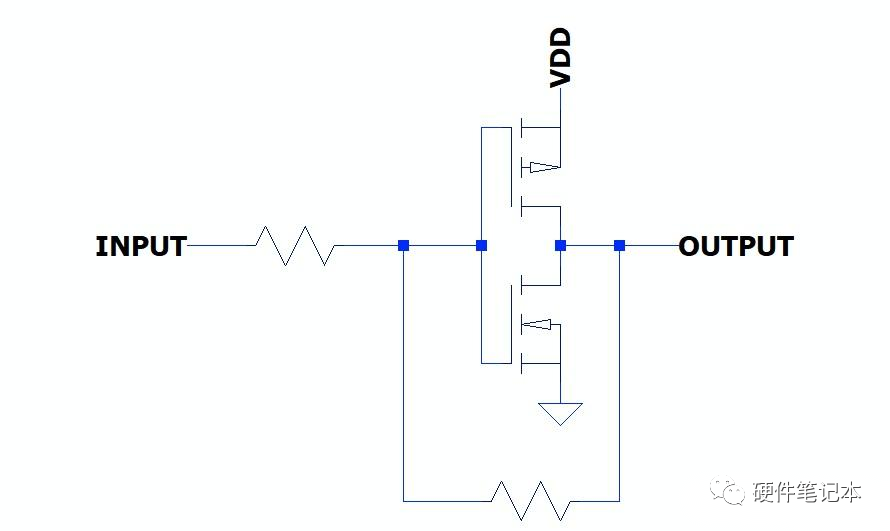

作為電路中最常見的電子元器件之一,電阻可以實(shí)現(xiàn)限流、隔離、上下拉等不同功能。以上拉為例,IIC通信接口SDA和SCLK都需要通過電阻實(shí)現(xiàn)上拉輸入/輸出。那么,電阻是如何實(shí)現(xiàn)上下拉功能的呢?

2023-11-13 18:23:06 788

788

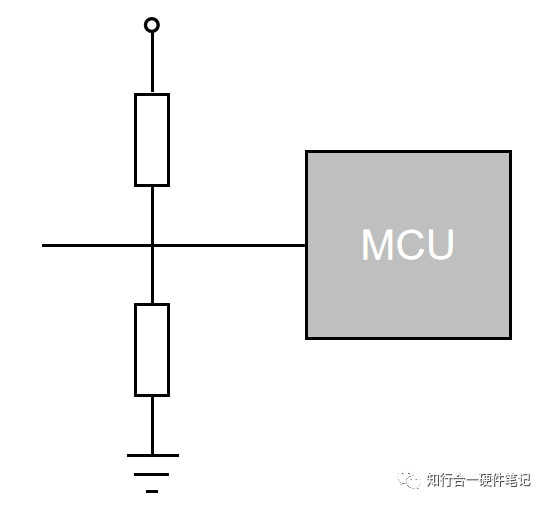

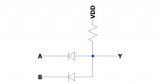

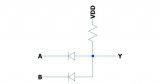

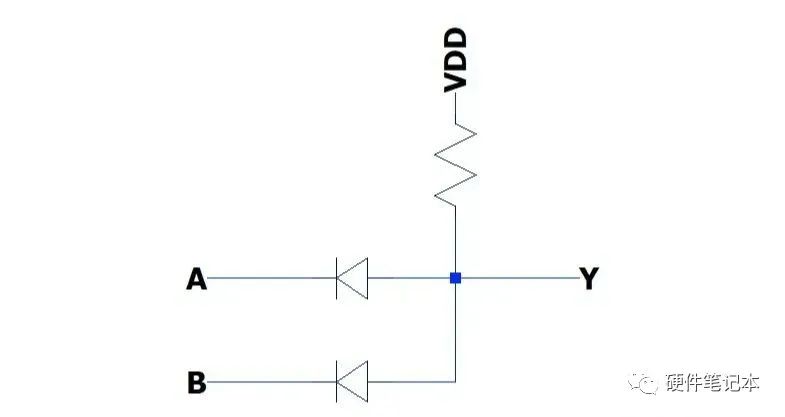

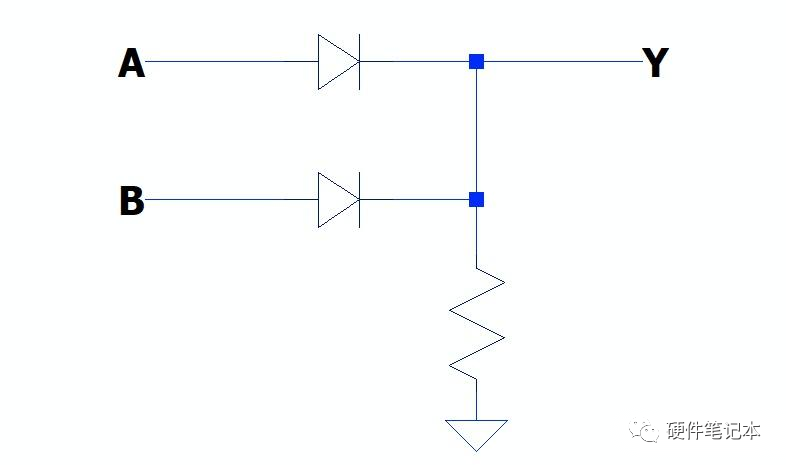

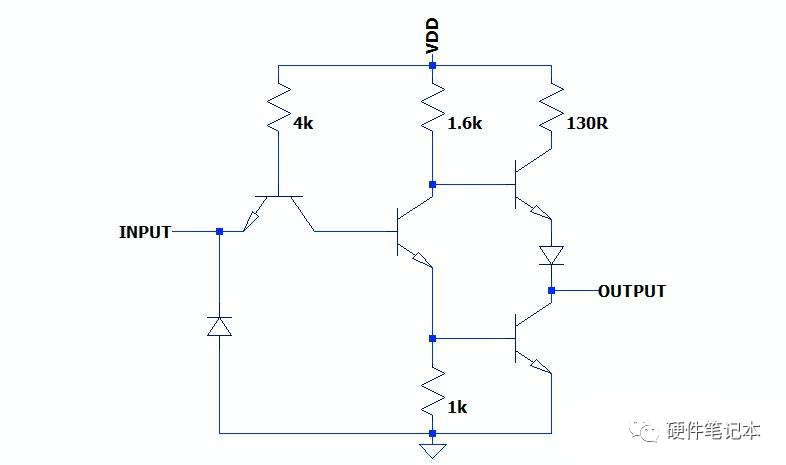

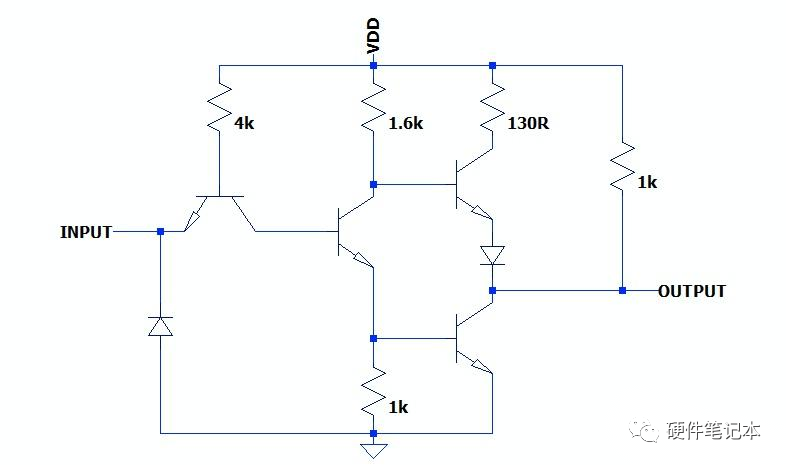

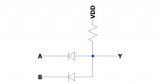

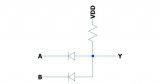

一個(gè)最簡(jiǎn)單的二極管與門如下圖。與門實(shí)現(xiàn)邏輯與操作Y=A&B,即A或者B任意為L的時(shí)候,輸出Y為L,只有當(dāng)A和B都為H時(shí),Y才為H。

2023-12-02 11:05:34 333

333

0-10V調(diào)光器上拉和下拉能力分別是多少? 我要并接100個(gè)調(diào)光電源,調(diào)光器的驅(qū)動(dòng)能力是否會(huì)不夠?

2019-06-10 14:59:39

74HC595為什么帶不動(dòng)芯片的驅(qū)動(dòng)能力?74HC595是怎么提高芯片的驅(qū)動(dòng)能力的呢?

2021-10-25 09:01:06

低電平,作用嗎:比如:當(dāng)一個(gè)接有上拉電阻的端口設(shè)為輸如狀態(tài)時(shí),他的常態(tài)就為高電平,用于檢測(cè)低電平的輸入。上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就

2013-07-21 21:43:41

|+-----+ |元件| |+-----+ +------+=下拉電阻 -Gnd 一般來說上拉或下拉電阻的作用是增大電流,加強(qiáng)電路的驅(qū)動(dòng)能力 比如說51的p1口 還有,p0口必須接上拉電阻才可以

2012-03-08 14:59:41

深入淺出上拉電阻下拉電阻淺談上下拉電阻思考:上下拉電阻有什么用呢?答:上下拉電阻的作用非常簡(jiǎn)單,就是將一個(gè)不確定的信號(hào)確定下來。通過上拉電阻將不確定的信號(hào)鉗位到高電平,通過下拉電阻,將不確定的信號(hào)鉗

2021-11-30 06:07:53

拉電阻2.0淺談上下拉電阻思考:上下拉電阻有什么用呢?答:上下拉電阻的作用非常簡(jiǎn)單,就是將一個(gè)不確定的信號(hào)確定下來。通過上拉電阻將不確定的信號(hào)鉗位到高電平,通過下拉電阻,將不確定的信號(hào)鉗位到低電平

2022-01-14 06:50:45

上下拉電阻的作用

2015-04-18 21:21:07

嗎: 比如:當(dāng)一個(gè)接有上拉電阻的端口設(shè)為輸如狀態(tài)時(shí),他的常態(tài)就為高電平,用于檢測(cè)低電平的輸入。 l 上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是灌電流

2016-09-23 17:19:31

器件連接時(shí)的灌電流能力不盡相同,連接上會(huì)有驅(qū)動(dòng)問題,此時(shí)需要加上拉電阻,加大輸出引腳的驅(qū)動(dòng)能力。 阻抗匹配長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配(并聯(lián)終端匹配),有效的抑制反射波

2019-07-27 08:38:52

上下拉電阻的用法

2012-08-16 13:38:14

的端口設(shè)為輸如狀態(tài)時(shí),他的常態(tài)就為高電平,用于檢測(cè)低電平的輸入。上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是灌電流。 上拉就是將不確定的信號(hào)通過

2012-08-07 15:15:18

上下拉電阻的用途,總結(jié)一下,對(duì)很多人應(yīng)有幫助

2012-10-24 17:01:13

的輸入。 -------上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的。 上下拉一般有兩個(gè)用處:1)提高輸出信號(hào)的驅(qū)動(dòng)能力、 2)確定輸入信號(hào)的電平

2018-06-28 06:21:54

下拉電阻。上拉就是將不確定的信號(hào)通過一個(gè)電阻鉗位在高電平,電阻同時(shí)起限流作用。下拉同理。也是將不確定的信號(hào)通過一個(gè)電阻鉗位在低電平。不過從程序設(shè)計(jì)的角度講,上拉就是如果沒有輸入信號(hào)則此時(shí)I/O狀態(tài)為1,下拉相反。具體配置為上拉還是下拉,要看電路圖。看外部有沒有上下拉電阻。

2019-05-21 06:21:09

回波干擾)上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是灌電流。上拉是對(duì)器件注入電流,下拉是輸出電流。上拉電阻阻值的選擇原則包括1、從節(jié)約功耗及芯片

2012-02-24 10:38:07

IO驅(qū)動(dòng)能力設(shè)置說明AT32F4xx IO 驅(qū)動(dòng)能力設(shè)置同其它MCU 的不同之處

2023-10-19 06:08:32

驅(qū)動(dòng)能力電源驅(qū)動(dòng)能力 -> 輸出電流能力 -> 輸出電阻1、指輸出電流的能力,比如芯片的IO在高電平時(shí)的最大輸出電流是4mA -> 該IO口的驅(qū)動(dòng)驅(qū)動(dòng)能力為4mA2、負(fù)載過大

2022-01-17 06:35:01

想問一下什么情況下需要加上下拉電阻?為什么需要加上下拉電阻?

2021-03-06 06:31:18

STM32不同組的GPIO驅(qū)動(dòng)能力有什么差別呢,為什么同樣的電路換組IO就不行呢

2018-10-26 10:14:42

STM32不同組的GPIO驅(qū)動(dòng)能力有什么差別呢,為什么同樣的電路換組IO就不行呢

2018-12-06 16:12:24

解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是你同學(xué)說的灌電流

2011-09-19 08:55:51

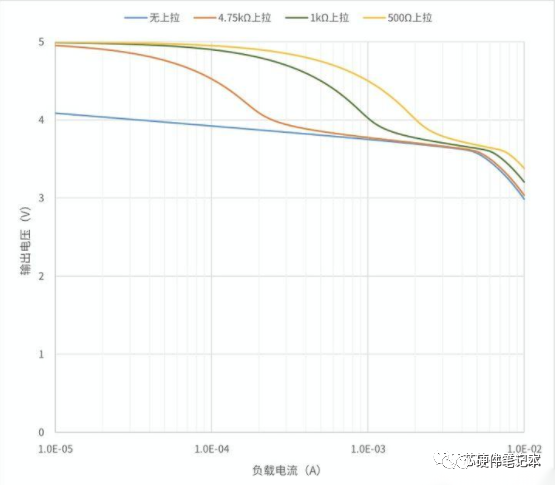

的選擇應(yīng)結(jié)合開關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定,主要需要考慮以下幾個(gè)因素:驅(qū)動(dòng)能力與功耗的平衡。 以上拉電阻為例,一般地說,上拉電阻越小,驅(qū)動(dòng)能力越強(qiáng),但功耗越大,設(shè)計(jì)是應(yīng)注意兩者之間的均衡。下級(jí)電路的驅(qū)動(dòng)需求。同樣以上拉電阻為例,當(dāng)輸出高電平時(shí),開關(guān)管斷開,上拉電阻應(yīng)適當(dāng)選擇以能夠向下級(jí)電路

2021-11-12 07:28:55

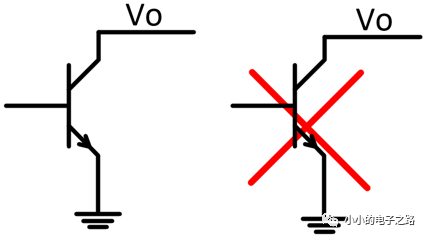

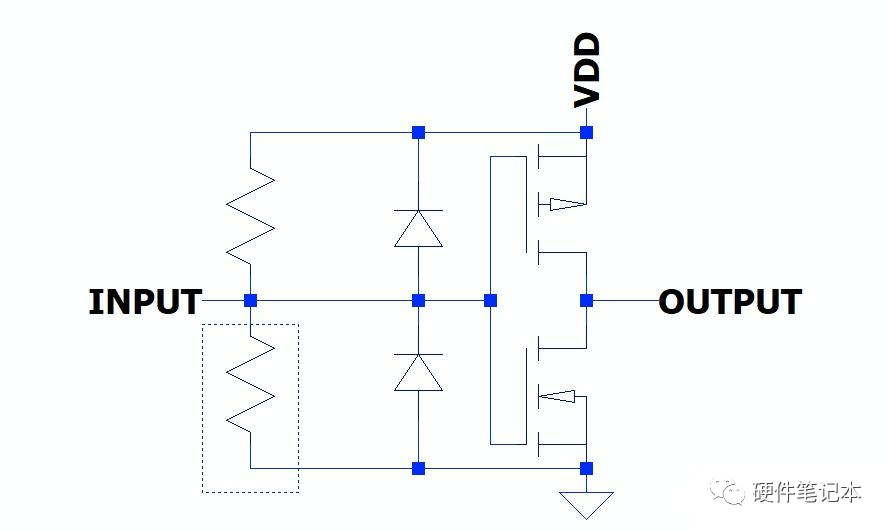

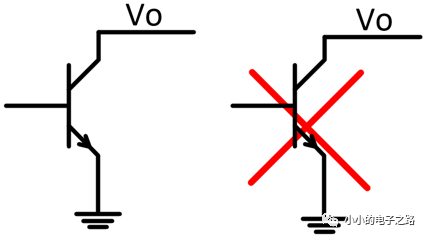

TTL電路驅(qū)動(dòng)CMOS電路時(shí),如果電路輸出的高電平低于CMOS電路的最低高電平(一般為 3.5V), 這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2.OC門電路必須使用上拉電阻,以提高輸出的高電平值。3.為增強(qiáng)輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。4.在CMO

2022-01-25 07:23:49

嗎: 比如:當(dāng)一個(gè)接有上拉電阻的端口設(shè)為輸如狀態(tài)時(shí),他的常態(tài)就為高電平,用于檢測(cè)低電平的輸入。 l 上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是你同學(xué)說的灌電流

2008-05-22 08:46:35

就為高電平,用于檢測(cè)低電平的輸入”。4、上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是我們通常所說的灌電流5、接電阻就是為了防止輸入端懸空6、減弱外部

2015-06-24 11:24:37

,該電阻稱為下拉電阻,使該端口平時(shí)為低電平,作用嘛: 比如:當(dāng)一個(gè)接有上拉電阻的端口設(shè)為輸如狀態(tài)時(shí),他的常態(tài)就為高電平,用于檢測(cè)低電平的輸入。 l 上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供

2019-06-27 05:55:08

電阻的作用是增大電流,加強(qiáng)電路的驅(qū)動(dòng)能力比如說51的p1口還有,p0口必須接上拉電阻才可以作為io口使用上拉和下拉的區(qū)別是一個(gè)為拉電流,一個(gè)為灌電流一般來說灌電流比拉電流要大也就是灌電流驅(qū)動(dòng)能力強(qiáng)一

2019-09-05 11:52:04

衡量電路輸出驅(qū)動(dòng)能力的幾個(gè)概念為什么能夠衡量輸出驅(qū)動(dòng)能力

2021-02-24 07:33:06

、OC門電路必須加上拉電阻,才能使用。3、為加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗

2016-09-27 09:20:11

一、什么是上下拉電阻?上拉、下拉電阻統(tǒng)一稱為拉電阻,作用是將狀態(tài)不確定的信號(hào)線通過一個(gè)電阻將其箝位至高電平(上拉)或低電平(下拉)這里有人可能會(huì)疑惑?什么叫狀態(tài)不確定的信號(hào)?在數(shù)字電路中,通常有三種

2022-01-14 08:58:32

) 。

一般來說上拉或下拉電阻的作用是增大電流,加強(qiáng)電路的驅(qū)動(dòng)能力。比如說51的p1口,還有,p0口必須接上拉電阻才可以作為io口使用。上拉和下拉的區(qū)別是一個(gè)為拉電流,一個(gè)為灌電流。一般來說灌電流比拉電流要大,也就

2023-05-18 17:30:56

持系統(tǒng)設(shè)計(jì)中,已經(jīng)不容小覷了.100k的上拉下拉我較少看到,是否因?yàn)?b class="flag-6" style="color: red">驅(qū)動(dòng)能力太弱,為0.01ma的量級(jí).一般來說,在電壓驅(qū)動(dòng)模式的電路中,100k電阻被使用吧.但是不是說,這樣我們就一味選擇10k電阻呢

2015-10-19 18:06:17

般情況下電壓在5V時(shí)選4.7K左右,3.3V在3.3K左右.這樣可加大驅(qū)動(dòng)能力和加速邊沿的翻轉(zhuǎn)I2C上拉電阻確定有一個(gè)計(jì)算公式:Rmin={Vdd(min)-o.4V}/3mARmax=(T

2011-10-25 09:53:50

,用于檢測(cè)低電平的輸入”。4、上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是我們通常所說的灌電流5、接電阻就是為了防止輸入端懸空6、減弱外部電流對(duì)芯片

2018-11-30 11:55:14

各位好,如下圖,本來想在參考源后面加運(yùn)放跟隨來提高驅(qū)動(dòng)能力,可結(jié)果驅(qū)動(dòng)能力變低了。飛線直接連可以驅(qū)動(dòng),過運(yùn)放跟隨后就不行了,各位大神,這是為啥呢,這種做法有啥問題呢還是

2019-08-02 17:31:08

電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是我們通常所說的灌電流5、接電阻就是為了防止輸入端懸空6、減弱外部電流對(duì)芯片產(chǎn)生的干擾7、保護(hù)cmos內(nèi)的保護(hù)

2011-07-28 09:58:10

請(qǐng)教如何測(cè)量單根信號(hào)驅(qū)動(dòng)能力, 比如A信號(hào),在不知此信號(hào)作用,不知是否為電源電壓還是IO電壓的前提下,且不能拆開該產(chǎn)品, 有沒辦法測(cè)量出A信號(hào)的驅(qū)動(dòng)能力(可以帶載多少電流) ,前提是不能把現(xiàn)有的產(chǎn)品燒壞!

2019-02-22 11:17:43

如何設(shè)計(jì)才能提升LED的驅(qū)動(dòng)能力?

2021-04-09 06:57:08

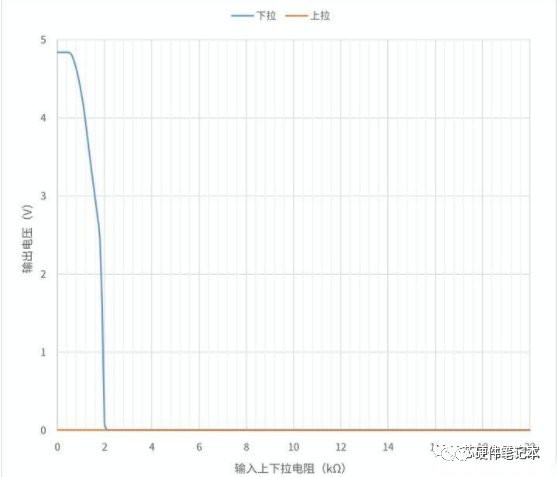

RS-485總線廣泛應(yīng)用于通信、工業(yè)自動(dòng)化等領(lǐng)域,在實(shí)際應(yīng)中,通常會(huì)遇到是否需要加上下拉電阻以及加多大的電阻合適的問題,下面我們將對(duì)這些問題進(jìn)行詳細(xì)的分析。一、為什么需要加上下拉電阻?根據(jù)

2019-05-21 07:10:59

更多的工資,一個(gè)道理)一般情況下,這種驅(qū)動(dòng)重負(fù)載(小電阻)的電路連接是不會(huì)燒毀內(nèi)部晶體管的,因?yàn)閮?nèi)部也是有限流電阻的,換句話講,就算輸出引腳對(duì)地短路,輸出電流也不會(huì)超過最大的驅(qū)動(dòng)能力(除非是不正

2020-08-19 09:00:00

已知上下拉電阻,怎么計(jì)算出AD值,下拉電阻是10k,上拉接NTC

2018-07-18 14:39:51

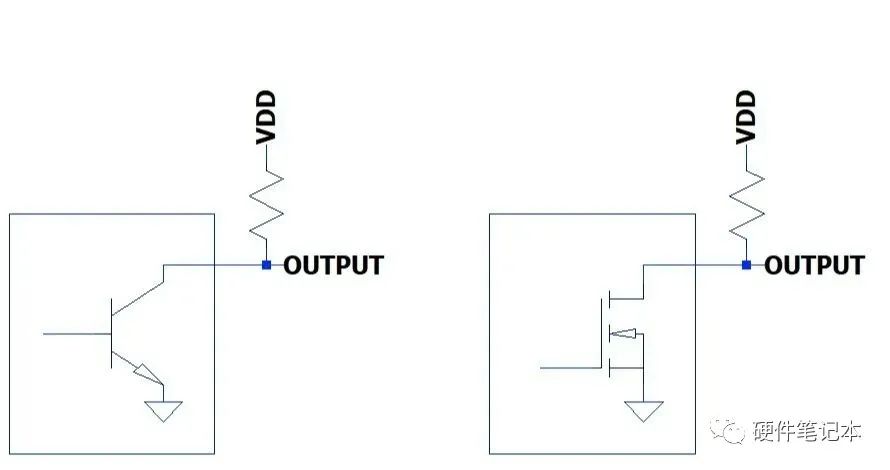

開漏輸出模式下不外接上拉電阻有驅(qū)動(dòng)能力嗎

2023-10-15 13:28:20

為什么說驅(qū)動(dòng)能力不夠是因?yàn)樘峁╇娏魈《皇请妷海亢头治?b class="flag-6" style="color: red">驅(qū)動(dòng)能力不夠?什么情況下要考慮啟動(dòng)能力驅(qū)動(dòng)能力?怎么知道在集成電路里和平常IC驅(qū)動(dòng)能力是否足夠?

2021-10-09 09:44:23

道理 對(duì)上拉電阻和下拉電阻的選擇應(yīng)結(jié)合開關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定,主要需要考慮以下幾個(gè)因素: 驅(qū)動(dòng)能力與功耗的平衡。以上拉電阻為例,一般地說,上拉電阻越小,驅(qū)動(dòng)能力越強(qiáng),但功耗越大,設(shè)計(jì)是應(yīng)

2014-11-17 10:24:15

如何去使用上拉電阻?上拉電阻阻值的選擇原則包括哪些?拉電流和灌電流為什么能夠衡量輸出驅(qū)動(dòng)能力?

2021-09-30 09:03:13

到10k 之間選取。對(duì)下拉電阻也有類似道理。 對(duì)上拉電阻和下拉電阻的選擇應(yīng)結(jié)合開關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定,主要需要考慮以下幾個(gè)因素:1、驅(qū)動(dòng)能力與功耗的平衡。以上拉電阻為例,一般地說,上

2014-08-21 09:56:08

驅(qū)動(dòng)器的上拉、下拉的電阻值(典型值和最大值),同時(shí)也給出了最小的連續(xù)驅(qū)動(dòng)電流值200mA,因此可以得出:4A的驅(qū)動(dòng)電流能力應(yīng)該為脈沖電流值。后面的峰值電流和電源電壓的關(guān)系圖也說明了這一點(diǎn)。EL7104

2017-02-20 17:46:04

我用f28377的GPIO口做大功率可控硅的驅(qū)動(dòng),可惜GPIO的輸出電流太小,不能夠直接驅(qū)動(dòng)TIP122,問用什么芯片可以增強(qiáng)GPIO口的驅(qū)動(dòng)能力

2020-05-29 15:21:24

問電路必須加上拉電阻,以提高輸出的電平值。3.為加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上接電阻。4.在CMOS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻降低輸入阻抗

2017-05-22 18:49:54

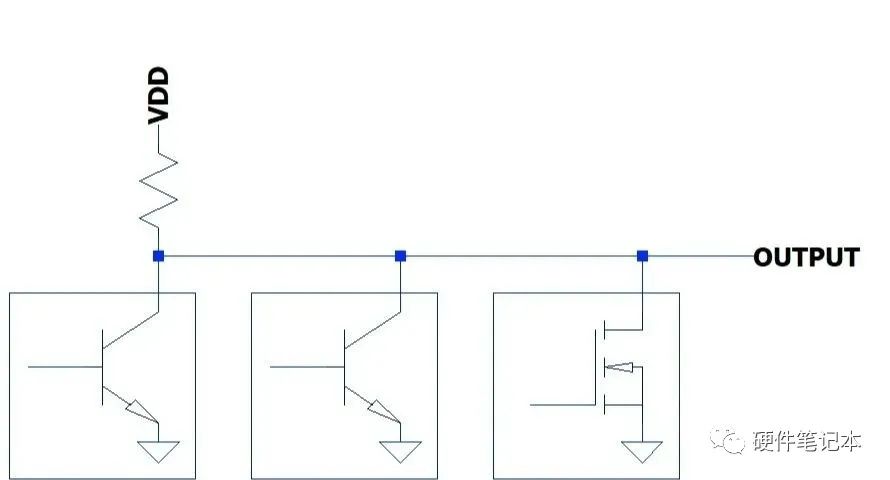

2、驅(qū)動(dòng)能力問題CMOS電路的驅(qū)動(dòng)能力的提高,除選用驅(qū)動(dòng)能力較強(qiáng)的緩沖器來完成之外,還可將同一個(gè)芯片幾個(gè)同類電路并聯(lián)起來提高,這時(shí)驅(qū)動(dòng)能力提高到N倍(N為并聯(lián)門的數(shù)量)。如圖2所示。3、輸入端

2021-09-17 06:49:26

或下拉來增加或減小驅(qū)動(dòng)電流。11、增加高電平輸出時(shí)的驅(qū)動(dòng)能力。1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),若TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接

2018-10-25 22:42:06

驅(qū)動(dòng)能力是后級(jí)電路帶負(fù)載能力的大小,影響因素是后級(jí)負(fù)載大小、電壓要求的大小等。對(duì)于要求精細(xì)的芯片來說,輸出的電壓和電流各不相同,但是總的功率是一定的。74HC595(總線驅(qū)動(dòng)器,典型的TTL型三態(tài)

2021-07-29 09:21:38

加上拉電阻,程序可以正常跑通,但有些資料卻強(qiáng)調(diào)說單片機(jī)的IO口使用時(shí)要加上拉、下拉電阻。以下就以LBQ同學(xué)的可愛問題解釋一下上下拉電阻吧。事不宜遲,馬上進(jìn)入正題首先聲明一下:我們這次用的是STC89...

2022-01-14 07:09:37

RS485是一種常見的通訊接口方式,在我們的實(shí)際產(chǎn)品中也是多次使用。但我們平常并不會(huì)去過多考慮某一實(shí)現(xiàn)的細(xì)節(jié)問題,不過最近我們遇到了一個(gè)因如上下拉電阻的選擇問題而造成的通訊故障,所以在這一

2023-04-27 17:03:40

,CyU3PGpioSetValue,在配置參數(shù)里CyU3PGpioSimpleConfig_t的結(jié)構(gòu)里,沒有看到此io口是否可以配置內(nèi)部上拉或下拉電阻。請(qǐng)為cx3的io口沒有內(nèi)部上拉電阻或下拉電阻嗎?我們?cè)O(shè)計(jì)電路時(shí)必須自己考慮外部上拉下拉來提升驅(qū)動(dòng)能力嗎?

2024-02-28 06:25:22

我想用8路DA芯片AD5668,系統(tǒng)要求它每個(gè)DA輸出通道的驅(qū)動(dòng)能力大于2mA。但查看手冊(cè)并沒有發(fā)現(xiàn)它的驅(qū)動(dòng)能力是多少,麻煩告知一下。謝謝。

2018-08-10 06:43:54

請(qǐng)問ADuM1400的驅(qū)動(dòng)能力如何?例如用于SPI總線隔離,輸出端可否同時(shí)驅(qū)動(dòng)多個(gè)具有SPI接口的器件?或者說能驅(qū)動(dòng)能力取決于什么?

2018-09-07 10:20:58

DSP芯片有多大的驅(qū)動(dòng)能力?

2019-09-10 05:55:55

stm32的驅(qū)動(dòng)能力有多大?

2019-08-15 04:35:17

問題描述很簡(jiǎn)單,但是一直困擾我常聽說上拉電阻可以增加信號(hào)驅(qū)動(dòng)能力,那么本來就是驅(qū)動(dòng)能力弱,再加上一個(gè)電阻,豈不是更加削弱了信號(hào)的驅(qū)動(dòng)能力嗎?謝謝回答!

2020-08-28 02:12:57

這個(gè)是在書上截取的一段話,照這樣下去,要提高IO的驅(qū)動(dòng)能力,外部多并聯(lián)幾個(gè)上拉電阻或者接一個(gè)小一點(diǎn)的上拉電阻豈不是驅(qū)動(dòng)都省了?

2019-08-02 04:36:31

上拉電阻與下拉電阻

上下拉電阻: 1、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),

2008-01-14 13:10:44 6297

6297 上拉電阻和下拉電阻的選型和計(jì)算,根據(jù)不同情況選擇不同上下拉電阻的方法

2015-11-30 18:20:28 0

0 上拉電阻,與下拉電阻的分析

2017-07-24 16:40:20 70

70 (或漏極)開路輸 出型電路(如普通門電路)提升電流和電壓的能力是有限的,上拉電阻的功能主要是為集電極開路輸出型電路輸出電流通道。 二、上下拉電阻作用: 1、提高電壓準(zhǔn)位: a. 當(dāng) TTL 電路驅(qū)動(dòng) COMS 電路時(shí),如果 TTL 電路輸出的高電平

2017-11-27 15:59:38 77866

77866

上拉電阻就是將不確定的信號(hào)通過一個(gè)電阻拉到高電平,同時(shí)此電阻也起到一個(gè)限流作用,下拉就是下拉到低電平。

2018-11-02 16:22:25 8495

8495 本文主要介紹了上下拉電阻的接線方法及作用。

2019-09-30 11:27:36 17287

17287

詳解RS-485上下拉電阻的選擇

2020-02-27 15:33:50 5869

5869

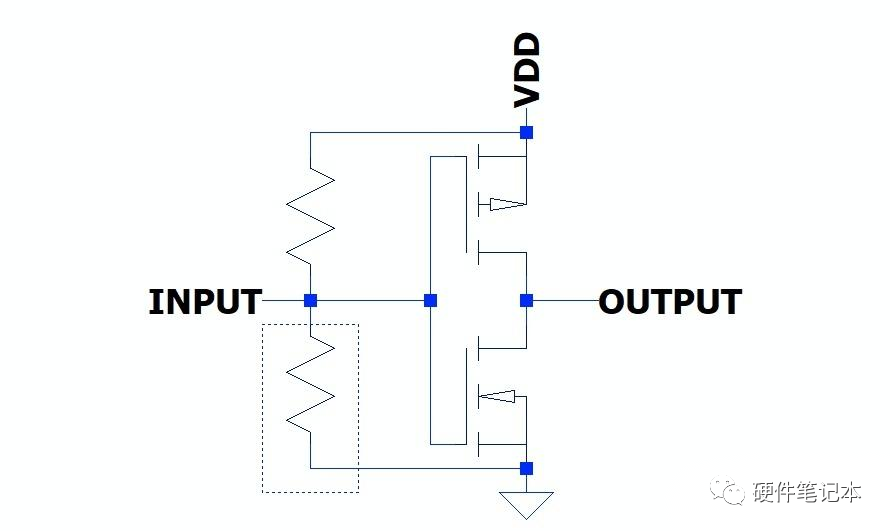

加上下拉電阻就是加在單片機(jī)管腳的帶負(fù)荷能力。如上拉電阻的接法就是電源正通過一個(gè)合適阻值的電阻后接到需上接的管腳即可。

2020-09-18 16:44:22 5375

5375

的選擇應(yīng)結(jié)合開關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定,主要需要考慮以下幾個(gè)因素:驅(qū)動(dòng)能力與功耗的平衡。 以上拉電阻為例,一般地說,上拉電阻越小,驅(qū)動(dòng)能力越強(qiáng),但功耗越大,設(shè)計(jì)是應(yīng)注意兩者之間的均衡。下級(jí)電路的驅(qū)動(dòng)需求。同樣以上拉電阻為例,當(dāng)輸出高電平時(shí),開關(guān)管斷開,上拉電阻應(yīng)適當(dāng)選擇以能夠向下級(jí)電路

2021-11-07 13:51:03 26

26 深入淺出上拉電阻下拉電阻淺談上下拉電阻思考:上下拉電阻有什么用呢?答:上下拉電阻的作用非常簡(jiǎn)單,就是將一個(gè)不確定的信號(hào)確定下來。通過上拉電阻將不確定的信號(hào)鉗位到高電平,通過下拉電阻,將不確定的信號(hào)

2021-11-20 12:21:03 16

16 當(dāng)TTL電路驅(qū)動(dòng)CMOS電路時(shí),如果電路輸出的高電平低于CMOS電路的最低高電平(一般為 3.5V), 這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2.OC門電路必須使用上拉電阻,以提高輸出的高電平值。3.為增強(qiáng)輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也

2021-12-01 09:21:05 11

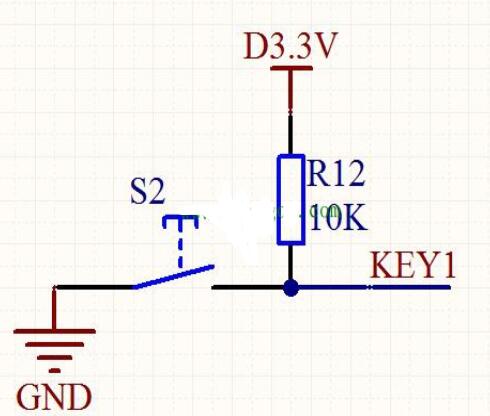

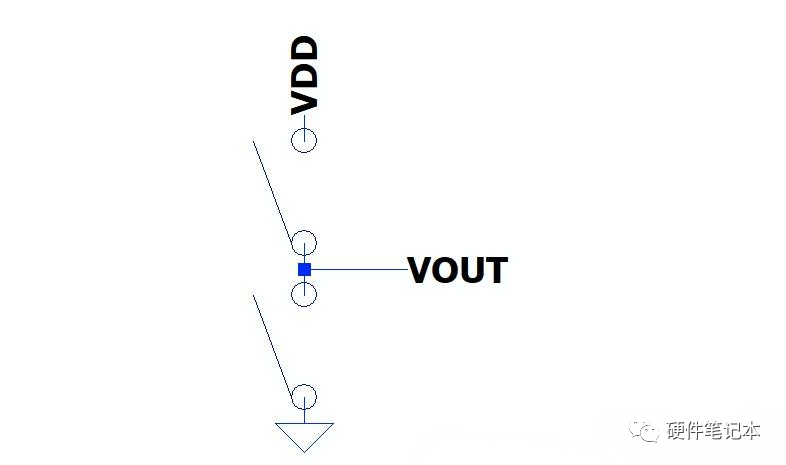

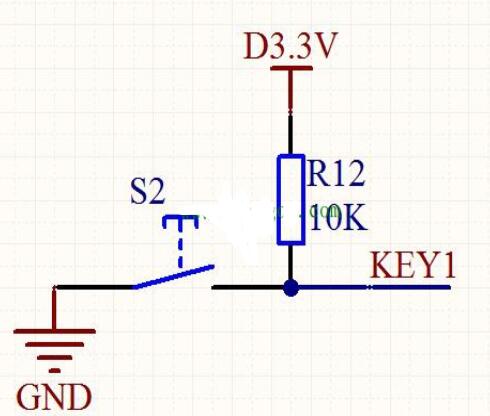

11 判斷上下拉電阻時(shí),只需要看按鍵按下之前,兩端是高電平還是低電平。例如:R1這個(gè)電阻,一端接VCC,在按鍵按下之前兩端是高電平,所以它就是上拉電阻,是為了檢測(cè)低電平輸入。R2這個(gè)電阻,一端接GND,在按鍵按下之前,兩端是低電平,所以它就是下拉電阻,是為了檢測(cè)高電平輸入。...

2022-01-14 14:00:34 19

19 上拉電阻和下拉電阻的選型和計(jì)算上下拉電阻的出發(fā)點(diǎn)在正常工作或單一故障狀態(tài)下,管腳均不應(yīng)出現(xiàn)不定狀態(tài)從功耗角度考慮,在長時(shí)間的管腳等待狀態(tài)下,管腳端口的電阻不應(yīng)消耗太多電流上下拉的選擇從抗擾角度出發(fā)

2022-01-14 14:06:35 31

31 -> 輸出電阻1、指輸出電流的能力,比如芯片的IO在高電平時(shí)的最大輸出電流是4mA -> 該IO口的驅(qū)動(dòng)驅(qū)動(dòng)能力為4mA2、負(fù)載過大(小電阻) -> 負(fù)載電流超過其最大輸出電流 -> 驅(qū)動(dòng)能力不足 -> 輸出電壓下降 -> 邏輯電路無法保持高電平 -> 邏輯混

2022-01-18 10:51:27 11

11 “上下拉電阻應(yīng)用很簡(jiǎn)單嗎?”那可不一定。電路設(shè)計(jì)中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會(huì)損壞電子器件。一般情況下,元器件需要上下拉的地方,加4.7K或10k,3.3K也行,甚至1K也可以,不會(huì)考慮太多。

2022-11-23 15:27:15 1510

1510

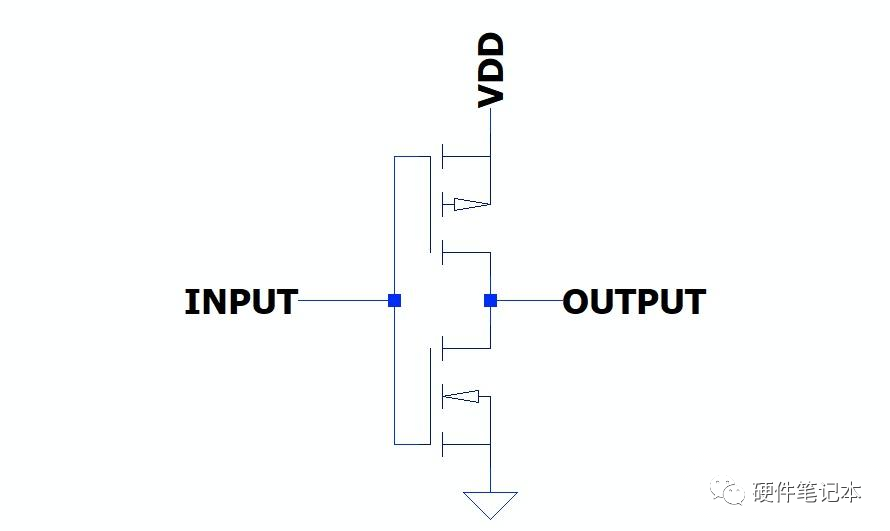

在這么原始的邏輯電路中就已經(jīng)出現(xiàn)了上下拉電阻,這里面的原理也非常簡(jiǎn)單粗暴:利用開關(guān)的閉合(電阻為0)和開啟(電阻無窮大)的特性,配合電阻,就可以輕松實(shí)現(xiàn)兩種電壓的輸出。

2023-02-20 09:26:14 1056

1056 下拉就是接地,上拉就相當(dāng)于升壓,提高驅(qū)動(dòng)能力或者穩(wěn)定性。 上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的問題的。一般說法是上拉增大電流,下拉電阻是用來吸收電流(抵抗干擾)。 上拉是將電壓拉高,下拉

2023-02-23 16:20:02 1236

1236 “上下拉電阻應(yīng)用很簡(jiǎn)單嗎?”那可不一定。電路設(shè)計(jì)中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會(huì)損壞電子器件。一般情況下,元器件需要上下拉的地方,加4.7K或10k,3.3K也行,甚至1K也可以,不會(huì)考慮太多。

2023-03-17 16:32:38 705

705

最近看到一個(gè)關(guān)于上下拉電阻的問題,發(fā)現(xiàn)不少人認(rèn)為上下拉電阻能夠增強(qiáng)驅(qū)動(dòng)能力。隨后跟幾個(gè)朋友討論了一下,大家一致認(rèn)為不存在上下拉電阻增強(qiáng)驅(qū)動(dòng)能力這回事,因?yàn)槌薕C輸出這類特殊結(jié)構(gòu)外,上下拉電阻就是

2023-08-10 09:19:11 305

305

上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的,一般說法是拉電流。下拉電阻是用來吸收電流的,也就是灌電流。

2023-08-22 14:20:26 1063

1063 芯片的驅(qū)動(dòng)能力指什么 芯片的驅(qū)動(dòng)能力指的是芯片在輸出電流和電壓時(shí)所能承受的最大值。在電子產(chǎn)品中,芯片驅(qū)動(dòng)能力的大小直接影響到該產(chǎn)品的性能和穩(wěn)定性。 芯片驅(qū)動(dòng)能力的大小是由芯片內(nèi)部的硅片晶體管以及外部

2023-08-29 10:06:38 1161

1161 在A和B兩條線上加上下拉電阻,以及加多大的電阻合適。本文將對(duì)這個(gè)問題進(jìn)行分析和解釋。485總線是如何工作的?首先,我們需要了解485總線的工作原理和信號(hào)特性。根據(jù)RS-48

2023-09-08 08:22:30 703

703

電阻是如何實(shí)現(xiàn)上下拉功能的呢? 上下拉功能是指在電路中通過連接電阻來實(shí)現(xiàn)對(duì)信號(hào)的上拉和下拉控制。在數(shù)字電路中,上拉和下拉功能通常用于控制輸入端的電平狀態(tài),確保輸入端在沒有外部信號(hào)輸入時(shí)能夠保持穩(wěn)定

2024-02-04 09:32:18 160

160

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論