移動通信系統發展數十年,一直為追求更高的頻譜效率而進行技術更新,從2G時代的GMSK,到3G時代的CDMA,到4G時代的OFDM。同時,大規模集成電路的設計技術與生產技術,也有了從幾百納米到幾十納米的時代變化。系統越來越大的帶寬需求,意味著對終端芯片平臺越來越高的處理能力要求。系統從2G 到4G的發展,無線網絡本身的發展也是需要一個較長的時間與過程,且對已有的2G和3G網絡的淘汰也不可能在一夜間完成,于是對終端芯片平臺也提出了自適應的隨網絡演進而變化的需求,即多種模式自動切換的工作模式需求。本文將從幾種無線通信系統對終端基帶芯片的需求開始討論,介紹一種由簡約納電子公司設計完成的適用于2G/3G/4G的軟件無線終端基帶芯片平臺。

1. 現有4G終端基帶芯片的狀況

如下圖1所示,4G無線通信系統基礎技術是OFDM。OFDM系統信號是時頻域都存在的陣列信號。時頻域信號間的變換,信道估計與MIMO檢測等大量陣列信號的處理,需要大量并行的矢量處理。高度并行的矢量處理器正應OFDM系統陣列信號處理需求而生。 多核多線程內核加上向量處理器是4G基帶芯片架構的大勢所趨。

圖1:OFDM系統陣列信號處理示意圖

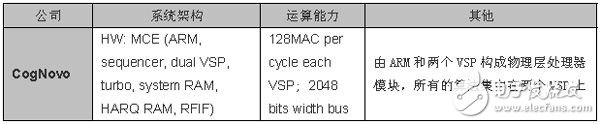

從已發表的有關無線終端基帶處理器的文獻和資料來看,業界在可編程和矢量處理應用方面已有許多進展,有如表1所示。

表1:基帶處理器中的處理能力

其它的還有IMEC 的ADRES,Michigan University 的ArdBerg等。

2. 2G/3G/4G的終端基帶系統需求分析

終端系統需求分為兩個方面,一是功能需求,一是性能需求。本章節通過抽象架構示意圖說明,2G/3G/4G幾個系統的功率需求;再逐步分析,不同的系統在性能上的需求。性能需求的分析,本文從系統帶寬,采樣率,到鏈路算法處理的復雜度分析入手。

2.1 無線通信終端基帶平臺的抽象架構

圖2:無線通信終端基帶平臺的抽象架構

功能需求如上圖2所示,所有的終端基帶系統都需要完成:

● 對上下行鏈路信號的處理,調制解調電路(或者算法),接收均衡與解碼電路(或者算法),對增益/頻率/功率的環路控制;

● 對通信鏈路的建立保持釋放等高層協議功能。

這些功能在不同的芯片上,構建不同的系統架構時,會有不同的軟硬件的分工。

2.2 2G/3G/4G系統的性能需求

圖3:2G/3G/4G系統性能需求示意圖

2G 是以語音通信為主的系統,3G是兼顧語音通信和數據通信的系統,4G是以高速數據通信為主體的系統。2G空中接口的帶寬小于200khz,能提供幾百 Kbps的數據流量;而3G帶寬約2Mhz,提供幾MBps數據流量;4G帶寬高于20MHz,提供超過100MBps數據流量。2G和3G射頻接口簡單,1個接收通道,1個發射通道,基帶信號的采樣率2G在1MHz左右(以4倍過采樣為例),3G約10MHz;4G的射頻接口有MIMO的模式,2--4個接收通道,1--2個發射通道,且基帶信號的采樣率大于30MHz。系統的基礎技術2G是GMSK調制方式和卷積碼;鏈路處理算法簡單,處理的數據量低;3G 是CDMA調制方式,卷積碼加Turbo碼,需要采用匹配濾波器和Turbo 解碼等比較復雜的算法,但處理的數據量還比較低;4G采用OFDM技術,卷積碼加Turbo碼,鏈路處理需要采用MIMO檢測和Turbo解碼等比較復雜的算法,且處理數據量相對于2G和3G大幅度提高,高層協議棧也需要有較大的數據流量處理的技術。以此為系統性能需求的基礎,可以分析得到物理層的運算量 2G每秒低于50MOPS的需求量,3G約每秒小于500MOPS,4G超過5000MOPS。高層協議棧處理,2G約每秒10MOPS左右,3G每秒小于100MOPS,而4G超過1000MOPS。對緩存的數據區域的需求:2G物理層低于128KBytes,高層協議棧低于256Kbytes;3G物理層小于512KBytes,高層協議棧小于5Mbytes;4G物理層超過2MBytes,高層協議棧超過20Mbytes。

2.3 無線通信終端基帶平臺的需求分析小結

綜上所述,從2G到4G的終端基帶平臺有著非常相似的系統功能架構,但由于系統帶寬和基礎技術的革命性變化,在性能需求上有著從量變到質變的飛躍。但相類似的功能架構,引導著架構設計者追尋一種可以兼顧幾個時代的終端基帶平臺。本文所述的方案則是這樣的一個平臺。

3. 基于定制方式的多模架構設計

由于4G的網絡建設還需要一段時間,4G終端芯片在架構設計時,需要考慮以多模的架構兼容2G/3G的需求,以便于終端在網絡中移動時可以充分的享用網絡的資源。

在 2G時代,傳統的芯片架構設計方案將其中物理層的部分采用電路邏輯實現,高層協議則由一個可編程的內核電路來運行相應的軟件。3G/4G時代,傳統的思路是繼承前者已有的電路,增加新的電路邏輯來實現物理層的部分,然后增加可編程內核的能力或者多個可編程內核來運行高層協議。于是,形成了如圖4所示的傳統多模架構。

圖4:傳統多模基帶芯片架構

這種的架構的好處是,開發周期相對短,2G和3G的物理層已經穩定工作,但主要缺陷是邏輯電路的面積也較大,從而導致芯片成本較高。

4. SL3000系統架構介紹

SL3000芯片是簡約納基于對2G/3G/4G終端基帶系統的理解,設計實現完成的一顆多模芯片。不同于定制電路(ASIC)的設計思路,SL3000的物理層采用分布式的多個向量處理器的架構,適用于2G/3G/4G多個不同的物理層算法運行;另外一個子系統也是由多個可編程的內核構成,以便于高層多模協議棧軟件運行。這兩個子系統獨立運行在不同的時鐘域,根據系統負載可以采用各自最合適的工作頻率。

4.1 SL3000的系統框圖

圖5:SL3000的系統架構

4.2 SL3000子系統功能簡介

如圖5所示,SL3000內部分為兩個大的子系統:L23子系統和PHY子系統。L23子系統由兩個SL-Core構成,每個SL-Core子系統中有獨自的Cache和RAM,以及DMA控制器和加解密模塊。兩個SL-Core之間有1Mbytes的共享內存。L23子系統還包含100M的GMAC控制器,USB2.0控制器,DDR 控制器等外設接口,為高速的數據通路提供接口。內核子系統與外設之間通過專有的網絡互聯互通。

圖6:不同信號處理要求不同的矢量處理器結構

PHY子系統由6個VE(Vector Engine)構成。如圖6所示,由于在不同的信號處理階段,信號本身具有不同的特征,需要矢量處理器也具有不同的特征。

其中三個VE是并行處理16位位寬的數據處理器,適用于通信鏈路中的I/Q數據處理的算法(例如均衡,匹配濾波,MIMO檢測,FFT等等);一個VE是并行處理8位位寬的數據處理器,適用于通信鏈路中的軟符號的處理(例如QAM解映射,HARQ軟合并等算法);一個VE是并行處理1位位寬的數據處理器,適用于比特編解碼算法(例如CRC計算,加解擾等);一個是Turbo解碼器,適用于3G/4G中的Turbo碼的處理。按照鏈路處理的需求,比特處理的 VE也承擔整個物理層調度的功能,它可以通過特定接口訪問其他幾個VE的內存空間,方便進行整個流程與時序的控制調度。其他幾個VE兩兩之間有特定的通路進行通信互聯,以便于數據在多個VE之間按照流水線處理的環節自然流暢地傳輸。

RFIF接口模塊可以適應采樣率從1MHz到 40MHz的范圍,有兩個接收通路和一個發射通路,可靈活處理有無MIMO的射頻前端接口。同時RFIF模塊內有可編程的基準時鐘模塊,可以通過改變外部輸入PLL的基準時鐘和時鐘倍頻參數,提供不同的2G或3G或4G的系統時鐘。RFIF模塊中有專門的DMA引擎,可以自動完成對外接口與內部存儲器之間的數據傳輸。這里的內部存儲器包括了其中兩個VE的內存空間和VE之間共享的一塊專門的數據存儲空間。這個專門的數據通路的設計,為基帶數據的輸入和輸出提供了足夠的帶寬資源。

L23子系統與PHY子系統之間也通過專有的網絡互聯。且有一塊特定的共享內存掛在這個網絡上,L23 子系統的內核與DMA、PHY子系統的VE和DMA也都可以對此共享內存進行訪問。這個特定的網絡通路和共享內存區域為L23子系統與PHY子系統之間進行大量數據傳輸提供了足夠的帶寬資源。

圖7:基于SL3000構建多模終端參考方案

圖7表達了基于SL3000的架構,可構成多模終端的方案。RFIF接口可連接一顆多頻段多帶寬可配置的射頻芯片。語音可以走I2S接口與外部的語音處理芯片構成的通路,數據既可以走USB 接口也可以走GMAC接口。L23子系統有足夠的能力運行多模的協議棧,PHY 子系統也有足夠的能力運行多模的物理層軟件。除了在上行和下行鏈路的局部直連總線外,沒有復雜的多核互連網絡。這樣搭建的是一個簡潔的,低成本低功耗的多模終端方案。

5. 多模運行性能報告

這里給出TD-SCDMA和TD-LTE兩個系統在SL3000上運行的性能統計報告作為參考。由于整個鏈路處理的多個模塊分布在不同的VE 上,在此對具體模塊的分布方案不做詳細的介紹,只給出整個鏈路運算的實際測試得到的性能數據本身。

5.1 TD-LTE的性能數據

5.1.1 物理層鏈路處理的效率

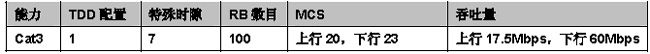

以上行峰值速率50Mbps,下行峰值速率100Mbps的處理為例,具體測試用例的參數如表2所示:

表2:測試用例參數

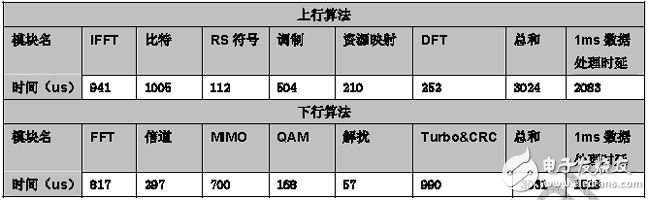

主頻330MHz時,各個算法模塊的每子幀數據處理所需的平均時間如表3所示:

表3:算法效率實測數據

TD- LTE整個上行1ms子幀的數據處理,需要92892cycles,即3024us@330MHz,整個下行鏈路處理花費1878110cycles,即 3031us@330MHz。由于所有的算法是分布在多個VE 上實現的,幾個算法是可以并行處理的,整體1ms處理時延上行是2.083ms@330MHz,下行只有1.52ms@330MHz。在上下行配置為 SA17條件下,每5ms有兩個上行子幀,三個下行子幀,上行吞吐量達到17.5Mbps,

下行吞吐量達到60Mbps,達到TD-LTE Cat3的上行峰值速率要求。

5.2 TD-SCDMA 的性能數據

對于TD-SCDMA系統的物理層,以上下行吞吐量分別為384kbps的處理為例,對其性能進行測試。具體測試用例的參數如表4所示:

表4:測試用例參數

主頻245MHz時,各個算法模塊的每子幀數據處理所需的平均時間如表5所示:

表5:算法效率實測數據

TD- SCDMA整個10ms幀的時間內,在上下行分別達到384kbps流量的條件下,整個上行鏈路處理花費207053cycles,即 864μs@245MHz,整個下行鏈路處理花費460376cycles,即1236us@245MHz。由于其中不同部分的算法分布在不同的VE上,實際上各個部分是可以并行運行的,真正一幀數據的時延上行小于864μs,下行小于1236μs的,用1/5的運算量就完全滿足實時性要求。

5.3 功耗與面積

目前的MPW樣片采用65nm工藝,未使用功耗控制。在主頻245MHz下,所有的內核與外設都全速運行,整顆芯片在峰值功耗在1.09W左右。 SL3000在65nm工藝流片,成品芯片的面積是79mm2。根據經驗,如采用40nm或以下的工藝和低功耗設計,物理層設計進一步優化,無論是功耗還是面積都會有較大的優化空間。預計面積在30mm2,功耗預計0.5W。

6. 小結

本文基于對 2G/3G/4G的需求分析,介紹了一顆終端基帶芯片SL3000的架構,以及基于SL3000 構建的多模終端參考方案,并提供了在此芯片上實現的多模系統的運行性能。從各項測試數據和驗證結果來看,SL3000是一顆具有多模功能,且滿足 2G/3G/4G性能需求的基帶平臺,能夠比較靈活地通過軟件編程而實現多種無線通信系統包括一些自定義的系統的終端。經過進一步的優化設計,其功耗和面積可以和同類多模ASIC芯片相當,但SL3000具有更大的編程靈活性,以適應其它信號處理、如雷達、測試儀表的需求。

電子發燒友App

電子發燒友App

評論