1 引言

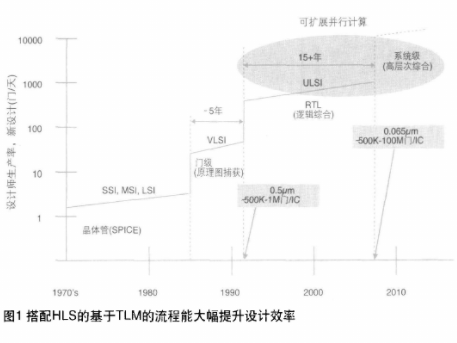

當(dāng)前集成電路制造技術(shù)迅速發(fā)展,SoC(system-on-chip)設(shè)計(jì)已經(jīng)成為集成電路設(shè)計(jì)的發(fā)展方向。隨著SoC 設(shè)計(jì)的復(fù)雜度提高,在開(kāi)發(fā)SoC 的過(guò)程中,驗(yàn)證工作越發(fā)重要和繁重,所占的開(kāi)銷占據(jù)總開(kāi)銷的40%“70%。SoC 設(shè)計(jì)的驗(yàn)證過(guò)程不但影響到芯片的成功設(shè)計(jì),而且影響到芯片的上市時(shí)間,因此驗(yàn)證的正確性及其耗時(shí)的縮短成為了SoC 設(shè)計(jì)的關(guān)鍵。

傳統(tǒng)設(shè)計(jì)中,系統(tǒng)級(jí)設(shè)計(jì)使用高級(jí)語(yǔ)言C/C++等描述功能模塊的算法,驗(yàn)證的時(shí)候使用硬件描述語(yǔ)言(VHDL 或Verilog HDL)。系統(tǒng)驗(yàn)證之前必須通過(guò)手工將原始的C/C++代碼轉(zhuǎn)換為VHDL/Verilog HDL 代碼,這個(gè)轉(zhuǎn)換過(guò)程耗時(shí)大并且容易產(chǎn)生錯(cuò)誤。在系統(tǒng)驗(yàn)證過(guò)程中,使用傳統(tǒng)硬件描述語(yǔ)言對(duì)復(fù)雜模塊的驗(yàn)證需要耗費(fèi)大量時(shí)間。

為了提高系統(tǒng)級(jí)驗(yàn)證效率,本文針對(duì)視頻芯片中的運(yùn)動(dòng)估計(jì)與補(bǔ)償單元模塊(MECU)提出了基于SystemC 的驗(yàn)證方法和流程。該方法大大縮短了系統(tǒng)驗(yàn)證的搭建時(shí)間和系統(tǒng)驗(yàn)證過(guò)程的時(shí)間。本文利用SystemC 支持設(shè)計(jì)者在不同抽象級(jí)建模的特點(diǎn),給MECU 添加了低抽象級(jí)接口,使該單元能夠和視頻芯片內(nèi)部其它模型通訊以便完成整個(gè)芯片的系統(tǒng)級(jí)驗(yàn)證。本文最后的仿真結(jié)果證明了該設(shè)計(jì)流程的有效性。

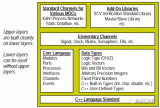

2 SystemC 語(yǔ)言

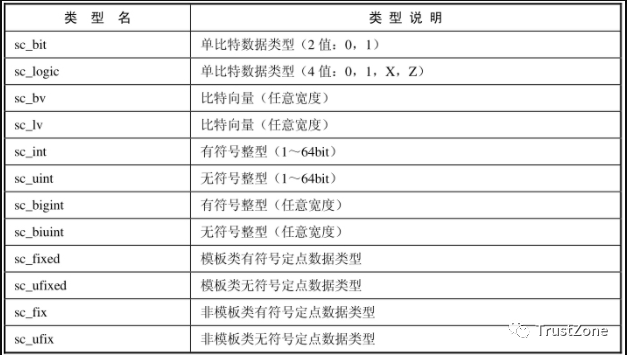

SystemC 是由C++衍生而來(lái),本質(zhì)是在C++的基礎(chǔ)上添加了硬件擴(kuò)展庫(kù)和仿真核,這使SystemC 可以在不同抽象級(jí)對(duì)復(fù)雜電子系統(tǒng)建模。它既可以描述純功能的模型和系統(tǒng)體系結(jié)構(gòu),又可以描述軟硬件的具體實(shí)現(xiàn),進(jìn)行軟硬件的協(xié)同驗(yàn)證。

SystemC 包括以下建模元素:

*模塊(module) 相當(dāng)于C++的類定義,是一個(gè)可以多層次的實(shí)體。一個(gè)模塊可以嵌套其他模塊和一些進(jìn)程,是SystemC 里面最基本的單元。

*進(jìn)程(process) 用來(lái)描述模塊的功能,包含于模塊中。進(jìn)程是由事件(event)來(lái)觸發(fā)的,這種觸發(fā)的方式使進(jìn)程可以并行執(zhí)行,實(shí)現(xiàn)了硬件系統(tǒng)的并行特性,SystemC 包括三種不同的進(jìn)程。

*接口(interface) 定義了一組方法實(shí)現(xiàn)目標(biāo),但是不實(shí)現(xiàn)這些方法。

*通道(channel) 實(shí)現(xiàn)了接口定義的方法,分為基本通道和層次化通道。

*端口(port) 總是與一定的接口類型相關(guān)聯(lián),端口只能連接到實(shí)現(xiàn)了該類接口的通道上,通過(guò)端口模塊和進(jìn)程來(lái)訪問(wèn)通道內(nèi)定義的接口方法。

*信號(hào)(signal) 用來(lái)實(shí)現(xiàn)各個(gè)進(jìn)程之間的通訊。SystemC 提供了多種信號(hào)格式來(lái)滿足從寄存器傳輸級(jí)(Register Transmit Level, RTL)到功能級(jí)等不同抽象級(jí)的模擬。

*事件(event) 用來(lái)觸發(fā)各個(gè)進(jìn)程的開(kāi)始以及暫停,通常多個(gè)事件組成一個(gè)敏感列表(sensitive list)共同決定進(jìn)程的狀態(tài)。

*時(shí)鐘信號(hào)(clock) 時(shí)鐘在同步電路設(shè)計(jì)中是一個(gè)非常重要的角色,本質(zhì)上它是一種特殊的信號(hào),為仿真過(guò)程提供了時(shí)間基準(zhǔn)。

上述建模元素使得SystemC 能夠順利的搭建硬件平臺(tái)。

3 基于SystemC 的建模方法

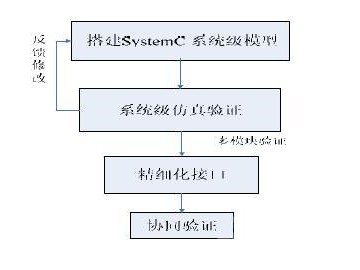

系統(tǒng)級(jí)驗(yàn)證過(guò)程中,對(duì)于復(fù)雜算法模型只需要建立參考模型(Reference Models),搭建驗(yàn)證平臺(tái),觀察模型的一些重要功能(算法、進(jìn)程等等),不需要了解RTL 層面的細(xì)節(jié)。利用事務(wù)級(jí)建模方法(TLM, Transaction Level Modeling)技術(shù)很容易建立參考模型。一個(gè)完整的芯片是由多個(gè)功能模塊組成,采用SystemC 對(duì)復(fù)雜算法單元建立模型能使功能驗(yàn)證時(shí)間縮短,而一些簡(jiǎn)單模型的驗(yàn)證需要在RTL 層面。為了實(shí)現(xiàn)不同抽象級(jí)模塊通訊,本文對(duì)使用SystemC 建立的復(fù)雜單元模型進(jìn)行接口精細(xì)化處理。本文對(duì)實(shí)際芯片單元提出的SystemC 建模驗(yàn)證流程。

驗(yàn)證流程描述:

(1)搭建SystemC 系統(tǒng)級(jí)模型:

使用基于C++的SystemC 能很容易搭建系統(tǒng)級(jí)模型。利用SystemC 對(duì)所要實(shí)現(xiàn)的系統(tǒng)功能進(jìn)行描述,主要描述系統(tǒng)的算法、結(jié)構(gòu)等,不考慮每個(gè)時(shí)鐘周期寄存器數(shù)值改變。只有針對(duì)復(fù)雜算法單元使用SystemC 建模,才能夠發(fā)揮SystemC 節(jié)省建模和驗(yàn)證時(shí)間的優(yōu)勢(shì)。

(2)系統(tǒng)級(jí)功能仿真:

利用支持SystemC 的工具對(duì)建立的模型進(jìn)行仿真驗(yàn)證系統(tǒng)功能,觀察結(jié)果并且不斷進(jìn)行反饋修改直到仿真正確。

(3)精細(xì)化接口:

精細(xì)化接口是多模塊驗(yàn)證過(guò)程的關(guān)鍵。因?yàn)樵趯?duì)單個(gè)復(fù)雜單元系統(tǒng)級(jí)驗(yàn)證的時(shí)候,抽象級(jí)很高,只需要考慮其功能性。多個(gè)模塊驗(yàn)證時(shí)外部單元模型可能在RTL 級(jí)別構(gòu)建,這時(shí)需要利用SystemC 能在不同抽象級(jí)建模的優(yōu)勢(shì),在一個(gè)較大的模塊中實(shí)現(xiàn)不同的抽象層建模,即在和外部模型接口處將抽象級(jí)降低到RTL 級(jí)。精細(xì)化接口的過(guò)程需要根據(jù)外部模塊接口調(diào)節(jié)輸入輸出數(shù)據(jù)位寬、設(shè)置敏感事件列表,并且嚴(yán)格按照外部時(shí)鐘控制數(shù)據(jù)的傳輸,保證順利和外部模塊通訊。

(4)協(xié)同驗(yàn)證:

驗(yàn)證多個(gè)模塊共同工作的正確性,這時(shí)候發(fā)現(xiàn)錯(cuò)誤就能夠及時(shí)進(jìn)行設(shè)計(jì)的修改,提高芯片設(shè)計(jì)效率。驗(yàn)證結(jié)果正確的模塊就可以進(jìn)行后端流程,建立的驗(yàn)證平臺(tái)也可以作為外部驅(qū)動(dòng)的測(cè)試平臺(tái)進(jìn)行軟件的驗(yàn)證。

4 應(yīng)用實(shí)例

4.1 MECU 原理

廣泛應(yīng)用在手機(jī)中的視頻編解碼芯片編解碼流程包括了DCT 變換、量化、VLC 編碼、反DCT 變換,反量化、運(yùn)動(dòng)估計(jì)、運(yùn)動(dòng)補(bǔ)償、插值計(jì)算、邊緣填充等步驟,其中運(yùn)動(dòng)估計(jì)與補(bǔ)償部分是實(shí)現(xiàn)壓縮圖像時(shí)間冗余度的重要環(huán)節(jié),由于其算法的復(fù)雜性該部分占據(jù)了大部分的編解碼時(shí)間, 對(duì)MECU 模塊的驗(yàn)證是整個(gè)芯片驗(yàn)證中工作量最大的環(huán)節(jié)。

本文中MECU采用MVFast(Motion Vector Field Adaptive Fast Motion Estimation) 算法實(shí)現(xiàn)ME/MC:ME 部分在圖像編碼過(guò)程中實(shí)現(xiàn)運(yùn)動(dòng)預(yù)測(cè),計(jì)算出運(yùn)動(dòng)矢量,同時(shí)完成宏塊編碼類型(MBmode)判斷和運(yùn)動(dòng)矢量編碼類型判斷;MC 部分在圖像編碼過(guò)程中,根據(jù)輸入各塊的運(yùn)動(dòng)矢量完成YUV 的插值處理輸出運(yùn)動(dòng)參考?jí)K數(shù)據(jù)和當(dāng)前處理塊數(shù)據(jù);在圖像解碼處理中完成插值處理輸出參考?jí)K數(shù)據(jù)。

4.2 模塊搭建

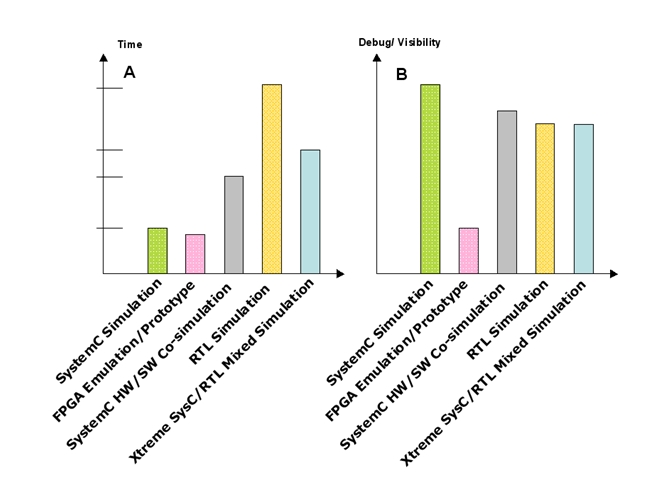

采用Verilog 語(yǔ)言直接建立MECU 模型用于芯片設(shè)計(jì)時(shí),由于MECU 算法復(fù)雜,建模過(guò)程耗時(shí)巨大。Verilog 建模期間系統(tǒng)驗(yàn)證工程師需要等待模型建立完成,這樣增長(zhǎng)了芯片設(shè)計(jì)周期,另一方面對(duì)使用Verilog 建立的MECU 模型驗(yàn)證耗費(fèi)時(shí)間長(zhǎng)。由于基于SystemC的建模時(shí)間相對(duì)Verilog 建模時(shí)間縮短3~4 倍,驗(yàn)證過(guò)程具有快速性優(yōu)勢(shì),本文嘗試采用SystemC 進(jìn)行前期建模和驗(yàn)證工作。

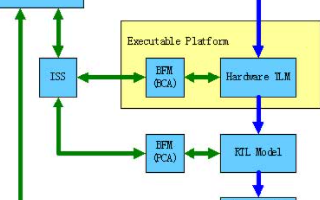

依據(jù)本文第二部分介紹的驗(yàn)證方法,首先建立MECU 硬件仿真模型進(jìn)行功能驗(yàn)證,然后在這個(gè)硬件模型正確的基礎(chǔ)上進(jìn)行外圍模塊設(shè)計(jì)的驗(yàn)證,以實(shí)現(xiàn)整個(gè)芯片的系統(tǒng)級(jí)驗(yàn)證。

第一步利用SystemC 對(duì)ME 和MC 分別進(jìn)行系統(tǒng)級(jí)建模。在建立ME 和MC 這兩個(gè)模塊時(shí),只需要實(shí)現(xiàn)ME 和MC 各自算法功能和兩個(gè)模塊之間的通訊,因此不需要按照精確的時(shí)序建模。在C 語(yǔ)言實(shí)現(xiàn)MVFAST 算法模型基礎(chǔ)上,用SC_MODULE 將ME 和MC 各自編寫成可仿真的模塊MEU 和MCU,內(nèi)部的功能利用Process 來(lái)實(shí)現(xiàn)。模型建立之后,搭建平臺(tái)進(jìn)行功能驗(yàn)證,觀察數(shù)據(jù)經(jīng)過(guò)ME 和MC 之后的變化是否完全符合算法要求。

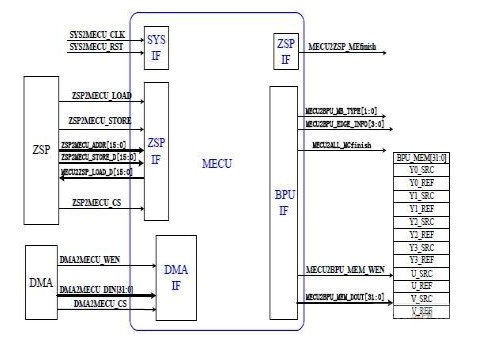

MEU 和MCU 模型功能驗(yàn)證結(jié)束之后需要協(xié)同芯片中其它模塊進(jìn)行驗(yàn)證,由于MECU的外圍模塊是在RTL 級(jí)建模,并且嚴(yán)格按照時(shí)鐘進(jìn)行數(shù)據(jù)處理,因此必須對(duì)MECU 接口進(jìn)行精細(xì)化。本實(shí)驗(yàn)添加了SYS_IF ,ZSP-IF, DMA-IF 和BPU-IF 模塊以實(shí)現(xiàn)與外圍模塊通訊,這些接口模塊包括和外圍模塊相匹配的輸入輸出端口,并且由時(shí)鐘嚴(yán)格控制數(shù)據(jù)的傳輸。

4.3 接口模塊描述

(1)SYS_IF 提供MECU 的外部時(shí)鐘以及復(fù)位信號(hào)接口,這兩個(gè)控制信號(hào)對(duì)MECU 內(nèi)部所有模塊有效。

(2)MEU 和MCU 的觸發(fā)由外部ZSP 產(chǎn)生的開(kāi)始信號(hào)來(lái)控制,在MECU 內(nèi)部包含的控制寄存器也由ZSP 來(lái)控制。ZSP_IF 模塊的添加實(shí)現(xiàn)了ZSP 對(duì)MECU 進(jìn)行讀寫控制。

(3)MECU 模型編解碼過(guò)程需要處理的數(shù)據(jù)是通過(guò)ZSP 控制DMA 提供,因此添加DMA_IF模塊實(shí)現(xiàn)和DMA 通訊,搬運(yùn)數(shù)據(jù)以供MECU 處理。

(4)最終MC 完成產(chǎn)生的數(shù)據(jù),通過(guò)BPU_IF 模塊傳輸出到BPU 中(用于軟硬件結(jié)果對(duì)比)。

從上述結(jié)構(gòu)可以看出,MECU 包括了六個(gè)模塊:ME,MC,SYS_IF,ZSP_IF, DMA_IF 以及BPU_IF。ME 和MC 作為核心功能模塊實(shí)現(xiàn)了MECU 單元的算法,SYS_IF,ZSP_IF, DMA_IF以及BPU_IF 四個(gè)接口模塊由時(shí)鐘嚴(yán)格控制數(shù)據(jù)的傳輸,實(shí)現(xiàn)和外圍模塊通訊功能。

5 仿真結(jié)果分析

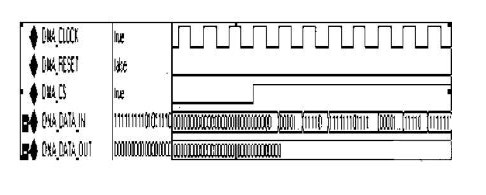

利用上述SystemC 模型進(jìn)行仿真驗(yàn)證,采用一組352*288 像素的圖像作為仿真對(duì)象,使用Mentor 公司的Modelsim 作為仿真工具。首先建立測(cè)試平臺(tái),對(duì)外部ZSP,DMA 進(jìn)行模擬以提供控制信號(hào)和處理數(shù)據(jù),然后利用Modelsim 進(jìn)行仿真驗(yàn)證和時(shí)序分析。

?

仿真得到的數(shù)據(jù)結(jié)果完全符合算法的期望值,證明了搭建模型的正確性。時(shí)序分析結(jié)果表明:使用SystemC 對(duì)圖像的一個(gè)宏塊(16*16 像素)進(jìn)行編碼平均需要680 個(gè)clock cycle,其中ME 和MC 部分占用11 個(gè)clock cycle;用傳統(tǒng)硬件描述語(yǔ)言Verilog 建模進(jìn)行驗(yàn)證一個(gè)模塊的編碼平均需要3000 個(gè)clock cycle,其中ME 和MC 占據(jù)2200 個(gè)clock cycle。將基于SystemC 和Verilog 兩種建模方法的ME 和MC 驗(yàn)證時(shí)間相比較發(fā)現(xiàn):采用SystemC 進(jìn)行純功能性驗(yàn)證時(shí)間比使用Verilog 驗(yàn)證時(shí)間縮短了約200 倍,因此驗(yàn)證時(shí)間上的優(yōu)勢(shì)是顯著的。

6 總結(jié)

本文對(duì) SystemC 驗(yàn)證方法進(jìn)行了深入的研究,針對(duì)視頻編解碼芯片MECU 單元的驗(yàn)證提出了使用SystemC 驗(yàn)證的建模流程,通過(guò)端口細(xì)化方法使芯片能在不同抽象級(jí)建模驗(yàn)證,這種方法在當(dāng)前國(guó)內(nèi)驗(yàn)證方面使用不多。仿真結(jié)果證明了該流程的有效性,和使用傳統(tǒng)硬件描述語(yǔ)言驗(yàn)證相比時(shí)間顯著縮短。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論