1.如何實現高速時鐘信號的差分布線? 在高速設計中,如何解決信號的完整性問題?差分布線方式是如何實現的?對于只有一個輸出端的時鐘信號線,如何實現差分布線?

專家解答:

信號完整性基本上是阻抗匹配的問題。而影響阻抗匹配的因素有信號源的架構和輸出阻抗(output impedance),走線的特性阻抗,負載端的特性,走線的拓樸(topology)架構等。解決的方式是靠端接(termination)與調整走線的拓樸。

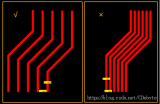

差分對的布線有兩點要注意,一是兩條線的長度要盡量一樣長,另一是兩線的間距(此間距由差分阻抗決定)要一直保持不變,也就是要保持平行。平行的方式有兩種,一為兩條線走在同一走線層(side-by-side),一為兩條線走在上下相鄰兩層(over-under)。一般以前者side-by-side實現的方式較多。

要用差分布線一定是信號源和接收端也都是差分信號才有意義。所以對只有一個輸出端的時鐘信號是無法使用差分布線的

2.關于高速差分信號布線.在pcb上靠近平行走高速差分信號線對的時候,在阻抗匹配的情況下,由于兩線的相互耦合,會帶來很多好處。但是有觀點認為這樣會增大信號的衰減,影響傳輸距離。是不是這樣,為什么?我在一些大公司的評估板上看到高速布線有的盡量靠近且平行,而有的卻有意的使兩線距離忽遠忽近,我不懂那一種效果更好。我的信號1GHz以上,阻抗為50歐姆。

在用軟件計算時,差分線對也是以50歐姆來計算嗎?還是以100歐姆來算?接收端差分線對之間可否加一匹配電阻?謝謝!

專家解答:

會使高頻信號能量衰減的原因一是導體本身的電阻特性(conductor loss), 包括集膚效應(skin effect), 另一是介電物質的dielectric loss。 這兩種因子在電磁理論分析傳輸線效應(transmission line effect)時, 可看出他們對信號衰減的影響程度。 差分線的耦合是會影響各自的特性阻抗, 變的較小, 根據分壓原理(voltage divider)這會使信號源送到線上的電壓小一點。 至于, 因耦合而使信號衰減的理論分析我并沒有看過, 所以我無法評論。

對差分對的布線方式應該要適當的靠近且平行。 所謂適當的靠近是因為這間距會影響到差分阻抗(differential impedance)的值, 此值是設計差分對的重要參數。 需要平行也是因為要保持差分阻抗的一致性。 若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal

integrity)及時間延遲(timing delay)。

差分阻抗的計算是 2(Z11 - Z12), 其中, Z11是走線本身的特性阻抗, Z12是兩條差分線間因為耦合而產生的阻抗, 與線距有關。 所以, 要設計差分阻抗為100歐姆時, 走線本身的特性阻抗一定要稍大于50歐姆。 至于要大多少, 可用仿真軟件算出來。

接收端差分線對間的匹配電阻通常會加, 其值應等于差分阻抗的值。 這樣信號品質會好些。歡迎到www.mentor.com/icx里面有一些不錯的技術資料。

3. 如何處理實際布線中的一些理論沖突的問題.在實際布線中,很多理論是相互沖突的;例如:

1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者絕對的隔離會導致小信號模擬地走線過長,很難實現理論的接法。我的做法是:將模/數功能模塊的地分割成一個完整的孤島,該功能模塊的模/數地都連接在這一個孤島上。再通過溝道讓孤島和“大”地連接。不知這種做法是否正確?

2。理論上晶振與CPU的連線應該盡量短,由于結構布局的原因,晶振與CPU的連線比較長、比較細,因此受到了干擾,工作不穩定,這時如何從布線解決這個問題?諸如此類的問題還有很多,尤其是高速PCB布線中考慮EMC、EMI問題,有很多沖突,很是頭痛,請問如何解決這些沖突?多謝!

專家解答:

A 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑(returning current path)變太大。

B 晶振是模擬的正反饋振蕩電路, 要有穩定的振蕩信號, 必須滿足loop gain與phase的規范, 而這模擬信號的振蕩規范很容易受到干擾, 即使加ground guard traces可能也無法完全隔離干擾。 而且離的太遠, 地平面上的噪聲也會影響正反饋振蕩電路。 所以, 一定要將晶振和芯片的

距離進可能靠近。

C 確實高速布線與EMI的要求有很多沖突。 但基本原則是因EMI所加的電阻電容或ferrite bead, 不能造成信號的一些電氣特性不符合規范。 所以, 最好先用安排走線和PCB疊層的技巧來解決或減少EMI的問題, 如高速信號走內層。 最后才用電阻電容或ferrite bead的方式, 以降低對信號的傷害。

4.模數部分關于抗干擾的問題.一些系統中經常有A/D,問:要提高抗干擾性,除了模擬地和數字地分開只在電源一點連接,加粗地線和電源線外,希望專家給一些好的意見和建議!

專家解答:

除了地要分開隔離外, 也要注意模擬電路部分的電源, 如果跟數字電路共享電源, 最好要加濾波線路。 另外, 數字信號和模擬信號不要有交錯, 尤其不要跨過分割地的地方(moat)。

5.高速信號的自動布線.為了最大限度的保證高速信號質量,我們都習慣于手工布線,但效率太低。使用自動布線器又無法監控關鍵信號的繞線方式,過孔數目、位置等。手工走完關鍵信號再自動布線又會降低自動布線的布通率,而且自動布線結果的調整意味著更多的布線工作量,如何平衡以上矛盾,利用優秀的布線器幫助完成高速信號的布線?

專家解答:

現在較強的布線軟件的自動布線器大部分都有設定約束條件來控制繞線方式及過孔數目。 各家EDA公司的繞線引擎能力和約束條件的設定項目有時相差甚遠。 例如, 是否有足夠的約束條件控制蛇行線(serpentine)蜿蜒的方式, 能否控制差分對的走線間距等。 這會影響到自動布線出來的走線方式是否能符合設計者的想法。 另外, 手動調整布線的難易也與繞線引擎的能力有絕對的關系。 例如, 走線的推擠能力, 過孔的推擠能力, 甚至走線對敷銅的推擠能力等等。 所以, 選擇一個繞線引擎能力強的布線器, 才是解決之道。

如果您對蔽公司Expedition有興趣試看看我們的繞線引擎, 請電21-64159380, 會有專人為您服務。

6關于test coupon.test coupon的設計有什么規范可以參照嗎?如何根據板子的實際情況設計test coupon?有什么需要注意的問題?謝謝!

專家解答:

test coupon是用來以TDR (Time Domain Reflectometer) 測量所生產的PCB板的特性阻抗是否滿足設計需求。 一般要控制的阻抗有單根線和差分對兩種情況。 所以, test coupon上的走線線寬和線距(有差分對時)要與所要控制的線一樣。 最重要的是測量時接地點的位置。 為了減少接地引線(ground lead)的電感值, TDR探棒(probe)接地的地方通常非常接近量信號的地方(probe tip), 所以, test coupon上量測信號的點跟接地點的距離和方式要符合所用的探棒。 以下提供兩篇文章參考:

1. http://developer.intel.com/design/chipsets/applnots/pcd_pres399.pdf

2. http://www.Polarinstruments.com/index.html (點選Application notes)

7.關于高速PCB設計中信號層空白區域敷銅接地問題.在高速PCB設計中,信號層的空白區域可以敷銅,那么多個信號層的敷銅是都接地好呢,還是一半接地,一半接電源好呢?

專家解答:

一般在空白區域的敷銅絕大部分情況是接地。 只是在高速信號線旁敷銅時要注意敷銅與信號線的距離, 因為所敷的銅會降低一點走線的特性阻抗。 也要注意不要影響到它層的特性阻抗, 例如在dual stripline的結構時。

8. 特性阻抗.感謝您回答我上次的問題。上回您說電源平面和地平面基本上都是金屬平面,所以對電場磁場都有屏蔽效應,那我可以把電源平面上面的信號線使用微帶線模型計算特性阻抗嗎?電源和地平面之間的信號可以使用帶狀線模型計算嗎?

專家解答:

是的, 在計算特性阻抗時電源平面跟地平面都必須視為參考平面。 例如四層板: 頂層-電源層-地層-底層, 這時頂層走線特性阻抗的模型是以電源平面為參考平面的微帶線模型。

9.高速信號線的匹配問題.在高速板(如p4的主板)layour,為什么要求高速信號線(如cpu數據,地址信號線)要匹配? 如果不匹配會帶來什么隱患?其匹配的長度范圍(既信號線的時滯差)是由什么因素決定的,怎樣計算?

專家解答:

要求走線特性阻抗匹配的主要原因是要避免高速傳輸線效應(transmission line effect)所引起的反射(reflection)影響到信號完整性(signal integrity)和延遲時間(flight time)。也就是說如果不匹配,則信號會被反射影響其質量。

所有走線的長度范圍都是根據時序(timing)的要求所訂出來的。影響信號延遲時間的因素很多,走線長度只是其一。P4要求某些信號線長度要在某個范圍就是根據該信號所用的傳輸模式(common clock或source synchronous)下算得的timing margin,分配一部份給走線長度的允

許誤差。 至于, 上述兩種模式時序的計算, 限于時間與篇幅不方便在此詳述, 請到下列網址

http://developer.intel.com/design/Pentium4/guides 下載"Intel Pentium 4 Processor in the 423-pin Package/Intel 850 Chipset Platform Design Guide"。 其中 "Methodology for Determining Topology and Routing Guideline"章節內有詳述。

10.測試點生成.在高密度印制板上通過軟件自動產生測試點一般情況下能滿足大批量生產的測試要求嗎?添加測試點會不會影響高速信號的質量?

專家解答:

一般軟件自動產生測試點是否滿足測試需求必須看對加測試點的規范是否符合測試機具的要求。另外,如果走線太密且加測試點的規范比較嚴,則有可能沒辦法自動對每段線都加上測試點,當然,需要手動補齊所要測試的地方。

至于會不會影響信號質量就要看加測試點的方式和信號到底多快而定。基本上外加的測試點(不用線上既有的穿孔(via or DIP pin)當測試點)可能加在線上或是從線上拉一小段線出來。前者相當于是加上一個很小的電容在線上,后者則是多了一段分支。這兩個情況都會對高速信號多多少少會有點影響,影響的程度就跟信號的頻率速度和信號緣變化率(edge rate)有關。影響大小可透過仿真得知。原則上測試點越小越好(當然還要滿足測試機具的要求)分支越短越好。

11.如何選擇PCB板材?如何選擇PCB板材?如何避免高速數據傳輸對周圍模擬小信號的高頻干擾,有沒有一些設計的基本思路?

專家解答:

選擇PCB板材必須在滿足設計需求和可量產性及成本中間取得平衡點。設計需求包含電氣和機構這兩部分。通常在設計非常高速的PCB板子(大于GHz的頻率)時這材質問題會比較重要。例如,現在常用的FR-4材質,在幾個GHz的頻率時的介質損dielectric loss會對信號衰減有很大的影響,可能就不合用。就電氣而言,要注意介電常數(dielectric constant)和介質損在所設計的頻率是否合用。

避免高頻干擾的基本思路是盡量降低高頻信號電磁場的干擾,也就是所謂的串擾(Crosstalk)。可用拉大高速信號和模擬信號之間的距離,或加ground guard/shunt traces在模擬信號旁邊。還要注意數字地對模擬地的噪聲干擾。

12.PCB板各個層都代表什么意思.眾所周知PCB板包括很多層,但其中某些層的含義我還不是很清楚。mechanical,keepoutlayer,topoverlay,bottomoverlay, toppaste,bottompaste,topsolder,bottomsolder,drillguide,drilldrawing,multilayer這些層不知道它們的確切含義。希望您指教。

專家解答:

在EDA軟件的專門術語中,有很多不是有相同定義的。以下就字面上可能的意義來解釋。

Mechnical: 一般多指板型機械加工尺寸標注層

Keepoutlayer: 定義不能走線、打穿孔(via)或擺零件的區域。這幾個限制可以獨立分開定義。

Topoverlay: 無法從字面得知其意義。多提供些訊息來進一步討論。

Bottomoverlay: 無法從字面得知其意義。可多提供些訊息來進一步討論。

Toppaste: 頂層需要露出銅皮上錫膏的部分。

Bottompaste: 底層需要露出銅皮上錫膏的部分。

Topsolder: 應指頂層阻焊層,避免在制造過程中或將來維修時可能不小心的短路

Bottomsolder: 應指底層阻焊層。

Drillguide: 可能是不同孔徑大小,對應的符號,個數的一個表。

Drilldrawing: 指孔位圖,各個不同的孔徑會有一個對應的符號。

Multilayer: 應該沒有單獨這一層,能指多層板,針對單面板和雙面板而言。

13.地的連接問題.一個系統往往分成若干個PCB,有電源、接口、主板等,各板之間的地線往往各有互連,導致形成許許多多的環路,產生諸如低頻環路噪聲,不知這個問題如何解決?

專家解答:

各個PCB板子相互連接之間的信號或電源在動作時,例如A板子有電源或信號送到B板子,一定會有等量的電流從地層流回到A板子 (此為Kirchoff current law)。這地層上的電流會找阻抗最小的地方流回去。所以,在各個不管是電源或信號相互連接的接口處,分配給地層的管腳數不能太少,以降低阻抗,這樣可以降低地層上的噪聲。另外,也可以分析整個電流環路,尤其是電流較大的部分,調整地層或地線的接法,來控制電流的走法(例如,在某處制造低阻抗,讓大部分的電流從這個地方走),降低對其它較敏感信號的影響。

14.little problem .why the wien bridge can only be balanced at one frequency? even if the ratio of coupled resistors is varied

專家解答:

The operation principle of Wien bridge oscillator is positive feedback mechanism. The transfer function (or gain) of the Wien bridge oscillator (in

Laplace transform) is Af(s)=A(s)/[1-A(s)B(s)], which A(s) is open loop gain of amplifier and B(s) is the gain of feedback network. To oscillate spontaneously, the Af(s) must approach to infinity which implies denominator is zero. That is, the product of A(s) and B(s) need to be equal to 1. Due to the frequency dependence of A(s)B(s), there is only one frequency can make the denominator to be zero. That is why the Wien bridge only balance at one frequency. The oscillation frequency is determined by the resistors and capacitors in the positive feedback path, f=1/[2psqrt(R1C1R2C2)], where R1, C1, R2, C2 are the components in the positive feedback path. The components on negative feedback path are

nothing to do with the oscillation frequency. The other intuitive insight to this concept of balancing at one frequency is to treat the network of positive feedback path as a frequency selector. There are a high-pass filter formed by a series capacitor with a grounded resistor and a low-pass filter formed by a series resistor with a grounded capacitor. The total effect is similar to a bandpass filter. There is a website to address this concept: http://www.interq.or.jp/japan/se-

inoue/e_ckt18_2.htm#2.

?

15.如何估算特性阻抗。(1)能否提供一些經驗數據、公式和方法來估算布線的阻抗。(2)當無法滿足阻抗匹配的要求時,是在信號線的末端加并聯的匹配電阻好,還是在信號線上加串聯的匹配電阻好。(3)差分信號線中間可否加地線。

專家解答:

?

???????? 1.以下提供兩個常被參考的特性阻抗公式:

?????????? a.微帶線(microstrip)

??????????? Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)] 其中,W為線寬,T為走線的銅皮

厚度,H為走線到參考平面的距離,Er是PCB板材質的介電常數(dielectric constant)。此公式

必須在0.1<(W/H)<2.0及1<(Er)<15的情況才能應用。

??????????? b.帶狀線(stripline)

??????????? Z=[60/sqrt(Er)]ln{4H/[0.67p(T+0.8W)]} 其中,H為兩參考平面的距離,并且

走線位于兩參考平面的中間。此公式必須在W/H<0.35及T/H<0.25的情況才能應用。

????????? 最好還是用仿真軟件來計算比較準確。

???????? 2.選擇端接(termination)的方法有幾項因素要考慮:

????????? a.信號源(source driver)的架構和強度。

????????? b.功率消耗(power consumption)的大小。

????????? c.對時間延遲的影響,這是最重要考慮的一點。

???????? 所以,很難說哪一種端接方式是比較好的。

???????? 3.差分信號中間一般是不能加地線。因為差分信號的應用原理最重要的一點便是利用差分信號間相互耦合(coupling)所帶來的好處,如flux cancellation,抗噪聲(noise immunity)能力等。若在中間加地線,便會破壞耦合效應。

16.關于特性阻抗的計算.我覺得信號線特性阻抗的微帶線和帶狀線模型都是要參考地平面的,現在我想問一下,如果信號線下面的銅皮都被掏空,沒有參考的地平面,該如何計算頂層的信號線的特性阻抗?另外,我看一些資料寫在消除信號線上噪聲方面,電源平面也可以和地平面起相同的作用,是嗎?

專家解答:

沒有參考平面時電場與磁場的互動關系與有參考平面時不同,而這互動關系會影響到特性阻抗的值。現在絕大部分特性阻抗的計算公式都是假設有參考平面的, 我還沒看到這種無參考平面的特性阻抗公式。但是,可以用TDR (Time Domain Reflectometer)對實際的板子做量測來得到無參考平面的特性阻抗。

信號線上的噪聲產生的原因是別的線上的信號所產生的電場和磁場的能量經由mutual inductance及mutual capacitance而傳到被感染的信號線上。電源平面和地平面基本上都是金屬平面,所以對電場磁場都有屏蔽效應(shielding effect)。

17.關于高速PCB設計的技術書籍和資料.能介紹一些國外的目前關于高速PCB設計水平、加工能力、加工水平、加工材質以及相關的技術書籍和資料嗎?

專家解答:

現在高速數字電路的應用有通信網路和計算機等相關領域。在通信網路方面,PCB板的工作頻率已達GHz上下,迭層數就我所知有到40層之多。計算機相關應用也因為芯片的進步,無論是一般的PC或服務器(Server),板子上的最高工作頻率也已經達到400MHz (如Rambus) 以上。因應這高速高密度走線需求,盲埋孔(blind/buried vias)、mircrovias及build-up制程工藝的需求也漸漸越來越多。 這些設計需求都有廠商可大量生產。

以下提供幾本不錯的技術書籍:

?????? 1.Howard W. Johnson,“High-Speed Digital Design - A Handbook of Black Magic”;

?????? 2.Stephen H. Hall,“High-Speed Digital System Design”;

?????? 3.Brian Yang,“Digital Signal Integrity”;

18.有關柔性電路板的設計與加工.我公司打算采用柔性電路板設計來解決小型成像系統中信號傳送和電路板互接的問題。請問剛柔板設計是否需要專用設計軟件與規范?另外國內何處可以承接該類電路板加工?謝謝。

專家解答:

可以用一般設計PCB的軟件來設計柔性電路板(Flexible Printed Circuit)。一樣用Gerber格式給FPC廠商生產。由于制造的工藝和一般PCB不同,各個廠商會依據他們的制造能力會對最小線寬、最小線距、最小孔徑(via)有其限制。除此之外,可在柔性電路板的轉折處鋪些銅皮加以補強。至于生產的廠商可上網”FPC”當關鍵詞查詢應該可以找到。

19.PCB的布線調整.我想請問一個問題:因覺機器布的不如意,調整起來反而費時。我一般是用的手工布線,現在搞的PCB板多半要用引腳密度較大的貼片封裝芯片,而且帶總線的(ABUS,DBUS,CBUS等),因工作頻率較高,故引線要盡可能短.自然的就是很密的信號線勻布在小范圍面積的板子上。我現感覺到花的時間較多的是調整這些密度大的信號線, 一是調整線間的距離,使之盡可能的均勻。因為在布線的過程中,一般的都時不時的要改線。每改一次都要重新均勻每一根已布好的線的間距。越是布到最后,這種情況越是多。 二是調整線的寬度,使之在一定寬度中盡可能的容下新増加的線。一般一條線上有很多彎曲,一個彎就是一段,手工調整只能一段一段地調整,調整起來也費時間。 我想如果在布線的過程中,能按我的思路先粗粗地手工拉線,完了以后, 軟件能從這兩個方面幫我自動地調整。或是即便已布完,如要改線,也是粗粗地改一下,然后讓軟件調整。甚至,到最后我覺的需要調整元件的封裝,也就是說整片布線都需要調整,都讓軟件來干。那樣就要快多了.我用的是Protel98。我知道這軟件能做自動均勻調整元件封裝的距離而不能自動調整線距和線寬。可能是其中的一些功能我還不會用,或是有其他什么辦法,在此請教一下。

專家解答:

線寬和線距是影響走線密度其中兩個重要的因素。一般在設計工作頻率較高的板子時,布線之前需要先決定走線的特性阻抗。在PCB迭層固定的情況下,特性阻抗會決定出符合的線寬。而線距則和串擾(Crosstalk)大小有絕對的關系。最小可以接受的線距決定于串擾對信號時間延遲與信號完整性的影響是否能接受。這最小線距可由仿真軟件做預仿真(pre-simulation)得到。也就是說,在布線之前,需要的線寬與最小線距應該已經決定好了,并且不能隨意更動,因為會影響特性阻抗和串擾。這也是為什幺大部分的EDA布線軟件在做自動布線或調整時不會去動線寬和最小線距。

如果這線寬和最小線距已經設定好在布線軟件,則布線調整的方便與否就看軟件繞線引擎的能力強弱而定。如果您對蔽公司Expedition有興趣試看看我們的繞線引擎,請電21-64159380,會有專人為您服務。

1.如何實現高速時鐘信號的差分布線? 在高速設計中,如何解決信號的完整性問題?差分布線方式是如何實現的?對于只有一個輸出端的時鐘信號線,如何實現差分布線?

專家解答:

信號完整性基本上是阻抗匹配的問題。而影響阻抗匹配的因素有信號源的架構和輸出阻抗(output impedance),走線的特性阻抗,負載端的特性,走線的拓樸(topology)架構等。解決的方式是靠端接(termination)與調整走線的拓樸。

差分對的布線有兩點要注意,一是兩條線的長度要盡量一樣長,另一是兩線的間距(此間距由差分阻抗決定)要一直保持不變,也就是要保持平行。平行的方式有兩種,一為兩條線走在同一走線層(side-by-side),一為兩條線走在上下相鄰兩層(over-under)。一般以前者side-by-side實現的方式較多。

要用差分布線一定是信號源和接收端也都是差分信號才有意義。所以對只有一個輸出端的時鐘信號是無法使用差分布線的

2.關于高速差分信號布線.在pcb上靠近平行走高速差分信號線對的時候,在阻抗匹配的情況下,由于兩線的相互耦合,會帶來很多好處。但是有觀點認為這樣會增大信號的衰減,影響傳輸距離。是不是這樣,為什么?我在一些大公司的評估板上看到高速布線有的盡量靠近且平行,而有的卻有意的使兩線距離忽遠忽近,我不懂那一種效果更好。我的信號1GHz以上,阻抗為50歐姆。

在用軟件計算時,差分線對也是以50歐姆來計算嗎?還是以100歐姆來算?接收端差分線對之間可否加一匹配電阻?謝謝!

專家解答:

會使高頻信號能量衰減的原因一是導體本身的電阻特性(conductor loss), 包括集膚效應(skin effect), 另一是介電物質的dielectric loss。 這兩種因子在電磁理論分析傳輸線效應(transmission line effect)時, 可看出他們對信號衰減的影響程度。 差分線的耦合是會影響各自的特性阻抗, 變的較小, 根據分壓原理(voltage divider)這會使信號源送到線上的電壓小一點。 至于, 因耦合而使信號衰減的理論分析我并沒有看過, 所以我無法評論。

對差分對的布線方式應該要適當的靠近且平行。 所謂適當的靠近是因為這間距會影響到差分阻抗(differential impedance)的值, 此值是設計差分對的重要參數。 需要平行也是因為要保持差分阻抗的一致性。 若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal

integrity)及時間延遲(timing delay)。

差分阻抗的計算是 2(Z11 - Z12), 其中, Z11是走線本身的特性阻抗, Z12是兩條差分線間因為耦合而產生的阻抗, 與線距有關。 所以, 要設計差分阻抗為100歐姆時, 走線本身的特性阻抗一定要稍大于50歐姆。 至于要大多少, 可用仿真軟件算出來。

接收端差分線對間的匹配電阻通常會加, 其值應等于差分阻抗的值。 這樣信號品質會好些。歡迎到www.mentor.com/icx里面有一些不錯的技術資料。

3. 如何處理實際布線中的一些理論沖突的問題.在實際布線中,很多理論是相互沖突的;例如:

1。處理多個模/數地的接法:理論上是應該相互隔離的,但在實際的小型化、高密度布線中,由于空間的局限或者絕對的隔離會導致小信號模擬地走線過長,很難實現理論的接法。我的做法是:將模/數功能模塊的地分割成一個完整的孤島,該功能模塊的模/數地都連接在這一個孤島上。再通過溝道讓孤島和“大”地連接。不知這種做法是否正確?

2。理論上晶振與CPU的連線應該盡量短,由于結構布局的原因,晶振與CPU的連線比較長、比較細,因此受到了干擾,工作不穩定,這時如何從布線解決這個問題?諸如此類的問題還有很多,尤其是高速PCB布線中考慮EMC、EMI問題,有很多沖突,很是頭痛,請問如何解決這些沖突?多謝!

專家解答:

A 基本上, 將模/數地分割隔離是對的。 要注意的是信號走線盡量不要跨過有分割的地方(moat), 還有不要讓電源和信號的回流電流路徑(returning current path)變太大。

B 晶振是模擬的正反饋振蕩電路, 要有穩定的振蕩信號, 必須滿足loop gain與phase的規范, 而這模擬信號的振蕩規范很容易受到干擾, 即使加ground guard traces可能也無法完全隔離干擾。 而且離的太遠, 地平面上的噪聲也會影響正反饋振蕩電路。 所以, 一定要將晶振和芯片的

距離進可能靠近。

C 確實高速布線與EMI的要求有很多沖突。 但基本原則是因EMI所加的電阻電容或ferrite bead, 不能造成信號的一些電氣特性不符合規范。 所以, 最好先用安排走線和PCB疊層的技巧來解決或減少EMI的問題, 如高速信號走內層。 最后才用電阻電容或ferrite bead的方式, 以降低對信號的傷害。

4.模數部分關于抗干擾的問題.一些系統中經常有A/D,問:要提高抗干擾性,除了模擬地和數字地分開只在電源一點連接,加粗地線和電源線外,希望專家給一些好的意見和建議!

專家解答:

除了地要分開隔離外, 也要注意模擬電路部分的電源, 如果跟數字電路共享電源, 最好要加濾波線路。 另外, 數字信號和模擬信號不要有交錯, 尤其不要跨過分割地的地方(moat)。

5.高速信號的自動布線.為了最大限度的保證高速信號質量,我們都習慣于手工布線,但效率太低。使用自動布線器又無法監控關鍵信號的繞線方式,過孔數目、位置等。手工走完關鍵信號再自動布線又會降低自動布線的布通率,而且自動布線結果的調整意味著更多的布線工作量,如何平衡以上矛盾,利用優秀的布線器幫助完成高速信號的布線?

專家解答:

現在較強的布線軟件的自動布線器大部分都有設定約束條件來控制繞線方式及過孔數目。 各家EDA公司的繞線引擎能力和約束條件的設定項目有時相差甚遠。 例如, 是否有足夠的約束條件控制蛇行線(serpentine)蜿蜒的方式, 能否控制差分對的走線間距等。 這會影響到自動布線出來的走線方式是否能符合設計者的想法。 另外, 手動調整布線的難易也與繞線引擎的能力有絕對的關系。 例如, 走線的推擠能力, 過孔的推擠能力, 甚至走線對敷銅的推擠能力等等。 所以, 選擇一個繞線引擎能力強的布線器, 才是解決之道。

如果您對蔽公司Expedition有興趣試看看我們的繞線引擎, 請電21-64159380, 會有專人為您服務。

6關于test coupon.test coupon的設計有什么規范可以參照嗎?如何根據板子的實際情況設計test coupon?有什么需要注意的問題?謝謝!

專家解答:

test coupon是用來以TDR (Time Domain Reflectometer) 測量所生產的PCB板的特性阻抗是否滿足設計需求。 一般要控制的阻抗有單根線和差分對兩種情況。 所以, test coupon上的走線線寬和線距(有差分對時)要與所要控制的線一樣。 最重要的是測量時接地點的位置。 為了減少接地引線(ground lead)的電感值, TDR探棒(probe)接地的地方通常非常接近量信號的地方(probe tip), 所以, test coupon上量測信號的點跟接地點的距離和方式要符合所用的探棒。 以下提供兩篇文章參考:

1. http://developer.intel.com/design/chipsets/applnots/pcd_pres399.pdf

2. http://www.Polarinstruments.com/index.html (點選Application notes)

7.關于高速PCB設計中信號層空白區域敷銅接地問題.在高速PCB設計中,信號層的空白區域可以敷銅,那么多個信號層的敷銅是都接地好呢,還是一半接地,一半接電源好呢?

專家解答:

一般在空白區域的敷銅絕大部分情況是接地。 只是在高速信號線旁敷銅時要注意敷銅與信號線的距離, 因為所敷的銅會降低一點走線的特性阻抗。 也要注意不要影響到它層的特性阻抗, 例如在dual stripline的結構時。

8. 特性阻抗.感謝您回答我上次的問題。上回您說電源平面和地平面基本上都是金屬平面,所以對電場磁場都有屏蔽效應,那我可以把電源平面上面的信號線使用微帶線模型計算特性阻抗嗎?電源和地平面之間的信號可以使用帶狀線模型計算嗎?

專家解答:

是的, 在計算特性阻抗時電源平面跟地平面都必須視為參考平面。 例如四層板: 頂層-電源層-地層-底層, 這時頂層走線特性阻抗的模型是以電源平面為參考平面的微帶線模型。

9.高速信號線的匹配問題.在高速板(如p4的主板)layour,為什么要求高速信號線(如cpu數據,地址信號線)要匹配? 如果不匹配會帶來什么隱患?其匹配的長度范圍(既信號線的時滯差)是由什么因素決定的,怎樣計算?

專家解答:

要求走線特性阻抗匹配的主要原因是要避免高速傳輸線效應(transmission line effect)所引起的反射(reflection)影響到信號完整性(signal integrity)和延遲時間(flight time)。也就是說如果不匹配,則信號會被反射影響其質量。

所有走線的長度范圍都是根據時序(timing)的要求所訂出來的。影響信號延遲時間的因素很多,走線長度只是其一。P4要求某些信號線長度要在某個范圍就是根據該信號所用的傳輸模式(common clock或source synchronous)下算得的timing margin,分配一部份給走線長度的允

許誤差。 至于, 上述兩種模式時序的計算, 限于時間與篇幅不方便在此詳述, 請到下列網址

http://developer.intel.com/design/Pentium4/guides 下載"Intel Pentium 4 Processor in the 423-pin Package/Intel 850 Chipset Platform Design Guide"。 其中 "Methodology for Determining Topology and Routing Guideline"章節內有詳述。

10.測試點生成.在高密度印制板上通過軟件自動產生測試點一般情況下能滿足大批量生產的測試要求嗎?添加測試點會不會影響高速信號的質量?

專家解答:

一般軟件自動產生測試點是否滿足測試需求必須看對加測試點的規范是否符合測試機具的要求。另外,如果走線太密且加測試點的規范比較嚴,則有可能沒辦法自動對每段線都加上測試點,當然,需要手動補齊所要測試的地方。

至于會不會影響信號質量就要看加測試點的方式和信號到底多快而定。基本上外加的測試點(不用線上既有的穿孔(via or DIP pin)當測試點)可能加在線上或是從線上拉一小段線出來。前者相當于是加上一個很小的電容在線上,后者則是多了一段分支。這兩個情況都會對高速信號多多少少會有點影響,影響的程度就跟信號的頻率速度和信號緣變化率(edge rate)有關。影響大小可透過仿真得知。原則上測試點越小越好(當然還要滿足測試機具的要求)分支越短越好。

11.如何選擇PCB板材?如何選擇PCB板材?如何避免高速數據傳輸對周圍模擬小信號的高頻干擾,有沒有一些設計的基本思路?

專家解答:

選擇PCB板材必須在滿足設計需求和可量產性及成本中間取得平衡點。設計需求包含電氣和機構這兩部分。通常在設計非常高速的PCB板子(大于GHz的頻率)時這材質問題會比較重要。例如,現在常用的FR-4材質,在幾個GHz的頻率時的介質損dielectric loss會對信號衰減有很大的影響,可能就不合用。就電氣而言,要注意介電常數(dielectric constant)和介質損在所設計的頻率是否合用。

避免高頻干擾的基本思路是盡量降低高頻信號電磁場的干擾,也就是所謂的串擾(Crosstalk)。可用拉大高速信號和模擬信號之間的距離,或加ground guard/shunt traces在模擬信號旁邊。還要注意數字地對模擬地的噪聲干擾。

12.PCB板各個層都代表什么意思.眾所周知PCB板包括很多層,但其中某些層的含義我還不是很清楚。mechanical,keepoutlayer,topoverlay,bottomoverlay, toppaste,bottompaste,topsolder,bottomsolder,drillguide,drilldrawing,multilayer這些層不知道它們的確切含義。希望您指教。

專家解答:

在EDA軟件的專門術語中,有很多不是有相同定義的。以下就字面上可能的意義來解釋。

Mechnical: 一般多指板型機械加工尺寸標注層

Keepoutlayer: 定義不能走線、打穿孔(via)或擺零件的區域。這幾個限制可以獨立分開定義。

Topoverlay: 無法從字面得知其意義。多提供些訊息來進一步討論。

Bottomoverlay: 無法從字面得知其意義。可多提供些訊息來進一步討論。

Toppaste: 頂層需要露出銅皮上錫膏的部分。

Bottompaste: 底層需要露出銅皮上錫膏的部分。

Topsolder: 應指頂層阻焊層,避免在制造過程中或將來維修時可能不小心的短路

Bottomsolder: 應指底層阻焊層。

Drillguide: 可能是不同孔徑大小,對應的符號,個數的一個表。

Drilldrawing: 指孔位圖,各個不同的孔徑會有一個對應的符號。

Multilayer: 應該沒有單獨這一層,能指多層板,針對單面板和雙面板而言。

13.地的連接問題.一個系統往往分成若干個PCB,有電源、接口、主板等,各板之間的地線往往各有互連,導致形成許許多多的環路,產生諸如低頻環路噪聲,不知這個問題如何解決?

專家解答:

各個PCB板子相互連接之間的信號或電源在動作時,例如A板子有電源或信號送到B板子,一定會有等量的電流從地層流回到A板子 (此為Kirchoff current law)。這地層上的電流會找阻抗最小的地方流回去。所以,在各個不管是電源或信號相互連接的接口處,分配給地層的管腳數不能太少,以降低阻抗,這樣可以降低地層上的噪聲。另外,也可以分析整個電流環路,尤其是電流較大的部分,調整地層或地線的接法,來控制電流的走法(例如,在某處制造低阻抗,讓大部分的電流從這個地方走),降低對其它較敏感信號的影響。

14.little problem .why the wien bridge can only be balanced at one frequency? even if the ratio of coupled resistors is varied

專家解答:

The operation principle of Wien bridge oscillator is positive feedback mechanism. The transfer function (or gain) of the Wien bridge oscillator (in

Laplace transform) is Af(s)=A(s)/[1-A(s)B(s)], which A(s) is open loop gain of amplifier and B(s) is the gain of feedback network. To oscillate spontaneously, the Af(s) must approach to infinity which implies denominator is zero. That is, the product of A(s) and B(s) need to be equal to 1. Due to the frequency dependence of A(s)B(s), there is only one frequency can make the denominator to be zero. That is why the Wien bridge only balance at one frequency. The oscillation frequency is determined by the resistors and capacitors in the positive feedback path, f=1/[2psqrt(R1C1R2C2)], where R1, C1, R2, C2 are the components in the positive feedback path. The components on negative feedback path are

nothing to do with the oscillation frequency. The other intuitive insight to this concept of balancing at one frequency is to treat the network of positive feedback path as a frequency selector. There are a high-pass filter formed by a series capacitor with a grounded resistor and a low-pass filter formed by a series resistor with a grounded capacitor. The total effect is similar to a bandpass filter. There is a website to address this concept: http://www.interq.or.jp/japan/se-

inoue/e_ckt18_2.htm#2.

?

15.如何估算特性阻抗。(1)能否提供一些經驗數據、公式和方法來估算布線的阻抗。(2)當無法滿足阻抗匹配的要求時,是在信號線的末端加并聯的匹配電阻好,還是在信號線上加串聯的匹配電阻好。(3)差分信號線中間可否加地線。

專家解答:

?

???????? 1.以下提供兩個常被參考的特性阻抗公式:

?????????? a.微帶線(microstrip)

??????????? Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)] 其中,W為線寬,T為走線的銅皮

厚度,H為走線到參考平面的距離,Er是PCB板材質的介電常數(dielectric constant)。此公式

必須在0.1<(W/H)<2.0及1<(Er)<15的情況才能應用。

??????????? b.帶狀線(stripline)

??????????? Z=[60/sqrt(Er)]ln{4H/[0.67p(T+0.8W)]} 其中,H為兩參考平面的距離,并且

走線位于兩參考平面的中間。此公式必須在W/H<0.35及T/H<0.25的情況才能應用。

????????? 最好還是用仿真軟件來計算比較準確。

???????? 2.選擇端接(termination)的方法有幾項因素要考慮:

????????? a.信號源(source driver)的架構和強度。

????????? b.功率消耗(power consumption)的大小。

????????? c.對時間延遲的影響,這是最重要考慮的一點。

???????? 所以,很難說哪一種端接方式是比較好的。

???????? 3.差分信號中間一般是不能加地線。因為差分信號的應用原理最重要的一點便是利用差分信號間相互耦合(coupling)所帶來的好處,如flux cancellation,抗噪聲(noise immunity)能力等。若在中間加地線,便會破壞耦合效應。

16.關于特性阻抗的計算.我覺得信號線特性阻抗的微帶線和帶狀線模型都是要參考地平面的,現在我想問一下,如果信號線下面的銅皮都被掏空,沒有參考的地平面,該如何計算頂層的信號線的特性阻抗?另外,我看一些資料寫在消除信號線上噪聲方面,電源平面也可以和地平面起相同的作用,是嗎?

專家解答:

沒有參考平面時電場與磁場的互動關系與有參考平面時不同,而這互動關系會影響到特性阻抗的值。現在絕大部分特性阻抗的計算公式都是假設有參考平面的, 我還沒看到這種無參考平面的特性阻抗公式。但是,可以用TDR (Time Domain Reflectometer)對實際的板子做量測來得到無參考平面的特性阻抗。

信號線上的噪聲產生的原因是別的線上的信號所產生的電場和磁場的能量經由mutual inductance及mutual capacitance而傳到被感染的信號線上。電源平面和地平面基本上都是金屬平面,所以對電場磁場都有屏蔽效應(shielding effect)。

17.關于高速PCB設計的技術書籍和資料.能介紹一些國外的目前關于高速PCB設計水平、加工能力、加工水平、加工材質以及相關的技術書籍和資料嗎?

專家解答:

現在高速數字電路的應用有通信網路和計算機等相關領域。在通信網路方面,PCB板的工作頻率已達GHz上下,迭層數就我所知有到40層之多。計算機相關應用也因為芯片的進步,無論是一般的PC或服務器(Server),板子上的最高工作頻率也已經達到400MHz (如Rambus) 以上。因應這高速高密度走線需求,盲埋孔(blind/buried vias)、mircrovias及build-up制程工藝的需求也漸漸越來越多。 這些設計需求都有廠商可大量生產。

以下提供幾本不錯的技術書籍:

?????? 1.Howard W. Johnson,“High-Speed Digital Design - A Handbook of Black Magic”;

?????? 2.Stephen H. Hall,“High-Speed Digital System Design”;

?????? 3.Brian Yang,“Digital Signal Integrity”;

18.有關柔性電路板的設計與加工.我公司打算采用柔性電路板設計來解決小型成像系統中信號傳送和電路板互接的問題。請問剛柔板設計是否需要專用設計軟件與規范?另外國內何處可以承接該類電路板加工?謝謝。

專家解答:

可以用一般設計PCB的軟件來設計柔性電路板(Flexible Printed Circuit)。一樣用Gerber格式給FPC廠商生產。由于制造的工藝和一般PCB不同,各個廠商會依據他們的制造能力會對最小線寬、最小線距、最小孔徑(via)有其限制。除此之外,可在柔性電路板的轉折處鋪些銅皮加以補強。至于生產的廠商可上網”FPC”當關鍵詞查詢應該可以找到。

19.PCB的布線調整.我想請問一個問題:因覺機器布的不如意,調整起來反而費時。我一般是用的手工布線,現在搞的PCB板多半要用引腳密度較大的貼片封裝芯片,而且帶總線的(ABUS,DBUS,CBUS等),因工作頻率較高,故引線要盡可能短.自然的就是很密的信號線勻布在小范圍面積的板子上。我現感覺到花的時間較多的是調整這些密度大的信號線, 一是調整線間的距離,使之盡可能的均勻。因為在布線的過程中,一般的都時不時的要改線。每改一次都要重新均勻每一根已布好的線的間距。越是布到最后,這種情況越是多。 二是調整線的寬度,使之在一定寬度中盡可能的容下新増加的線。一般一條線上有很多彎曲,一個彎就是一段,手工調整只能一段一段地調整,調整起來也費時間。 我想如果在布線的過程中,能按我的思路先粗粗地手工拉線,完了以后, 軟件能從這兩個方面幫我自動地調整。或是即便已布完,如要改線,也是粗粗地改一下,然后讓軟件調整。甚至,到最后我覺的需要調整元件的封裝,也就是說整片布線都需要調整,都讓軟件來干。那樣就要快多了.我用的是Protel98。我知道這軟件能做自動均勻調整元件封裝的距離而不能自動調整線距和線寬。可能是其中的一些功能我還不會用,或是有其他什么辦法,在此請教一下。

專家解答:

線寬和線距是影響走線密度其中兩個重要的因素。一般在設計工作頻率較高的板子時,布線之前需要先決定走線的特性阻抗。在PCB迭層固定的情況下,特性阻抗會決定出符合的線寬。而線距則和串擾(Crosstalk)大小有絕對的關系。最小可以接受的線距決定于串擾對信號時間延遲與信號完整性的影響是否能接受。這最小線距可由仿真軟件做預仿真(pre-simulation)得到。也就是說,在布線之前,需要的線寬與最小線距應該已經決定好了,并且不能隨意更動,因為會影響特性阻抗和串擾。這也是為什幺大部分的EDA布線軟件在做自動布線或調整時不會去動線寬和最小線距。

如果這線寬和最小線距已經設定好在布線軟件,則布線調整的方便與否就看軟件繞線引擎的能力強弱而定。如果您對蔽公司Expedition有興趣試看看我們的繞線引擎,請電21-64159380,會有專人為您服務。

電子發燒友App

電子發燒友App

評論