CADENCE PCB設(shè)計技術(shù)方案

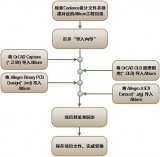

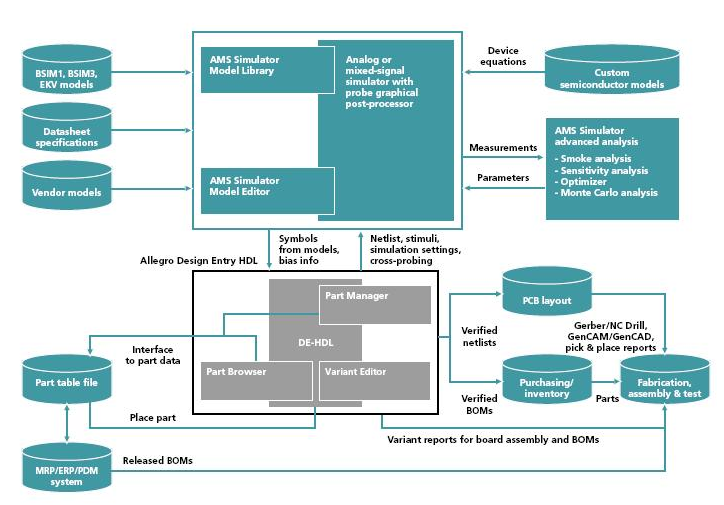

CADENCE PCB設(shè)計解決方案能為解決與實現(xiàn)高難度的與制造密切相關(guān)的設(shè)計提供完整的設(shè)計環(huán)境,該設(shè)計解決方案集成了從設(shè)計構(gòu)想至最終產(chǎn)品所需要的一切設(shè)計流程,包含設(shè)計輸入元件庫工具、PCB編輯器和一個自動/交互連布線器,以及用于制造和機(jī)械CAD的接口,并且隨著設(shè)計難度和復(fù)雜性的增加,可通過統(tǒng)一的數(shù)據(jù)庫架構(gòu),使用模型和庫為Cadence OrCAD和Allegro產(chǎn)品線提供完全可升級的PCB解決方案,加速你的設(shè)計速度并擴(kuò)大設(shè)計規(guī)模,從而提高了設(shè)計效率,縮短了設(shè)計周期,以及更快地實現(xiàn)量產(chǎn)。

Cadence PCB設(shè)計解決方案集成在以下產(chǎn)品中:

. Cadence Allegro PCB Design LXL和GXL

. Cadence OrCAD PCB Designer、Cadence OrCAD PCB Designer with PSpice以及Cadence OrCAD PCB Designer Basics

. Cadence OrCAD EE Designer 和 Cadence OrCAD EE Designer Plus

優(yōu)點

.可靠、可升級、可節(jié)約成本的PCB編輯和布線解決方案,并隨設(shè)計的需求而時刻更新

.提供從基礎(chǔ)/高級布局和布線到戰(zhàn)略性規(guī)劃和全局布線的完整的互聯(lián)環(huán)境

.使用高速規(guī)則/約束加快高級設(shè)計

.包含一套全面的功能組合

.包含一個從前端到后端的約束管理系統(tǒng),用于約束創(chuàng)建、管理和確認(rèn)

.通過應(yīng)用軟件的整合提高設(shè)計效率

.可實現(xiàn)前端到后端的緊密結(jié)合

功能特性

PCB編輯器技術(shù)

PCB編輯環(huán)境

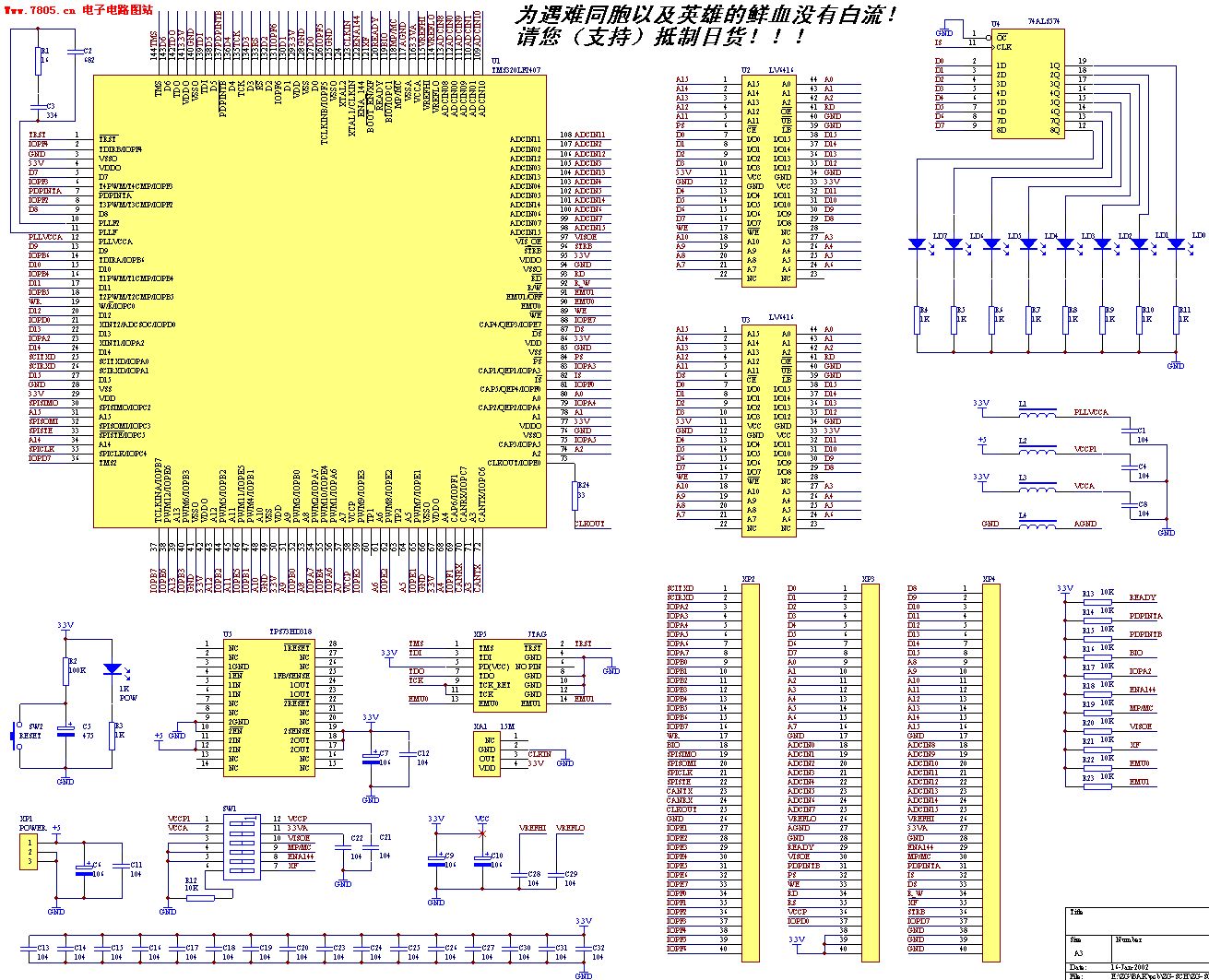

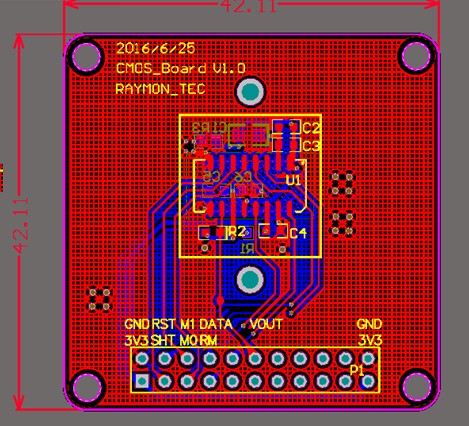

Cadence PCB設(shè)計解決方案的核心是PCB編輯器,這是一種直觀的、易于使用的、約束導(dǎo)向型的環(huán)境,方便用戶創(chuàng)建和編輯從簡單到復(fù)雜的PCB。它廣泛的功能組合解決了當(dāng)今設(shè)計和制造中存在的各種問題。該PCB編輯器提供了強(qiáng)大而靈活的布局規(guī)劃工具,基于Allegro平臺的PCB設(shè)計分割技術(shù)提供了同步設(shè)計功能,其功能可縮短布線時間,并加速產(chǎn)品更早的上市,強(qiáng)大的基于形狀的走線推擠功能帶來了高生產(chǎn)效率的互聯(lián)環(huán)境,同時可實時地顯示長度和時序容限,動態(tài)鋪銅功能提供了在放置和布線迭代時的實時鋪地填充和修復(fù)功能,該PCB編輯器還可以產(chǎn)生全套底片加工,裸板裝配和測試輸出,包括Gerber 274x、NC drill和各種格式的裸板測試,見圖1。

?

約束管理

約束管理系統(tǒng)實時地顯示了物理/間距和高速規(guī)則以及它們的狀態(tài),根據(jù)設(shè)計當(dāng)前所處的狀態(tài),并且可適用于設(shè)計過程的任一階段,每個工作表提供了一個電子數(shù)據(jù)表界面,能夠讓用戶以層級的方式進(jìn)行定義,管理和確認(rèn)不同的規(guī)則。這種強(qiáng)大的功能應(yīng)用可以讓設(shè)計師用圖形創(chuàng)建、編輯和評估約束集,使其作為圖形的拓?fù)浣Y(jié)構(gòu),當(dāng)作理想的實現(xiàn)策略的電子藍(lán)圖。一旦約束被提交到數(shù)據(jù)庫中,它們就可被用來驅(qū)動信號線的放置和布線過程。該約束管理系統(tǒng)是完全集成到PCB編輯器中,而約束可以隨著設(shè)計過程的進(jìn)行而被實時地確認(rèn),確認(rèn)過程的結(jié)果是用圖形化的方式表示約束條件是否滿足。滿足約束用綠色顯示,不滿足約束就用紅色顯示,這可使設(shè)計師可以及時地看到設(shè)計的進(jìn)度,以及因電子數(shù)據(jù)表中任何設(shè)計變動而產(chǎn)生的影響。

布圖規(guī)劃與布局

約束和規(guī)則驅(qū)動的方法有利于強(qiáng)大而靈活的布局功能,包括互動和自動的元件布局,工程師或設(shè)計師可以在設(shè)計輸入或布圖規(guī)劃階段將元件或支電路分配到特定的區(qū)域,可以通過REF、封裝方式、相關(guān)信號名、零件號碼或原理圖表/頁面號碼來過濾或選擇元件。當(dāng)今的電路板上有成千上萬種元器件,需要精確的管理,通過實時的器件裝配分析和反饋,得以實現(xiàn)器件裝配時從整體上來考慮并滿足EMS規(guī)則,以提高設(shè)計師的設(shè)計速度和效率。DFA(可裝配型設(shè)計)分析。Allegro PCB Design XL和GXL有提供實現(xiàn)了在互動式元件放置時,實時地進(jìn)行DFA規(guī)則檢查,基于一個器件類型和封裝排列的二維電子表格,DFA可以實時地檢查器件的邊到邊,邊到端或端到端的距離是否違反最小要求,使得PCB設(shè)計師可以同步地放置元器件以實現(xiàn)最優(yōu)的可布線性,可生產(chǎn)性和信號時序要求。

戰(zhàn)略規(guī)劃和設(shè)計意圖(GRE,global rounting environment)

由總線互聯(lián)主導(dǎo)的高度約束,高密度設(shè)計可能會花大量時間用于戰(zhàn)略性規(guī)劃和布線,加上當(dāng)今元件的密度問題,新的信號標(biāo)準(zhǔn)和特定的拓?fù)浣Y(jié)構(gòu)要求,傳統(tǒng)的CAD工具和技術(shù)已經(jīng)不足以滿足捕捉 設(shè)計師的特定布線意圖要求。

全局布線環(huán)境技術(shù),僅限于Allegro PCB Design GXL,提供了捕捉和貫徹設(shè)計師意圖所需的技術(shù)和方法,通過交互的流程規(guī)劃架構(gòu)和全局布線引擎,用戶可以第一時間地將他們的經(jīng)驗和設(shè)計意圖應(yīng)用到可以了解他們所需的工具中,該解決方案完成了這一目標(biāo), 讓用戶創(chuàng)建抽取的互聯(lián)數(shù)據(jù),通過互聯(lián)流程規(guī)劃架構(gòu),并迅速匯合于一個解決方案中,用全局布線引擎對其加以處理,使用互聯(lián)提取功能降低了系統(tǒng)需要處理的元件數(shù)量,將元件數(shù)量從可能存在的成千上萬種減少到數(shù)百種,從而使手動操作的需要大大地降低,此外,它也降低了用戶在互聯(lián)流程規(guī)劃架構(gòu)中可見器件數(shù)量,減少了他們需要在物理上進(jìn)行管理的元件的數(shù)量,使用提取數(shù)據(jù)功能,布線過程中可以通過提取數(shù)據(jù)比較可布線空間和用戶的設(shè)計意圖是否相一致,從而得以快速完成,所以該布線引擎可以解決布線細(xì)節(jié)問題,貫徹特定的意圖,用戶不用時刻盯著屏幕就可以解決布線問題,這代表著當(dāng)前設(shè)計工具的大幅簡化,讓用戶可以更快更有效地完成他們的設(shè)計,如今用戶可以比以往任何時候更快,更容易地匯合到一個成功的互聯(lián)解決方案中,通過效率和設(shè)計速度的提高縮短了設(shè)計周期時間。見圖2。

?

設(shè)計分割

設(shè)計團(tuán)隊越來越分散于世界各地,這就讓縮短設(shè)計周期時間的相關(guān)問題變得更加復(fù)雜,手動操作解決多用戶問題非常耗時, 緩慢而且易于出錯,PCB設(shè)計分割技術(shù), Allegro PCB設(shè)計層有提供,提供了多用戶, 同步的設(shè)計方法,實現(xiàn)了更快地上市,并減少了布局時間,使用該技術(shù),同時作業(yè)于一個布局圖的多個設(shè)計師可以共同調(diào)用單個數(shù)據(jù)庫,不管小組相隔多遠(yuǎn),設(shè)計分割技術(shù)讓設(shè)計師能夠?qū)⒃O(shè)計分割為多個部分或者區(qū)域,由多個設(shè)計組成員進(jìn)行規(guī)劃和編輯, 這樣,所有設(shè)計師都可以查看所有被分割的部分,并更新設(shè)計視窗,監(jiān)控其他用戶部分的狀態(tài)和進(jìn)度,這可以大大縮短整個設(shè)計周期,并加速設(shè)計流程。

交互式走線編輯

PCB編輯器的交互式布線功能提供了強(qiáng)大的,交互的功能,可以使受控自動操作,以維持用戶操作,同時將布線效率最大化,實時的,圖形的,任意角度的推擠布線讓用戶可以選擇,推擠優(yōu)先,,環(huán)繞優(yōu)先,或,僅環(huán)繞,模式,推擠優(yōu)先模式讓用戶可以建造最合適的互聯(lián)路徑,而實時的,圖形布線器會自動地解決動態(tài)推擠障礙,布線會自動跳躍障礙,如引腳或?qū)Э祝谛枰ㄔ鞌?shù)據(jù)總線時,貼線優(yōu)先模式是完美的解決方案,在環(huán)繞優(yōu)先模式中,布線器圖形會跟隨其它互聯(lián)為優(yōu)先,只有在沒有選擇的時候才會推開或跳過障礙,僅環(huán)繞型執(zhí)行起來就像環(huán)繞優(yōu)先模式,但沒有對其它蝕刻目標(biāo)的推擠意圖,實時嵌入式圖形布線引擎可以通過推擠障礙,或者跟隨銅皮的障礙,同時動態(tài)地跳躍過孔或元件引腳以優(yōu)化布線,在編輯時,設(shè)計師可以使用一種能夠顯示具有高速約束的互聯(lián)下的時序間隙的實時圖形化窗口,互聯(lián)布線還提供了在多個線路上執(zhí)行群組布線的能力,以及用高速長度或延遲約束進(jìn)行線路的交互式調(diào)整的能力,見圖3。

?

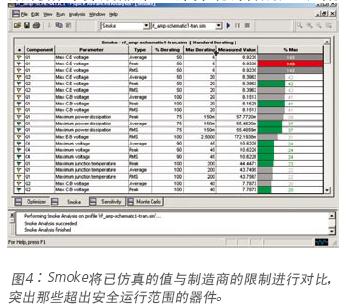

動態(tài)鋪銅

動態(tài)鋪銅技術(shù)提供了實時灌注/修復(fù)功能, Shape參數(shù)可以被適用于三個不同的方面, 參數(shù)可以被添加到全局shape, 同類shape, 以及單個shape中,走線,導(dǎo)孔和元件添加到動態(tài)銅皮中,將會按照其形狀自動連接或避讓,當(dāng)物體被移去時,形狀會自動填充回去,在編輯完成后,動態(tài)鋪銅不需要批量自動避讓,也不需要其它的后期加工步驟, RF設(shè)計RF設(shè)計要求包括要比以往更快,更精確地解決高性能/高頻率電路,RF/復(fù)合信號技術(shù)為PCB RF設(shè)計提供了一種完整的,從前端到后端,從原理圖到布局到制造的解決方案,RF技術(shù)包含了高級的RF性能,包括參數(shù)化創(chuàng)建和編輯RF器件的智能布局功能, 以及一種靈活的圖形編輯器,一種雙向的IFF界面提供了RF電路數(shù)據(jù)的快速而有效地傳輸,并進(jìn)行仿真和確認(rèn),這種雙向流程消除了電路仿真和布局之間手動和易于出錯的迭代,Allegro PCB Design XL和GXL級提供了此功能,見圖4。  ??

??

PCB制造

可以進(jìn)行全套底片加工,裸板裝配和測試輸出,包括各種格式的Gerber 274x,NC drill和裸板測試,更重要的是,CADENCE通過其Valor ODB++界面,還包含Valor Universal Viewer,支持業(yè)界倡導(dǎo)的Gerber-less制造, ODB++數(shù)據(jù)格式可創(chuàng)建精確而可靠的制造數(shù)據(jù),進(jìn)行高質(zhì)量的Gerber-less制造。

PCB自動布線器技術(shù)

自動化的互聯(lián)環(huán)境

設(shè)計復(fù)雜度,密度和高速布線約束的提高使PCB的手動布線既困難又耗時,復(fù)雜的互聯(lián)布線問題通過強(qiáng)大的,自動化的技術(shù)得以解決,這種強(qiáng)大的,經(jīng)實踐證明的自動布線器含有一種批量布線模式,含有眾多的用戶可定義的布線策略,以及自動的策略調(diào)整,互動的布線環(huán)境,具有實時互動走線推擠特性,有助于對走線的快速編輯,具有廣泛的布圖規(guī)劃功能和完整的元件放置特點的互動式放置環(huán)境,使得無需切換應(yīng)用程序就可以進(jìn)行放置變更,優(yōu)化布線,通過使用自動交互式布圖規(guī)劃和放置功能,設(shè)計師可以提高布線質(zhì)量和效率,這與元件布局直接相關(guān),此外,廣泛的規(guī)則集讓設(shè)計師可以控制范圍廣泛的約束,從默認(rèn)的板級規(guī)則到按照線路種類的規(guī)則,再到區(qū)域規(guī)則,Allegro產(chǎn)品提供的高速布線能力能夠解決線路安排,時序,串?dāng)_,布線層的設(shè)置,和當(dāng)今高速電路所需要的特殊器件要求。

自動布線

高級自動布線技術(shù)提供了強(qiáng)大的,基于形狀的自動布線,有快速,高效率等特點,它的布線算法可對于類型廣泛的PCB互連挑戰(zhàn),從簡單到復(fù)雜,從低密度到高密度,并可滿足高速約束的需要,這些強(qiáng)大的算法最高效率地使用了布線區(qū)域,為了給各種情形找到最佳的布線方案,布線器使用一種多通路,重視成本,可解決沖突的算法,廣泛的規(guī)則集提供了物理和電子約束控制的能力,廣泛的規(guī)則集具有解決設(shè)計中各種布線元素的特定規(guī)則的靈活性,用戶可以定義滿足通用物理/間距線路規(guī)則所需的規(guī)則,和復(fù)雜,層級高速規(guī)則的分類規(guī)則,見圖5,?

?

制造性設(shè)計能力可以大大提高制造的良品率,制造算法提供了伸展功能,能夠根據(jù)可用空間自動地加大銅皮間隙,自動銅皮伸展,將銅皮重新定位,創(chuàng)造銅皮與引腳,銅皮與SMD焊盤,以及相鄰銅皮之間的額外空間,從而提高可制造性,用戶可以靈活地定義各種范圍的間距值,或者使用默認(rèn)值, 臨近的拐角和測試點可以被添加到布線過程中,制造算法會自動使用最優(yōu)的規(guī)則范圍,從最大值開始直到最小值,測試點插入可自動添加到可以測試的導(dǎo)孔或焊盤作為測試點,可測試的導(dǎo)孔可以在前端,后端或PCB的兩邊被探測到,支持單面和蛤殼式測試器,設(shè)計師可以根據(jù)它們的制造需要,靈活選擇測試點插入方法,為了避免昂貴的測試設(shè)備調(diào)整,測試點可以是,固定,的,測試點約束包括測試探測表面,導(dǎo)孔尺寸,導(dǎo)孔柵格,和最小的中心間距。

互動式布線編輯

布線編輯器可以簡化走線編輯過程,隨著新的走線,推擠功能會自動推開原有的走線,圍繞引腳進(jìn)行布線,使用推擠功能,設(shè)計師可以沿著現(xiàn)有的走線移動原有的走線部分或?qū)Э祝⑶以诒匾臅r候推到其它引腳和導(dǎo)孔前端,重像功能使其更容易評估假定的情況,隨著走線部分或?qū)Э自谥羔樋刂葡乱苿樱車淖呔€就會被推擠和動態(tài)顯示,這樣經(jīng)調(diào)整的布線可以在接收最終配置前被評估,布線編輯器非常適合密集的多層電路板,有效導(dǎo)孔的位置很難發(fā)現(xiàn),只要在選定的地點點擊兩次就可以定位導(dǎo)孔,可能的話,可以通過將走線推擠到所需的板層上創(chuàng)造出可選地點,如果不可行,布線編輯器會顯示出DRC,并顯示附近的有效導(dǎo)孔位置,此外,復(fù)制布線功能可以讓現(xiàn)有的布線被復(fù)制,以完成未布線的總線連接,簡化總線的創(chuàng)建。

布局編輯

布局編輯器讓設(shè)計師迅速放置元件的同時可以同步評估空間,邏輯流程和擁擠度,移動模式讓元件可以被作為單一元件或群組進(jìn)行翻轉(zhuǎn),旋轉(zhuǎn),排列,推擠和移動,指導(dǎo)布局模式選擇具有最高連通性的元件,計算出其最理想的位置,而不會破壞設(shè)計規(guī)則或約束,用戶可以拒絕也可以接受該位置, 只要直接輸入XY軸位置就可以放置元件, 這種功能對于放置連接器和有固定位置的元件特別實用,密度分析可以通過將PCB與顯示區(qū)域范圍的色圖,從高度擁擠到輕微擁擠的區(qū)域,重疊,圖形化地顯示了電路的擁擠度,這有助于確認(rèn)在哪里進(jìn)行布局調(diào)整,以緩解擁擠度,并提高布線完成率,見圖6。 ??

??

高速約束

高速布線約束和算法能夠滿足當(dāng)今高速電路的差分對,線路布局,時序,串?dāng)_,布線層的設(shè)置和特殊的幾何要求,對于差分對布線,用戶只需定義兩個走線之間的間距,而自動布線器會解決剩下的一切,布線算法可以智能地處理導(dǎo)孔周圍或之間的布線, 并自動順應(yīng)指定的長度或時序標(biāo)準(zhǔn),自動網(wǎng)絡(luò)屏蔽被用于降低噪聲敏感型線路中存在的干擾,不同的設(shè)計規(guī)則可以被應(yīng)用于設(shè)計的不同部分,例如,用戶可以在設(shè)計的走線部分指定嚴(yán)格的間距規(guī)則,而在其它地方指定沒那么嚴(yán)格的規(guī)則。

PCB編輯器集成

PCB布線技術(shù)被緊密結(jié)合到PCB編輯器中, 通過PCB編輯器界面,所有設(shè)計信息和約束被自動傳遞到布線器,一旦布線完成,所有布線信息會自動傳回到PCB編輯器, 圖6,布局編輯器容許你在布線過程的所有階段評估空間,邏輯流程和擁擠度。

文檔

CADENCE工具提供了用戶向?qū)В昂箨P(guān)聯(lián)幫助,F(xiàn)1,參考指南,在線教程和多媒體演示等一系列的文檔, 這些文檔可以幫助你:

.通過搜索在線幫助系統(tǒng)尋找你所需要的答案,并且用豐富的超文本交叉引用在相關(guān)主題間迅速查找,

.通過在線互動教程的幫助學(xué)習(xí)該技術(shù),

.查找錯誤和警告信息。

PCB設(shè)計解決方案對比表格:OrCAD Allegro L,ALLEGRO XL,ALLEGRO GXL SERIES(SPB 16.0)

?

?

?

?

電子發(fā)燒友App

電子發(fā)燒友App

評論