在附件中是如何設置等長線的規則指導,因為經常性的會忘記,所以經撰寫下來,以供自己和他人參考,避免不必要的時間浪費在查找資料上。

2020-08-10 12:35:58

各位大俠,Allegro16.6 T等長是如何設置的呢,請幫幫忙啦~~~~

2016-02-29 08:22:15

allegro中 ddr等長設置及繞線的步驟

2015-12-28 22:01:11

個人小結,希望能對那些還不會用allegro設置等長規則的朋友有點作用。也歡迎同行交流。

2013-12-26 15:53:24

我需要畫1條50歐姆的特性阻抗線(射頻模塊到SMA天線),不知道allegro中的詳細操作步驟?請哪位賜教一下,謝謝

2015-03-04 10:50:33

/1bpr4Edh 密碼:eb61完整的整個視頻主要講解內容:一.allegro軟件常用菜單介紹二.簡單電路fanout1.走線和打孔2.IC及簡單電路的fanout3.移動、拷貝、及修改的靈活運用4.fanout

2016-06-21 15:18:02

用AD15正常走線再貼線是沒有問題的,但是當繞完等長再貼線時所繞部分會重復,總長變長。目前解決辦法是貼完線再一根根在所繞部分再重新Layout一下,請問各路大神有沒有遇到此問題并且有更好地解決辦法?

2018-09-03 11:13:04

我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對間等長有沒有要求?(PS:16對差分線,都做等長好復雜)謝謝!

2023-12-18 06:26:51

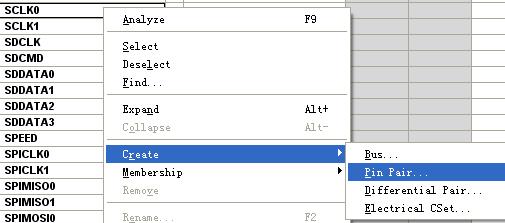

Class會增加一個 New Class,在該網絡組上右鍵,修改一個你想要的名字,如:SDRAM 等。單擊打開它,將需要等長的網絡,從左邊選取并添加到右邊的窗口中。然后再點擊 關閉設置。二. 布線在布

2013-01-12 15:18:43

采集所有信號的值,就必須對信號傳輸的延遲進行控制。等長走線的目的就是為了盡可能的減少所有相關信號在 PCB 上的傳輸延遲的差異。至于 USB/SATA/PCIE 等串行信號,并沒有上述并行總線的時鐘

2020-07-14 14:30:31

AltiumDesigner等長布線操作 我為大家介紹 等長布線,”等長走線“簡單的理解就是讓指定網絡的走線”長度“一樣。等長走線的主要目的是為了補償同一組時序相關的信號線中延時較小的走線,盡量減小

2018-03-09 09:54:43

C6000的CPU執行指令是流水線方式的,每個時鐘可以同時執行8個指令,這樣一來,不會產生沖突嗎?比如第一條指令,賦值給一個寄存器;第二條指令,讀取這個寄存器的值;如果并行,這樣的話,第二條指令怎么能讀到第一條指令賦給寄存器的值呢??用C或者匯編編寫程序時,要不要考慮這種沖突呢?謝謝您的回答

2019-01-15 10:27:23

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條雙向數據線配置,并進行主機發送從機接收。 1、SPI簡介及相關函數介紹SPI支持以三線同步串行模式進行數據交互,加上片選線支持硬件切換主從模式

2023-04-25 16:47:06

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條雙向數據線配置,并進行主機接收從機發送。 1、SPI簡介及相關函數介紹關于SPI單工通信模式下1條時鐘線和1條雙向數據線配置介紹,在第46章已經

2023-04-25 16:48:14

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條單向數據線配置,并進行主機接收從機發送。 1、SPI簡介及相關函數介紹關于SPI單工通信模式下1條時鐘線和1條單向數據線配置介紹,在第46章已經

2023-04-25 16:50:41

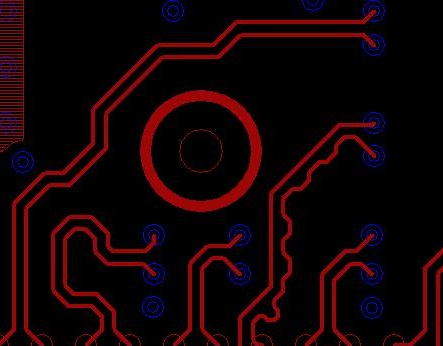

`如附圖所示的多個DDR2地址線走線等長大家是怎么做的(用pads),大家有什么好的方法嗎?共享一下,謝謝!`

2013-08-05 11:09:23

我正在使用 altium designer 設計一塊FPGA、DDR的板子。有一些疑惑,在繞等長線時,有一些線有過孔有一些線沒過孔,我發現穿過孔的距離并沒有被計算在線長中。那過孔豈不是會造成很大

2015-06-18 17:14:35

本帖最后由 宋一鋒 于 2016-11-25 17:53 編輯

PADS等長走線教程

2016-11-18 15:06:20

PADS等長走線教程

2013-04-27 23:34:35

PADS等長走線教程

2014-11-25 01:10:28

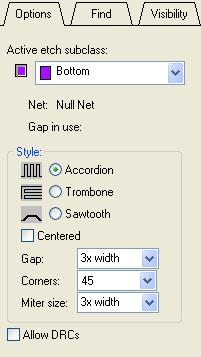

`各們老師們,如何設置差分等長自動走曲形線,而不是蛇形線。在長度約束里我設置數量也是最小了還是沒有像這樣的曲形線,是不是PADS沒有這個功能,請各們老師們幫小弟解答一下。`

2019-06-10 10:23:30

電阻RS值為O~33 Ω,并聯匹配電阻RT值應該在25~68 Ω。本組內的信號不要和數據信號組在同一個電阻排內。控制信號組:控制信號組的信號最少,只有時鐘使能和片選兩種信號。仍需要有一個完整的地平面和電源

2017-10-16 15:30:56

號的等長約束一般都比較嚴格,基本會要求在等長正負50mil以內甚至更小。經常看到的還有內存顆粒的等長要求。有些約束說DDR2的等長要求數據線時鐘線等長控制在正負50mil,地址線等長控制在正負

2014-12-01 11:00:33

SDRAM要跑143M ,那SDRAM走線 有哪些要求?數據線等長,地址線等長 ,時鐘線長度各有什么要求?

2015-01-29 15:09:21

請問各位大佬:TF數據線和時鐘線等長,這種情況如何處理有一根數據線較長,這時還是以時鐘線長度為基準嗎

2019-03-19 07:35:02

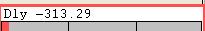

畫一組等長線,某些線的等長進度條騙了我。以為達到設定的長度會停下來,可是還是超出了好多。怎么設定讓他嚴格等長

2014-12-31 11:27:41

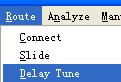

;數字鍵2增大繞線拐角幅度;數字鍵3減小繞線Gap間距;數字鍵4增大繞線Gap間距;Shift+a可以直接在走線模式下繞點對點等長Ctrl+鼠標中鍵可以查看網絡長度原創文章,轉載請注明: 轉載自 allegro小北PCB設計

2018-08-04 13:03:03

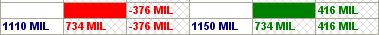

pcb editor里面調地址等長線的時候右下角出現的提示條是什么意思?有紅色的綠色的?

2015-07-27 17:32:49

CB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關”信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是時鐘線

2019-05-22 02:48:05

protel 中兩個焊盤之間用多條導線連接要怎么設置? 只要我第二條一連上第一條導線就會消失 。這可以設置嗎?

2012-09-03 11:25:03

想用一個串口收發兩條指令 。先發一條指令 ,回數。判斷回數正確在發另一條指令 ,回第二條回數。采用堆棧結構。堆棧0:堆棧1:運行后buffer顯示:我希望是buffer2 中回第二條發數指令+第二條

2015-06-13 10:16:17

請教一下。我畫等長差分線。這一條想走蛇形線。但是點不動。。

2019-08-08 05:35:18

1、時鐘線等長概念 在一塊主板上,從北橋芯片到CPU、內存、AGP插槽的距離應該相等,主板設計的基本要求,即所謂的“時鐘線等長”概念。作為CPU與內存連接橋梁的北橋芯片,在布局上是很有講究的。例如

2018-08-30 10:14:47

剛學ALLEGRO,一直搞不懂差分對設置等長跟阻抗匹配的關系,不知附圖那樣設置對不對,求指點

2014-11-30 22:41:22

我在畫一原理圖,將Flash連在兩個接口上,想讓Flash到兩個接口都等長,而因為屬于同一網絡節點,結果弄成了一條線等長,求指導啊

2013-01-15 15:59:40

、等長 (7)不要驅動其他時鐘二、布線 (1)時鐘晶振:時鐘線先經過負載電容,再到達晶振,周圍打孔,GND屏蔽 (2)同源時鐘:時鐘線的并聯匹配電阻靠近負載芯片,串聯電阻靠近時鐘芯片或者CPU

2019-05-21 09:34:14

如何將RXD與TXD倆條線經過轉化后用一條線代替

2013-01-25 10:53:40

有一種新概念使您能夠只用兩條引線進行4線電阻測量為什么使用4條線測量電阻?2x4線電阻測量是怎樣的?哪種萬用表適合您?

2021-04-09 06:34:22

各位大俠:想請問下,如何在Protel ***中設置手工不同網絡之間的等長走線,越詳細越好!謝謝!

2012-09-15 22:44:01

文|原創:臥龍會 不安分的饅頭相信很多LAYOUT 工程師都聽說過高端產品用ALLEGRO,低端產品用AD的說法吧。當然這種說法也不是完全錯誤,這個就見仁見智吧。畢竟ALLEGRO在高速布線方面確實

2018-01-12 17:09:48

在ALLEGRO中設置好T型接點后,如下圖所示據我的理解,ALLEGRO中T型接點等長設置的是圖中BC和BD兩斷走線的等長,對吧??那如何設置AB走線的等長??

2017-07-07 17:55:14

畫等長線的時候,兩根線的差距差了200MM,并且線的密集程度較大,怎么處理?另外 AD中的xSignals怎么用的,有啥用

2019-07-12 18:01:52

線沒有按規則走線這里我知道,這是為了達到等長的要求才這樣處理的,如果兩條線完全等距就沒法滿足等長要求了。4、另外我最想問的就是關于數據線、地址線、時鐘線的等長關系,數據線是組內等長他和時鐘線地址線沒有

2012-10-29 16:14:50

我用PROTEL99SE畫好了原理圖,開始進行PCB布線,我想將圖示左邊的二條垂直相交的線在交點處畫2條斜線,結果它自動將本來是一條線分成二段并與斜線組成二條新線,而我在旁邊沒有節點處這樣畫又可以實現的意圖,請問是哪里設置關閉自動合并操作。

2013-12-25 23:16:05

AD轉換芯片數字輸出A0-A11這12根數據線與FPGA連接時要做等長嗎?

AD轉換芯片時鐘為70MHz,如果不需要,那么時鐘速率達到多少需要做等長,就是畫蛇形線!

2023-12-12 08:15:53

AD轉換芯片數字輸出A0-A11這12根數據線與FPGA連接時要做等長嗎?AD轉換芯片時鐘為70MHz,如果不需要,那么時鐘速率達到多少需要做等長,就是畫蛇形線!

2019-01-21 15:55:14

DDR3的數據線等長是怎么設置長度的

2019-07-17 04:47:35

跪求Altium designer中單線等長和差分等長以及保持原間距走線和等間距走線是怎么使用的,請求高人指點,謝謝!

2019-09-25 05:35:17

等長線畫好之后 白色飛線如何刪除

2019-08-28 04:32:34

除了 I2C1 引腳 35 和 36 之外,CMWX1ZZABZ 中是否還有第二條 I2C 總線?我寧愿使用第二個 I2C 而不是添加 MUX 來連接所有傳感器。

2022-12-15 07:03:55

在MCU和SRAM連接的數據線和地址線是分別做等長(就是數據線一組自己做等長,地址線一組做等長),還是數據線和地址地址線一起做等長?另外那些SRAM的片選信號線等控制線需要做等長嗎?是自己等長還是和數據線地址線一起?SRAM布線是對走線的長度有沒有限制?

2019-09-19 23:25:09

請問一下allegro如何使二條時鐘線等長?

2021-04-25 08:47:46

有個項目很糾結,希望大家幫忙解答下:用的芯片主要有一塊DSP芯片,一塊DDR2芯片,一塊FLASH芯片等,在走線的時候這3個芯片之間的數據線,地址線需不需要等長走線?

2019-09-26 05:38:04

差分線何時要考慮線的等長?如果要考慮使用等長線的話,兩根信號線之間的長度之差最大不能超過多少?如何計算?

2019-05-20 05:35:12

用AD16畫等長時 ,地址線已經都連接上了,但是顯示長度都為0,怎么解決呢?

2019-06-11 05:35:35

如果我把DDR的數據線的高8位分為一組,低8位分為一組,組內等長,這兩組線的長度是不是要一樣長?然后我把地址線,控制線,時鐘線分為一組等長,地址線,控制線,時鐘線的長度是不是要與數據線的長度一樣長,還是怎么樣???

2019-06-14 05:35:21

范圍,而不是等長。又因為飛行時間的最小時序要求一般都可以滿足,也就是第二個公式在很多場合可以忽略不計,帶給PCB設計的要求就是符合第一個公式,結論就是走線越短越好。任何因為并不存在時序要求而做的整個總線繞等長,而又為了繞等長而導致這個總線的布線度增加,串擾增加,這樣的設計是錯誤的,失敗的例子非常多。

2014-10-21 09:35:50

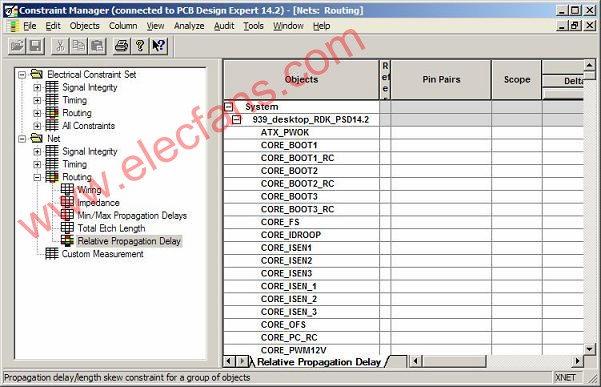

對于簡單走線等長在以前文檔中都有涉及這里不再復述了,下面內容將給大家介紹一下有關Xnet等長的設置問題, 如現在主板DD

2010-06-28 09:38:18 27423

27423

allegro_差分線等長設置,有需要的下來看看

2016-02-22 16:15:35 62

62 第一步:連接好需要繞等長的線,

第二步: T+R T+R開始繞等長, TABTAB 鍵調出等長屬性設置框

第三步:滑動走蛇形線即可;

2016-09-12 16:13:30 0

0 有了單線的自動等長,那就肯定不會放過板上隨處可見的差分了,看大招——Auto-interactive Phase Tune。現在板子的速率越來越高,板上的差分線也就跟著越來越多,對內等長的工作量自然就加大了。但是自從有了繞線新功能,就再也不擔心繞等長費時多啦。步驟和單線繞等長一樣,簡單明了。

2018-10-19 15:33:40 26240

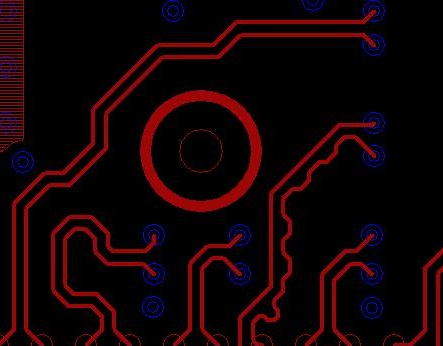

26240 經常畫高速板的同學都知道,10個高速板有9個要繞等長,而且內存出現的頻率尤其頻繁,整的現在畫板子不繞兩下都有點不習慣。好在上期給大家介紹了幾種快的不能再快的繞等長的方法,用allegro繞等長還是非常任性的。看看下圖,多么漂亮,整齊,干凈,密密麻麻繞的像一根根腸子似的等長線。

2018-11-11 10:55:36 4915

4915 本文檔的主要內容詳細介紹的是Allegro PCB設計時等長設置的一些方法與技巧解析。以DDR3(4pcs,fly-by 結構)為例,講述一下在allegro 中如何添加電氣約束(時序等長)。

2018-11-27 16:02:57 0

0 至于 USB/SATA/PCIE 等串行信號,并沒有上述并行總線的時鐘概念,其時鐘是隱含在串行數據中的。數據發送方將時鐘包含在數據中發出,數據接收方通過接收到的數據恢復出時鐘信號。這類串行總線沒有

2018-11-29 15:34:27 4989

4989 等長走線的目的就是為了盡可能的減少所有相關信號在 PCB 上的傳輸延遲的差異。至于 USB/SATA/PCIE 等串行信號,并沒有上述并行總線的時鐘概念,其時鐘是隱含在串行數據中的。數據發送方將時鐘

2019-04-26 15:27:25 10423

10423

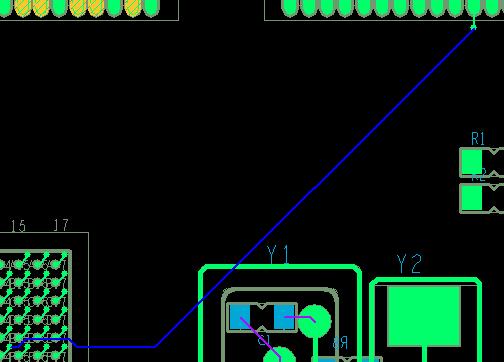

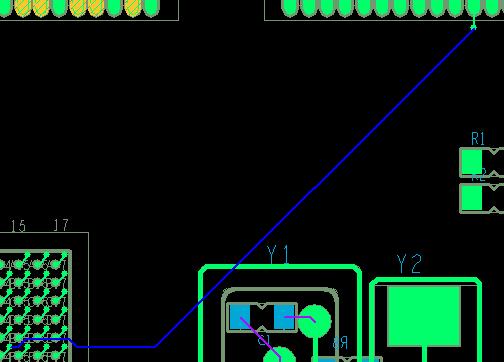

本例中需要實現PCI-e金手指到EMMC芯片等長,包括D0-D7,CLK,CMD這10條網絡。查看各條網絡,確認是否存在串聯匹配電阻。本例中,僅在時鐘線上存在,如下圖的高亮器件。

2019-06-22 09:44:22 8172

8172

在PCB設計中,等長走線主要是針對一些高速的并行總線來講的。 由于這類并行總線往往有多根數據信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDRSDRAM)甚至4次,而隨著芯片運行頻率的提高

2020-09-27 14:08:18 2505

2505

在PCB設計中,等長走線主要是針對一些高速的并行總線來講的。 由于這類并行總線往往有多根數據信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDRSDRAM)甚至4次,而隨著芯片運行頻率的提高

2020-10-24 09:29:38 8604

8604 在 PCB 設計中,等長走線主要是針對一些高速的并行總線來講的。由于這類并行總線往往有多根數據信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDR SDRAM)甚至 4 次,而隨著芯片運行

2020-11-22 11:54:17 18394

18394 Allegro的全稱是CadenceAllegroPCBDesigner,是Cadence公司推出的一個完整的、高性能印制電路板設計套件。通過頂尖的技術,它為創建和編輯復雜、多層、高速、高密度

2022-05-13 09:28:25 1797

1797

Allegro(AiDT)自動等長介紹

2022-12-30 09:19:41 3

3

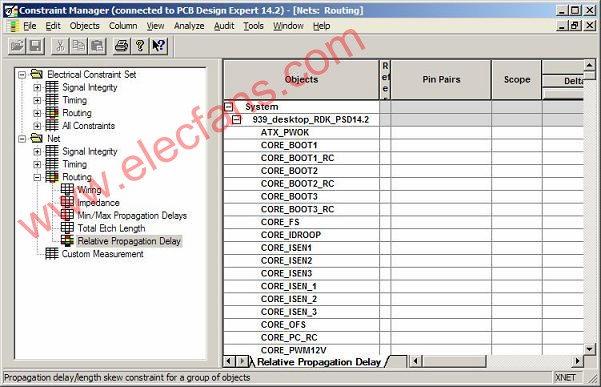

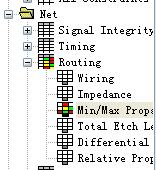

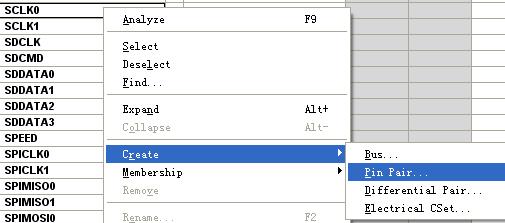

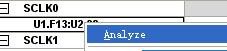

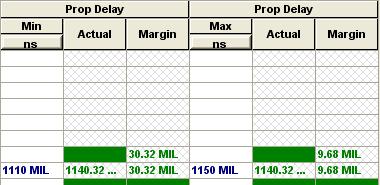

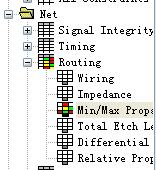

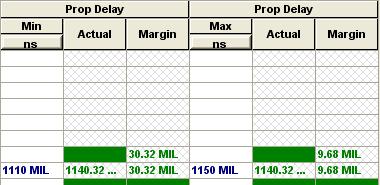

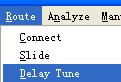

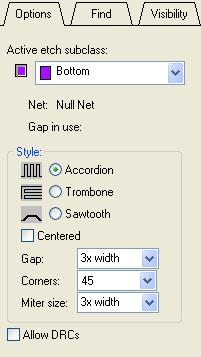

?打開約束管理器,在

?打開約束管理器,在 ?

? ??

?? ?

? ?

? ??

?? ?

? ?

?

??

?? ?

? ?

?

?

? ??

?? ?

? ?

? ??

?? ?

?

??

?? 電子發燒友App

電子發燒友App

評論