傳輸線效應(yīng)PCB 板上的走線可等效為下圖所示的串聯(lián)和并聯(lián)的電容、電阻和電感結(jié)構(gòu)。串聯(lián)電阻的典型值0.25-0.55 ohms/foot,因?yàn)榻^緣層的緣故,并聯(lián)電阻阻值通常很高。將寄生電阻、電容和電感

2009-06-18 07:53:30

關(guān)于傳輸線內(nèi)電磁波的反射和投射

2021-01-06 07:55:22

傳輸線原理和功率測量 議程如果您能回答這些問題:? 為什么要測量功率?? 好的傳感器有哪些特點(diǎn)?? 有辦法測量峰值功率嗎?? 什么是調(diào)制信號?? 我能在多大程度上影響不確定度?那么您已有良好的基礎(chǔ)!

2009-10-15 09:28:41

板的生產(chǎn)變得越來越重要。另外,其它的方法,如余線(stub)長度最短化、末端去除和整線使用,也用來保持信號傳遞中瞬時(shí)阻抗的穩(wěn)定。四. 傳輸線阻抗的計(jì)算設(shè)計(jì)一個(gè)預(yù)定的特性阻抗,需要不斷調(diào)整線寬、介質(zhì)厚度

2015-01-23 11:56:02

必不可少的條件 ,從而達(dá)到寬頻帶傳輸的目的。 以 500kHz~2MHz 范圍內(nèi)的超聲換能器的阻抗匹配變壓器的設(shè)計(jì)為例 ,具體給出了確定傳輸線變壓器特性阻抗、線長、磁心、導(dǎo)線型號和匝數(shù)的方法。

2020-02-20 18:43:02

傳輸線在計(jì)算機(jī)的應(yīng)用分析在應(yīng)用Smith圓圖60多年的今天。計(jì)算機(jī)的飛速發(fā)展促成傳輸線CAD的出現(xiàn)。換句話說,Smith圓圖的全部功能都可以由Computer Program來實(shí)現(xiàn)。本講主要討論單枝節(jié)匹配和雙枝節(jié)自動(dòng)匹配。 [hide][/hide]

2009-11-02 10:09:13

在低頻時(shí),一段普通導(dǎo)線就可以有效地將兩個(gè)電路短接在一起,但是在高頻時(shí)候就不同了。在高頻電路中,一個(gè)小小的過孔、連接器就會對信號產(chǎn)生很大的影響。為了分析高速信號,引入了一個(gè)新的模型——傳輸線。傳輸線有什么特征?主要是時(shí)延和阻抗。如果電路中傳輸線的阻抗突變會導(dǎo)致信號的反射,使得信號質(zhì)量產(chǎn)生較大的影響。

2019-08-12 06:15:15

傳輸線理論(1)

2012-04-08 11:28:48

傳輸線的例題講解傳輸線問題這里暫時(shí)告一段落,本講全面地回顧一下傳輸線理論的基本內(nèi)容和基本方法。[/hide]

2009-11-02 10:12:37

`<p><font face="Verdana">傳輸線的基本知識</font>

2008-12-05 15:38:12

信號在傳播過程中的能量損失不可避免,傳輸線損耗產(chǎn)生的原因有以下幾種:導(dǎo)體損耗,導(dǎo)線的電阻在交流情況下隨頻率變化,隨著頻率升高,電流由于趨膚效應(yīng)集中在導(dǎo)體表面,受到的阻抗增大,同時(shí),銅箔表面的粗糙度也

2019-08-02 08:28:08

一段如下圖所示的無限長的傳輸線的傳輸線上某幾個(gè)點(diǎn)處的電壓和電流值在圖中標(biāo)出。對無限長的傳輸線,電壓與通過該點(diǎn)的電流相除所得的比值保持常數(shù)。這個(gè)比值就稱為傳輸線的特性狙抗。數(shù)學(xué)上表示為:特性阻抗

2017-12-29 15:45:10

(平衡式)傳輸線,而單端應(yīng)用較多。單端傳輸線路下圖為典型的單端(通常稱為非平衡式)傳輸線電路。單端傳輸線是連接兩個(gè)設(shè)備的最為常見的方法。在上圖中,一條導(dǎo)線連接了一個(gè)設(shè)備的源和另一個(gè)設(shè)備的負(fù)載

2009-09-28 14:48:47

傳輸線矩陣分析 在全駐波傳輸線中,把短路工作狀態(tài)作為標(biāo)準(zhǔn)狀態(tài);完全類似,在行駐波狀?態(tài)中,則把小負(fù)載電阻 < 作為標(biāo)準(zhǔn)狀態(tài),其它狀態(tài)只是在

2009-11-02 09:46:40

傳輸線腔理論 矩形腔和圓柱腔都屬于一類傳輸線腔。我們可以把它作為一類模型總結(jié)出來。 [/hide]

2009-11-02 17:47:32

在計(jì)算阻抗之前,我想很有必要理解這兒阻抗的意義。傳輸線阻抗的由來以及意義傳輸線阻抗是從電報(bào)方程推導(dǎo)出來(具體可以查詢微波理論)

2019-06-03 06:34:27

結(jié)構(gòu) 解決傳輸線效應(yīng)的另一個(gè)方法是選擇正確的布線路徑和終端拓?fù)浣Y(jié)構(gòu)。走線的拓?fù)浣Y(jié)構(gòu)是指一根網(wǎng)線的布線順序及布線結(jié)構(gòu)。當(dāng)使用高速邏輯器件時(shí),除非走線分支長度保持很短,否則邊沿快速變化的信號將被信號主干走

2017-06-08 15:43:43

在接收端并聯(lián)端接一個(gè)與傳輸線阻抗匹配的電阻,因接收端多為大輸入阻抗,故并聯(lián)后電阻約等于傳輸線阻抗,此法雖然改進(jìn)了振鈴現(xiàn)象,但會降低高電平。

2019-05-23 08:47:00

1. SI問題的成因 SI問題最常見的是反射,我們知道PCB傳輸線有“特征阻抗”屬性,當(dāng)互連鏈路中不同部分的“特征阻抗”不匹配時(shí),就會出現(xiàn)反射現(xiàn)象。 SI反射問題在信號波形上的表征就是:上沖

2018-09-21 11:47:55

本文主要介紹了目前業(yè)界使用的幾種PCB傳輸線信號損耗測量方法。由于采用的測試方法不同,測得插入損耗值也不一樣,測試結(jié)果不能直接做橫向?qū)Ρ龋虼藨?yīng)根據(jù)各種技術(shù)方法的優(yōu)勢和限制,并且結(jié)合自身的需求選擇合適的信號損耗測試技術(shù)。

2021-02-24 06:59:59

在電路設(shè)計(jì)的各種場合里都能接觸到傳輸線這一術(shù)語。顯然,傳輸線是信號完整性分析當(dāng)中重點(diǎn)考察的元件之一,很多分析都建立在此基礎(chǔ)上。本文將討論傳輸線的相關(guān)物墁基礎(chǔ)。 那么,什么是傳輸線呢?工程應(yīng)用所

2018-11-23 15:46:38

傳輸線有兩個(gè)非常重要的特征:特征阻抗和時(shí)延。可以利用這兩個(gè)特征來預(yù)測和描述信號與傳輸線的大多數(shù)相互行為。 特征阻抗描述了信號沿傳輸線傳播時(shí)所受到的瞬態(tài)阻抗,它是傳輸線的固有屬性,僅和傳輸線

2018-09-03 11:06:40

)就能支持這一結(jié)論的成立。 為了避免煩瑣的理論和微分方程推導(dǎo),再給出一些關(guān)于一階模型的實(shí)用計(jì)算公式,便于讀者今后查閱。 以上介紹的這些關(guān)系式適用于所有的傳輸線,并且與其幾何形狀無關(guān)。如果知道其中的兩個(gè),就可以求出其余所有的參數(shù),非常便捷實(shí)用。

2018-09-03 11:18:45

為了弄清楚信號在傳輸線的傳播速度,有必要再次仔細(xì)地考察一下信號在傳輸線的傳播過程。 前面介紹了傳輸線擁有兩條路徑:信號路徑和電流返回路徑。當(dāng)信號源接入后,信號開始在傳輸線上傳播,兩條路徑問

2018-09-03 11:06:48

大家在典型的PCB中用到的傳輸線是由埋入或者附著在具有一個(gè)或多個(gè)參考平面的絕緣材料上的導(dǎo)電跡線構(gòu)成的,導(dǎo)電跡線一般使用銅材料,電介質(zhì)使用一種叫“FR4”的玻璃纖維。 數(shù)字設(shè)計(jì)系統(tǒng)中最常見的兩種

2018-09-03 11:06:40

本帖最后由 eehome 于 2013-1-5 10:00 編輯

針對PCB信號傳輸線阻抗不匹配所導(dǎo)致的產(chǎn)品輻射發(fā)射超標(biāo)問題,采取了改變D-SUB、LVDS傳輸線的寬度,并在信號線兩側(cè)追加地保

2012-03-31 14:26:18

是本身傳導(dǎo)損耗,趨膚效應(yīng)和表面粗糙度。下面兩張圖是仿真傳輸線模型時(shí)需要設(shè)置的參數(shù),這次我們選擇的是內(nèi)層差分線做演示。需要在這個(gè)界面編輯線寬,間距,銅厚,以及到參考層的介質(zhì)厚度等參數(shù),編輯完成后,點(diǎn)擊

2022-11-10 17:27:55

。 (六)、避免傳輸線效應(yīng)的方法 針對上述傳輸線問題所引入的影響,我們從以下幾方面談?wù)効刂七@些影響的方法。 6.1 嚴(yán)格控制關(guān)鍵網(wǎng)線的走線長度 如果設(shè)計(jì)中有高速跳變的邊沿,就必須考慮到在PCB

2014-11-19 11:10:50

存在,所有信號在傳輸過程中都會存在損耗。 常見傳輸線損耗有:導(dǎo)體損耗和介質(zhì)損耗,低頻下?lián)p耗主要為導(dǎo)體損耗,高頻主要為介質(zhì)損耗。 (2)導(dǎo)體損耗:通常表現(xiàn)在趨膚效應(yīng)和表面粗糙度帶來的阻性損耗。 a

2023-03-07 16:06:22

最近在研究spice傳輸線,spice中理想傳輸線是等效為延遲電路,眾所周知,SPICE主要基于節(jié)點(diǎn)分析法。每個(gè)器件需要提供導(dǎo)納矩陣。我看了ngspice源代碼中的tra器件的導(dǎo)納矩陣的求解過程

2021-07-07 16:15:43

USB的傳輸線結(jié)構(gòu)是如何的呢?USB的數(shù)據(jù)格式是怎么樣的呢?USB主機(jī)是如何識別USB設(shè)備的?

2021-10-27 06:46:37

請問傳輸線在protel中的原理圖中是像矩形波那樣的嗎?

2012-07-13 10:15:27

數(shù)字信號的邊沿速度(上升或下降時(shí)間)比在PCB走線上傳送的電信號的傳播延遲來得小時(shí),信號將受到傳輸線效應(yīng)的極大影響。電信號在傳輸線的傳送方式就如水流過一根長的方形管子一樣。這就是所謂的電波傳播。就如水是以

2016-09-09 11:11:14

什么是傳輸線?PCB上常見的傳輸線是什么?

2021-10-14 06:53:30

` 本帖最后由 cooldog123pp 于 2020-4-28 08:21 編輯

傳輸線會對整個(gè)電路設(shè)計(jì)帶來以下效應(yīng)。· 反射信號Reflected signals· 延時(shí)和時(shí)序錯(cuò)誤Delay

2018-12-24 10:00:07

作者:黃剛剛接觸高速理論的時(shí)候,那時(shí)說得最多的理論之一就是傳輸線的分布模型,也就是說我們在考慮高速信號傳輸的時(shí)候要把傳輸線分成很多很多段去考量。坦白說,本人在剛?cè)胄泻蟮南鄬Ρ容^長的時(shí)間內(nèi)是沒有很透徹

2019-07-24 08:25:49

什么是傳輸線?傳輸線由哪幾部分組成?

2021-06-15 08:25:36

什么是傳輸線?由哪幾條長度導(dǎo)線組成?PCB的傳輸線結(jié)構(gòu)是如何構(gòu)成的?

2021-06-29 08:36:04

傳輸線設(shè)計(jì)是高頻有線網(wǎng)絡(luò)、射頻微波工程、雷射光纖通信等光電工程的基礎(chǔ),為了能讓能量可以在通信網(wǎng)路中無損耗地傳輸,良好的傳輸線設(shè)計(jì)是重要關(guān)鍵。 無線通信加上視頻技術(shù)將成為未來的明星產(chǎn)業(yè),要達(dá)到這個(gè)

2019-06-20 08:17:26

與計(jì)算方法根據(jù)信號傳輸線的不同位置可以形成各種各樣的結(jié)構(gòu)及其計(jì)算方法(參見《現(xiàn)代印制電路基礎(chǔ)》一書第十四章)。2.3特性阻抗值Z0的一般設(shè)計(jì)規(guī)則 ⑴選用合適的基板(CCL)材料和PCB結(jié)構(gòu),確定信號

2018-02-08 08:29:08

信號在長距離的傳輸線上傳輸時(shí)為什么傳輸線末端上的信號的幅值會隨著頻率的改變而改變,同時(shí)傳輸線的輸入端的幅值也發(fā)生改變(改變都是隨著頻率的增大而發(fā)生幅值上的一會增大一會減小的規(guī)律),而且發(fā)生的相移根據(jù)傳輸線的長度和信號的頻率來計(jì)算得到的理想信號相移差距很大是什么原因?

2018-08-31 10:09:14

信號在長距離的傳輸線上傳輸時(shí)為什么傳輸線末端上的信號的幅值會隨著頻率的改變而改變,同時(shí)傳輸線的輸入端的幅值也發(fā)生改變(改變都是隨著頻率的增大而發(fā)生幅值上的一會增大一會減小的規(guī)律),而且發(fā)生的相移根據(jù)傳輸線的長度和信號的頻率來計(jì)算得到的理想信號相移差距很大是什么原因?

2023-11-21 08:15:53

傳輸線匹配和阻抗共軛匹配矛盾嗎?如果傳輸線的特征阻抗為復(fù)數(shù),那么為了實(shí)現(xiàn)傳輸線和負(fù)載的匹配(相等),就需要把負(fù)載通過一個(gè)匹配網(wǎng)絡(luò)裝換成傳輸線特征阻抗,這樣的匹配就不是共軛匹配了。我想問,會有這種情況存在嗎?還是說特征阻抗一般都是實(shí)數(shù),所以不會存在這種情況。如果存在的話,怎么做匹配呢?

2012-11-13 21:36:47

摘要:在印制電路板設(shè)計(jì)、生產(chǎn)等過程中,傳輸線的信號損耗是板材應(yīng)用性能的重要參數(shù)。信號損耗測試是印制電路板的信號完整性的重要表征手段之一。本文介紹了目前業(yè)界使用的幾種PCB傳輸線信號損耗測量方法

2018-09-17 17:32:53

摘 要:印刷電路板走線傳輸線效應(yīng)是影響印刷電路板走線信號質(zhì)量的主要因素。本文結(jié)合Protel SDK,提出一種采用Client/Server結(jié)構(gòu)嵌入于Protel的計(jì)算機(jī)自動(dòng)印刷電路板走線傳輸線

2018-08-27 15:45:52

? 摘要:在高速印刷電路板(PCB)設(shè)計(jì)中,邏輯門元器件速度的提高,使得PCB傳輸線效應(yīng)成了電路正常工作的制約因素。對傳輸線做計(jì)算機(jī)仿真,可以找出影響信號傳輸性能的各種因素,優(yōu)化信號的傳輸特性

2018-08-27 16:00:07

在高速PCB設(shè)計(jì)過程中,由于存在傳輸線效應(yīng),會導(dǎo)致一些一些信號完整性的問題,如何應(yīng)對呢?

2021-03-02 06:08:38

實(shí)現(xiàn)阻抗控制的傳輸線配置方式控制阻抗 PCB 通常使用微波傳輸帶或帶狀線傳輸線路,以單端(未平衡)或差分(已平衡)配置的方式生產(chǎn)。單端配置以下為幾種常見單端微波傳輸帶和帶狀線傳輸帶的配置:注意以下各

2009-09-28 16:16:56

微波頻率4GHz,但是輸出引腳很窄(只有計(jì)算的微帶線線寬的四分之一左右),如何設(shè)計(jì)傳輸線比較好?如下圖所示兩種方法(黑色的表示電容焊盤),一種直接用跟輸出引腳寬度相同的線引出到電容,然后在電容另一端

2014-01-02 16:35:09

的,同時(shí)沒有任何射頻信號線通過其下穿過的鏡像地,以提供一個(gè)良好的射頻信號信號回路;7、盡量縮短傳輸線的長度,長的傳輸線將帶來衰減,不同的線路使用不同粗細(xì)的走線,如電源就盡可能粗些;8、避免射頻傳輸線的直角

2021-04-20 20:25:28

本文介紹了一種去除傳輸線的方法。

2021-05-21 07:10:45

廣義傳輸線理論 從本門課程一開始,我們就強(qiáng)調(diào)從最宏觀的角度:微波工程有兩種方法——場論的方法和網(wǎng)絡(luò)的方法。首先,我們要把傳輸線理論推廣到波導(dǎo),由微波雙導(dǎo)線發(fā)展到波導(dǎo)是因?yàn)楫?dāng)其它人或物靠近雙導(dǎo)線時(shí)會

2009-11-02 10:26:11

在RF和微波范圍最常用的是同軸線纜,下圖有選擇的展示了RF和微波電路中的傳輸線。 在這些傳輸線中采用損耗很低的介質(zhì)支撐材料以使信號損耗最小。外邊有延續(xù)的圓柱導(dǎo)體的半剛性同軸線在微波范圍內(nèi)有良好的性能

2017-12-21 17:21:59

微波傳輸線理論 微波傳輸的最明顯特征是別樹一幟的微波傳輸線,例如,雙導(dǎo)線、同軸線、帶線和微帶等等。我們很容易提出一個(gè)問題:微波傳輸線為什么不采用50周市電明線呢? 低頻傳輸線和微波

2009-11-02 09:22:38

的焊球上監(jiān)視SERDES發(fā)送器輸出信號很難做到。通常信號會引到SMA或SMP連接器后再用示波 器進(jìn)行監(jiān)測。然而,信號特性會因?yàn)镮C和連接器之間的傳輸線而發(fā)生改變。因此,真正的挑戰(zhàn)是在SERDES引腳處監(jiān)視信號性能,而這可以通過去除傳輸線效應(yīng)來實(shí)現(xiàn)。

2019-08-21 07:12:48

你好,我有一個(gè)短的傳輸線,長3英寸,寬1英寸,標(biāo)準(zhǔn)雙面fr4 0.062“基板。我想知道的是,是否可以在ADS中顯示該傳輸線的電感。通常情況下,線路在ADS中表示為阻抗,但如果有一種方法可以知道

2019-04-26 08:45:57

?表面貼裝易于集成

應(yīng)用范圍: 廣泛應(yīng)用于各類微波系統(tǒng),空間技術(shù)中。標(biāo)準(zhǔn) 50/100歐姆傳輸線

單線金屬導(dǎo)線

帶兩排調(diào)節(jié)墊的單線金屬導(dǎo)線

帶四排調(diào)節(jié)墊的單線金屬導(dǎo)線

2023-06-13 13:57:39

摘要在高頻電路設(shè)計(jì)中,可以采用多種不同的傳輸線技術(shù)來進(jìn)行信號的傳輸,如常見的同軸線、微帶線、帶狀線和波導(dǎo)等。而對于PCB平面電路,微帶線、帶狀線、共面波導(dǎo)(CPW),及介質(zhì)集成波導(dǎo)(SIW)等是常用

2019-06-24 06:35:11

在靜態(tài)直流的情況下,傳輸線就是一個(gè)小電阻,可以忽略。請問這個(gè)結(jié)論對嗎?怎么理解呢

2013-07-18 10:25:45

為什么很多PCB傳輸線的阻抗都是50歐姆?最近搞電路分析,在很多地方看到PCB上的傳輸線特性阻抗都舉例為50歐姆,并且也在很多地方發(fā)現(xiàn)該特性阻抗為50歐姆,想問個(gè)為什么?為什么不是其他的阻值,30歐姆,100歐姆等等。

2018-11-27 09:33:58

請問如何在ADS中設(shè)計(jì)傳輸線?有哪位大神知道嗎

2021-06-22 06:23:57

誰知道如何使用multisim 驗(yàn)證傳輸線匹配原理。那個(gè)傳輸線中的nominal electrical length 是什么意思啊。。 跪求指導(dǎo)。我的這個(gè)圖有什么問題

2014-10-08 09:32:58

)、避免傳輸線效應(yīng)的方法 針對上述傳輸線問題所引入的影響,我們從以下幾方面談?wù)効刂七@些影響的方法。 6.1 嚴(yán)格控制關(guān)鍵網(wǎng)線的走線長度 如果設(shè)計(jì)中有高速跳變的邊沿,就必須考慮到在PCB板上存在傳輸線

2015-05-05 09:30:27

效應(yīng)的方法 針對上述傳輸線問題所引入的影響,我們從以下幾方面談?wù)効刂七@些影響的方法。 6.1 嚴(yán)格控制關(guān)鍵網(wǎng)線的走線長度 如果設(shè)計(jì)中有高速跳變的邊沿,就必須考慮到在PCB板上存在傳輸線效應(yīng)

2018-08-24 17:07:55

的準(zhǔn)確性和實(shí)用性。最通常的做法是將控制EMI的各項(xiàng)設(shè)計(jì)規(guī)則應(yīng)用在設(shè)計(jì)的每一環(huán)節(jié),實(shí)現(xiàn)在設(shè)計(jì)各環(huán)節(jié)上的規(guī)則驅(qū)動(dòng)和控制。 避免傳輸線效應(yīng)的方法 針對上述傳輸線問題所引入的影響,我們從以下幾方面談?wù)効刂七@些

2018-11-22 17:14:46

超過50MHz,將近50% 以上的設(shè)計(jì)主頻超過120MHz,有20%甚至超過500M。當(dāng)系統(tǒng)工作在50MHz時(shí),將產(chǎn)生傳輸線效應(yīng)和信號的完整性問題;而當(dāng)系統(tǒng)時(shí)鐘達(dá)到120MHz時(shí),除非使用高速電路設(shè)計(jì)

2019-06-20 07:31:24

高頻信號傳輸線高頻信號會產(chǎn)生電磁場,向?qū)Ь€四周輻射,并且有趨膚效應(yīng),傳輸線不能直接使用導(dǎo)線,需要考慮走線方式、電容、電感、阻抗等因素。

2019-05-24 06:48:59

摘要:介紹了TLCODE方法對多路傳輸線并聯(lián)電路的模擬情況。根據(jù)TLCODE方法的要求,在引入接地電阻的條件下推導(dǎo)了多路傳輸線并聯(lián)時(shí)的界面電壓公式,同時(shí)構(gòu)建了一個(gè)多路傳輸線并

2010-05-28 10:22:08 11

11 傳輸線效應(yīng)詳解

基于上述定義的傳輸線模型,歸納起來,傳輸線會對整個(gè)電路設(shè)計(jì)帶來以下效應(yīng)。• 反射信號Reflected signals&

2009-03-25 11:29:55 3400

3400 如何減少傳輸線效應(yīng)

高速電路傳輸線效應(yīng)是指系統(tǒng)工作在50MHz時(shí),將產(chǎn)生傳輸線效應(yīng)和信號的完整性問題;而當(dāng)系統(tǒng)時(shí)鐘達(dá)到120MHz時(shí),則必須使用高速電路設(shè)計(jì)知識才能使之

2009-04-07 22:34:47 1110

1110 如何避免高速PCB設(shè)計(jì)中傳輸線效應(yīng)

1、抑止電磁干擾的方法

很好地解決信號完整性問題將改善PCB板的電磁兼容性(EMC)。其中非常重要的是保證PCB板有很好的接

2009-11-20 11:17:00 799

799 傳輸線等效電容的計(jì)算方法

從題目的信息可以得出兩個(gè)信息:(1)這條傳輸線是高速線,沒有特殊說明,缺省阻抗應(yīng)該是50歐姆;

2010-04-16 17:32:38 9201

9201 高速電路傳輸線效應(yīng)是指系統(tǒng)工作在50MHz時(shí),將產(chǎn)生傳輸線效應(yīng)和信號的完整性問題;而當(dāng)系統(tǒng)時(shí)鐘達(dá)到120MHz時(shí),則必須使用高速電路設(shè)計(jì)知識才能使之正常工作。因此,只有通過高速電路仿真和先進(jìn)的物理設(shè)計(jì)軟件,才能實(shí)現(xiàn)設(shè)計(jì)過程的可控性。

2019-01-22 16:17:30 11061

11061

解決傳輸線效應(yīng)的另一個(gè)方法是選擇正確的布線路徑和終端拓?fù)浣Y(jié)構(gòu)。走線的拓?fù)浣Y(jié)構(gòu)是指一根網(wǎng)線的布線順序及布線結(jié)構(gòu)。當(dāng)使用高速邏輯器件時(shí),除非走線分支長度保持很短,否則邊沿快速變化的信號將被信號主干走線上

2019-06-06 14:55:04 1897

1897 在低頻時(shí),一段普通導(dǎo)線就可以有效地將兩個(gè)電路短接在一起,但是在高頻時(shí)候就不同了。在中,一個(gè)小小的過孔、連接器就會對信號產(chǎn)生很大的影響。為了分析高速信號,引入了一個(gè)新的模型——傳輸線。理想傳輸線的兩個(gè)

2020-11-03 10:41:00 2

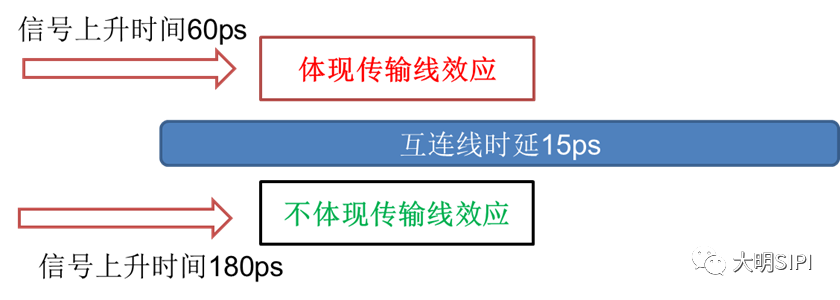

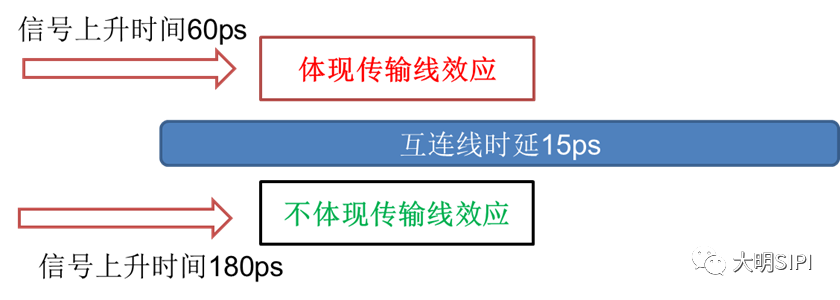

2 當(dāng)互連線的長度大于1/6倍的信號上升時(shí)間的空間延伸時(shí),互連線就體現(xiàn)出傳輸線效應(yīng)。”

上升時(shí)間越小越容易體現(xiàn)傳輸線效應(yīng)。

2023-06-14 17:06:07 822

822

電子發(fā)燒友App

電子發(fā)燒友App

評論