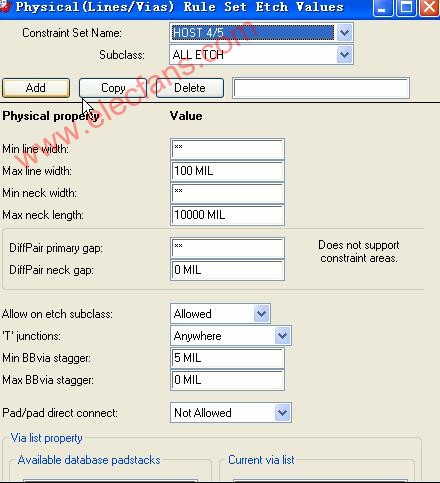

PCB布線經常會要求對重要的信號線進行規則的設置。布線規則的設置通常包括線寬和線距兩大部分。下面就以一主板Layout guide

2010-06-21 08:48:22 10808

10808

本文主要詳解PCB設計高速模擬輸入信號走線,首先介紹了PCB設計高速模擬輸入信號走線方法,其次闡述了九大關于PCB設計高速模擬輸入信號走線規則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

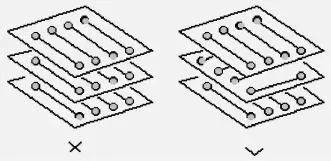

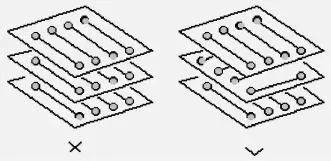

信號線規則二:高速信號的走線閉環規則由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現一種失誤,即時鐘信號等高速信號網絡,在多層的PCB走線的時候產生了閉環的結果,這樣

2018-11-28 11:14:18

各位做過高速電路板的高手,請問在走高速信號線,我想進行等長處理,那么走線的長度如何控制?有相關的計算軟件沒?希望大家積極參與討論十分感謝!

2010-06-27 15:45:47

比如射頻走線或者一些高速信號線,必須走多層板外層還是內層也可以走線

2023-10-07 08:22:18

高速PCB信號走線的九條規則.pdf(220.78 KB)

2019-09-16 07:26:43

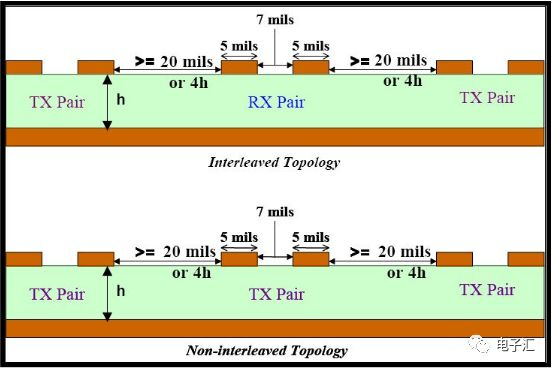

設計,一些心得和大家交流、交流。規則一、高速信號走線屏蔽規則如上圖所示:在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線

2021-03-31 06:00:00

通過高速PCB來控制解決。做了4年的EMI設計,一些心得和大家交流、交流。規則一、高速信號走線屏蔽規則 如上圖所示:在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只

2022-04-18 15:22:08

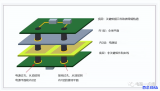

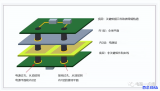

1.高頻信號靠近地平面2.電源層和地層設計滿足20H規則。即地平面的邊緣比電源平面大20H(H是電源層和地層之間的距離)3.將時鐘信號走在中間層4.地平面完整,不要被割斷。5.信號走線盡量不換層

2015-03-06 10:26:55

規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地

2016-01-19 22:50:31

問:使用高速轉換器時,有哪些重要的PCB布局布線規則? 答:為了確保設計性能達到數據手冊的技術規格,必須遵守一些指導原則。首先,有一個常見的問題:“AGND和DGND接地層應當分離嗎?”簡單回答

2018-09-12 15:04:59

我的負片層無法走線,發現是布線規則里面沒有新添加的兩層,這樣應該去哪里設置呢?謝謝。

2022-11-06 19:24:54

BGA芯片的布線規則

2015-05-19 15:25:03

一個優秀的Layout,一塊好的板子,并不是隨便布線連同就可以實現電路要求的,凡事都得謹慎,此處別處摘要,講述SDRAM類高速器件布線規則:如果你沒有信號完整性的知識和對傳輸線的認識,恐怕你很難

2015-01-15 10:39:37

DDR2時鐘線走線規則a)時鐘線包括MEM_CLKOUT#0、MEM_CLKOUT0、MEM_CLKOUT#1、MEM_CLKOUT1,MEM_CLKOUT#2、MEM_CLKOUT2

2015-02-03 14:13:44

附件為DDR3走線主要的規則介紹,有興趣的朋友可以下載看看,老手就不用了~

2019-03-08 20:37:44

DDR-Topology DDR布線通常是一款硬件產品設計中的一個重要的環節,也正是因為其重要性,網絡上也有大把的人在探討DDR布線規則,有很多同行故弄玄虛,把DDR布線說得很難,我在這里要

2019-05-31 07:52:36

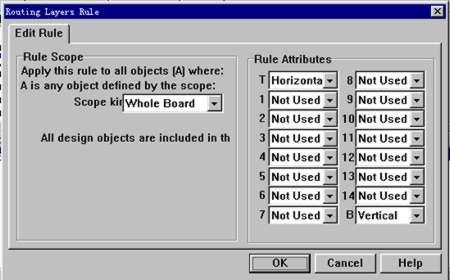

表: PCB布線應遵循的基本規則如下: 1. 控制走線的方向 在PCB布線時,避免將不同的信號在相鄰層形成同一方向,相鄰層的走線應成正交結構,以免減少不必要的層間竄擾。當PCB布線受到結構限制

2023-04-17 14:59:49

各位大神,我的PCB走線規則不知咋回事,只能拐45度的彎。望各位大神指點一二?

2019-04-16 22:44:45

MIPI信號走線相關要求 MIPI總線在目前的移動設備手機/平板的LCD或者Camera應用的十分廣泛。 以下是MIPI信號走線規則一些Checklist 阻抗要求:MIPI的差分線阻抗

2023-04-12 15:08:27

開發中,本人總結出了一套DDR布線方法,具有高度的可行性,于是本人再次編寫一份這樣的文章,除了講述DDR布線規則,還想講述一下布線過程,采用本人的布線過程可以少走很多彎路。本文即將講到的所有方法,無線

2022-08-11 09:07:02

關于PCB的布線規則

2012-06-06 13:31:38

優良的PCB分層策略多層板設計PCB布線規則

2021-02-24 08:17:16

PCB布線規則解析

鋪設通電信號的道路以連接各個器件,即PCB布線。在PCB設計中,布線是完成產品設計的重要步驟。PCB布線有些規則相關知識,用此文來和大家分享一番:

走線的方向控制規則

在 PCB

2023-11-14 16:06:37

PCB布局布線規則

2013-08-06 13:33:46

前言完整具有實際使用價值的PCB是需要符合相應的PCB規則的,這些規則就是設計要求。如果我們在設計PCB時沒有按照這些設計要求來進行PCB板的布局布線時,最后我們設計完成的PCB板是使用不了的。所以PCB的布局布線規則非常非常重要,它能指導我們設計完成能夠滿足要求的并正常工作的PCB板。...

2021-11-11 07:11:58

產生寄生耦合。自動布線的布通率,依賴于良好的布局,布線規則可以預先設定,包括走線的彎曲次數、導通孔的數目、步進的數目等。一般先進行探索式布經線,快速地把短線連通,然后進行迷宮式布線,先把要布的連線進行

2019-08-01 08:04:25

;nbsp;高速信號走線規則教程 ◎ PCB布線的幾點經驗 ◎ &

2009-04-14 23:48:45

Protel 自動布線規則

2012-08-20 18:06:40

SATA3.0的布線規則,與2.0的差別

2015-06-08 19:32:35

全方位剖析BGA布線規則與技巧 http://www.weeqoo.com/bbs/bbsdetail-271365-13.html

2008-07-17 10:33:53

altium_designer_布線規則設定

2013-03-08 22:37:48

復查根據“PCB檢查表”,內容包括設計規則,層定義、線寬、間距、焊盤、過孔設置;還要重點復查器件布局的合理性,電源、地線網絡的走線,高速時鐘網絡的走線與屏蔽,去耦電容的擺放和連接等。復查不合格

2015-07-24 12:29:05

本帖最后由 cooldog123pp 于 2020-2-23 15:45 編輯

2016-01-05 22:04:59

點設計規范https://bbs.elecfans.com/jishu_538123_1_1.html12.【PCB小知識 12】高速信號走線規則https://bbs.elecfans.com/jishu_538939_1_1.html非常感謝@cooldog123pp的分享,期待版主明年更多優秀的帖子!`

2016-01-19 10:32:56

`表層走線與內層走線更為規范的說法應該是微帶線與帶狀線。兩種走線方式因為介質和參考面不同,會存在比較明顯的差異。對于長距離傳輸的高速信號,尤其是背板之類的,需要特別注意損耗帶來的影響,避免高頻分量

2020-03-09 10:57:00

使用高速轉換器時,有哪些重要的PCB布局布線規則?

2021-04-21 06:58:58

問:使用高速轉換器時,有哪些重要的PCB布局布線規則?答:為了確保設計性能達到數據手冊的技術規格,必須遵守一些指導原則。首先,有一個常見的問題:“AGND和DGND接地層應當分離嗎?”簡單回答

2018-10-30 15:01:16

本帖最后由 松山歸人 于 2021-2-25 16:57 編輯

一、在做高壓鋁基板有哪些走線規則?

2021-02-25 10:12:23

請問無刷電機如何去進行pcb布局?無刷電機的pcb走線規劃是怎樣的?

2021-06-26 07:29:35

圖解在高速的PCB設計中的走線規則

2021-03-17 07:53:30

差分信號走線要注意什么?有什么規則?

2021-05-26 06:27:09

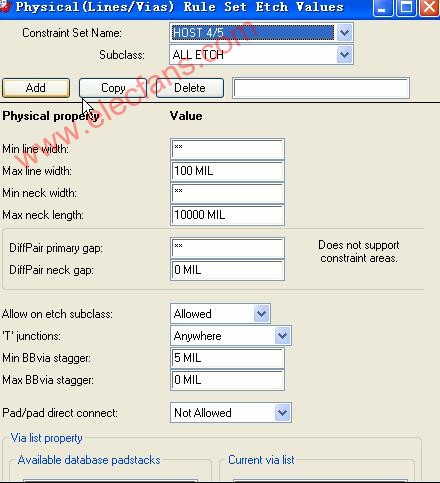

布線規則是設置布線的各個規范(像使用層面、走線寬度、安全間距、過孔大小、布線的拓樸結構等部分規則)可通過Design-Rules 下的 Menu鏈接從其它板導出后,再導入PCB板,這個步驟不必每次都要設置,按個人的習慣,設定一次就可以。

2019-07-16 06:50:29

PCB制板工藝要求,會適當發現原理圖的問題,了解EMI,EMC問題,精通數字模擬信號的劃分,熟悉高速信號走線規則,熟悉ALLEGRO軟件,現有大量空閑時間,希望能夠兼職做產品,如有需要,請聯系人:袁S,QQ:395505627,或發QQ郵箱也可,謝謝大家!`

2017-03-03 09:47:32

電源線和地線的布線規則有哪些

2014-12-15 15:15:04

規則一:高速信號走線屏蔽規則 在高速的設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。 圖1

2018-09-20 10:38:01

新手請教下藍牙 pcb布局與布線規則,求!!

2015-11-23 08:30:31

隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規則:規則一:高速信號走線屏蔽規則在高速

2017-11-02 12:11:12

哎,剛學習PCB布線,了解了些布線規則。有些疑問,還請知道幫忙回答下。1.如何區分大小信號。2.如何判斷那些線要考慮差分啊 .阻抗匹配等。3.如何區分那些走線是要高速走線。呵呵 ,這些問題都感覺問的好菜,可是我是菜鳥,不懂這些,感覺看了很多什么布線規則也是瞎看。

2012-04-26 10:27:05

對于PCB布線規則搞不太懂,電源線和地線的大小一般是怎樣設置的?又是根據什么來設置的?電流電壓大小?請指教!

2019-06-05 05:35:31

請問大俠,怎么樣讓每次打開pads軟件中的顏色和走線規則都保持跟之前一樣

2013-04-20 23:16:57

誰有高速PCB布局布線規范,謝謝

2020-04-16 21:10:10

為100+-15%歐姆DDR布線規則。DDR1走線要求信號盡量不走過孔,信號線等寬,線與線等距,走線必須滿足2W原則,以減少信號間的串擾,對DDR2及以上的高速器件,還要求高頻數據走線等長,以保證信號的阻抗匹配。【第十招】保持信號傳輸的完整性保持信號傳輸的完整性,防止由于地線分割引起的“地彈現象”。

2019-07-28 09:00:18

PADS 2005高速布線規則全集

2006-03-12 02:29:54 0

0 BGA出線規則

2006-05-07 13:54:56 0

0 數字地模擬地的布線規則,如何降低數字信號和模擬信號間的相互干擾呢?在設計之前必須了解電磁兼容(EMC)的兩個基本原則:第一個原則是盡可能減小電流環路的面積;第二個原則

2008-07-18 17:47:12 0

0 pcb布線規則,布板需要注意的點很多,但是基本上注意到了下面的這此規則,LAYOUT PCB應該會比較好,不管是高速還是低頻電路,都基本如此。

2007-12-10 16:35:41 24563

24563 Protel 自動布線規則

一、布線的層面 Protel98、99的PCB編輯器,可以在16個“Signal Layer(信號層面)”上實現布線,每個都可以單獨設置布線屬性

2009-07-02 10:04:57 11151

11151

PCB布線規則之PCI卡篇

PCI卡的布線比較講究,這是PCI信號的特點決定的。在常規性的高頻數字電路設計中我們總是力求避免阻抗

2009-11-18 14:01:57 1110

1110 PCB的DDR布局布線規則與實例教程說明

2015-11-13 16:13:47 0

0 Protel DXP布線規則設置,Protel DXP布線規則設置。

2015-12-28 11:40:31 0

0 數字地模擬地布線規則,如何降低數字信號和模擬信號間的相互干擾

2016-01-04 18:31:05 0

0 AltiumDesigner高級覆銅布線規則。

2016-04-11 15:33:37 0

0 altium-designer-布線規則設定,感興趣的可以看看。

2016-07-22 16:18:06 0

0 EMI相關PCB布局布線規則,感興趣的小伙伴們可以看看。

2016-07-26 15:18:26 0

0 高頻在PCB中的布線規則,感興趣的小伙伴們可以看看。

2016-07-26 15:18:26 0

0 PCB繪制-布局布線規則,感興趣的小伙伴們可以看看。

2016-07-26 16:29:36 0

0 高頻PCB板布線規則,感興趣的小伙伴們可以看看。

2016-07-26 16:29:36 0

0 PCB手動布線規則,感興趣的小伙伴們可以看看。

2016-08-16 18:29:59 0

0 DDR2_DDR3_SDRAM,PCB布線規則指導

2017-10-31 10:06:48 78

78 規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有

2017-11-25 07:43:00 7508

7508

規則一 規則 圖1 如圖1所示,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或者只屏蔽了部分,都會造成EMI泄漏。建議屏蔽線,每1000mil,打孔接地。 規則二、高速信號的走線閉環

2018-09-12 09:10:01 1157

1157 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 規則一:高速信號走線屏蔽規則 如上圖所示: 在高速的PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線,每1000mil,打孔

2020-02-14 11:53:40 11779

11779 由慢速信號還是快速信號,您的走線都需要遵循一些PCB布線規則,以確保您的電路板按預期工作。 開始在組件之間路由信號之前,您需要查看您的設計規則,并將其調整為符合信號標準。在開始圍繞PCB布線信號之前,需要設置以下重要的PCB布線規

2020-12-17 13:14:38 2701

2701 電子發燒友網為你提供圖解在高速的PCB設計中的走線規則資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:43:14 23

23 電子發燒友網為你提供詳解PCB高速信號電路設計中的布線規則資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-25 08:47:42 36

36 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的 EMI 問題,也來越受

到電子工程師的關注。

高速 PCB 設計的成功,對 EMI 的貢獻越來越受到重視,幾乎 60%的 EMI 問題可

以通過高速 PCB 來控制解決

2022-04-22 11:54:57 0

0 小編給大家分享7條實用的布線規則,收藏就是賺到啦。另外推薦一個超級好用的工具,減少我很多工作量哦!

2022-10-20 10:07:46 765

765

「實用干貨」7條實用的PCB布線規則,可收藏

2023-02-01 08:36:57 891

891 解決。 高速信號走線屏蔽規則 如上圖所示:在高速的PCB設計中,時鐘等關鍵的高速信號線,則需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線每1000mil打孔接地 。 高速信號的走線閉環規則 由于PCB板的密度越來越高,很多PCB

2023-05-22 09:15:58 834

834

今天給大家分享的是:高速信號、14條高速信號布局設計規則。

2023-09-07 09:19:57 454

454

硬核分享,使用高速轉換器時應遵循哪些重要的PCB布線規則?

2023-10-17 16:34:09 263

263 7條實用的PCB布線規則

2022-09-30 11:48:00 38

38 PCI-Express總線接口的布線規則

2023-11-29 15:49:58 492

492

電子發燒友App

電子發燒友App

評論