????混合信號(hào)SoC設(shè)計(jì),往往包括模擬、射頻、數(shù)字、定制數(shù)字和來自不同IP提供商IP。為實(shí)現(xiàn)完整意義上芯片級(jí)驗(yàn)證,需要采用SPICE、射頻仿真器、混合信號(hào)仿真器和Fast?SPICE等多重仿真器組合。設(shè)計(jì)者在不同設(shè)計(jì)階段往往需要采用來自不同公司仿真器。

????為降低用戶在設(shè)計(jì)工具方面使用難度和工具轉(zhuǎn)換風(fēng)險(xiǎn),Cadence推出Multi-Mode仿真解決方案,通過使用統(tǒng)一用戶接口、器件模型、語法格式、內(nèi)部方程式,極大地提高了數(shù)據(jù)兼容性和仿真結(jié)果可信度。Multi-Mode技術(shù)使設(shè)計(jì)者可在統(tǒng)一設(shè)計(jì)環(huán)境中,在模擬、射頻、混合信號(hào)、芯片級(jí)電路驗(yàn)證不同設(shè)計(jì)階段,自由切換Spectre、SpectreRF、AMS?Designer和Ultrasim等仿真器。模擬/混合信號(hào)電路仿真面臨挑戰(zhàn)主要有急劇增長設(shè)計(jì)復(fù)雜度,對(duì)仿真器容量和速度提出更高要求;激烈市場競爭和不斷爬升流片費(fèi)用,使如何縮短設(shè)計(jì)周期、提高流片成功率成為芯片設(shè)計(jì)中主要問題之一;深亞微米小尺寸效應(yīng)影響變得更為顯著,如短/窄溝效應(yīng)對(duì)閾值電壓影響、亞閾值電流、體效應(yīng)導(dǎo)致襯底電流等;低信號(hào)擺幅設(shè)計(jì)中電路噪聲和交叉耦合效應(yīng)、低電源電壓下信號(hào)線和電源網(wǎng)格電壓降和電遷移問題等;對(duì)互連線延遲、信號(hào)串?dāng)_、襯底效應(yīng)、接地噪音等物理效應(yīng)考慮,依賴于精確后仿真結(jié)果。?

????上述問題解決越來越依賴于全芯片晶體管級(jí)電路仿真及后仿真,而傳統(tǒng)晶體管級(jí)SPICE仿真器由于容量和速度限制,通常只適用于模塊級(jí)電路設(shè)計(jì),因此Fast?SPICE技術(shù)引入不可避免。SPICE技術(shù)即Fast?SPICE仿真器采用電路分塊、多速率、簡化模型等加速仿真技術(shù)。Fast?SPICE把相關(guān)電路模塊放在一起,將大矩陣分成許多小矩陣,減小計(jì)算量。此外,事件驅(qū)動(dòng)技術(shù)可忽略不活動(dòng)電路,進(jìn)一步降低運(yùn)算量。電路分塊另一個(gè)優(yōu)點(diǎn)是可采用多速率仿真。各個(gè)電路模塊往往存在不同工作頻率,因此仿真中不同電路塊可以采用不同仿真步長。這樣,既可以保證高頻率電路得到精確結(jié)果,又讓低頻率模塊避免重復(fù)計(jì)算,降低CPU負(fù)荷。?

????簡化模型技術(shù)是Fast?SPICE加速另一項(xiàng)重要技術(shù)。在傳統(tǒng)電路仿真中,MOSFET或BJT需要一組復(fù)雜公式進(jìn)行計(jì)算,常常耗費(fèi)大量CPU時(shí)間。而Fast?SPICE在仿真開始時(shí)先產(chǎn)生模型表格,然后進(jìn)行查表,從而節(jié)省大量時(shí)間。Fast?SPICE通過多層次簡化模型,可以滿足不同精度和速度要求。

????Virtuoso?UltraSim?Simulator作為新一代Fast?SPICE仿真器,引入了分層化同型仿真、動(dòng)態(tài)電路分割等技術(shù),對(duì)電路中相同子模塊只需計(jì)算其中一個(gè),避免重復(fù)計(jì)算,從而進(jìn)一步提升仿真容量和速度;提供與傳統(tǒng)SPICE完全兼容以及和SPICE類似仿真精度;簡潔選項(xiàng)使設(shè)計(jì)者可以方便地定制電路仿真;改進(jìn)RC減小技術(shù)使之可以進(jìn)行精確、快速后仿真。此外,UltraSim已完全集成于Cadence標(biāo)準(zhǔn)模擬設(shè)計(jì)流程之中。這些優(yōu)點(diǎn)使UltraSim成為目前業(yè)內(nèi)應(yīng)用最廣泛Fast?SPICE工具之一。

混合電路加速仿真

- 混合電路(13669)

相關(guān)推薦

如何通過仿真有效提高數(shù)模混合設(shè)計(jì)性

如何通過仿真有效提高數(shù)模混合設(shè)計(jì)性

一 、數(shù)模混合設(shè)計(jì)的難點(diǎn) 二、提高數(shù)模混合電路性能的關(guān)鍵 三、仿真工具在數(shù)模混合設(shè)計(jì)中的應(yīng)用 四、小結(jié) 五、混合信號(hào)PC

2009-08-01 19:28:17 1359

1359

1359

1359

數(shù)模混合電路設(shè)計(jì)的難點(diǎn)

數(shù)模混合電路設(shè)計(jì)的難點(diǎn)

數(shù)模混合電路的設(shè)計(jì),一直是困擾硬件電路設(shè)計(jì)師提高性能的瓶頸。眾所

2010-10-05 09:46:48 2513

2513

2513

2513博通推出VXLAN云端網(wǎng)路專用的伺服器虛擬網(wǎng)路加速技術(shù)

博通(Broadcom)公司推出NetXtreme II 伺服器虛擬網(wǎng)路加速技術(shù)(NV),用以佈建VXLAN環(huán)境,并可提升55%以上的伺服器效能。搭配使用Smart NV技術(shù)的StrataXGS Trident II系列交換器平臺(tái),博通為VX

2012-09-07 13:40:39 1159

1159

1159

1159基于FPGA的軟硬件協(xié)同仿真加速技術(shù)

在系統(tǒng)設(shè)計(jì)中,硬件復(fù)雜電路設(shè)計(jì)的調(diào)試與仿真工作對(duì)于設(shè)計(jì)者來說十分困難。為了降低仿真復(fù)雜度,加快仿真速度,本文提出利用FPGA加速的思想,實(shí)現(xiàn)軟硬件協(xié)同加速仿真。經(jīng)過實(shí)驗(yàn),相對(duì)于純軟件仿真,利用軟硬件協(xié)同加速仿真技術(shù),仿真速度提高近30倍,大大縮短了仿真時(shí)間。##仿真實(shí)例及結(jié)論

2014-03-25 11:52:52 4722

4722

4722

47220RCAD電路混合電路仿真教程

0RCAD電路混合電路仿真教程:以Capture部分為例,就直接從V7.11跳到V9;而其它部分也跳升到V9,所以V9版本可說是orCAD的一個(gè)新指針:OrCAD for Windows包括電路

2008-07-30 22:28:20

混合電路和模塊技術(shù)簡史

作者 / Steve Munns ADI 公司軍用航空市場經(jīng)理50 多年來,混合電路和模塊技術(shù)一直在發(fā)展,現(xiàn)在,模塊采用了 COTS(商用現(xiàn)成有售) 形式,為縮短設(shè)計(jì)周期、減輕過時(shí)淘汰問題以及應(yīng)對(duì)

2018-10-23 14:34:07

混合信號(hào)電路板的設(shè)計(jì)準(zhǔn)則

電平向高電平(狀態(tài))跳變時(shí),如果數(shù)字信號(hào)跳變的速度足夠快,則將產(chǎn)生過沖和回鈴反射現(xiàn)象。對(duì)于現(xiàn)代板極設(shè)計(jì)來說,混合信號(hào)PCB的概念比較模糊,這是因?yàn)榧词乖诩兇獾摹皵?shù)字”器件中,仍然存在仿真電路和仿真效應(yīng)

2015-01-14 15:06:08

混合信號(hào)PCB的分區(qū)設(shè)計(jì)

直接影響到電路性能和電磁兼容性能。本文介紹的地和電源的分區(qū)設(shè)計(jì)能優(yōu)化混合信號(hào)電路的性能。 如何降低數(shù)字信號(hào)和仿真信號(hào)間的相互干擾呢?在設(shè)計(jì)之前必須了解電磁兼容 (EMC) 的兩個(gè)基本原則︰第一個(gè)原則

2012-10-17 15:49:38

混合信號(hào)示波器如何加速復(fù)雜系統(tǒng)測試?

的測試手段和工具,來完成比以往更加復(fù)雜的測試任務(wù)。為了解系統(tǒng)的整體工作特性,工程師只有同時(shí)測量模擬、數(shù)字信號(hào),甚至包括總線信號(hào),才能了解系統(tǒng)故障的原因和掌握信號(hào)和指令的時(shí)序和邏輯關(guān)系。如何加速復(fù)雜系統(tǒng)測試?也只有混合信號(hào)示波器能做到了。

2019-08-09 06:48:24

混合信號(hào)示波器是如何加速復(fù)雜系統(tǒng)測試的?

請(qǐng)教各位,混合信號(hào)示波器是如何加速復(fù)雜系統(tǒng)測試的?

2021-05-10 06:29:36

混合電網(wǎng)仿真是什么

這是含風(fēng)能,光伏PV,儲(chǔ)能,考慮了居民用電,居民用電價(jià)格,考慮需求側(cè)響應(yīng),混合電網(wǎng)仿真,使用可再生能源實(shí)現(xiàn)提高能源效率,以下是風(fēng)機(jī)的模型如下圖:我們的成本函數(shù)可以定義如下:我們計(jì)算出風(fēng)力渦輪機(jī)可以在

2021-07-12 06:20:39

混合集成電路EMC設(shè)計(jì)產(chǎn)生的原因闡述

本文詳細(xì)闡述了混合集成電路電磁干擾產(chǎn)生的原因,并結(jié)合混合集成電路的工藝特點(diǎn)提出了系統(tǒng)電磁兼容設(shè)計(jì)中應(yīng)注意的問題和采取的具體措施,為提高混合集成電路的電磁兼容性奠定了基礎(chǔ)。

2019-07-25 07:28:47

混合集成電路電磁干擾產(chǎn)生的原因是什么

本文詳細(xì)闡述了混合集成電路電磁干擾產(chǎn)生的原因,并結(jié)合混合集成電路的工藝特點(diǎn)提出了系統(tǒng)電磁兼容設(shè)計(jì)中應(yīng)注意的問題和采取的具體措施,為提高混合集成電路的電磁兼容性奠定了基礎(chǔ)。

2021-04-26 06:16:00

Altium Designer的混合電路信號(hào)仿真工具介紹

Altium Designer的混合電路信號(hào)仿真工具,在電路原理圖設(shè)計(jì)階段實(shí)現(xiàn)對(duì)數(shù)模混合信號(hào)電路的功能設(shè)計(jì)仿真,配合簡單易用的參數(shù)配置窗口,完成基于時(shí)序、離散度、信噪比等多種數(shù)據(jù)的分析。Altium

2019-07-19 07:52:07

LabVIEW開發(fā)多速率實(shí)時(shí)混合仿真

LabVIEW開發(fā)多速率實(shí)時(shí)混合仿真

混合仿真是一種子結(jié)構(gòu)技術(shù),通過將數(shù)值建模的優(yōu)點(diǎn)與實(shí)驗(yàn)測試的優(yōu)點(diǎn)相結(jié)合來模擬感興趣的結(jié)構(gòu)。模擬結(jié)構(gòu)的其余部分特別令人感興趣,因此可以進(jìn)行物理復(fù)制,以揭示粘彈性

2023-11-06 19:34:14

MOSFET的電路加負(fù)壓驅(qū)動(dòng)

我看一個(gè)MOSFET驅(qū)動(dòng)電路的設(shè)計(jì)與仿真PPT里面說,Vg中存在負(fù)電壓,一定程度上加長了驅(qū)動(dòng)延遲時(shí)間,要消除負(fù)壓,然后又看了一個(gè)技術(shù)手冊(cè),專門介紹了一種負(fù)壓驅(qū)動(dòng)電路。如下圖所示,所示可以負(fù)壓驅(qū)動(dòng)可以加速關(guān)斷速度~然后我就懵了,想問下大家,什么時(shí)候要用負(fù)壓驅(qū)動(dòng)?還有負(fù)壓驅(qū)動(dòng)能加速關(guān)斷嗎?

2019-01-23 15:57:14

PSPICE仿真時(shí)如何加速,縮短仿真時(shí)間?!

最近公司在做一個(gè)開關(guān)電源的仿真,用的是暫態(tài)分析,但是時(shí)間總是長不了,幾十毫秒的波形也要運(yùn)行個(gè)20分鐘,我想看到全部的過程,但是要運(yùn)行幾十個(gè)小時(shí),有沒有什么辦法可以加速仿真,縮短運(yùn)行時(shí)間的?求助高手!

2012-07-26 13:39:52

nanosim和vcs混合仿真的過程是怎樣的?

nanosim和vcs為什么可以聯(lián)合起來進(jìn)行數(shù)字模擬混合仿真?nanosim和vcs混合仿真的過程是怎樣的?

2021-06-18 08:28:30

兩相四線混合式步進(jìn)電機(jī)用雙H橋驅(qū)動(dòng)電路之Multisim仿真及優(yōu)化 相關(guān)資料推薦

1. 仿真圖2. 驅(qū)動(dòng)電路原理解析2.1 兩相四線混合式步進(jìn)電機(jī)驅(qū)動(dòng)原理首先給出兩相四線混合式步進(jìn)電機(jī)的整步驅(qū)動(dòng)順序圖。可以看出,兩相驅(qū)動(dòng)電壓的相位差為90°,因此,第一節(jié)中驅(qū)動(dòng)電路的兩個(gè)脈沖電壓源

2021-07-08 07:24:12

二相混合式步進(jìn)電機(jī)開環(huán)細(xì)分控制simulink建模仿真含模型文件

控制(或SVPWM控制)使用滯環(huán)電流pwm控制,因此需要在電流反饋回路加入低通濾波?也可以使用SVPWM控制,在我的另一篇文章中有提(二相混合式步進(jìn)電機(jī)閉環(huán)矢量控制simulink仿真(含仿真文件

2020-06-14 22:33:19

什么仿真軟件可以做電路的老化仿真實(shí)驗(yàn)?

請(qǐng)問大家,有什么仿真軟件可以做電路元器件的加速老化仿真實(shí)驗(yàn),PSpice可以嗎?

2018-06-07 09:52:58

以DAC為例,介紹AMS-Design數(shù)模混合電路仿真的方法是什么?

以DAC為例,介紹AMS-Design數(shù)模混合電路仿真的方法是什么?混合電路仿真有哪幾種方法?分別是什么?SpectreVerilog仿真器和AMS-Design仿真器有

2021-06-22 07:00:26

基于電流測試的混合電路故障診斷

于開路故障,采用在開路點(diǎn)接入10 MΩ點(diǎn)電阻來建立故障模型。 3.1 IDDQ在混合電路故障檢測中的應(yīng)用 在PSPICE中對(duì)各個(gè)故障模型進(jìn)行仿真,可以很容易得出靜態(tài)電流值。IDDQ對(duì)于混合電路的橋

2018-11-05 15:50:13

我的數(shù)模混合設(shè)計(jì)難點(diǎn)經(jīng)驗(yàn)

或者并聯(lián)電容,用來提供完整回流路徑。無論哪種方法,似乎都有一定道理,而且都有成功的先例,然而所有這些分割方案的有效性以及可能存在的問題,一直沒有檢驗(yàn)的標(biāo)準(zhǔn)。 數(shù)模混合電路的仿真,還存在模型的問題。業(yè)界

2011-12-02 15:44:34

數(shù)模混合仿真詳細(xì)解說

最近研究數(shù)字電路和模擬電路混合仿真問題,cadence軟件的確很強(qiáng)大。附件傳來我的心得及設(shè)計(jì)方法,供大家參考。有不對(duì)的地方請(qǐng)盡管提出。

2013-04-08 13:51:06

數(shù)模混合電路設(shè)計(jì)的難點(diǎn)

的有效性以及可能存在的問題,一直沒有檢驗(yàn)的標(biāo)準(zhǔn)。數(shù)模混合電路的仿真,還存在模型的問題。業(yè)界普遍接受的模擬電路仿真模型還是 SPICE模型,數(shù)字電路信號(hào)完整性分析使用IBIS模型。多家EDA公司的仿真

2016-09-18 23:48:10

通過仿真有效提高數(shù)模混合設(shè)計(jì)性

通過仿真有效提高數(shù)模混合設(shè)計(jì)性目錄: 前言 一 、數(shù)模混合設(shè)計(jì)的難點(diǎn) 二、提高數(shù)模混合電路性能的關(guān)鍵 三、仿真工具在數(shù)模混合設(shè)計(jì)中的應(yīng)用 四、小結(jié) 五、混合信號(hào)PCB設(shè)計(jì)基礎(chǔ)問答前言: 數(shù)模混合電路

2008-07-07 17:30:47

orcad全能混合電路仿真

0RCAD全能混合電路仿真:第一部分 0rCAD環(huán)境與Capture第l章 OrCAD PSpice簡介1—1 SPICE的起源1—2 OrCAD PSpi

2008-07-30 22:20:15 0

0

0

0如何通過仿真有效提高數(shù)模混合設(shè)計(jì)性

如何通過仿真有效提高數(shù)模混合設(shè)計(jì)性:一 、數(shù)模混合設(shè)計(jì)的難點(diǎn) 二、提高數(shù)模混合電路性能的關(guān)鍵 三、仿真工具在數(shù)模混合設(shè)計(jì)中的應(yīng)用 四、小結(jié) 五、混合信號(hào)PCB設(shè)計(jì)基礎(chǔ)問

2009-09-16 12:31:33 12

12

12

12電子管集成電路混合功放制作詳解

電子管-集成電路混合功放制作詳解:本文介紹一款電子管集成電路混合功放的制作。該功放前級(jí)使用由6N3組成的SRPP電路加上一級(jí)6N1陰極輸出器,既具有寬的頻率響應(yīng),又有較強(qiáng)的輸

2009-12-11 08:30:59 219

219

219

219厚膜混合集成電容式加速度計(jì)

設(shè)計(jì)了電容式加速度計(jì)的信號(hào)檢測電路,與電容式加速度計(jì)敏感單元進(jìn)行聯(lián)調(diào)和測試,并進(jìn)行了標(biāo)定。為減小體積,提高電容式加速度計(jì)的檢測精度,采用厚膜混合集成工藝,將檢測電路和

2010-02-21 13:59:43 17

17

17

17數(shù)模混合仿真在以太網(wǎng)芯片設(shè)計(jì)中的應(yīng)用

數(shù)模混合仿真在超大規(guī)模集成電路驗(yàn)證中具有十分重要的作用。本文介紹了數(shù)模混合仿真的實(shí)現(xiàn)原理和仿真方法。在集成以太網(wǎng)控制芯片設(shè)計(jì)中,采用這種混合仿真方法,進(jìn)行了整體功

2010-02-24 15:42:32 10

10

10

10Ansoft仿真器

Ansoft仿真器

Ansoft用于射頻、模擬和混合信號(hào)電路設(shè)計(jì)的新一代仿真器Nexxim是Ansoft新一代電路仿真工具,能夠快速精確地仿真復(fù)雜和大規(guī)模的模擬和混合信號(hào)電路

2010-04-06 13:59:05 93

93

93

93混合厚膜電路

在現(xiàn)代電子技術(shù)領(lǐng)域內(nèi),電路設(shè)計(jì)師經(jīng)常要接觸到混合微電路。混合微電路一般可分為多片混合電路(MCU)、混合薄膜電路(Hybrid Thin Film Microcircuits)、混合厚膜電路(Hybrid Thick Film M

2010-04-23 08:19:01 22

22

22

22基于PSPICE的電路仿真分析與設(shè)計(jì)

摘要:通過模擬電路、數(shù)字電路、數(shù)字模擬混合電路等三個(gè)具體的仿真分析實(shí)例,闡述了PSPICE在電路的仿真分析與設(shè)計(jì)中的應(yīng)用,電路仿真分析結(jié)果完全符合設(shè)計(jì)的理論分析值的要

2010-04-27 13:19:24 99

99

99

99[組圖]模擬/數(shù)模混合電路加速仿真技術(shù)

如今,涉及模擬和數(shù)模混合電路的SoC設(shè)計(jì)日益增多。由于電路規(guī)模增大和復(fù)雜度提

2006-04-16 18:20:16 1226

1226

1226

1226PROSPICE:Spice 3F5混合型仿真器

PROSPICE:Spice 3F5 混合型仿真器PROSPICE 是結(jié)合ISIS 原理圖設(shè)計(jì)環(huán)境使用的混合型電路仿真器。基于工業(yè)標(biāo)準(zhǔn)SPICE3F5 的模擬內(nèi)核,加上混合型仿真的擴(kuò)展以及交互電路動(dòng)

2009-04-21 11:16:38 2883

2883

2883

2883利用ADMS平臺(tái)加速混合信號(hào)集成電路設(shè)計(jì)

利用ADMS平臺(tái)加速混合信號(hào)集成電路設(shè)計(jì)

越來越多的設(shè)計(jì)正向混合信號(hào)發(fā)展,IBS公司預(yù)測顯示,到2006年所有集成電路設(shè)計(jì)中有73%將為混合信號(hào)設(shè)計(jì)。目前混合信號(hào)技術(shù)

2009-12-26 14:39:03 853

853

853

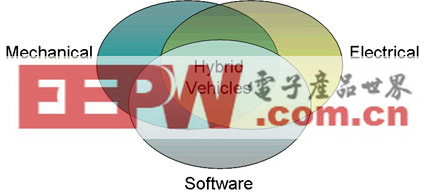

853基于仿真的設(shè)計(jì)集成提高混合動(dòng)力車輛的可靠性

基于仿真的設(shè)計(jì)集成提高混合動(dòng)力車輛的可靠性

由于存在集成要求,混合動(dòng)力汽車成為一種設(shè)計(jì)、制造和維護(hù)都最為復(fù)雜的系統(tǒng),魯棒的設(shè)計(jì)方法為設(shè)計(jì)可靠的混合

2010-01-13 11:29:54 673

673

673

673

混合集成電路,混合集成電路是什么意思

混合集成電路,混合集成電路是什么意思

由半導(dǎo)體集成工藝與薄(厚)膜工藝結(jié)合而制成的集成電路。混合集成電路是在基片上用成膜方法制作厚

2010-03-20 16:19:02 4061

4061

4061

4061混合集成電路,什么是混合集成電路

混合集成電路,什么是混合集成電路

由半導(dǎo)體集成工藝與薄(厚)膜工藝結(jié)合而制成的集成電路。混合集成電路是在基片上用成膜方法制作厚膜或

2010-04-02 17:25:45 949

949

949

949protel設(shè)計(jì)之原理圖仿真

protel設(shè)計(jì)之原理圖仿真

Protel99 SE的混合信號(hào)電路仿真引擎現(xiàn)在與3F5完全兼容,支持所有標(biāo)準(zhǔn)的SPICE模型。電路仿

2010-04-26 15:18:48 5469

5469

5469

5469數(shù)模混合仿真基本流程

1、 輸入命令which verilog.vmx,參看仿真所需的verilog.vmx文件是否存在, which icfb,查看所需的系統(tǒng)文件是否存在; 2、 在需要進(jìn)行仿真的文件目錄下啟動(dòng)icfb

2011-02-15 10:57:55 62

62

62

62TMS320VC5416的多路加速采集系統(tǒng)設(shè)計(jì)方法

摘要:本文介紹了一種基于TMS320VC5416的多路加速采集與處理系統(tǒng)的設(shè)計(jì)方法。該系統(tǒng)采用AD73360作為數(shù)據(jù)采集前端,通過DSP的MCBSP和AD73360級(jí)聯(lián),可實(shí)現(xiàn)多路模擬加速信號(hào)的實(shí)時(shí)采集和處理。 關(guān)鍵詞:TMS320VC5416;AD73360;加速度;數(shù)據(jù)處理

2011-03-02 00:03:32 107

107

107

107模擬/混合信號(hào)仿真器

Harmony單核模擬/混合信號(hào)仿真器實(shí)時(shí)地動(dòng)態(tài)連接SmartSpice 電路仿真器和SILOS-XVerilog仿真器的性能。Harmony集精度、性能、產(chǎn)量和靈活性于一身,仿真以Verilog,SPICE,Verilog-A和Verilog-AMS形式的電

2011-03-31 13:09:54 73

73

73

73用于射頻、模擬和混合信號(hào)電路設(shè)計(jì)的新一代仿

Nexxim是Ansoft新一代電路仿真工具,能夠快速精確地仿真復(fù)雜和大規(guī)模的模擬和混合信號(hào)電路。它不僅提供了敏感的模擬和無線前端電路晶體管級(jí)的仿真精度,還具有針對(duì)現(xiàn)代復(fù)雜的混合

2011-04-05 11:18:04 28

28

28

28混合信號(hào)仿真技術(shù)綜述

隨著集成電路加工工藝技術(shù)的繼續(xù)發(fā)展,在單個(gè)芯片上實(shí)現(xiàn)整個(gè)復(fù)雜電子系統(tǒng)已成為可能。這樣的系統(tǒng)通常包括數(shù)字信號(hào)和模擬信號(hào)處理。在設(shè)計(jì)早期仿真這樣的IC設(shè)計(jì)來發(fā)現(xiàn)錯(cuò)誤已顯

2011-04-05 13:58:07 45

45

45

45超高速數(shù)模混合集成電路中時(shí)鐘分布電路的設(shè)計(jì)

本文介紹了采用 ADS 軟件設(shè)計(jì)超高速數(shù)模混合集成電路中時(shí)鐘分布電路的方法。利用ADS 瞬態(tài)仿真完成電路的原理圖仿真,并初步設(shè)計(jì)完成版圖,然后利用Momentum 對(duì)版圖中的時(shí)鐘分布電路

2011-07-05 15:41:05 74

74

74

74城域混合交通流仿真系統(tǒng)的人機(jī)界面設(shè)計(jì)實(shí)現(xiàn)

交通仿真軟件在 智能交通 研究領(lǐng)域的重要性日益凸現(xiàn), 針對(duì)國內(nèi)的混合交通狀況與城市化趨勢, 開發(fā)了城域混合交通流仿真與分析系統(tǒng)。作為面向?qū)ο蟮奈⒂^混合交通流仿真軟件, 其獨(dú)

2011-07-26 15:33:33 18

18

18

18LSI推出新一代Axxia網(wǎng)路加速卡AXP3420

LSI公司宣佈推出專為加速企業(yè)和云端資料中心關(guān)鍵網(wǎng)路任務(wù)的Axxia網(wǎng)路加速卡AXP3420。具備標(biāo)準(zhǔn)PCIe插槽的AXP3420可加速應(yīng)用程式識(shí)別和安全等網(wǎng)路功能,同時(shí)可提升伺服器和網(wǎng)路設(shè)備的

2012-05-08 11:23:41 942

942

942

942Mentor Graphics硬件加速仿真服務(wù)使用Veloce 硬件加速仿真平臺(tái)加速驗(yàn)證

俄勒岡州威爾遜維爾,2016 年 4 月 20 日 — Mentor Graphics公司(納斯達(dá)克代碼:MENT)今日宣布,Mentor? 硬件加速仿真服務(wù)采用具有專業(yè)服務(wù)和 IP 的 Veloce? 硬件加速仿真平臺(tái) ,借此加速仿真驗(yàn)證并降低與片上系統(tǒng) (SoC) 設(shè)計(jì)相關(guān)的風(fēng)險(xiǎn)。

2016-04-20 11:22:08 2307

2307

2307

2307如何通過仿真有效提高數(shù)模混合設(shè)計(jì)性(上)_硬件工程師必讀攻略

本文通過Ansoft公司的“AD-Mix Signal Noise Design Suites” 數(shù)模混合噪聲仿真設(shè)計(jì)軟件的對(duì)數(shù)模混合設(shè)計(jì)PCB的仿真,探索分析數(shù)模混合電路的噪聲干擾和優(yōu)化設(shè)計(jì)的途徑,以達(dá)到改善系統(tǒng)性能目的。

2016-06-23 17:15:59 0

0

0

0System generator DSP48E1 (2):四路加法器

環(huán)境 ?Matlab 2014 a ?Vivado 2014.4 ?System generator 2014.4 實(shí)現(xiàn)步驟 1、模型搭建與仿真 在simulink環(huán)境下工程搭建如下 圖3 四路加

2017-02-08 01:10:08 473

473

473

473

集成電路加工光致抗蝕劑概念與光刻技術(shù)的介紹

本文主要介紹集成電路加工-光刻技術(shù)與光刻膠。集成電路加工主要設(shè)備和材料:光刻設(shè)備,半導(dǎo)體材料:單晶硅等,掩膜,化學(xué)品:光刻膠(光致抗蝕劑),超高純?cè)噭庋b材料及光刻機(jī)的介紹

2017-09-29 16:59:02 18

18

18

18Veloce仿真環(huán)境下的SoC端到端硬件加速器功能驗(yàn)證

很多人認(rèn)為硬件加速器無非是一種速度更快的仿真器而已。毫無疑問,由于硬件加速器使用物理硬件進(jìn)行仿真,使用硬件加速器驗(yàn)證復(fù)雜的集成電路和大型片上系統(tǒng)(SoC)能比軟件仿真器快若干數(shù)量級(jí)。與仿真用通用計(jì)算機(jī)相比,仿真用單一功能計(jì)算機(jī)能提供更高容量、更高效的系統(tǒng)。

2018-03-28 14:50:00 3155

3155

3155

3155

protel電路仿真的資料總結(jié)

l Protel Advanced SIM99是一個(gè)能力強(qiáng)大的數(shù)/模混合信號(hào)電路仿真器,能提供連續(xù)的模擬信號(hào)和離散的數(shù)字信號(hào)仿真。

2019-11-13 11:49:00 0

0

0

0問答精選:5G不同頻段中電路材料的選型和電路加工帶米的影響

由羅杰斯公司先進(jìn)互聯(lián)解決方案事業(yè)部舉辦的題為5G不同頻段中電路材料的選型和電路加工帶米的影響“的在線技術(shù)講座于2018年9月18日上午十點(diǎn)在微波射頻網(wǎng)成功舉行。

2020-07-15 10:25:00 1

1

1

1二五混合進(jìn)制電路的仿真電路圖免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是二五混合進(jìn)制電路的仿真電路圖免費(fèi)下載

2020-07-17 16:31:24 17

17

17

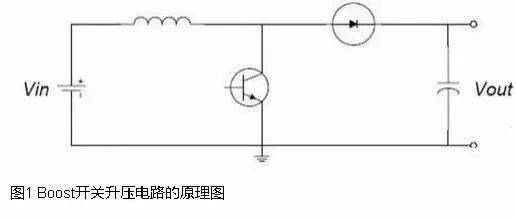

17怎么樣才能給Boost電路加保護(hù)電路

converter(或者叫step-up converter),是一種常見的開關(guān)直流升壓電路,它可以使輸出電壓比輸入電壓高。下面主要從基本原理、boost電路參數(shù)設(shè)計(jì)、如何給Boost電路加保護(hù)電路三個(gè)方面來描述。

2020-12-20 10:48:19 5063

5063

5063

5063

如何給Boost電路加保護(hù)電路?資料下載

電子發(fā)燒友網(wǎng)為你提供如何給Boost電路加保護(hù)電路?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:54:20 33

33

33

33使用Vivado仿真器進(jìn)行混合語言仿真的一些要點(diǎn)

Vivado 仿真器支持混合語言項(xiàng)目文件及混合語言仿真。這有助于您在 VHDL 設(shè)計(jì)中包含 Verilog 模塊,反過來也是一樣。 本文主要介紹使用 Vivado 仿真器進(jìn)行混合語言仿真的一些要點(diǎn)

2021-10-28 16:24:49 2774

2774

2774

2774Vivado仿真器進(jìn)行混合語言仿真的一些要點(diǎn)

本文主要介紹使用 Vivado 仿真器進(jìn)行混合語言仿真的一些要點(diǎn)。

2022-08-01 09:25:56 1007

1007

1007

1007電路仿真工具通常分為幾大類

按照仿真對(duì)象劃分,電路仿真工具通常分為三大類:晶體管級(jí)的模擬電路仿真工具、門級(jí)和RTL級(jí)的數(shù)字電路仿真工具、模數(shù)混合電路仿真工具。

2022-08-24 10:09:28 3122

3122

3122

3122通過仿真有效提高數(shù)模混合設(shè)計(jì)性能——硬件工程師必讀攻略

Suites” 數(shù)模混合噪聲仿真設(shè)計(jì)軟件對(duì)數(shù)模混合設(shè)計(jì)PCB進(jìn)行仿真,探索分析數(shù)模混合電路的噪聲干擾和優(yōu)化設(shè)計(jì)的途徑,以達(dá)到改善系統(tǒng)性能目的。

2023-01-03 13:53:50 1133

1133

1133

1133Altium Designer的電路仿真能力

Altium Designer的混合電路信號(hào)仿真工具,在電路原理圖設(shè)計(jì)階段實(shí)現(xiàn)對(duì)數(shù)模混合信號(hào)電路的功能設(shè)計(jì)仿真,配合簡單易用的參數(shù)配置窗口,完成基于時(shí)序、離散度、信噪比等多種數(shù)據(jù)的分析。

2023-02-17 14:11:29 1425

1425

1425

1425兩相四線混合式步進(jìn)電機(jī)用雙H橋驅(qū)動(dòng)電路之Multisim仿真及優(yōu)化

1. 仿真圖 2. 驅(qū)動(dòng)電路原理解析 2.1 兩相四線混合式步進(jìn)電機(jī)驅(qū)動(dòng)原理 首先給出兩相四線混合式步進(jìn)電機(jī)的整步驅(qū)動(dòng)順序圖。可以看出,兩相驅(qū)動(dòng)電壓的相位差為90°。 在驅(qū)動(dòng)電路中,一個(gè)H橋驅(qū)動(dòng)

2023-03-20 10:57:40 1

1

1

1如何加速PCIe仿真

不同而所有差異),而如果進(jìn)行網(wǎng)表級(jí)別的仿真一般需要1周以上的時(shí)間。此時(shí)加速PCIe仿真,提高效率是我們必須考慮的問題。常見的加速模式有如下三種。我們以VIP PCIe(Verification IP

2023-08-17 09:42:22 725

725

725

725

基于PDMS的靜態(tài)微流體混合器的制作與仿真

電子發(fā)燒友網(wǎng)站提供《基于PDMS的靜態(tài)微流體混合器的制作與仿真.pdf》資料免費(fèi)下載

2023-10-09 14:21:54 0

0

0

0 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論