01 布局

元器件布局的10條規(guī)則:

1. 遵照“先大后小,先難后易”的布置原則,即重要的單元電路、核心元器件應(yīng)當優(yōu)先布局.

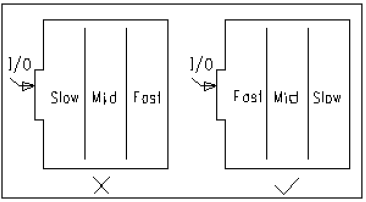

2. 布局中應(yīng)參考原理框圖,根據(jù)單板的主信號流向規(guī)律安排主要元器件.

3. 元器件的排列要便于調(diào)試和維修,亦即小元件周圍不能放置大元件、需調(diào)試的元、器件周圍要有足夠的空間。?

4. 相同結(jié)構(gòu)電路部分,盡可能采用“對稱式”標準布局;

5. 按照均勻分布、重心平衡、版面美觀的標準優(yōu)化布局;?

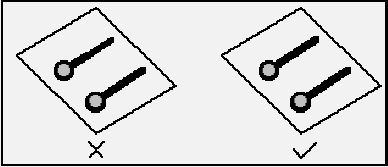

6. 同類型插裝元器件在X或Y方向上應(yīng)朝一個方向放置。同一種類型的有極性 分立元件也要力爭在X或Y方向上保持一致,便于生產(chǎn)和檢驗。?

7. 發(fā)熱元件要一般應(yīng)均勻分布,以利于單板和整機的散熱,除溫度檢測元件以外的溫度敏感器件應(yīng)遠離發(fā)熱量大的元器件。?

8. 布局應(yīng)盡量滿足以下要求:總的連線盡可能短,關(guān)鍵信號線最短;高電壓、大電流信號與小電流,低電壓的弱信號完全分開;模擬信號與數(shù)字信號分開;高頻信號與低頻信號分開;高頻元器件的間隔要充分。

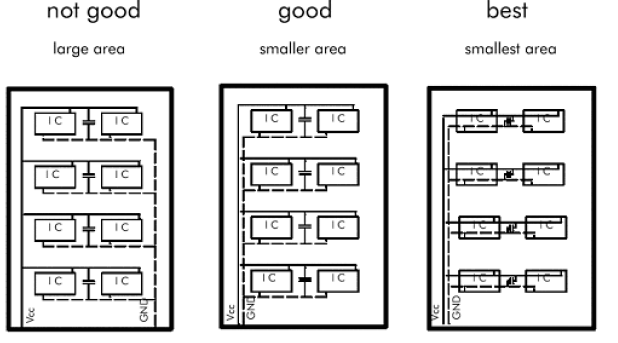

9、去偶電容的布局要盡量靠近IC的電源管腳,并使之與電源和地之間形成的回路最短。?

10、元件布局時,應(yīng)適當考慮使用同一種電源的器件盡量放在一起, 以便于將來的電源分隔。?

02 布線

(1)布線優(yōu)先次序

鍵信號線優(yōu)先:摸擬小信號、高速信號、時鐘信號和同步信號等關(guān)鍵信號優(yōu)先布線?

密度優(yōu)先原則:從單板上連接關(guān)系最復(fù)雜的器件著手布線。從單板上連線 最密集的區(qū)域開始布線?

注意點:

a、盡量為時鐘信號、高頻信號、敏感信號等關(guān)鍵信號提供專門的布線層,并保證其最小的回路面積。必要時應(yīng)采取手工優(yōu)先布線、屏蔽和加大安全間距等方法。保證信號質(zhì)量。?

b、電源層和地層之間的EMC環(huán)境較差,應(yīng)避免布置對干擾敏感的信號。

c、有阻抗控制要求的網(wǎng)絡(luò)應(yīng)盡量按線長線寬要求布線。?

(2)四種具體走線方式

1 、時鐘的布線:

時鐘線是對EMC 影響最大的因素之一。在時鐘線上應(yīng)少打過孔,盡量避免和其它信號線并行走線,且應(yīng)遠離一般信號線,避免對信號線的干擾。同時應(yīng)避開板上的電源部分,以防止電源和時鐘互相干擾。

如果板上有專門的時鐘發(fā)生芯片,其下方不可走線,應(yīng)在其下方鋪銅,必要時還可以對其專門割地。對于很多芯片都有參考的晶體振蕩器,這些晶振下方也不應(yīng)走線,要鋪銅隔離。

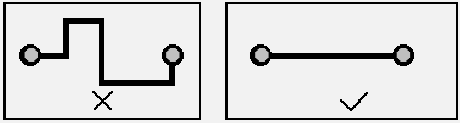

2、直角走線:

直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一,那么直角走線究竟會對信號傳輸產(chǎn)生多大的影響呢?從原理上說,直角走線會使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實不光是直角走線,頓角,銳角走線都可能會造成阻抗變化的情況。

直角走線的對信號的影響就是主要體現(xiàn)在三個方面:

一是拐角可以等效為傳輸線上的容性負載,減緩上升時間;

二是阻抗不連續(xù)會造成信號的反射;

三是直角尖端產(chǎn)生的EMI。

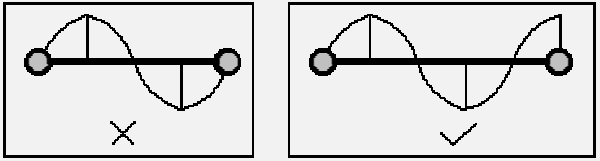

3、差分走線:

差分信號(Differential Signal)在高速電路設(shè)計中的應(yīng)用越來越廣泛,電路中最關(guān)鍵的信號往往都要采用差分結(jié)構(gòu)設(shè)計.定義:通俗地說,就是驅(qū)動端發(fā)送兩個等值、反相的信號,接收端通過比較這兩個電壓的差值來判斷邏輯狀態(tài)“0”還是“1”。而承載差分信號的那一對走線就稱為差分走線。

差分信號和普通的單端信號走線相比,最明顯的優(yōu)勢體現(xiàn)在以下三個方面:

a.抗干擾能力強,因為兩根差分走線之間的耦合很好,當外界存在噪聲干擾時,幾乎是同時被耦合到兩條線上,而接收端關(guān)心的只是兩信號的差值,所以外界的共模噪聲可以被完全抵消。

b.能有效抑制EMI,同樣的道理,由于兩根信號的極性相反,他們對外輻射的電磁場可以相互抵消,耦合的越緊密,泄放到外界的電磁能量越少。

c.時序定位精確,由于差分信號的開關(guān)變化是位于兩個信號的交點,而不像普通單端信號依靠高低兩個閾值電壓判斷,因而受工藝,溫度的影響小,能降低時序上的誤差,同時也更適合于低幅度信號的電路。目前流行的LVDS(low voltage differential signaling)就是指這種小振幅差分信號技術(shù)。

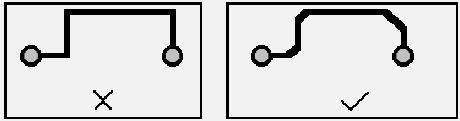

對于PCB工程師來說,最關(guān)注的還是如何確保在實際走線中能完全發(fā)揮差分走線的這些優(yōu)勢。也許只要是接觸過Layout的人都會了解差分走線的一般要求,那就是“等長、等距”。

等長是為了保證兩個差分信號時刻保持相反極性,減少共模分量;等距則主要是為了保證兩者差分阻抗一致,減少反射。“盡量靠近原則”有時候也是差分走線的要求之一。

4、蛇形線:

蛇形線是Layout中經(jīng)常使用的一類走線方式。其主要目的就是為了調(diào)節(jié)延時,滿足系統(tǒng)時序設(shè)計要求。

設(shè)計者首先要有這樣的認識:

蛇形線會破壞信號質(zhì)量,改變傳輸延時,布線時要盡量避免使用。但實際設(shè)計中,為了保證信號有足夠的保持時間,或者減小同組信號之間的時間偏移,往往不得不故意進行繞線。

注意點:

成對出現(xiàn)的差分信號線,一般平行走線,盡量少打過孔,必須打孔時,應(yīng)兩線一同打孔,以做到阻抗匹配。

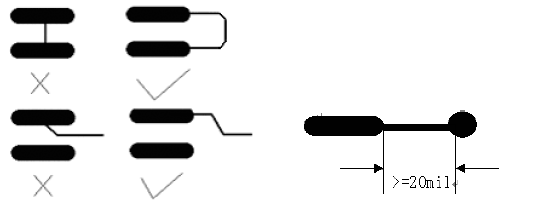

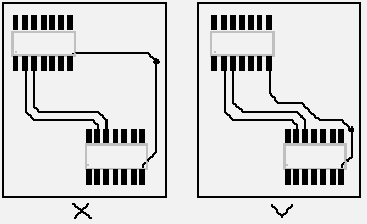

相同屬性的一組總線,應(yīng)盡量并排走線,做到盡量等長。從貼片焊盤引出的過孔盡量離焊盤遠些。

(3)布線常用規(guī)則

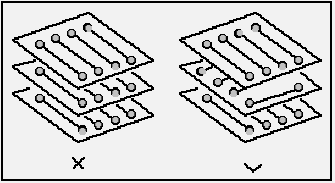

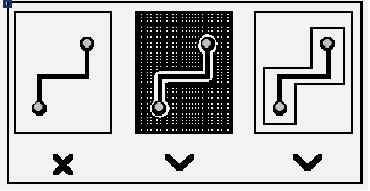

1、走線的方向控制規(guī)則:?

即相鄰層的走線方向成正交結(jié)構(gòu)。避免將不同的信號線在相鄰層走成同一方向,以減少不必要的層間竄擾;

當由于板結(jié)構(gòu)限制(如某些背板)難以避免出現(xiàn)該情況,特別是信號速率較高時,應(yīng)考慮用地平面隔離各布線層,用地信號線隔離各信號線。?

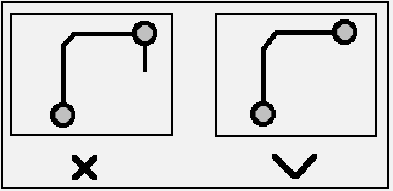

2、走線的開環(huán)檢查規(guī)則:

一般不允許出現(xiàn)一端浮空的布線(Dangling Line), 主要是為了避免產(chǎn)生"天線效應(yīng)",減少不必要的干擾輻射和接受,否則可能帶來不可預(yù)知的結(jié)果。?

3、阻抗匹配檢查規(guī)則:?

同一網(wǎng)絡(luò)的布線寬度應(yīng)保持一致,線寬的變化會造成線路特性阻抗的不均勻,當傳輸?shù)乃俣容^高時會產(chǎn)生反射,在設(shè)計中應(yīng)該盡量避免這種情況。

在某些條件下,如接插件引出線,BGA封裝的引出線類似的結(jié)構(gòu)時,可能無法避免線寬的變化,應(yīng)該盡量減少中間不一致部分的有效長度。

4、走線長度控制規(guī)則:?

即短線規(guī)則,在設(shè)計時應(yīng)該盡量讓布線長度盡量短,以減少由于走線過長帶來的干擾問題,特別是一些重要信號線,如時鐘線,務(wù)必將其振蕩器放在離器件很近的地方。對驅(qū)動多個器件的情況,應(yīng)根據(jù)具體情況決定采用何種網(wǎng)絡(luò)拓撲結(jié)構(gòu)。?

5、倒角規(guī)則:?

PCB設(shè)計中應(yīng)避免產(chǎn)生銳角和直角, 產(chǎn)生不必要的輻射,同時工藝性能也不好。

6、器件去藕規(guī)則:?

A. 在印制版上增加必要的去藕電容,濾除電源上的干擾信號,使電源信號穩(wěn)定。

在多層板中,對去藕電容的位置一般要求不太高,但對雙層板,去藕電容的布局及電源的布線方式將直接影響到整個系統(tǒng)的穩(wěn)定性,有時甚至關(guān)系到設(shè)計的成敗。?

B. 在雙層板設(shè)計中,一般應(yīng)該使電流先經(jīng)過濾波電容濾波再供器件使用。?

C. 在高速電路設(shè)計中,能否正確地使用去藕電容,關(guān)系到整個板的穩(wěn)定性。?

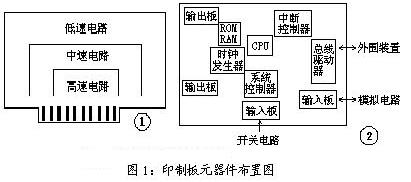

7、器件布局分區(qū)/分層規(guī)則:?

A. 主要是為了防止不同工作頻率的模塊之間的互相干擾,同時盡量縮短高頻部分的布線長度。

B. 對混合電路,也有將模擬與數(shù)字電路分別布置在印制板的兩面,分別使用不同的層布線,中間用地層隔離的方式。?

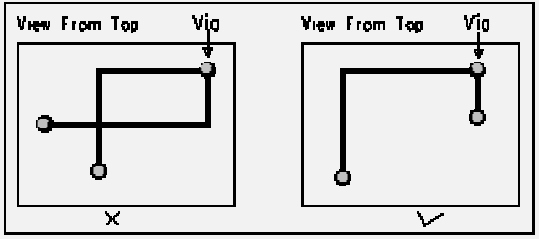

8、地線回路規(guī)則:

環(huán)路最小規(guī)則,即信號線與其回路構(gòu)成的環(huán)面積要盡可能小,環(huán)面積越小,對外的輻射越少,接收外界的干擾也越小。?

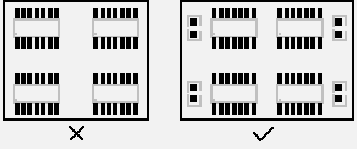

9、電源與地線層的完整性規(guī)則:?

對于導通孔密集的區(qū)域,要注意避免孔在電源和地層的挖空區(qū)域相互連接,形成對平面層的分割,從而破壞平面層的完整性,并進而導致信號線在地層的回路面積增大。

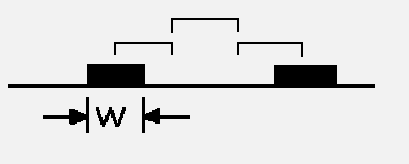

10、3W規(guī)則:

為了減少線間串擾,應(yīng)保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持70%的電場不互相干擾,稱為3W規(guī)則。如要達到98%的電場不互相干擾,可使用10W的間距。

11、屏蔽保護:

對應(yīng)地線回路規(guī)則,實際上也是為了盡量減小信號的回路面積,多見于一些比較重要的信號,如時鐘信號,同步信號;

對一些特別重要,頻率特別高的信號,應(yīng)該考慮采用銅軸電纜屏蔽結(jié)構(gòu)設(shè)計,即將所布的線上下左右用地線隔離,而且還要考慮好如何有效的讓屏蔽地與實際地平面有效結(jié)合。?

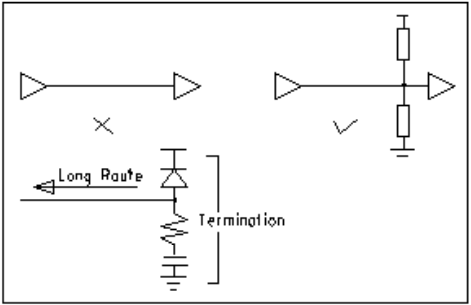

12、走線終結(jié)網(wǎng)絡(luò)規(guī)則:

在高速數(shù)字電路中, 當PCB布線的延遲時間大于信號上升時間(或下降時間) 的1/4時,該布線即可以看成傳輸線,為了保證信號的輸入和輸出阻抗與傳輸線的阻抗正確匹配,可以采用多種形式的匹配方法, 所選擇的匹配方法與網(wǎng)絡(luò)的連接方式和布線的拓樸結(jié)構(gòu)有關(guān)。

A. 對于點對點(一個輸出對應(yīng)一個輸入) 連接, 可以選擇始端串聯(lián)匹配或終端并聯(lián)匹配。前者結(jié)構(gòu)簡單,成本低,但延遲較大。后者匹配效果好,但結(jié)構(gòu)復(fù)雜,成本較高。

B. 對于點對多點(一個輸出對應(yīng)多個輸出) 連接, 當網(wǎng)絡(luò)的拓樸結(jié)構(gòu)為菊花鏈時,應(yīng)選擇終端并聯(lián)匹配。

當網(wǎng)絡(luò)為星型結(jié)構(gòu)時,可以參考點對點結(jié)構(gòu)。星形和菊花鏈為兩種基本的拓撲結(jié)構(gòu), 其他結(jié)構(gòu)可看成基本結(jié)構(gòu)的變形, 可采取一些靈活措施進行匹配。

在實際操作中要兼顧成本、 功耗和性能等因素, 一般不追求完全匹配,只要將失配引起的反射等干擾限制在可接受的范圍即可。

13、走線閉環(huán)檢查規(guī)則:

防止信號線在不同層間形成自環(huán)。在多層板設(shè)計中容易發(fā)生此類問題, 自環(huán)將引起輻射干擾。

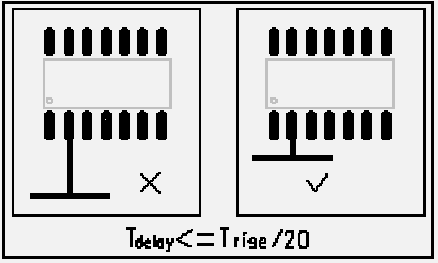

14、走線的分枝長度控制規(guī)則:

盡量控制分枝的長度,一般的要求是Tdelay<=Trise/20。

15、走線的諧振規(guī)則:

主要針對高頻信號設(shè)計而言, 即布線長度不得與其波長成整數(shù)倍關(guān)系, 以免產(chǎn)生諧振現(xiàn)象。

16、孤立銅區(qū)控制規(guī)則:

孤立銅區(qū)的出現(xiàn), 將帶來一些不可預(yù)知的問題, 因此將孤立銅區(qū)與別的信號相接, 有助于改善信號質(zhì)量,通常是將孤立銅區(qū)接地或刪除。

在實際的制作中, PCB廠家將一些板的空置部分增加了一些銅箔,這主要是為了方便印制板加工,同時對防止印制板翹曲也有一定的作用。

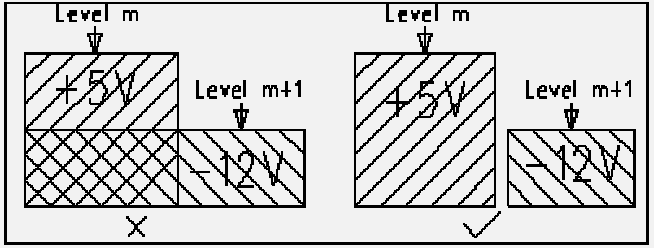

17、重疊電源與地線層規(guī)則:

不同電源層在空間上要避免重疊。主要是為了減少不同電源之間的干擾, 特別是一些電壓相差很大的電源之間, 電源平面的重疊問題一定要設(shè)法避免, 難以避免時可考慮中間隔地層。

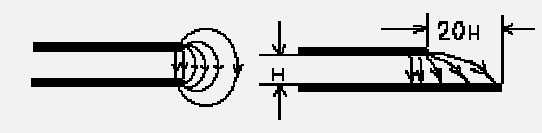

18、20H規(guī)則:

由于電源層與地層之間的電場是變化的, 在板的邊緣會向外輻射電磁干擾。稱為邊沿效應(yīng)。

解決的辦法是將電源層內(nèi)縮, 使得電場只在接地層的范圍內(nèi)傳導。以一個H(電源和地之間的介質(zhì)厚度)為單位,若內(nèi)縮20H則可以將70%的電場限制在接地層邊沿內(nèi);內(nèi)縮100H則可以將98%的電場限制在內(nèi)。?

(4)其他

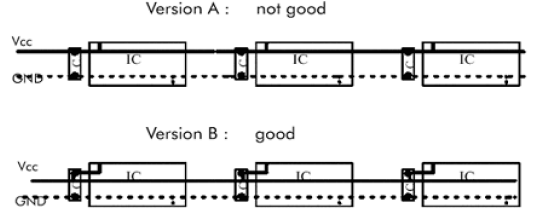

對于單雙層板電源線應(yīng)盡量粗而短。電源線和地線的寬度要求可以根據(jù)1mm的線寬最大對應(yīng)1A 的電流來計算,電源和地構(gòu)成的環(huán)路盡量小。

為了防止電源線較長時,電源線上的耦合雜訊直接進入負載器件,應(yīng)在進入每個器件之前,先對電源去藕。且為了防止它們彼此間的相互干擾,對每個負載的電源獨立去藕,并做到先濾波再進入負載。

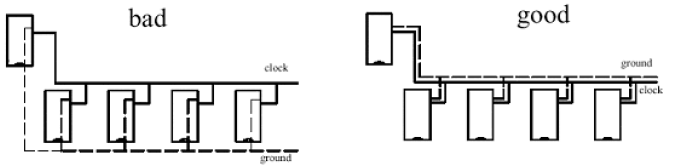

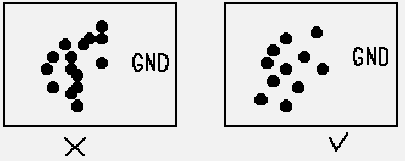

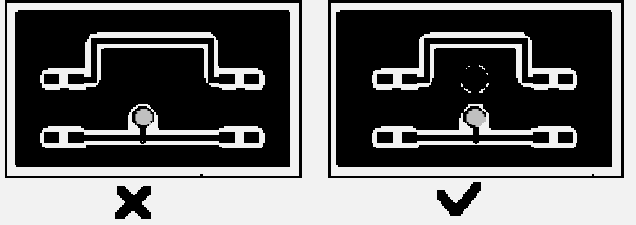

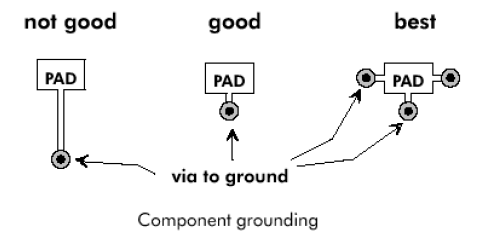

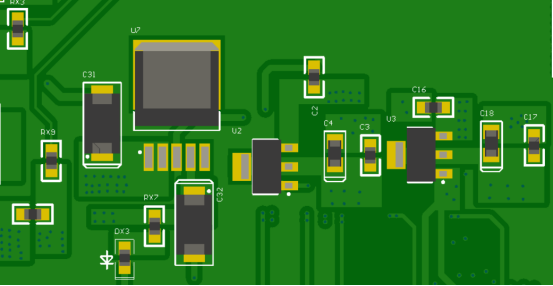

在布線中應(yīng)保持接地良好。如下圖。

03 DDR 布線規(guī)則

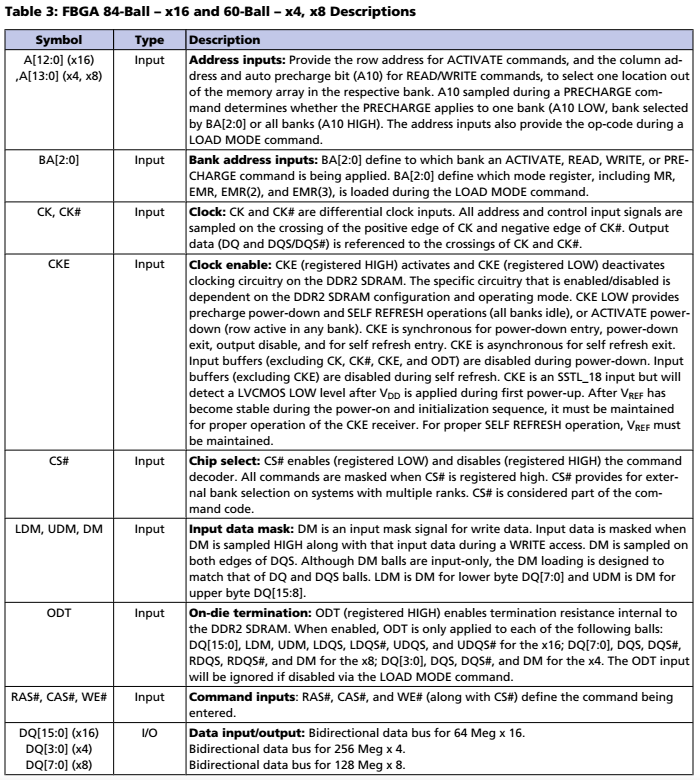

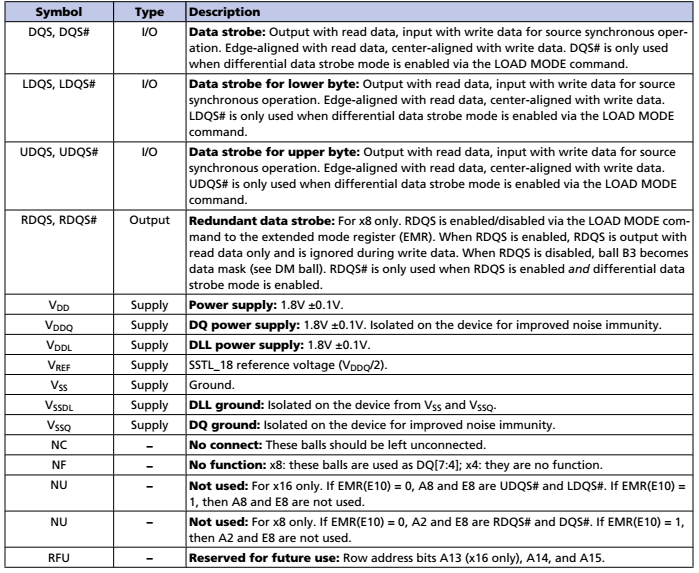

(1)首先了解下 DDR2 信號的組成:

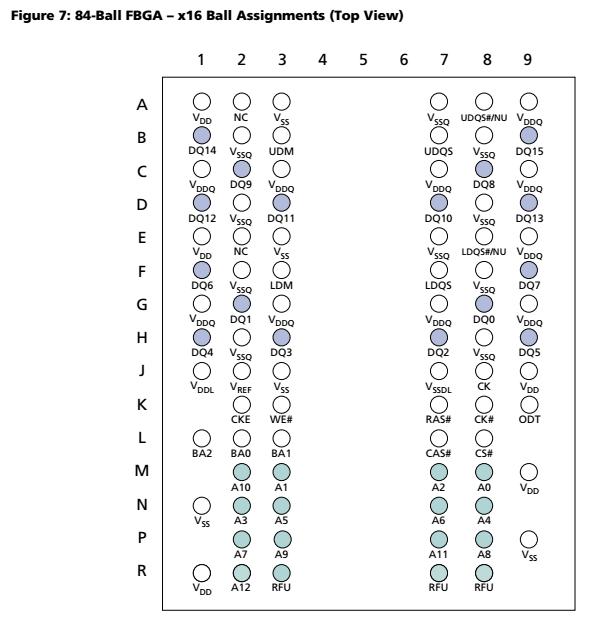

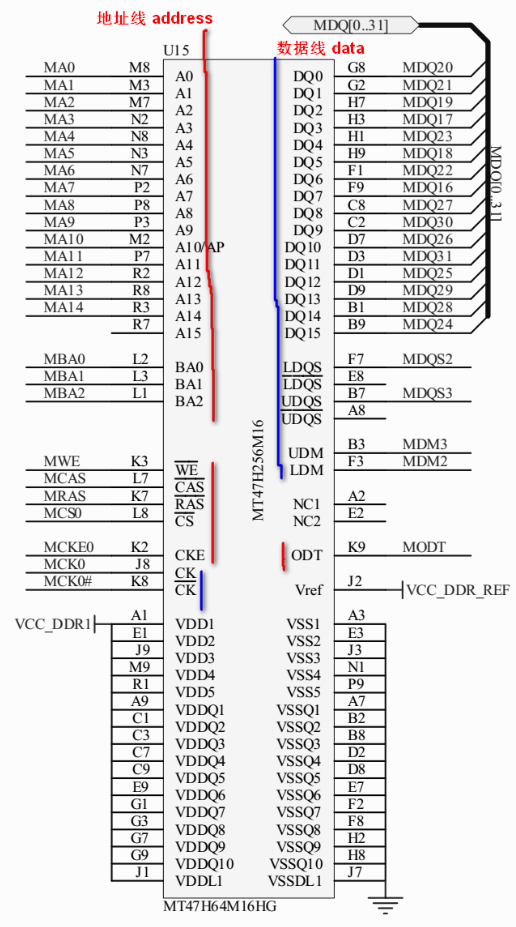

我用的DDR2芯片型號為:MT47H64M16HG

封裝:

引腳定義:

原理圖:

數(shù)據(jù)線和地址線:

數(shù)據(jù)線:DQ[0-15],DQS,DM,(時鐘信號)CK/CK#

地址線:A[0-15],BA[0-2],(控制信號)CS/WE/RAS/CAS,CKE、ODT

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論