PCB routing 策略&routingchecklist

2012-08-20 15:59:57

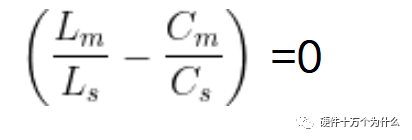

號技術(shù)。對于PCB工程師來說,最關(guān)注的還是如何確保在實際走線中能完全發(fā)揮差分走線的這些優(yōu)勢。也許只要是接觸過Layout的人都會了解差分走線的一般要求,那就是“等長、等距”。等長是為了保證兩個差分信號時刻

2015-01-12 14:53:57

、高速PCB設(shè)計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質(zhì)量,所以只作時序匹配之用而無其它目的。 7、有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

2018-09-13 15:50:25

下面從直角走線、差分走線、蛇形線三個方面來闡述PCB LAYOUT的走線。

2021-03-17 07:25:46

結(jié)構(gòu),能有效的減少相互間的耦合。 6. 高速PCB 設(shè)計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質(zhì)量,所以只作時序匹配之用而無其它目的。 7. 有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

2019-06-10 10:11:23

高速PCB設(shè)計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質(zhì)量,所以只作時序匹配之用而無其它目的。7. 有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

2017-07-07 11:45:56

PCB Layout中的走線策略

2012-08-04 16:32:25

小振幅差分信號技術(shù)。對于PCB工程師來說,最關(guān)注的還是如何確保在實際走線中能完全發(fā)揮差分走線的這些優(yōu)勢。也許只要是接觸過Layout的人都會了解差分走線的一般要求,那就是“等長、等距”。等長是為了保證兩個

2014-08-13 15:44:05

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PCB設(shè)計中

2019-08-05 06:40:24

新人,求PCB布局走線資料,謝謝!

2014-08-02 19:19:40

PCB中走線有幾種這幾種分別有什么作用?哪種對信號的影響最好?

2012-11-13 15:49:21

pcb走線時,會影響到已經(jīng)布完的線。之前正在布的線不會對已經(jīng)布完的線產(chǎn)生影響,現(xiàn)在不知道怎么恢復。

2019-09-25 03:58:46

PCB走線寬度、電流關(guān)系計算工具:PCB走線寬度、電流關(guān)系計算工具.zip (850.77 KB )

2019-10-09 01:16:38

PCB走線電流計算工具

2021-03-12 13:36:29

好的圖像質(zhì)量的保證。 PCB走線如果可能的話,信號走線使用6mil, 走線間距使用6mil. 放置0.1uF的退耦電容在對應的DSP電源腳上,并盡可能的靠近。它的走線盡可能的粗。電源正極的走線最少要

2023-04-13 16:09:54

求高手貢獻PCB設(shè)計走線經(jīng)驗!及相關(guān)技術(shù)

2013-01-11 20:02:07

1.PCB走線線寬的重要性 PCB載流能力的計算一直缺乏權(quán)威的技術(shù)方法、公式,經(jīng)驗豐富CAD工程師依靠個人經(jīng)驗能作出較準確的判斷。但是對于CAD新手,不可謂遇上一道難題。 對于大電流電源走線

2023-04-12 16:02:23

`為什么下圖中PCB走線正反面不同。孔與孔之間為直接通路。為什么背面的走線環(huán)繞迂回。小白菜提問,求高手詳解。謝謝`

2018-10-29 08:46:46

本帖最后由 24不可說 于 2017-9-3 13:29 編輯

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終

2017-09-03 13:25:35

采訪過蘋果公司CEO的B站up主-何同學,近期更新一條視頻中,有出現(xiàn)過他自己設(shè)計的PCB圖。很多人說他不應該直角走線。PCB為什么不能直角走線呢?一般在高速信號線中,直角線會帶來阻抗的不均勻

2022-09-08 16:54:17

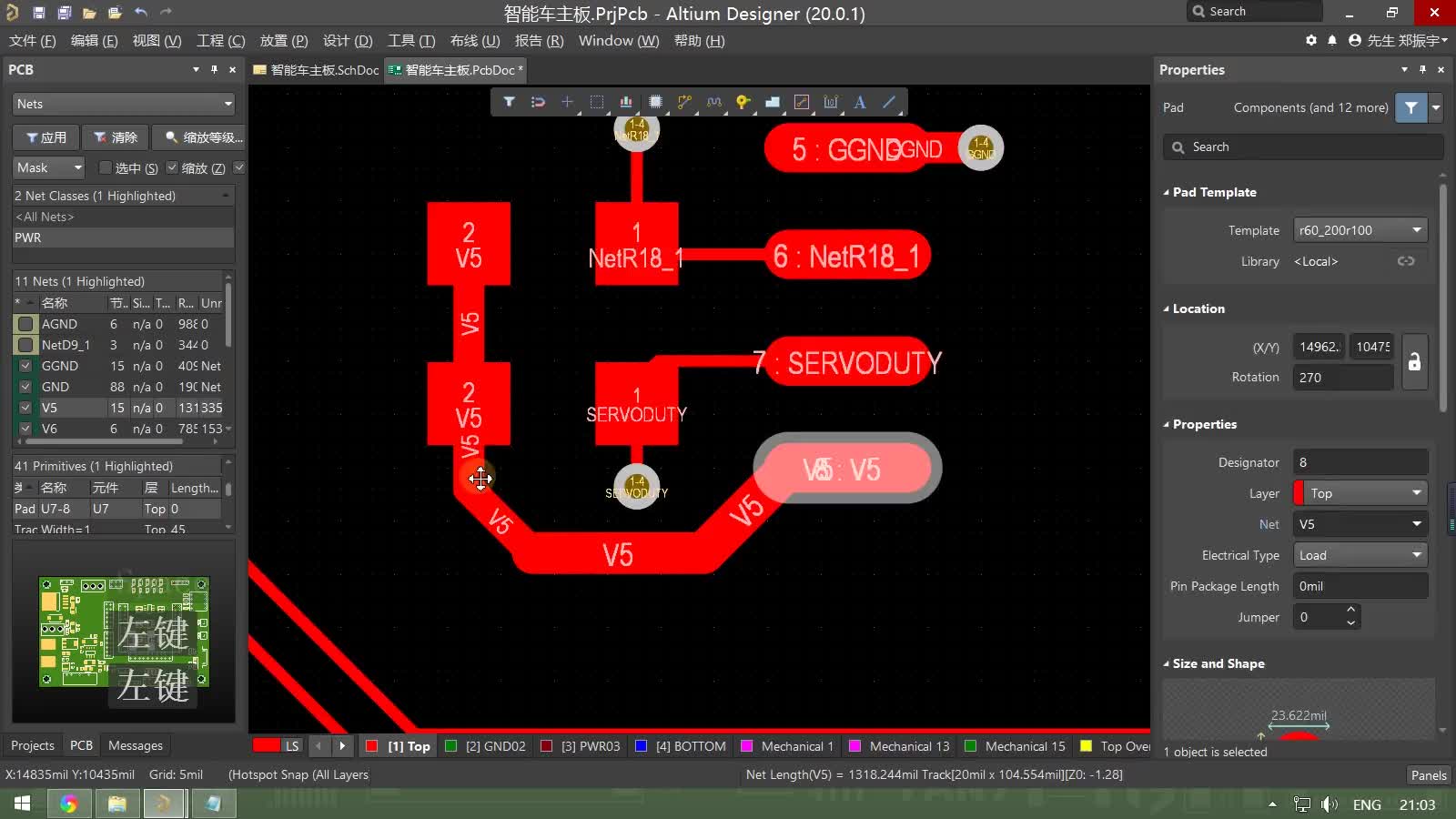

`用altium 畫PCB 對稱電路時走線沒有走對稱,看起來有點別扭。像這種對稱電路走線一般要怎么處理比較好呢?像我這樣畫對電器想能有沒有什么影響?要怎么畫才比較合理?希望大家指點指點`

2017-01-07 11:20:13

。 采用表面拉線的方式進行出線操作(14)芯片的第四排、五排、第六排,通過孔換到第三層層,在內(nèi)層第三中拉出走線(內(nèi)層第二層通常用作參考層GND)。 在內(nèi)層第三中拉出走線總體來說,BGA布線中所需的PCB層數(shù)

2020-07-06 15:58:12

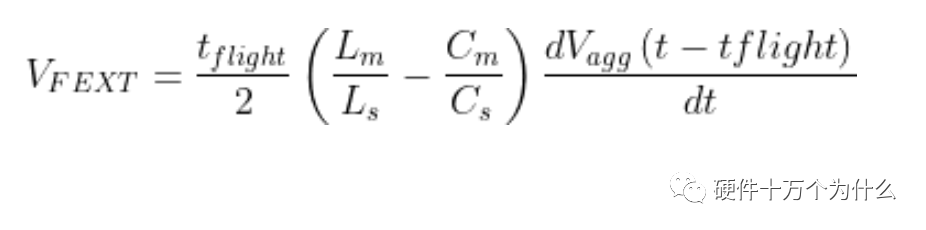

經(jīng)常聽說“PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾”,這就是3W原則,信號線之間的干擾被稱為串擾。那么,你知道串擾是怎么形成的嗎?當兩條走線很近時,一條信號線上的信號可能會在另一

2022-12-27 20:33:40

在pcb的設(shè)計過程中,元器件的布局和走線的調(diào)整是非常重要的一個步驟。恰當?shù)牟季挚梢院喕季€的難度,更重要的是可以提高PCB的電氣性能,減少EMC,EMI。 下面是同一個原理圖對應的兩種不同的布局和走

2019-10-17 04:37:54

PCB布線這幾種走線方式,你會嗎?在我們學習嵌入式開發(fā)的過程中,PCB布線是必不可少的。好的布線方式,輕則看著美觀、布局合理,重則可以節(jié)約生產(chǎn)成本,達到良好的電路性能和散熱性能,使元器件的性能達到

2020-02-28 10:50:28

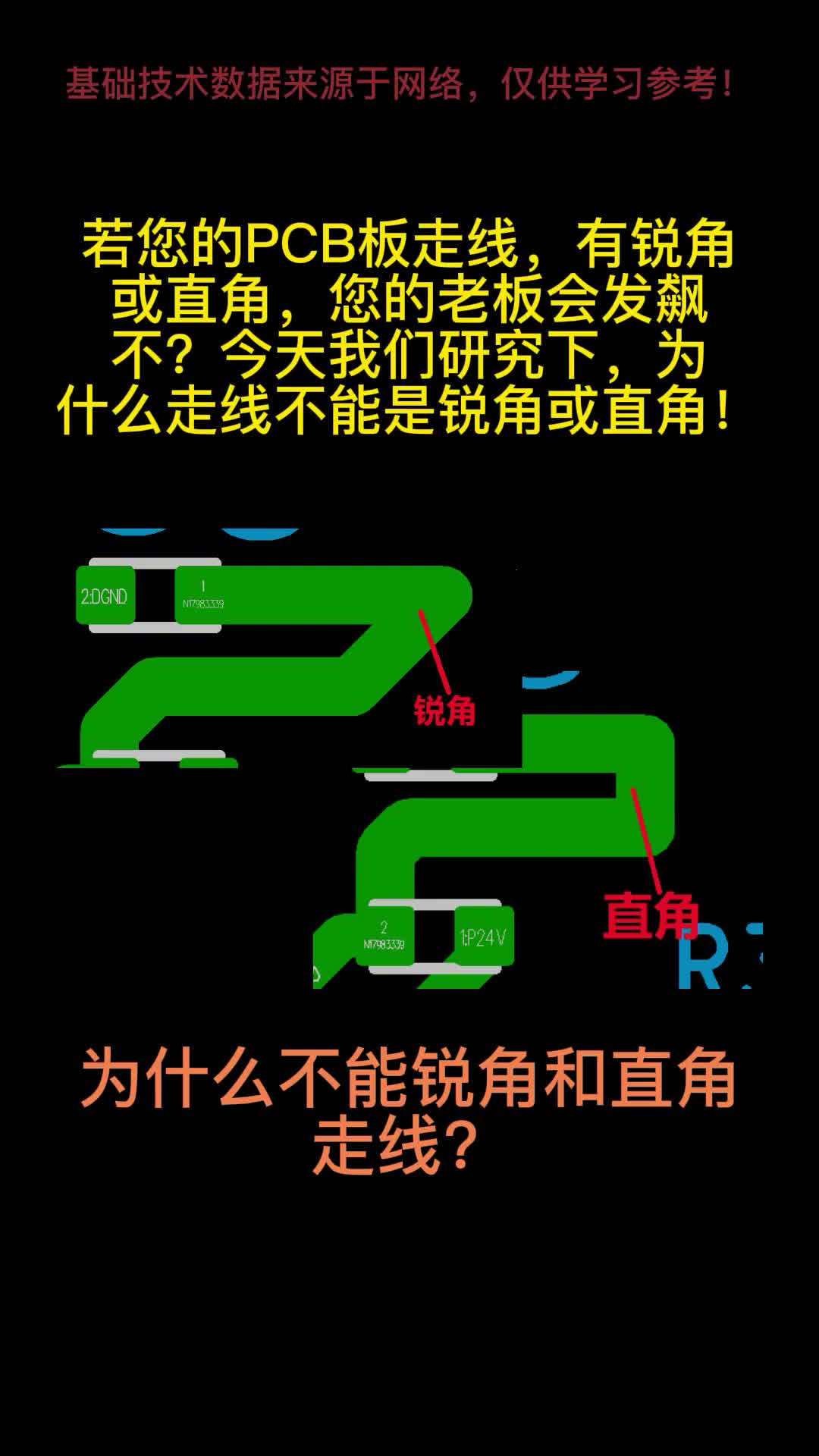

線角度 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一,那么直角走線究竟會對信號傳輸產(chǎn)生多大的影響呢? 從原理上說,直角走線會使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)

2019-08-20 15:27:06

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關(guān)"信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是時鐘

2017-11-22 20:04:14

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關(guān)”信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是

2018-08-30 10:14:44

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關(guān)”信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是

2020-07-14 18:02:17

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關(guān)"信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處?;最典型的就是

2018-09-20 11:05:23

PCB電容引腳之間可以走線嗎?

2023-04-13 16:25:48

直角走線一般是pcb布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一,那么直角走線究竟會對信號傳輸產(chǎn)生多大的影響呢?從原理上說,直角走線會使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實

2014-10-28 15:08:55

1.1 PCB板上預劃分數(shù)字、模擬、DAA信號布線區(qū)域。1.2 數(shù)字、模擬元器件及相應走線盡量分開并放置於各自的布線區(qū)域內(nèi)。1.3 高速數(shù)字信號走線盡量短。1.4 敏感模擬信號走線盡量短。1.5

2019-05-30 06:58:19

PCB設(shè)計走線的寬度與最大允許電流有何關(guān)系?PCB設(shè)計走線的寬度與銅厚有何關(guān)系?

2021-10-11 09:49:14

PCB設(shè)計走線的規(guī)則是什么

2021-03-17 06:36:28

可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。 主要從直角走線,差分走線,蛇形線等三個方面來闡述。 1. 直角走線 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量

2018-09-17 17:31:52

硬件工程師做久了自然有自己處理電路板的一套方法,也許不是最好的辦法,自己卻能理解其中的意義。但是工作中還是要按照最完美的辦法進行操作,本期我們就來了解一下關(guān)于高速信號走線準則到底有哪幾條是你不清楚的?

2020-10-30 08:33:48

PCB能不能以銳角走線pcb layout能不能以90°走線

2021-02-26 08:14:21

1. 一般規(guī)則1.1 PCB板上預劃分數(shù)字、模擬、DAA信號布線區(qū)域。1.2 數(shù)字、模擬元器件及相應走線盡量分開并放置於各自的布線區(qū)域內(nèi)。1.3 高速數(shù)字信號走線盡量短。1.4 敏感模擬信號走線盡量

2014-03-14 17:44:44

pcb走線為什么直接連不到芯片引腳上呢?

2023-04-10 16:29:30

pcb走線線寬和電流的關(guān)系

2012-07-16 16:48:57

pcb布局,走線方面,有什么建議嗎,該怎么怎么走,怎么提高效率

2016-10-15 14:51:34

;=2倍的線寬。PCI板上的蛇行線就是為了適應PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個分布參數(shù)的 LC濾波器,還可作為收音機天線的電感線圈,短而窄的蛇形走線可做保險絲等等

2019-05-22 02:48:05

蛇形線是布線過程中常用的一種走線方式,其主要目的是為了調(diào)節(jié)延時滿足系統(tǒng)時序設(shè)計要求,但是設(shè)計者應該有這樣的認識:蛇形線會破壞信號質(zhì)量,改變傳輸延時,布線時要盡量避免使用,因此一塊PCB上的蛇形線越多

2015-01-12 15:40:09

請問大神,用這個打開PCB工程文件的時候鼠標所指的同一網(wǎng)絡(luò)的走線不會高亮顯示,這要怎么解決?

2017-08-27 10:42:29

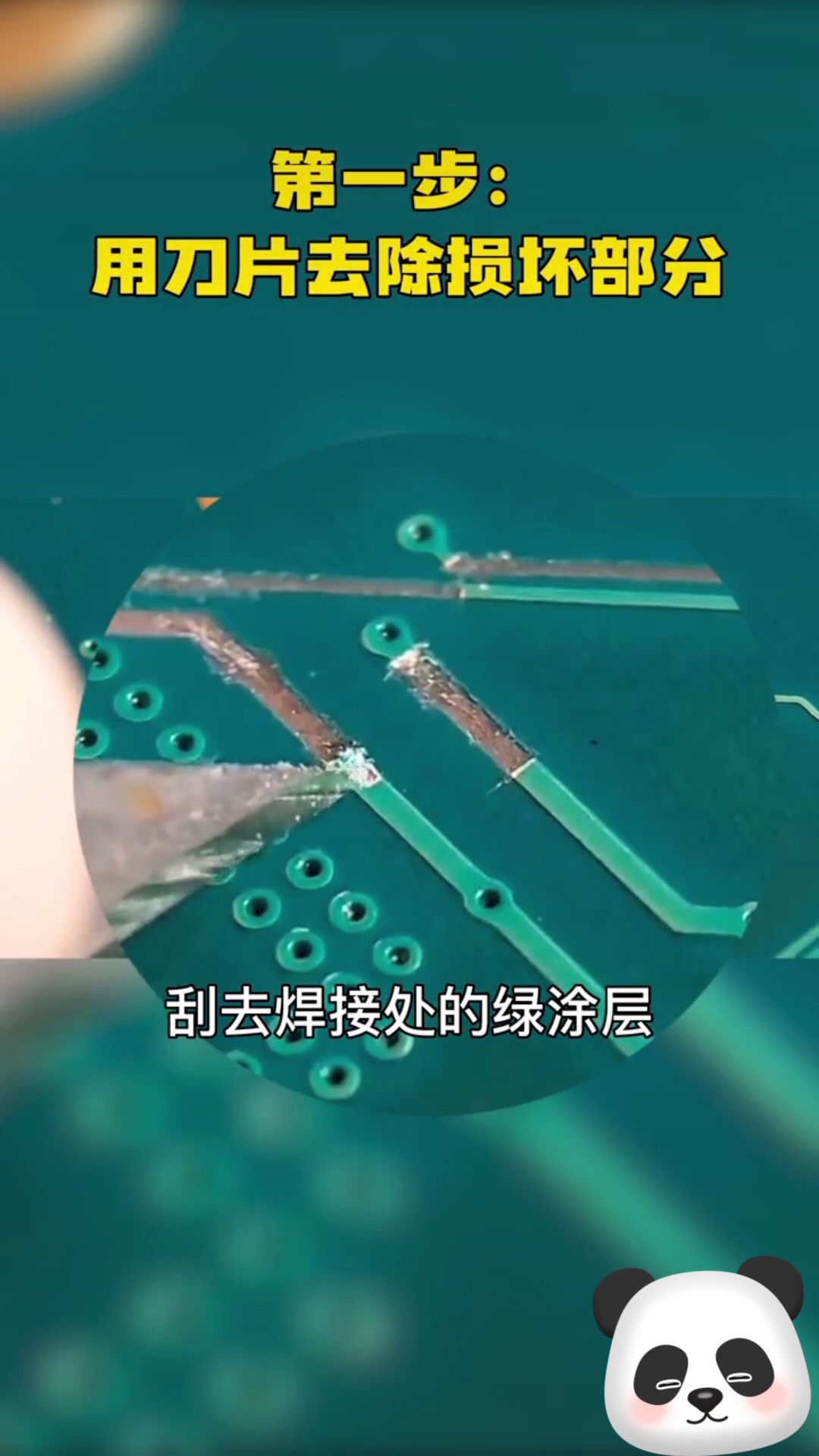

PCB設(shè)計時,有時候需要在不增加PCB走線寬度的情況下提高該走線通過大電流的能力(載流能力),通常的方法是給該導線鍍錫(或者上錫);下面以在PCB頂層走線鍍錫為例,使用AD09軟件,簡單介紹如何走線上錫處理:1、?選擇TopLayer層,確定需要走線的地方,畫一條導線;(圖文詳解見附件)

2019-09-06 15:57:30

PCB設(shè)計:通常的BGA器件如何走線?

2021-02-26 06:13:16

本帖最后由 @adu 于 2013-6-8 10:39 編輯

如下圖有兩個焊盤在走線時,那種方式是最優(yōu)的哪?請從電氣性能、整體外觀、生產(chǎn)制造、溫度、震動、干擾、高頻信號等方面分析原因。本人習慣性用最后一張圖片的方式,有什么不妥的地方嗎,請高手們賜教。

2013-06-08 10:37:59

PCB Layout中的走線策略布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見

2009-08-20 20:58:49

是至關(guān)重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個方面來闡述。01直角走線直角走線一般是PCB布線中要求盡量避免

2018-07-08 13:28:36

在日常的PCB設(shè)計中,通常我們使用快捷鍵:shift+空格 來切換走線轉(zhuǎn)角的模式,比如斜角,直角,弧形轉(zhuǎn)角以及任意角度的轉(zhuǎn)角。 最近許多學員再請教,為什么使用shift+空格,也無法切換角度;下面

2019-11-11 17:05:26

cadence PCB 怎么取消走線?***用過,取消很容易,cadence沒發(fā)現(xiàn)這個功能!

2016-01-25 22:57:46

很多人對于PCB走線的參考平面感到迷惑,經(jīng)常有人問:對于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個是參考平面?要弄清楚這個問題,必須對了解傳輸線的概念。我們知道,必須使用傳輸線來分析

2014-11-17 10:07:29

)就是指這種小振幅差分信號技術(shù)。對于PCB工程師來說,最關(guān)注的還是如何確保在實際走線中能完全發(fā)揮差分走線的這些優(yōu)勢。也許只要是接觸過Layout的人都會了解差分走線的一般要求,那就是"等長

2019-03-18 21:38:12

為什么PCB走線中不能出現(xiàn)銳角和直角?而且走線也不能和IC的PIN腳垂直?會影響到什么?

2023-04-11 16:31:28

繞線方式等有關(guān)。隨著PCB走線信號速率越來越高,對時序要求較高的源同步信號的時序裕量越來越少,因此在PCB設(shè)計階段準確知道PCB走線對信號時延的影響變的尤為重要。本文基于仿真分析DK,串擾,過孔,蛇形

2014-10-21 09:54:56

走在帶狀線。微帶線的串擾相對帶狀線較大,帶狀線走線可以減小串擾的影響。 4,保持完整回流平面,避免跨分割,走線和參考面盡量緊耦合。 3.4 繞線方式對信號時延的影響 在PCB設(shè)計時候,有些設(shè)計人

2014-10-21 09:51:22

如何利用PCB走線設(shè)計一個0.05歐姆的采樣電阻?

2021-02-03 07:10:52

AD里PCB多根走線時怎么改變線寬

2019-09-12 04:20:46

如何在altium designer 的PCB圖里畫出 粗細漸變的走線

2019-09-04 04:21:32

射頻線PCB走線屏蔽孔,都有什么要求???求解

2016-01-13 14:40:40

PCB上面用更細的走線做保險有什么具體的公式算法,我有兩種電流規(guī)格,一種是2A的持續(xù)電流,一種是0.1A的持續(xù)電流,如果用表層走線做保險絲,要用多寬的走線,銅厚1OZ

2019-08-21 21:45:15

怎樣計算PCB布線中走線允許的最大長度?走線太長了都有哪些影響呢?

2023-04-10 17:10:25

(即菜單中的Place/Line), 二者走線的線寬參數(shù)是不一樣的,要分別設(shè)置。 一、 PCB走線幾種方式 1. 直角走線 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準

2014-12-16 09:47:09

,能有效的減少相互間的耦合。6. 高速PCB 設(shè)計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質(zhì)量,所以只作時序匹配之用而無其它目的。7.有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

2015-03-05 15:53:35

電源布局、網(wǎng)口電路、音頻走線的PCB設(shè)計

2021-03-04 06:10:24

直角走線一般是pcb布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一,那么直角走線究竟會對信號傳輸產(chǎn)生多大的影響呢?從原理上說,直角走線會使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實

2014-11-07 09:40:54

PCB走線線間距能不能走5mil?

2019-09-26 05:35:53

PCB長距離走線和短距離加個過孔走線哪種走線更合理?

2019-09-25 22:11:32

AD18 ,PCB,走線,任意走線,在哪里設(shè)置?

2019-03-07 01:36:59

HDMI差分對PCB怎么走線?要計算匹配阻抗嗎?差分對走多長有要求嗎?四對差分對要走一樣長嗎?

2019-05-31 05:35:21

蛇形線是Layout中經(jīng)常使用的一類走線方式。其主要目的就是為了調(diào)節(jié)延時,滿足系統(tǒng)時序設(shè)計要求。設(shè)計者首先要有這樣的認識:蛇形線會破壞信號質(zhì)量,改變傳輸延時,布線時要盡量避免使用。但實際設(shè)計中

2012-12-18 12:12:55

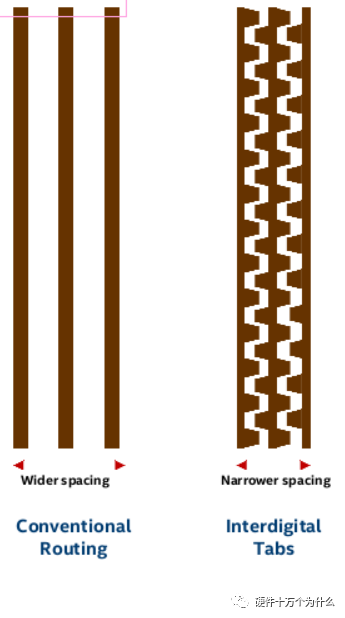

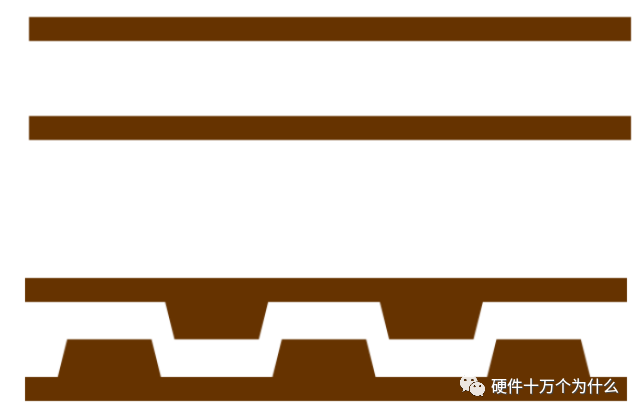

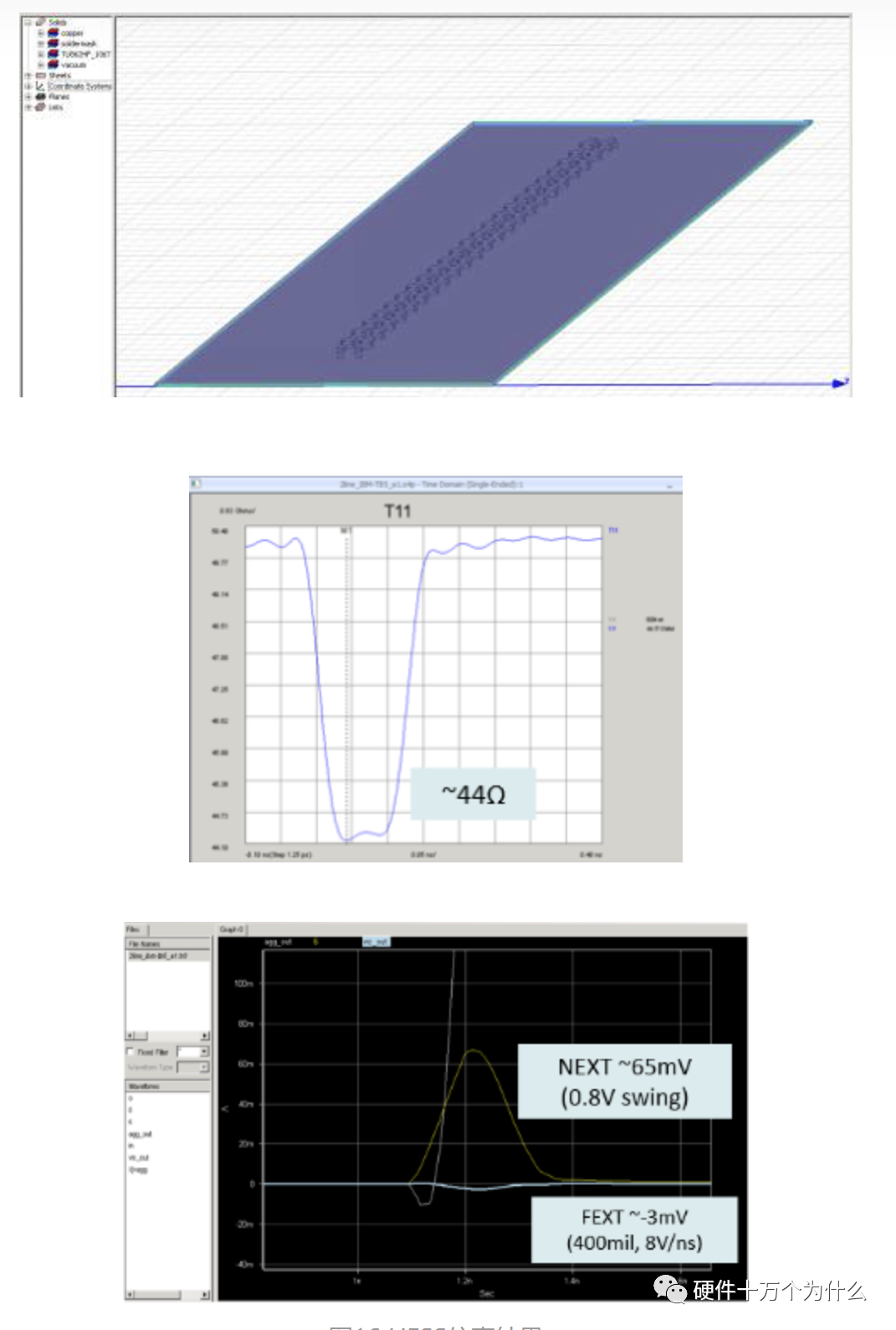

線寬并縮小間距是常規(guī)操作,比如常用的neck模式走線,這樣一來,線是拉出來了,阻抗卻被卡了脖子,一路飄高,此外,隨著走線間距的減小,串擾也隨之增加。于是,Tabbed routing應運而生。這種

2020-08-20 17:24:09

PCB走線之問會產(chǎn)生串擾現(xiàn)象,這種串擾不僅僅會在時鐘和其周圍信號之間產(chǎn)生,也會發(fā)生在其他關(guān)鍵信號上,如數(shù)據(jù)、地址、控制和輸入/輸出信號線等,都會受到串擾和耦合影響。為了解決這些信號的串擾

2018-11-27 15:26:40

為了避免不理想返回路徑的影響,可以采用差分對走線。為了獲得較好的信號完整性,可以選用差分對來對高速信號進行走線,如圖1所示,LVDS電平的傳輸就采用差分傳輸線的方式。 圖1 差分對走線實例

2018-11-27 10:56:15

PCB Auto-Routing設(shè)計注意:用AD10繪制的圖,低于AD10的版本無法打開。

2016-01-11 11:28:55 0

0 PCB Auto-Routing設(shè)計喜歡的朋友下載來學習

2016-02-17 14:29:31 0

0 Tabbed routing是指將特定形狀和尺寸的銅皮,按照一定的規(guī)則添加到走線上的一種布線處理方法。該方法是由Intel公司于2015年提出,主要適用于DDR4的數(shù)據(jù)信號走線。

2020-12-24 16:22:22 1135

1135

電子發(fā)燒友App

電子發(fā)燒友App

評論