向大神請教:在設(shè)計一個10層板PCB時,一些關(guān)鍵信號需要做阻抗匹配,對于如何選擇參考層有一些不明白,如下:1、中間信號層5做阻抗匹配時,是否可以選用電源層4和電源層7共同作為參考層?2、TOP信號層1某些信號做阻抗匹配時,是否可選用信號層3作為參考層?層疊示意圖

2022-04-24 11:23:09

給大家分享一個4層盲埋孔案例。

2019-08-30 04:41:16

其它信號的安全距離; 4. 單板信號速率高達(dá)56G,考慮TX穿RX連接器焊盤殘留孔銅的串?dāng)_; 5.因?yàn)?b class="flag-6" style="color: red">高速連接器正反兩面都有,考慮連接器PIN的STUB長度和背鉆,設(shè)計層疊時把電源層放在第2層和第33層,高速線走在單板的中間,這樣背鉆后的stub最短;

2020-07-16 14:46:08

做一個8層二階盲埋孔的板子,盲埋孔都應(yīng)該是哪幾層算是二階的,一般建議做哪些層比較好價格比較便宜?

2016-11-03 10:09:59

: ①制做2MM層:以線路層BGA焊盤拷貝出為另一層2MM層并將其處理為2MM范圍的方形體,2MM中間不可有空白、缺口(如有客戶要求以BGA處字符框?yàn)槿?b class="flag-6" style="color: red">孔范圍,則以BGA處字符框?yàn)?MM范圍做同樣處理

2018-08-30 10:14:43

BGA區(qū)域之后,引出布線可以散開走線,加大線和線之間的距離,以便于減少高速信號直接的串?dāng)_。

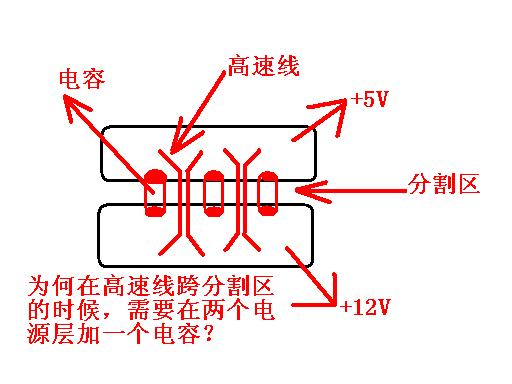

注意電源和GND平面被切斷

BGA芯片一般電源和GND網(wǎng)絡(luò)焊盤引腳都位于BGA中間部分,電源和GND的網(wǎng)絡(luò)

2023-06-02 13:51:07

目前,無論是ARM、DSP、FPGA等大多數(shù)封裝基本上都是BGA或MBGA,BGA在PCB布線上的可靠性還都基本上能滿足,但是MBGA封裝的:間距在0.5mm一下的,在PCB中布線到PCB加工制成,特別對于高速信號來說,布線會造成信號完整性的問題及制版質(zhì)量問題,請教各位大俠,如何解決???

2022-04-23 23:15:51

`各位大蝦們好!小弟初次使用BGA封裝的芯片,SPARTAN3A,封裝是CS484的。默認(rèn)使用的via為16/9mil,四層板。使用扇出功能以后得到的圖在下面。我發(fā)現(xiàn),這些過孔讓很多在內(nèi)層的電源管腳成了孤島,完全阻斷了電源層,請問,這個問題怎么解決?謝謝了!`

2011-10-26 16:39:28

BGA是一種芯片封裝的類型,英文 (Ball Grid Array)的簡稱,封裝引腳為球狀柵格陣列在封裝底部,引腳都成球狀并排列成一個類似于格子的圖案,由此命名為BGA。主板控制芯片諸多采用此類

2023-03-24 11:58:06

開窗:與阻焊優(yōu)化值一樣其單邊開窗范圍為1.25~3mil,阻焊距線條(或過孔焊盤)間距大于等于1.5mil;2、BGA塞孔模板層及墊板層的處理: ①制做2MM層:以線路層BGA焊盤拷貝出為另一層

2013-08-29 15:41:27

BGA虛焊檢測、BGA電路焊接工藝質(zhì)量評估與完好性快速檢測預(yù)警系統(tǒng)

2020-07-01 16:39:44

,我們總是先使用簡單的模型。相對于投入的精力,回報是巨大的。首先,差分過孔可以被模擬成一個統(tǒng)一的差分對,具有差分阻抗和介電常數(shù)。它被分成兩個或三個均等的部分,這取決于信號層是如何進(jìn)入和離開導(dǎo)通孔的。這些

2014-12-22 13:47:23

我設(shè)計一個四層板,電源有3.3V,5V,12V的,如何在電源層進(jìn)行信號分割?

2015-07-21 10:58:41

回流用的,而信號是用電感的方式回流,所以參考層只要在電源回路里就OK,與是 GND 還是PWR無關(guān)。參考層是信號回流用的,參考電位是用來讀取信號值的,一般會選 GND,不能把參考層和參考電位混淆。3、如果在芯片內(nèi)部信號參考的是電源,那么在PCB上參考電源會比較好,但多數(shù)芯片設(shè)計中高速信...

2021-12-27 07:10:09

高速信號的電源完整性分析在電路設(shè)計中,設(shè)計好一個高質(zhì)量的高速PCB板,應(yīng)該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

解決常見的問題需要采取的一些措施: 電源層對電流方向不限制,返回線可沿著最小阻抗即與信號線最接近的路徑走。這就可能使電流回路最小,而這將是高速系統(tǒng)首選的方法。但是電源層不排除線路雜波,不注意電源分布路徑

2018-09-12 15:09:57

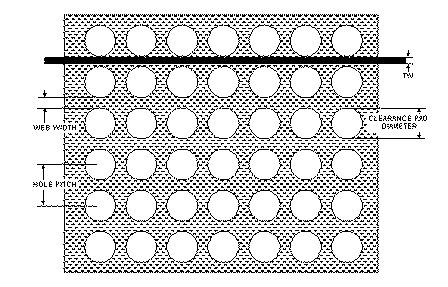

的焊盤區(qū)、POWER 層隔離區(qū)三部分組成。接下來,我們來了解下高速PCB中過孔的問題及設(shè)計要求。1. 高速PCB中過孔的影響高速PCB多層板中,信號從某層互連線傳輸?shù)搅硪?b class="flag-6" style="color: red">層互連線就需要通過過孔來實(shí)現(xiàn)

2019-09-25 17:12:01

多層PCB通常用于高速、高性能的系統(tǒng),其中一些層用于電源或地參考平面,這些平面通常是沒有分割的實(shí)體平面。無論這些層做什么用途,電壓為多少,它們將作為與之相鄰的信號走線的電流返回路徑。構(gòu)造一個好

2018-11-27 15:14:59

內(nèi)層有地、信號線、電源,下面通過1.6mm板厚幾個疊層結(jié)構(gòu),分析哪種結(jié)構(gòu)最合適。 首先,介紹一下PCB線路板廠采用較多的六層板的普通結(jié)構(gòu),此結(jié)構(gòu)使用于普通無高速信號的PCB板。(華秋電路現(xiàn)六層板免費(fèi)打

2019-10-16 18:03:20

【類別】主板 【Pin數(shù)】12306 【層數(shù)】12層 【最高速率】18G 【難 點(diǎn)】 1、兩片DDR的Flyby拓?fù)滏溄樱弧 ?、HDMI高速總線信號布線路勁與高壓電源區(qū)域較近; 3

2023-04-18 15:07:13

【類別】主板 【Pin數(shù)】12306 【層數(shù)】12層 【最高速率】18G 【難 點(diǎn)】 1、兩片DDR的Flyby拓?fù)滏溄樱弧 ?、HDMI高速總線信號布線路勁與高壓電源區(qū)域較近; 3

2023-04-19 15:32:18

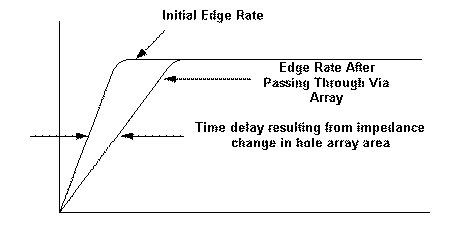

ps級快速邊緣信號對信號完整性的影響更大的SSN更大的Crosstalk更大的EMI[hide][/hide]華強(qiáng)pcb高質(zhì)量多層板打樣活動月,6層板400,8層板500,極速交期。點(diǎn)擊鏈接直接參與體驗(yàn)活動:http://url.elecfans.com/u/5101fbe4b0?

2009-09-12 10:31:31

12in;對比可知10信號最高頻率要高于100MHz,走線長度都在6in時10MHz需要視為高速信號。二、層疊結(jié)構(gòu)設(shè)計多層板中,信號層、電源層及地層的排列順序,對信號完整性有著很大的影響。在層疊

2020-12-21 09:23:34

1、由于單板大部分都是56G的高速線,部分的25G、10G的信號,經(jīng)過我司SI仿真,為保證信號質(zhì)量,我們推薦用M7NE板材,減小損耗; 2、單板高速線經(jīng)評估后需要14個布線內(nèi)層;電源電流較大

2020-07-16 11:33:11

此項(xiàng)后可設(shè)置填充圖案與基點(diǎn)之間的寬度,用于調(diào)整保溫層等內(nèi)填充圖案與基線的關(guān)系,不勾選則為 100%;【基線位置】有中間、左邊和右邊三種選擇,用于調(diào)整圖案與基線之間的橫向關(guān)系,動態(tài)繪制確認(rèn);【圖案選擇

2021-01-29 10:44:16

的DDR4信號,綠色是Pwr04層上的Vcc電源,黃色為芯片內(nèi)部的地pin和過孔,可以看到在第四層處地孔和電源層是斷開的,這個時候我們?nèi)y試這部分的線路阻抗時,探頭一端在信號pin上,地針肯定是在

2021-11-05 17:33:47

BGA是一種芯片封裝的類型,英文 (Ball Grid Array)的簡稱,封裝引腳為球狀柵格陣列在封裝底部,引腳都成球狀并排列成一個類似于格子的圖案,由此命名為BGA。主板控制芯片諸多采用此類

2023-03-24 11:52:33

用PADS LAYOUT畫一個四層板,但是按F4不能打通孔,提示VIOLATION DETECTED。但是我已經(jīng)設(shè)置好了相應(yīng)的盲孔和通孔,也將top layer和bottom layer設(shè)置成了層對(只設(shè)置了一個層對1~4,中間兩層是電源和地),安全間距也沒有問題。到底是怎么回事啊。

2014-10-16 23:31:24

各層圖形間的對位不準(zhǔn)。為了確保各層圖形的良好互連,焊盤環(huán)寬必須考慮層間圖形對位公差、有效絕緣間隙和可靠性的要求。體現(xiàn)在設(shè)計上就是控制焊盤環(huán)寬。 (1)金屬化孔焊盤應(yīng)大于等于5mil。 (2)隔熱環(huán)寬

2018-06-05 13:59:38

走線層之外,最重要的就是安排了獨(dú)立的電源和地層(鋪銅層)。在高速數(shù)字電路系統(tǒng)中,使用電源和地層來代替以前的電源和地總線的優(yōu)點(diǎn)主要在于:1)為數(shù)字信號的變換提供一個穩(wěn)定的參考電壓。2)均勻地將電源同時

2016-05-17 22:04:05

打孔換層,換層優(yōu)先選擇兩邊是GND的層面處理。盡量收發(fā)信號布線在不同層,如果空間有限,需收發(fā)信號走線同層時,應(yīng)加大收發(fā)信號之間的布線距離。

針對以上高速信號還有如下方面的要求:

一、BGA焊盤區(qū)域挖

2023-08-01 18:02:03

BGA焊點(diǎn)上時,也建議做樹脂塞孔。

1

塞孔的優(yōu)點(diǎn)

焊盤為了散熱,經(jīng)常會有過孔,為了防止焊錫從焊盤流去下面一層,對過孔做樹脂塞孔處理,可以使過孔塞孔達(dá)到更加飽滿、提高產(chǎn)品壽命的好處。

2

塞孔的缺點(diǎn)

由于

2023-05-04 17:02:26

在電路設(shè)計中,一般我們很關(guān)心信號的質(zhì)量問題,但有時我們往往局限在信號線上進(jìn)行研究,而把電源和地當(dāng)成理想的情況來處理,雖然這樣做能使問題簡化,但在高速設(shè)計中,這種簡化已經(jīng)是行不通的了。盡管電路設(shè)計

2021-12-28 07:48:43

。 1.3.14光點(diǎn)(IC或BGA旁),需平整、啞光、無缺口。否則機(jī)器無法順利識別,不能自動貼件。 1.3.15手機(jī)板不允許返沉鎳金,否則鎳厚嚴(yán)重不均。影響信號。 2.3PCB質(zhì)量對波峰焊

2018-09-13 15:45:11

連接多層板的地層;3、打地孔用于高速信號的換層的過孔的位置。但所有的這些情況,應(yīng)該是在保證電源完整性的情況下進(jìn)行的。那就是說,只要控制好地孔的間隔,多打地孔是允許的嗎?在五分之一的波長為間隔打地孔

2019-09-30 04:38:28

高速信號的換層的過孔的位置。但所有的這些情況,應(yīng)該是在保證電源完整性的情況下進(jìn)行的。那就是說,只要控制好地孔的間隔,多打地孔是允許的嗎?在五分之一的波長為間隔打地孔沒有問題嗎?假如我為了保證多層板

2019-06-03 01:35:16

請教下,我在做到BGA Fan out 的時候,怎么設(shè)置FAN OUT 的信號點(diǎn) 扇出到第幾層 ? 比如有些扇出到第2層,有些扇出到第4層。

2016-04-09 21:33:28

的模型。相對于投入的精力,回報是巨大的。首先,差分過孔可以被模擬成一個統(tǒng)一的差分對,具有差分阻抗和介電常數(shù)。它被分成兩個或三個均等的部分,這取決于信號層是如何進(jìn)入和離開導(dǎo)通孔的。這些部分中唯一的區(qū)別

2014-12-09 15:58:33

打孔換層,換層優(yōu)先選擇兩邊是GND的層面處理。盡量收發(fā)信號布線在不同層,如果空間有限,需收發(fā)信號走線同層時,應(yīng)加大收發(fā)信號之間的布線距離。

針對以上高速信號還有如下方面的要求:

01

BGA焊盤區(qū)域挖

2023-08-03 18:18:07

BGA是一種芯片封裝的類型,英文 (Ball Grid Array)的簡稱,封裝引腳為球狀柵格陣列在封裝底部,引腳都成球狀并排列成一個類似于格子的圖案,由此命名為BGA。主板控制芯片諸多采用此類

2023-03-24 11:51:19

/1508.html直播背景為了解決廣大PCB設(shè)計工程師BGA主控扇出困難、扇出不美觀、達(dá)不到高速信號要求的困擾,本次直播詳細(xì)講述如何快速的從BGA扇出、理清布線思路、快速完成PCB布線。直播過程中都是以實(shí)際

2021-03-30 22:03:56

焊點(diǎn)質(zhì)量 ,尤其對BGA、DCA元件的焊點(diǎn)檢查,作用不可替代,無須測試模具,缺點(diǎn)是價格目前相當(dāng)昂貴。

BGA焊接不良原因

1、BGA焊盤孔未處理

BGA焊接的焊盤上有孔,在焊接過程中 焊球會與焊料

2023-05-17 10:48:32

裝配封裝技術(shù)。在封裝底部,引腳都成球狀并排列成一個類似于格子的圖案,由此命名為BGA。目前主板控制芯片組多采用此類封裝技術(shù),材料多為陶瓷。采用BGA技術(shù)封裝的內(nèi)存,可以使內(nèi)存在體積不變的情況下,內(nèi)存容量

2018-09-18 13:23:59

請問各位,BGA扇孔為什么扇的孔比我規(guī)定要大啊,跟視頻中差距好大啊。

2019-07-25 00:10:10

焊接BGA的層為何要繪制禁止敷銅區(qū)?

2019-08-26 23:48:57

PCB設(shè)計時,在那種情況下會使用跨層盲孔(Skip via)的設(shè)計?一般疊構(gòu)和孔徑怎么設(shè)計?

2023-11-09 16:21:10

過多損失掉,因此在布線前期就需要規(guī)劃選擇一個合適的走線層。這里我們通過仿真軟件來對比表層走線與內(nèi)層走線,誰更適合用于高速信號的傳輸。首先搭建疊層模板,分別是表層走線模板和內(nèi)層走線的層疊模板:為了更接近

2020-03-09 10:57:00

4x7628pp,滑片2mm板厚極限14層,1.6mm一般最多12層,做14層阻抗不易控制高速要求:信號層與地層盡量近電源與地盡量近,并有一處相鄰保證地平面足夠大,并完整保證相鄰的兩個信號層盡量遠(yuǎn),布線走線為交叉走線,盡量滿足3W規(guī)則,不行則相互錯開信號層如果以VCC為參考平

2022-03-02 06:09:06

的引腳難以布線,需換層打孔布線。在BGA引腳間距小無法扇出時,解決的方法只有一種,哪就是打盤中孔。還有就是BGA背面放置濾波電容,當(dāng)BGA引腳多時背面的濾波電容無法避開引腳扇出的過孔,只能接受濾波電容的焊

2022-10-28 15:53:31

,表層是用來走線焊接元器件的,內(nèi)層則是規(guī)劃電源/接地層,該層僅用于多層板,主要用于布置電源線和接地線。我們稱之為雙層板、四層板和六層板,通常指信號層和內(nèi)部電源/接地層的數(shù)量。內(nèi)層設(shè)計在高速信號,試中信號

2022-12-08 11:49:11

內(nèi)電層的地孔,是全連接好?還是十字花好?為什么啊?請各位大神解答一下,謝謝

2017-05-10 10:02:28

。誤區(qū)二:有了仿真軟件平臺就可以做好高速 PCB 設(shè)計? EDA 設(shè)計軟件平臺集成了高速信號仿真功能,這對于高速 PCB 設(shè)計的規(guī)則制定與執(zhí)行,信號質(zhì)量仿真與評估都有很大的幫助。 但是,在 PCB 實(shí)際

2022-04-28 16:21:41

板的布線層層數(shù);(3)信號質(zhì)量控制:對于高速信號比較集中的PCB設(shè)計,如果重點(diǎn)關(guān)注信號質(zhì)量,那么就要求減少相鄰層布線以降低信號間串?dāng)_,這時布線層層數(shù)與參考層層數(shù)(Ground層或Power層)的比例

2017-03-01 15:29:58

一:差分線、蛇形線(等長線、高速線)二:四層板3:四層板的Gerber文件四:六層板介紹 差分線、蛇形線(等長線、高速線) 差分線:消除共模干擾信號,需要走差分線的線:USB、網(wǎng)絡(luò)接口、音頻

2015-06-18 15:50:34

我要設(shè)計一個四層的PCB板子,底層用于焊接面(全部做成BGA焊盤),也就是底層用作元件的BGA焊盤,焊盤上不想有孔。我暫時考慮用盲孔,然后用銅填孔$ L& P0 k. m" T8 SI4 m" q, b' @9 E請教大家有什么更好的辦法把頂層或內(nèi)層走線引到底層,謝謝。

2014-10-28 16:27:36

在高速PCB設(shè)計中,信號層的空白區(qū)域可以敷銅,而多個信號層的敷銅在接地和接電源上應(yīng)如何分配?

2009-09-06 08:39:35

正確,因?yàn)樗?b class="flag-6" style="color: red">信號和電源彼此靠得很近,因此極具挑戰(zhàn)性。對信號特性的正確了解有助于作出在功能方面哪個網(wǎng)絡(luò)具有更高優(yōu)先級的決定。在靠近BGA的層中使用大面積的接地平面有助于解決大多數(shù)信號完整性問題。盲孔

2018-01-24 18:11:46

原子哥,我也想搞個圖案在PCB板上,就像ALIENTEK MINI板上的外星人一樣,是怎么弄上去的?

2019-10-12 10:22:21

,在機(jī)械層畫一個“機(jī)械孔”。但是,使用這個方法時,經(jīng)常有一點(diǎn)想不明白,明明在Machinal 1層中畫了“機(jī)械孔”,但是進(jìn)入3D效果預(yù)覽時,卻發(fā)現(xiàn)沒有生成機(jī)械孔”,本以為是軟件3D預(yù)覽的問題,一直沒想

2019-07-10 06:53:29

使用貼片電容。可把貼片電容放在PCB板背面即焊接面,貼片電容到通孔用寬線連接并通過通孔與電源、地層相連。 2、考慮電源分布的布線規(guī)則 分開模擬和數(shù)字電源層 高速高精度模擬元件對數(shù)字信號很敏感

2017-12-04 14:19:43

作者:一博科技高速先生自媒體成員 黃剛本文分享一種高速串行PCB設(shè)計中不用增加工藝成本又能很好的改善原設(shè)計信號質(zhì)量的辦法哈! 有沒有遇到過這么一種情況。進(jìn)行高速串行信號的布線時,如果收發(fā)器件都放在

2021-11-11 11:56:56

的引腳難以布線,需換層打孔布線。在BGA引腳間距小無法扇出時,解決的方法只有一種,哪就是打盤中孔。還有就是BGA背面放置濾波電容,當(dāng)BGA引腳多時背面的濾波電容無法避開引腳扇出的過孔,只能接受濾波電容的焊

2022-10-28 15:55:04

對于4層板,接地孔必須大于TOP孔???有這種說法嗎???

2014-12-26 10:30:43

面過窄會引起寄生參數(shù)同時增加衰減;地平面、頂層的地已經(jīng)連接兩層的過孔,應(yīng)盡量保證射頻信號線做到完全的“屏蔽”,以增加產(chǎn)品的EMC能力。同時建議通過地孔將電源平面包裹起來,避免不必要的電子輻射。通常電源層

2022-11-07 20:48:45

鉆孔的距離是否能安全生產(chǎn)。如果BGA中高速線孔不做背鉆是否在BGA中出雙線設(shè)計。圖56、高速線要注意收發(fā)信號同層長距離(200mil以上)布線,如果層數(shù)不夠多,必須要同層走線也需要把間距加大,能調(diào)多大

2016-11-07 16:22:26

以上為8層板頂層部分元器件排列框圖,第2層左半部分為模擬地,右半部分為數(shù)字地,第3層、第6層為信號層,請問第三層的模擬地下,能否通過數(shù)字信號線路,如果不能通過,在第6層走數(shù)字信號線,該數(shù)字信號線應(yīng)該距離旁邊的模擬地通孔多遠(yuǎn),數(shù)字信號頻率分別為5M、0.5M,

2018-08-15 06:58:10

要注意,盤中孔是盲孔,同時通孔也有盤中孔時,要把所有的盤中孔挑出來做樹脂塞孔,切記不要忽略BGA上的孔,是不做樹脂塞孔的。

2

線路制作

樹脂塞孔的層線路,需要補(bǔ)償1.5-2mil,盡量多補(bǔ)。

3

阻焊

2023-05-05 10:55:46

求推薦 led芯片通過光蝕刻形成通孔和采用剝離工藝形成具有布線圖案的電極的相關(guān)書籍

2019-04-15 23:38:47

偏問題,適用于線寬較窄的高密度PCB。 所謂增層法,是以雙面或四面電路板為基礎(chǔ),采納逐次壓合的觀念,于其板外逐次增加線路層,并以非機(jī)械鉆孔式之盲孔做為增層間的互連,而在部分層次間連通的盲孔與埋孔,可

2019-12-13 15:56:04

添加測試點(diǎn)會不會影響高速信號的質(zhì)量?

2009-09-06 08:40:20

問:添加測試點(diǎn)會不會影響高速信號的質(zhì)量?答:至于會不會影響信號質(zhì)量就要看加測試點(diǎn)的方式和信號到底多快而定。基本上外加的測試點(diǎn)(不用線上既有的穿孔(via or DIP pin)當(dāng)測試點(diǎn))可能加在

2019-08-30 00:45:16

的決定。 在靠近BGA的層中使用大面積的接地平面有助于解決大多數(shù)信號完整性問題。盲孔的一個最大好處是,在盲孔/埋孔中消除了分支長度,這對高頻信號來說尤其重要。 本文小結(jié) 用于嵌入式設(shè)計的BGA封裝

2018-09-20 10:55:06

、電源的分割,一般的BGA都有IO電壓和Core電壓,需要在電源層將其分隔開。7、阻抗的控制,如果BGA的某些信號線需要特殊阻抗,要注意線徑和線寬,并計算好阻抗,連同PCB的Stack一起計算。8

2011-10-21 09:48:17

使用堅決避免的。這些過孔將影響到電源完整性,從而導(dǎo)致信號完整性問題,危害很大。打地孔,通常發(fā)生在如下的三種情況:1、打地孔用于散熱;2、打地孔用于連接多層板的地層;3、打地孔用于高速信號的換層的過孔的位置

2018-12-03 22:16:47

請問,BGA扇孔后,對線寬規(guī)則改變,重新扇孔無反應(yīng),報錯,綠色,怎么回事

2019-09-04 05:37:07

請問在BGA扇孔后,想快速旋轉(zhuǎn)(90度)一下bga焊盤和扇的孔之間的那根連線,要怎么操作?

2019-06-14 05:27:59

求8層Altium designer HDI盲埋孔飛行控制板實(shí)戰(zhàn)高速pcb設(shè)計教程的百度云地址

2019-09-20 05:35:47

化處理加工工藝對信號質(zhì)量有影響PCB 加工過程中,為了提高 PCB 銅皮層與介質(zhì)層的結(jié)合強(qiáng)度,降低 PCB 分層風(fēng)險,都會有粗化 / 棕化處理工藝,就是通過打磨或者腐蝕的方式使銅皮表面變得粗糙。在高速

2020-11-30 09:51:58

針對Spartan-3E FT256 BGA封裝的四層和六層高速PCB設(shè)計本應(yīng)用指南針對 FT256 1 mm BGA 封裝的 Spartan?-3E FPGA,討論了低成本、四至六層、大批量

2009-10-10 13:06:48

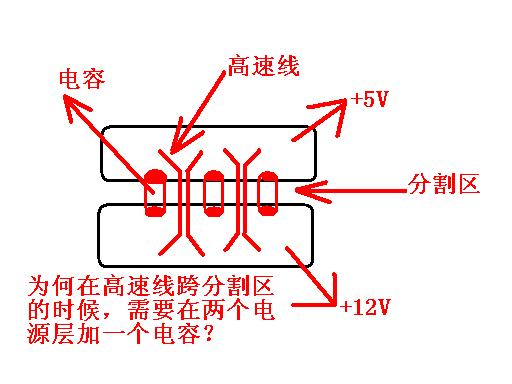

高速信號號在電源層分割時的處理辦法

2007-11-08 09:13:59 3681

3681

總的來說,設(shè)計好一個高質(zhì)量的高速PCB板,應(yīng)該從信號完整性(SI---Signal Integrity)和電源完整性(PI---Power Integrity )兩個方面來考慮。盡管比較直接的結(jié)果是

2019-05-22 14:50:37 2443

2443 在高速PCB設(shè)計中,“信號”始終是工程師無法繞開的一個知識點(diǎn)。不管是在設(shè)計環(huán)節(jié),還是在測試環(huán)節(jié),信號質(zhì)量都值得關(guān)注。在本文中,我們主要來了解下影響信號質(zhì)量的5大問題。

2019-10-10 17:21:31 5023

5023 本文針對高速BGA封裝與PCB差分互連結(jié)構(gòu)進(jìn)行設(shè)計與優(yōu)化,著重分析封裝與PCB互連區(qū)域差分布線方式、信號布局方式、信號孔/地孔比、布線層與過孔殘樁這四個方面對高速差分信號傳輸性能和串?dāng)_的具體

2020-09-28 11:29:58 2296

2296

在高速PCB設(shè)計中,“信號”始終是工程師無法繞開的一個知識點(diǎn)。不管是在設(shè)計環(huán)節(jié),還是在測試環(huán)節(jié),信號質(zhì)量都值得關(guān)注。

2020-11-20 10:55:07 3418

3418 在高速PCB設(shè)計中,“信號”始終是工程師無法繞開的一個知識點(diǎn)。不管是在設(shè)計環(huán)節(jié),還是在測試環(huán)節(jié),信號質(zhì)量都值得關(guān)注。在本文中,我們主要來了解下影響信號質(zhì)量的5大問題。 根據(jù)目前工作的結(jié)論,信號質(zhì)量

2020-12-22 16:34:40 1472

1472

在高速PCB設(shè)計中,“信號”始終是工程師無法繞開的一個知識點(diǎn)。不管是在設(shè)計環(huán)節(jié),還是在測試環(huán)節(jié),信號質(zhì)量都值得關(guān)注。在本文中,我們主要來了解下影響信號質(zhì)量的5大問題。根據(jù)目前工作的結(jié)論,信號質(zhì)量常見的問題主要表現(xiàn)在五個方面:過沖,回沖,毛刺,邊沿,電平

2020-12-24 18:20:46 840

840 針對高速BGA封裝與PCB差分互連結(jié)構(gòu)進(jìn)行設(shè)計與優(yōu)化,著重分析封裝與PCB互連區(qū)域差分布線方式,信號布局方式,信號孔/地孔比,布線層與過孔殘樁這四個方面對高速差分信號傳輸性能和串?dāng)_的具體影響。

2022-08-26 16:32:04 534

534 目前對于DDR4、DDR5等并行信號,信號速率越來越高,電源性能要求也越來越高,今天我們就來看看電源噪聲對信號質(zhì)量的影響;

2023-04-21 09:47:46 1289

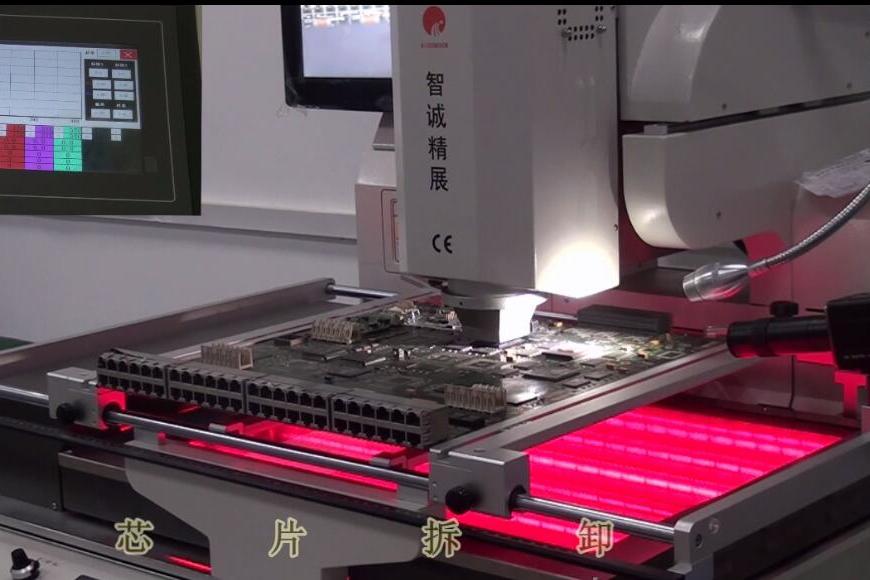

1289 一、檢查物料質(zhì)量 檢查BGA返修設(shè)備的物料質(zhì)量是確保設(shè)備質(zhì)量的重要步驟。一般來說,物料質(zhì)量應(yīng)通過檢測來確認(rèn),以確保其符合要求的性能和可靠性。比如,可以檢查PCB板的尺寸和表面質(zhì)量,檢查芯片的質(zhì)量

2023-04-24 17:07:58 398

398

高速光模塊主板BGA芯片底填膠點(diǎn)膠應(yīng)用由漢思化學(xué)提供客戶公司是研究、開發(fā)、生產(chǎn)、銷售計算機(jī)網(wǎng)絡(luò)設(shè)備及零部件、通訊設(shè)備及零部件并提供技術(shù)服務(wù)。其中通訊設(shè)備用到我公司的底部填充膠水。客戶產(chǎn)品是通訊設(shè)備

2023-03-14 17:28:39 587

587

電子發(fā)燒友App

電子發(fā)燒友App

評論