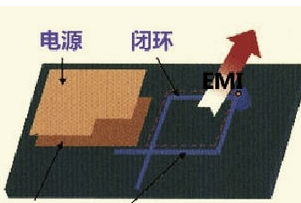

在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。##在高速的PCB設計中,時鐘等關鍵

2016-04-26 14:00:01 5104

5104

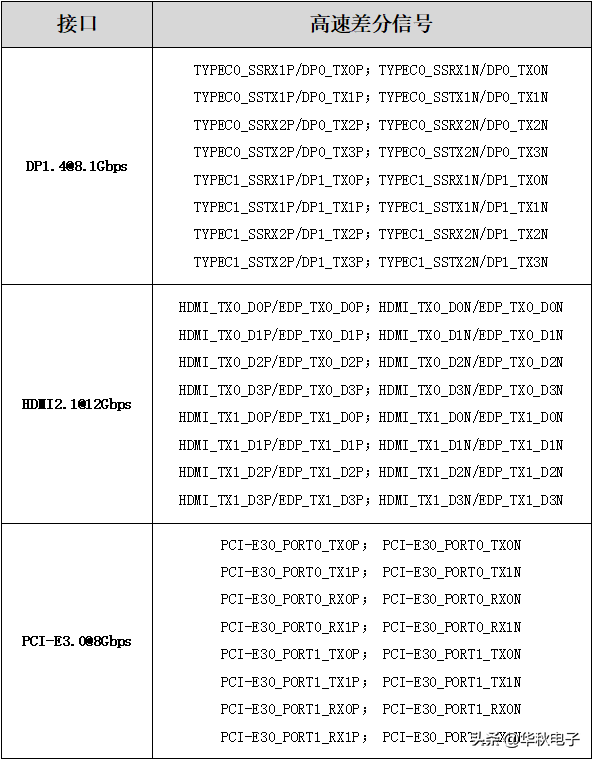

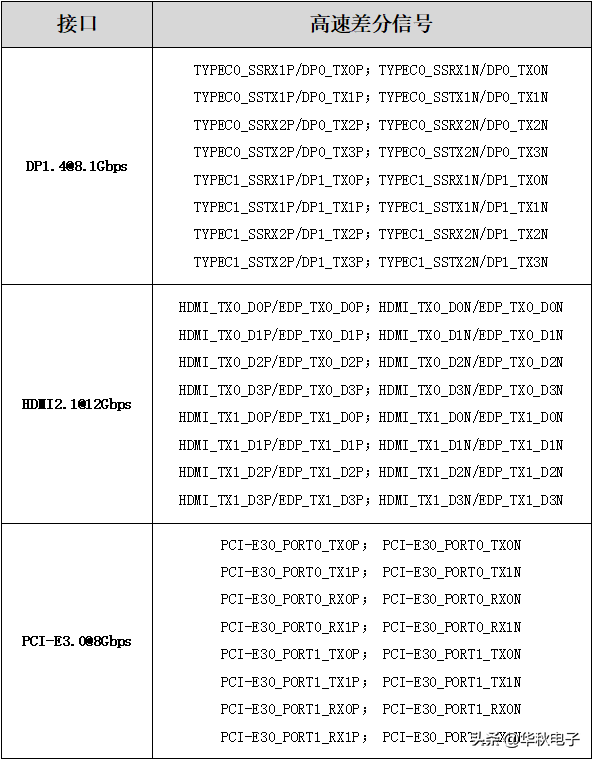

接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量少打孔

2023-08-02 08:41:11 1432

1432

PCB板的設計是電子工程師的必修課,而想要設計出一塊完美的PCB板也并不是看上去的那么容易。一塊完美的PCB板不僅需要做到元件選擇和設置合理,還需要具備良好的信號傳導性能。本文將會就PCB高速信號電路設計中的布線技巧知識,展開詳細介紹和分享,希望能夠對大家的工作有所幫助。

2016-03-23 11:15:27 3244

3244 本文主要詳解PCB設計高速模擬輸入信號走線,首先介紹了PCB設計高速模擬輸入信號走線方法,其次闡述了九大關于PCB設計高速模擬輸入信號走線規則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

PCB作為電子系統的載體,承載著系統中的工作芯片、傳輸線、供電網絡等關鍵部件,其本身的質量關系著系統的可靠性與穩定性。隨著信號頻率的升高,PCB的電磁兼容問題也越來越突出。PCB高速信號不連續參考面、電源抖動噪聲等非理想因素都會導致電磁能量通過傳導、輻射的方式散發出去,影響其他部件和系統的正常工作。

2022-07-18 12:49:32 3775

3775 當高速信號發生跨溝現象時,整個電流的環路面積將增加,通常系統的EMC輻射也將增加。同時傳輸線的特征阻抗也將發生變化(如下圖2所示為信號線阻抗變化曲線),信號遇到傳輸線特征阻抗突變點時將發生發射、振鈴等信號完整性問題。

2022-09-15 11:05:12 794

794 在某單板開發工作中,高速信號線非常多,為了保證單板的EMI性能,在PCB布線中,盡可能保證信號線走內部信號層,防止因為過多表層高速信號線產生的EMC問題無法定位。但是該方案帶來的直接問題是高速信號

2022-10-20 10:41:47 2554

2554

通常PCB上的打過孔換層會引起鏡像平面的非連續性,這就會導致信號的最佳回流途徑被破壞。

2023-01-10 10:19:31 1431

1431 如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-01 18:10:06 1263

1263

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-03 17:13:35 644

644

的數字系統的時鐘頻率高于100MHz。當系統時鐘頻率超過50 MHz時,將出現傳輸線效應和信號的完整性問題;而當系統時鐘頻率達到120 MHz時,基于傳統方法設計的PCB將無法工作,必須使用高速電路設計

2018-11-27 15:24:32

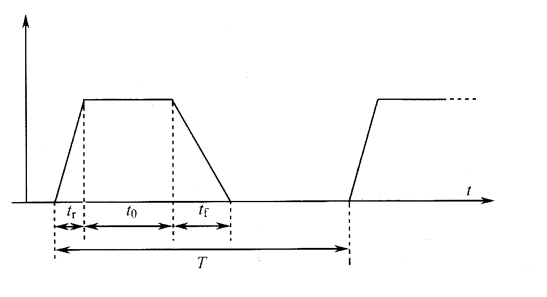

標準時鐘信號波形是梯形的周期數字脈沖,如圖1所示,脈沖周期為T;信號上升時間為tr;信號下降時間為tf。假設tr=tf,高電平維持時間為to,定義數字脈沖寬度為τ=to+tr。 圖1 數字時鐘

2018-11-27 15:26:18

PCB高速信號防靜電處理都有哪些做法,有加一些防靜電的ESD的器件,畫板的時候有哪些處理的方法可以防靜電

2023-04-07 17:29:11

PCB板上的高速信號需要進行仿真串擾嗎?

2023-04-07 17:33:31

硬件工程師做久了自然有自己處理電路板的一套方法,也許不是最好的辦法,自己卻能理解其中的意義。但是工作中還是要按照最完美的辦法進行操作,本期我們就來了解一下關于高速信號走線準則到底有哪幾條是你不清楚的?

2020-10-30 08:33:48

確保信號完整性的一個重要部分是信號走線的物理布線。PCB設計人員經常承受壓力,不僅要縮小設計,還要保持信號完整性。找到平衡點就是要知道問題可能發生的位置以及在系統出現故障之前可以推送信封的距離

2023-04-12 15:20:37

高速PCB信號走線的九條規則.pdf(220.78 KB)

2019-09-16 07:26:43

高速PCB設計之一 何為高速PCB設計電子產品的高速化、高密化,給PCB設計工程師帶來新的挑戰。PCB設計不再是產品硬件開發的附屬,而成為產品硬件開發中“前端IC,后端PCB,SE集成”3個環節中

2014-10-21 09:41:25

高速PCB設計的信號完整性問題 隨著器件工作頻率越來越高,高速PCB設計所面臨的信號完整性等問題成爲傳統設計的一個瓶頸,工程師在設計出完整的解決方案上面臨越來越大的挑戰。盡管有關的高速仿真工具

2012-10-17 15:59:48

高速pcb的信號完整性問題主要有哪些?應如何消除?

2023-04-11 15:06:07

高速信號PCB布線中降低寄生電感的具體措施

2021-03-08 08:49:46

影響高速信號鏈設計性能的機制是什么?高速ADC設計中的PCB布局布線技巧有哪些?

2021-04-21 06:29:52

振鈴、反射和串擾。如果不考慮高速信號布局布線的特殊性,設計出的電路板將不能正常工作。因此PCB板的設計成功是DSPs電路設計過程中非常關鍵的一個環節。 1 傳輸線效應 1.1信號完整性 信號

2018-09-12 15:09:57

`關于HyperLynx仿真的分析,當PCB發展到今天的時候,信號速度越來越快,信號的頻率越來越快,很多時候我們都無法去琢磨,在PCB板子設計好的時候我們都可以進行熱仿真,關鍵信號仿真,因為文件比較大,我們暫時無法上傳資料,有需要資料的人可以加QQ群:78297712 PCB高速信號完整性分析群78`

2015-05-17 17:03:52

本文針對以上問題對本人設計的主板PCB的高速信號基本噪聲,高速內存時序和電源分配系統噪聲進行分析和設計;采用軟件仿真的方法對問題進行分析,得出設計解決方案,并將仿真結果轉化為設計約束規則指導PCB布局布線設計,最后通過物理測試對設計進行了驗證。回復帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:02:40

`隨著PCB高速信號設計越發普遍,電子電路的設計越發面臨信號完整性、電源完整性、熱、電磁兼容等問題挑戰。在設計中引入仿真驗證手段,將大大提升產品開發效率,設計正確性,實現產品最快的推向市場

2018-02-13 13:57:12

年限:7年硬件開發1、熟練使用Altium、Allegro、PADS等電路開發軟件,Layout完成4、6、8層PCB,高速信號、模擬信號、音頻信號處理2、豐富的產品開發經驗,有過量產經驗3、有過CE,CCC,TUV等認證經歷QQ:714-277-950希望跟大家合作。。。。。。

2017-07-08 15:46:54

高速PCB設計是一個相對復雜的過程,由于高速PCB設計中需要充分考慮信號、阻抗、傳輸線等眾多技術要素,常常成為PCB設計初學者的一大難點,本文提供的幾個關于高速PCB設計的基本概念及技術要點

2023-04-19 16:05:28

),很多人在建立好CAE之后就開始填封裝了然后導入到PCB里面就發現錯了,其實CAE只是表現了元件的外殼類型并不是元件歡迎加入PCB高速信號完整性分析群 78297712

2015-05-17 17:34:29

本文主要分析一下在高速PCB設計中,高速信號與高速PCB設計存在一些理解誤區。誤區一:GHz 速率以上的信號才算高速信號? 提到“高速信號”,就需要先明確什么是“高速”,MHz 速率級別的信號算高速

2022-04-28 16:21:41

通用的高速信號PCB設計處理原則有:(1)層面的選擇:處理高速信號優先選擇兩邊是GND的層面處理(2)處理時要優先考慮高速信號的總長(3)高速信號Via數量的限制:高速信號允許換一次層,換層時加

2017-02-07 09:40:04

一、PCB設計時高速信號和低速信號區分在高速PCB電路設計過程中,經常會遇到信號完整性問題,導致信號傳輸質量不佳甚至出錯。那么如何區分高速信號和普通信號呢?很多人覺得信號頻率高的就是高速信號,實則

2021-11-11 07:59:58

解決高速PCB設計信號問題的全新方法

2021-04-25 07:56:35

高速數字PCB設計信號完整性解決方法

2021-03-29 08:12:25

作為一名合格的、優秀的PCB設計工程師,我們不僅要掌握高速PCB設計技能,還需要對其他相關知識有所了解,比如高速PCB材料的選擇。這是因為,PCB材料的選擇錯誤也會對高速數字電路的信號傳輸性能造成不良影響。

2021-03-09 06:14:27

對于高速信號,pcb的設計要求會更多,因為高速信號很容易收到其他外在因素的干擾,導致實際設計出來的東西和原本預期的效果相差很多。 所以在高速信號pcb設計中,需要提前考慮好整體的布局布線,良好

2023-04-12 14:22:25

最近要搞告訴信號的東西,但是從來沒有布過高速信號的PCB,求大神指教

2013-08-30 14:10:03

本文主要分析一下在高速 PCB 設計中,高速信號與高速 PCB 設計存在一些理解誤區。誤區一:GHz 速率以上的信號才算高速信號?提到“高速信號”,就需要先明確什么是“高速”,MHz 速率級別的信號

2020-11-30 09:51:58

高速PCB板的電源布線設計:本文分析討論了高速PCB板上由于高頻信號干擾和走線寬度的減小而產生的電源噪聲和壓降,并提出了高速PCB的電源模型,采用電源總線網絡布線,選取合適

2009-03-24 14:08:40 0

0 針對高速PCB信號測試所面臨的問題,介紹基于虛擬儀器的高速PCB信號檢測方法,利用虛擬儀器的數字化技術結合計算機軟件處理分析,為高速PCB信號測試和設計階段的邏輯功能驗證

2009-04-03 09:08:20 15

15 本文介紹了一種基于信號完整性計算機分析的高速數字信號 PCB板的設計方法。在這種設計方法中,首先將對所有的高速數字信號建立起PCB板級的信號傳輸模型,然后通過對信號完

2009-04-25 16:49:13 37

37 本文針對高速PCB板信號接地設計中存在接地噪聲及電磁輻射等問題,提出了高速PCB接地模型,并從PCB設計中布線策略的分析和去耦電容的使用等幾個方面討論了解決高速PCB板的接地噪聲

2009-12-08 14:53:23 63

63 高速設計與PCB仿真流程:1.1 高速信號與高速設計.4 1.1.1 高速信號的確定5 1.1.2 邊緣速率引發高速問題5 1.1.3 傳輸線效應6 1.2 高速 PCB 仿真的重要

2010-04-05 06:33:19 16

16 高速信號走線規則教程

隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的關注。高速PCB設計的成功,對EMI

2009-04-15 08:49:27 2798

2798

高速PCB中的信號回流及跨分割

這里簡單構造了一個“場景”,結合下圖介紹一下地回流和電源回流以及一些跨分割問題。為方便

2009-11-17 08:56:03 1053

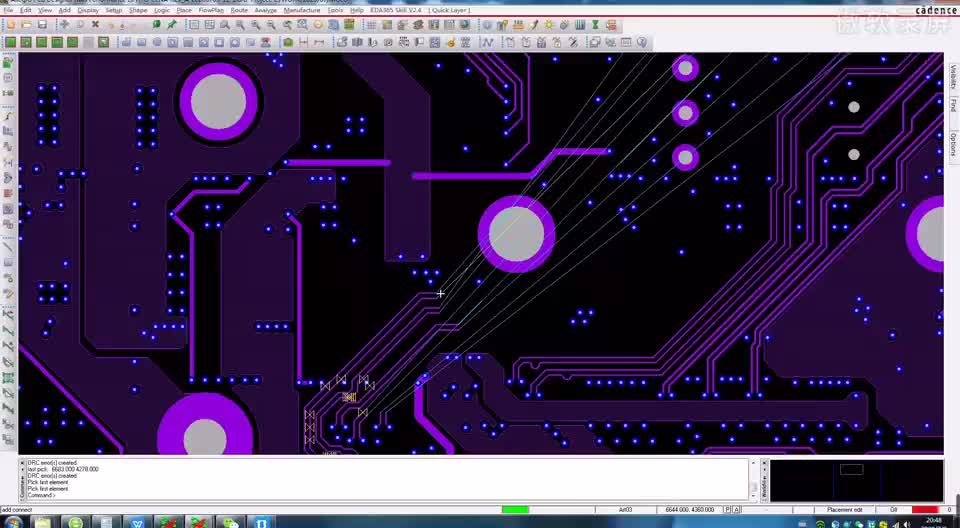

1053 基于Cadence的高速PCB設計

隨著人們對通信需求的不斷提高,要求信號的傳輸和處理的速度越來越快.相應的高速PCB的應用也越來越廣,設計也越來越

2009-12-12 17:50:27 954

954 分析了過孔的等效模型以及其長度、直徑變化對高頻信號的影響,采用Ansoft HFSS對其仿真驗證,提出在高速PCB設計中具有指導作用的建議。

2012-01-16 16:24:13 56

56 信號完整性分析及其在高速PCB設計中的應用,教你如何設計高速電路。

2016-04-06 17:29:45 15

15 高速PCB電路板的基本理論和信號完整性設計

2017-09-18 09:20:22 25

25 描述了高速PCB電路板信號完整性設計方法。 介紹了信號完整性基本理論, 重點討論了如何采用高速PCB設計方法保證高速數采模塊的信號完整性

2017-11-08 16:55:13 0

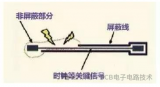

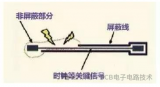

0 規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有

2017-11-25 07:43:00 7508

7508

高速 PCB 信號完整性仿真分析.pdf

2018-05-07 14:52:31 48

48 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的重視。

2018-12-06 08:59:43 17197

17197 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 隨著PCB高速信號速率的增加,PCB電路板正不斷向更高密度化、輕薄化及功能越來越多的方向發展,未來高速高密度多層PCB板或將成為高質量PCB出廠的唯一指標。目前高速PCB電路板正不斷向消費電子領域

2020-09-15 10:02:55 1594

1594 在高速PCB電路設計過程中,經常會遇到信號完整性問題,導致信號傳輸質量不佳甚至出錯。

2019-12-10 17:25:23 1655

1655 可見數字信號的頻譜并不局限于其時鐘頻率,而是覆蓋很寬的頻率范圍。

2019-09-23 14:11:44 3071

3071

在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環節,還是在測試環節,信號質量都值得關注。在本文中,我們主要來了解下影響信號質量的5大問題。

2019-10-10 17:21:31 5023

5023 本文主要分析一下在高速PCB設計中,高速信號與高速PCB設計存在一些理解誤區。 誤區一:GHz速率以上的信號才算高速信號? 提到高速信號,就需要先明確什么是高速,MHz速率級別的信號算高速、還是

2019-11-05 11:27:17 10310

10310

在高速的PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。

2019-12-16 14:52:30 2972

2972

規則一:高速信號走線屏蔽規則 如上圖所示: 在高速的PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線,每1000mil,打孔

2020-02-14 11:53:40 11779

11779 利用TDR(Time Domain Reflectometry)時域反射計測試PCB板、線纜和連接器的特征阻抗是IPC(美國電子電路與電子互連行業協會)組織指定的特征阻抗量測方法,在電子測量領域得到了廣泛的應用和普及。

2020-09-21 11:13:31 4916

4916 ,以使布局符合電路功能和生產要求的要求。 它們的不正確放置會產生電路兼容性問題,信號完整性問題,并導致PCB設計失敗。時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。 (1)合

2022-12-09 18:04:41 969

969 在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環節,還是在測試環節,信號質量都值得關注。

2020-11-20 10:55:07 3418

3418 本文檔的主要內容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現優化設計。

2021-01-13 17:00:59 25

25 在高速PCB設計中,差分信號的應用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。

2021-03-23 14:40:47 2760

2760 電子發燒友網為你提供詳解PCB高速信號電路設計中的布線規則資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-25 08:47:42 36

36 在高速PCB電路設計過程中,經常會遇到信號完整性問題,導致信號傳輸質量不佳甚至出錯。那么如何區分高速信號和普通信號呢?

2022-02-09 10:02:28 4

4 高速電路信號完整性分析與設計—PCB設計1

2022-02-10 17:31:51 0

0 高速電路信號完整性分析與設計—PCB設計2

2022-02-10 17:34:49 0

0 數字電路的原理圖中,數字信號的傳播是從一個邏輯門向另一個邏輯門,信號通過導線從輸出端送到接收端,看起來似乎是單向流動的,許多數字工程師因此認為回路通路是不相關的。

2022-03-21 11:03:20 3012

3012 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的 EMI 問題,也來越受

到電子工程師的關注。

高速 PCB 設計的成功,對 EMI 的貢獻越來越受到重視,幾乎 60%的 EMI 問題可

以通過高速 PCB 來控制解決

2022-04-22 11:54:57 0

0 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的關注。

2022-08-14 12:04:27 1218

1218 通常PCB上的打過孔換層會引起鏡像平面的非連續性,這就會導致信號的最佳回流途徑被破壞。 我們都知道,信號打孔換層會改變信號的回流路徑,如果信號換層,回流路徑也跟著換層,但是在信號換層處過孔不能將信號回路連通起來,將引起信號回路面積增大,從而導致EMC問題。

2022-12-20 09:59:30 2864

2864 跨分割,對于低速信號可能沒有什么關系,但是在高速數字信號系統中,高速信號是以參考平面作為返回路徑,就是回流路徑。

2023-02-21 13:44:36 1168

1168 在現代電子設計中,高速信號的傳輸已成為不可避免的需求。高速信號傳輸的成功與否,直接影響整個電子系統的性能和穩定性。因此,PCB設計中的高速信號傳輸優化技巧顯得尤為重要。本文將介紹PCB設計中的高速信號傳輸優化技巧。

2023-05-08 09:48:02 1143

1143 ? 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的重視。高速pcb設計的成功,對EMI的貢獻越來越受到重視,幾乎90%的EMI問題可以通過高速PCB來控制

2023-05-22 09:15:58 834

834

的典型應用一種是檢測地下鋪設的電纜的故障點位置,還有就是PCB高速信號走線的阻抗匹配分析。我們使用LOTO示波器的OSCH02型號,利用一些簡單的隨手可以找到的材料,

2022-05-27 00:00:00 1056

1056

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。高速信號布線時盡量少打孔

2023-08-03 17:31:07 662

662

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-03 18:15:02 486

486 pcb上的高速信號需要仿真串擾嗎? 在數字電子產品中,高速信號被廣泛應用于芯片內部和芯片間的數據傳輸。這些信號通常具有高帶寬,并且需要在特定的時間內準確地傳輸數據。然而,在高速信號傳輸的過程中,會出

2023-09-05 15:42:31 472

472 PCB高速信號在當今的一個pcb設計中顯然已成為主流,一名優秀的PCB工程師,除了在實戰項目慢慢積累設計PCB高速信號的經驗外,還需通過不斷學習來提升自己的知識儲存和專業技能。本文捷多邦小編就給大家科普一下PCB高速信號的一些相關布線知識。

2023-09-15 10:19:18 720

720 關于高速串行信號隔直電容的PCB設計注意點? 在高速串行信號傳輸中,隔直電容是一種常見的解決信號干擾問題的方法。由于高速信號傳輸時會產生電磁干擾和相鄰信號交叉干擾,隔直電容可以將交流信號通路隔離

2023-10-24 10:26:08 490

490 基于信號完整性分析的高速數字PCB的設計方法SIPCB

2022-12-30 09:21:20 3

3 對于高速信號,pcb的設計要求會更多,因為高速信號很容易收到其他外在因素的干擾,導致實際設計出來的東西和原本預期的效果相差很多。 所以在高速信號pcb設計中,需要提前考慮好整體的布局布線,良好的布局

2023-11-06 10:04:04 340

340

在高速PCB設計中,信號層的空白區域可以敷銅,而多個信號層的敷銅在接地和接電源上應如何分配? 在高速PCB設計中,信號層的空白區域可以敷銅,而多個信號層的敷銅在接地和接電源上應該經過合理分配。接地

2023-11-24 14:38:21 635

635 對于長距離傳輸的高速信號,尤其是背板之類的,需要特別注意損耗帶來的影響,避免高頻分量過多損失掉,因此在布線前期就需要規劃選擇一個合適的走線層。

2023-12-13 18:21:40 306

306

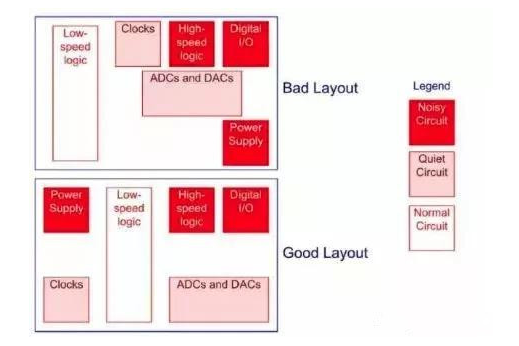

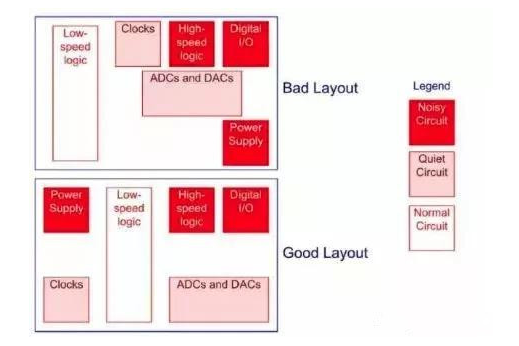

隔離一塊PCB板上的元器件有各種各樣的邊值(edge rates)和各種噪聲差異。對改善SI直接的方式就是依據器件的邊值和靈敏度,通過PCB板上元器件的物理隔離來實現。

2024-01-02 15:47:27 145

145

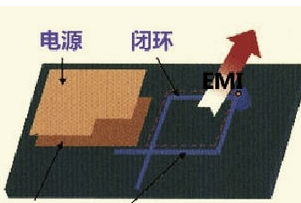

由于 PCB 板的密度越來越高,許多 PCB LAYOUT 工程師在走線的過程中,較容易出現一種失誤,即時鐘信號等高速信號網絡,在多層的 PCB 走線的時候產生了閉環的結果,這樣的閉環結果將產生環形天線,增加 EMI 的輻射強度。

2024-01-08 15:33:04 144

144

在高速的 PCB 設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成 EMI 的泄漏。

2024-01-10 16:03:05 369

369

電子發燒友App

電子發燒友App

評論