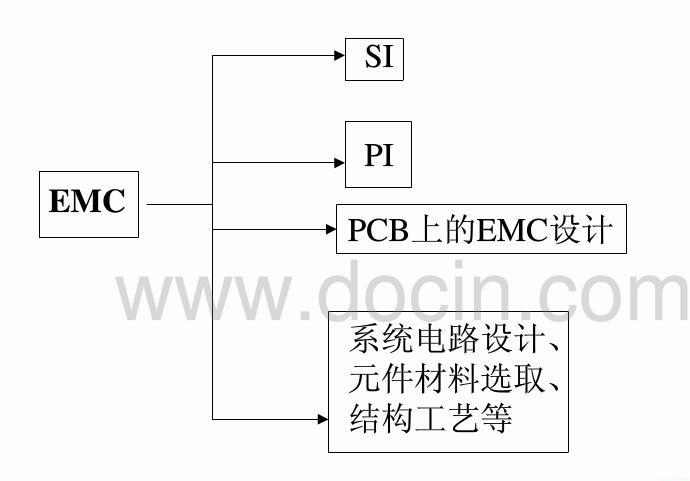

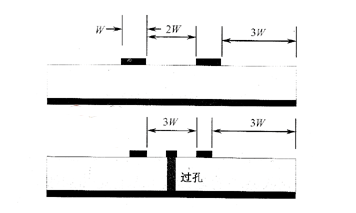

高速PCB走線的3-W原則

- 信號(75276)

- 走線(23300)

- PCB(13204)

相關推薦

9大硬件工程師談高速PCB信號走線規則

的PCB走線的時候一旦產生了開環的結果,將產生線形天線,增加EMI的輻射強度。圖3 開環規則規則四:高速信號的特性阻抗連續規則高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射

2018-11-28 11:14:18

3W原則是什么

3W原則在PCB設計中為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W規則。3W原則是指多個高速信號線長距離走線的時候,其間距...

2022-01-26 06:50:22

PCB LAYOUT 中的直角走線、差分走線和蛇形線

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中

2015-01-12 14:53:57

PCB LAYOUT三種特殊走線技巧闡述

、高速PCB設計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質量,所以只作時序匹配之用而無其它目的。 7、有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優于正常的蛇形走線。

2018-09-13 15:50:25

PCB Layout 3W原則 20H原則 五五原則

本帖最后由 一生紅與黑 于 2012-2-3 13:52 編輯

3W原則:這里3W是線與線之間的距離保持3倍線寬。你說3H也可以。但是這里H指的是線寬度。不是介質厚度。是為了減少線間串擾,應

2012-01-17 14:21:41

PCB Layout 3W原則 20H原則 五五原則

3W原則:4 A2 [3 F4 A. C這里3W是線與線之間的距離保持3倍線寬。你說3H也可以。但是這里H指的是線寬度。不是介質厚度。是為了減少線間串擾,應保證線間距足夠大,如果線中心距不少于3倍

2014-10-28 15:29:44

PCB Layout 中的直角走線、差分走線和蛇形線

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中

2019-06-10 10:11:23

PCB Layout走線秘籍

本帖最后由 maskmyself 于 2017-7-10 10:08 編輯

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速

2017-07-07 11:45:56

PCB Layout三個方面的走線策略

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-05-23 08:52:37

PCB Layout中的專業走線策略

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2014-08-13 15:44:05

PCB Layout的走線策略怎么優化?

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-08-05 06:40:24

PCB走線不要隨便拉

大安全間距等方法。保證信號質量。

d) 有阻抗控制要求的網絡應布置在阻抗控制層上,須避免其信號跨分割。

2布線竄擾控制

a) 3W原則釋義

線與線之間的距離保持3倍線寬。是為了減少線間串擾,應保證線間距足夠大,如果線中心距不少于3倍線寬時,則可保持70%的線間電場不互相干擾,稱為3W規則。

2023-12-12 09:23:35

PCB走線與各類信號布線注意事項

,MIPI信號線應遠離其它高速、高頻信號(并行數據線、時鐘線等),至少保持3W以上的距離且絕不能平行走線。對開關電源這一類的干擾源更應遠離。 過孔:MIPI信號線盡量不要打過孔,如有過孔則線對上的兩根

2023-04-12 15:08:27

PCB走線的設計細節詳解

好的圖像質量的保證。 PCB走線如果可能的話,信號走線使用6mil, 走線間距使用6mil. 放置0.1uF的退耦電容在對應的DSP電源腳上,并盡可能的靠近。它的走線盡可能的粗。電源正極的走線最少要

2023-04-13 16:09:54

PCB走線跟哪些因素有關?如何計算PCB走線的線寬?

來說,沒有按照正確的方法評估走線線寬,可能導致電流過大,燒毀板子走線;對于高速信號來說,沒有合適的計算線寬,可能導致阻抗失配,引起信號完整性問題。 2.PCB走線跟哪些因素有關 PCB的走線主要跟

2023-04-12 16:02:23

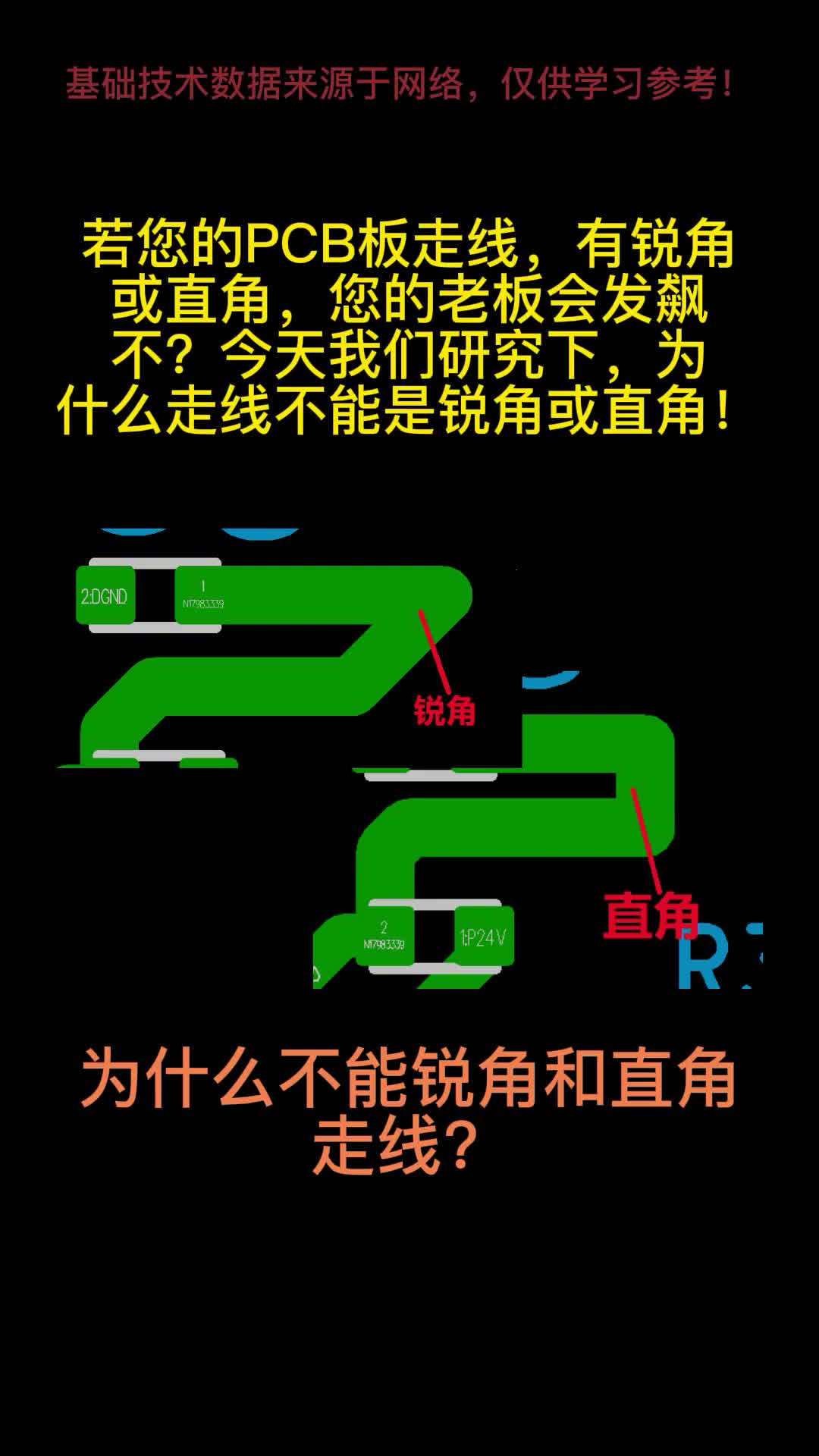

PCB中直角走線的對信號的影響有哪些?

不出來,高速PCB設計工程師的重點還是應該放在布局,電源/地設計,走線設計,過孔等其他方面。當然,盡管直角走線帶來的影響不是很嚴重,但并不是說我們以后都可以走直角線,注意細節是每個優秀工程師必備的基本素質

2014-11-18 17:29:31

PCB為什么不能直角走線?

采訪過蘋果公司CEO的B站up主-何同學,近期更新一條視頻中,有出現過他自己設計的PCB圖。很多人說他不應該直角走線。PCB為什么不能直角走線呢?一般在高速信號線中,直角線會帶來阻抗的不均勻

2022-09-08 16:54:17

PCB布局之蛇形走線

經常聽說“PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾”,這就是3W原則,信號線之間的干擾被稱為串擾。那么,你知道串擾是怎么形成的嗎?當兩條走線很近時,一條信號線上的信號可能會在另一

2022-12-27 20:33:40

PCB布局和走線的調整

在pcb的設計過程中,元器件的布局和走線的調整是非常重要的一個步驟。恰當的布局可以簡化布線的難度,更重要的是可以提高PCB的電氣性能,減少EMC,EMI。 下面是同一個原理圖對應的兩種不同的布局和走

2019-10-17 04:37:54

PCB布線有妙招,幫你搞定所有“難纏”的PCB走線

布線(Layout)是pcb設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-08-21 07:30:00

PCB直角走線的影響與計算方式。詳解

$ z/ V( f0 C5 c 總的說來,直角走線并不是想象中的那么可怕。至少在GHz以下的應用中,其產生的任何諸如電容,反射,EMI等效應在TDR測試中幾乎體現不出來,高速PCB設計工程師的重點還是

2014-10-28 15:08:55

PCB設計走線注意事項

1.1 PCB板上預劃分數字、模擬、DAA信號布線區域。1.2 數字、模擬元器件及相應走線盡量分開并放置於各自的布線區域內。1.3 高速數字信號走線盡量短。1.4 敏感模擬信號走線盡量短。1.5

2019-05-30 06:58:19

PCB設計走線的阻抗控制簡介

減少布線層,降低PCB成本。 當然,這樣做的代價是冒一些技術風險,甚至犧牲一半成功率。 對于背板的層疊設計,鑒于常見背板很難做到相鄰走線互相垂直,不可避免地出現平面長距離布線。 對于高速背板

2023-04-12 15:12:13

PCB設計高速信號走線的準則分享

硬件工程師做久了自然有自己處理電路板的一套方法,也許不是最好的辦法,自己卻能理解其中的意義。但是工作中還是要按照最完美的辦法進行操作,本期我們就來了解一下關于高速信號走線準則到底有哪幾條是你不清楚的?

2020-10-30 08:33:48

PCB設計中,3W原則、20H原則和五五原則都是什么?

`3W原則在PCB設計中為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W規則。3W原則是指多個高速信號線長距離走線的時候,其間距應該遵循

2020-09-27 16:49:19

PCB設計布線中的3種特殊走線技巧

電容,反射,EMI等效應在TDR測試中幾乎體現不出來,高速PCB設計工程師的重點還是應該放在布局,電源/地設計,走線設計,過孔等其他方面。當然,盡管直角走線帶來的影響不是很嚴重,但并不是說我們以后都可以

2018-09-17 17:31:52

PCB設計技巧Tips11:蛇形走線有什么作用?

的數據;在走線時一般遵循3W法則(繞線的間距要兩倍于線寬),這樣可消除線間78%的互感,盡量減少因電感變化而引起的阻抗不連續。 另外說明我不是高手,抬得越高摔得越痛;若想見識高手,可以到WWW

2014-11-19 11:54:01

pcb走線

1. 一般規則1.1 PCB板上預劃分數字、模擬、DAA信號布線區域。1.2 數字、模擬元器件及相應走線盡量分開并放置於各自的布線區域內。1.3 高速數字信號走線盡量短。1.4 敏感模擬信號走線盡量

2014-03-14 17:44:44

pcb蛇形走線

;=2倍的線寬。PCI板上的蛇行線就是為了適應PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個分布參數的 LC濾波器,還可作為收音機天線的電感線圈,短而窄的蛇形走線可做保險絲等等

2019-05-22 02:48:05

高速PCB走線的3-W原則

問題,布線應遵循3-W原則。 3-W原則就是讓所有的信號走線的間隔距離滿足:走線邊沿之間的距離應該大于或等于2倍的走線寬度,即兩條走線中心之間的距離應該大于或等于走線寬度的3倍。對于靠近PCB邊緣的走線

2018-11-27 15:26:40

高速PCB走線的誤區

誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識還不夠深入。從圖1-8-15的接收端的結構可以

2012-12-18 12:03:00

高速PCB走線的誤區

誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識還不夠深入。從圖1-8-15的接收端的結構可以

2012-12-19 16:52:38

高速PCB多層板疊層設計原則

多層PCB通常用于高速、高性能的系統,其中一些層用于電源或地參考平面,這些平面通常是沒有分割的實體平面。無論這些層做什么用途,電壓為多少,它們將作為與之相鄰的信號走線的電流返回路徑。構造一個好

2018-11-27 15:14:59

高速PCB布線差分對走線

分對之間的距離;s為差分對兩根信號線間的距離;W為差分對走線的寬度;Ff為介質厚度。 使用差分對走線時,要遵循以下原則: · 保持差分對的兩信號走線之間的距離S在整個走線上為常數; · 確保D

2018-11-27 10:56:15

高速PCB布線拐角走線

°拐角;另一種方法是用圓角,如圖2所示。圓角方式是最好的,45°拐角可以用到10 GHz頻率上。值得注意的是,對于45°拐角走線,拐角長度最好滿足:L≥31W。 圖1直角拐角的高頻等效電路 圖2拐角走線的處理 歡迎轉載,信息維庫電子市場網(www.dzsc.com):

2018-11-27 10:55:56

高速PCB設計系列基礎知識13|原理圖走線與設計步驟

上期講到了高速PCB設計中建立元件庫的方法元件放置完成后接下來的重點便是連接走線▼▼原理圖走線▼▼在原理圖走線中有導線的連接和總線的連接。執行Place指令下的操作,可以用以添加連線(Wire

2017-03-02 11:55:35

高速PCB設計解決EMI問題的九大規則

。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。 規則五:高速PCB設計的布線方向規則 相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串擾,增加EMI輻射。 簡而言之

2016-01-19 22:50:31

高速PCB設計調整走線長度

。 而絕對的要求是控制兩個器件之間的走線延遲為某一個值,比如器件A、B之間的延遲為Ins,而這樣的要求往往由高速電路設計者提出,而由PCB工程師去實現。要滿足這個要求,就必須知道信號的傳播速度c但需要

2018-11-27 15:22:54

高速中的蛇形走線在不同應用場合的不同作用

PCI-Clk,AGPCIK,IDE,DIMM等信號線。(2)若在一般普通PCB板中,除了具有濾波電感的作用外,還可作為收音機天線的電感線圈等等。如2.4G的對講機中就用作電感。(3)對一些信號布線長度要求

2019-03-22 06:20:09

高速中的蛇形走線適合什么情況

高速中的蛇形走線,適合在那種情況?有什么缺點沒,比如對于差分走線,又要求兩組信號是正交的。回答:”蛇形走線,因為應用場合不同而具不同的作用:(1)如果蛇形走線在計算機板中出現,其主要起到一個濾波電感

2019-05-09 07:35:35

高速串行總線走線有什么難點?

差分走線,差分走線嚴格按照差分仿真所得出的結論,2S,和 3W 的要求進行把控走線,其目的在于增強信號質量的耦合性能,減少信號的回損。

2019-09-11 11:52:29

高速電路PCB的網絡、傳輸線、信號路徑和走線

Netl。 但是,對于高速信號,如第3章所講的就完全不是這樣了,一個信號從引腳A輸出,到達D可能完全失真,而且也完全不考慮信號電流是如何返回的,所以需引入傳輸線的概念。傳輸線的原理在第3章已有詳細

2018-11-23 16:05:07

高速電路設計學習

完整性問題;3、蛇形線,滿足3W原則,高頻關鍵信號盡量不走蛇形線;4、盡量減少走線分叉,對于一驅多,走成菊花鏈來減少stub;5、控制過孔的數目,過孔呈容性,過多的過孔會導致信號完整性問題;6、對于晶振

2020-12-21 09:23:34

MIPI走線的6大法則

時,一般需要保持DP/DN在走線的過程中保持等距,保證一定的耦合程度,但是需要弄清楚的時,等長的優先級是高于等距的。且在走線時,線對之間要保持2W的距離。3、參考層MIPI走線應該保持連續的參考層,且最好

2018-05-21 11:53:33

PCBLayout中的走線方法及建意

PCBLayout中的走線方法走線的好壞將直接影響到整個系統的性能,布線(Layout)是PCB設計工程師最基本的工作技能之一。大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見

2010-03-16 09:23:41

USB PCB設計建議和差分布線的原則

為了保證良好的信號質量, USB 2.0 端口數據信號線按照差分線方式走線。為了達到USB 2.0 高速 480MHz 的速度要求,建議 PCB 布線設計采用以下原則:差分數據線走線盡可能短、直,差分數據線對內走線長度嚴格等長,走線長度偏差控制在±5mil 以內。

2019-05-23 08:52:33

[原創]PCB Layout中的走線策略

PCB Layout中的走線策略布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見

2009-08-20 20:58:49

[轉]PCB在設計布線中的3種特殊走線技巧

,其產生的任何諸如電容,反射,EMI等效應在TDR測試中幾乎體現不出來,高速PCB設計工程師的重點還是應該放在布局,電源/地設計,走線設計,過孔等其他方面。當然,盡管直角走線帶來的影響不是很嚴重,但

2018-07-08 13:28:36

【PCB小知識 6 】3W原則

PCB設計中,3W原則并不能完全滿足避免串擾的要求。按實踐經驗,如果沒有屏蔽地線的話,印制信號線之間大于lcm以上的距離才能很好地防止串擾,因此在PCB線路布線時,就需要在噪聲源信號(如時鐘走線)與非噪聲

2015-12-12 20:37:31

【PCB經驗分享】走線的參考平面在哪?

很多人對于PCB走線的參考平面感到迷惑,經常有人問:對于內層走線,如果走線一側是VCC,另一側是GND,那么哪個是參考平面?要弄清楚這個問題,必須對了解傳輸線的概念。我們知道,必須使用傳輸線來分析

2014-11-17 10:07:29

【快點PCB-3W和20H原則】

要強制使用3W原則,而且還要進行屏蔽地線包地處理,以防止串擾的發生。另外,不是所有的PCB上的走線都必須遵照3W布線原則。使用這一設計指導原則,在PCB布線前,決定哪些條走線必須使用3W原則是十分重要

2016-09-06 14:43:52

【轉】高速PCB之EMC 47原則

完整地平面相鄰,優選兩地平面之間。原因:關鍵信號線一般都是強輻射或極其敏感的信號線,靠近地平面布線能夠使其信號回路面積減小,減小其輻射強度或提高抗干擾能力。原則3:對于單層板,關鍵信號線兩側應該包地處

2018-11-23 16:21:49

三種特殊的PCB走線技巧

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-03-18 21:38:12

為什么PCB走線中避免出現銳角和直角?

,阻抗不連續,引起信號反射。為了減小不連續性,要對拐角進行處理,有兩種方法:切角和圓角。圓弧角的半徑應足夠大,一般來說,要保證:R>3W。銳角、直角走線銳角走線一般布線時我們禁止出現,直角走線一般

2017-08-12 15:09:54

仿真小技巧~高速信號如何選擇走線層?

`表層走線與內層走線更為規范的說法應該是微帶線與帶狀線。兩種走線方式因為介質和參考面不同,會存在比較明顯的差異。對于長距離傳輸的高速信號,尤其是背板之類的,需要特別注意損耗帶來的影響,避免高頻分量

2020-03-09 10:57:00

你知道高速疊層設計原則有哪些嗎

4x7628pp,滑片2mm板厚極限14層,1.6mm一般最多12層,做14層阻抗不易控制高速要求:信號層與地層盡量近電源與地盡量近,并有一處相鄰保證地平面足夠大,并完整保證相鄰的兩個信號層盡量遠,布線走線為交叉走線,盡量滿足3W規則,不行則相互錯開信號層如果以VCC為參考平

2022-03-02 06:09:06

信號在PCB走線中傳輸時延(下)

,相鄰走線間的影響就越小,走線間距盡量滿足3W原則。 2,使耦合長度盡量短。相鄰傳輸線平行走線長度越長串擾越大,走線時候盡量減小相鄰線平行走線長度;對于相鄰層走線盡量采用相鄰層垂直走線。 3,走線盡量

2014-10-21 09:51:22

原創|高速信號PCB設計處理的通用原則

通用的高速信號PCB設計處理原則有:(1)層面的選擇:處理高速信號優先選擇兩邊是GND的層面處理(2)處理時要優先考慮高速信號的總長(3)高速信號Via數量的限制:高速信號允許換一次層,換層時加

2017-02-07 09:40:04

帶你讀懂PCB設計的3W原則、20H原則及五五原則

~10mils),3W是夠了;但兩層板,走線與參考層高度距離(45~55mils),3W對高速信號走線可能不夠。3W原則一般是在50歐姆特征阻抗傳輸線條件下成立。3W原則是指多個高速信號線長距離走線

2019-05-08 08:30:00

我的PCB走線經驗歸納

在PCB設計中,布線是完成產品設計的重要步驟,PCB走線的好壞直接影響整個系統的性能,布線在高速PCB設計中是至關重要的。布線的設計過程限定高,技巧細、工作量大。PCB布線有單面布線、 雙面布線

2014-12-16 09:47:09

電源PCB設計指南:整體布局及走線原則

,一般電路應盡可能使元器件平行排列,這樣不僅美觀,而且裝焊容易,易于批量生產。三、布線原則1、輸入輸出端用的導線應盡量避免相鄰平行,最好加線間地線,以免發生反饋藕合。2、走線的寬度主要由導線與絕緣基板間

2020-08-01 07:54:14

硬件工程師談高速PCB信號走線的九個規則

網絡,在多層的PCB走線的時候一旦產生了開環的結果,將產生線形天線,增加EMI的輻射強度。 圖3 開環規則 規則四:高速信號的特性阻抗連續規則 高速信號,在層與層之間切換的時候必須保證特性阻抗

2018-09-20 10:38:01

解決高速PCB設計EMI(電磁干擾)的九大規則

設計的布線方向規則相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串擾,增加EMI輻射。簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以抑制線間的串擾。規則六:高速PCB設計中的拓撲結構

2017-11-02 12:11:12

詳解PCB直角走線的影響與計算方式。

! j9 K# {: E 總的說來,直角走線并不是想象中的那么可怕。至少在GHz以下的應用中,其產生的任何諸如電容,反射,EMI等效應在TDR測試中幾乎體現不出來,高速PCB設計工程師的重點還是應該放在

2014-11-07 09:40:54

一文詳解高速PCB的EMC設計原則

本文主要介紹了高速PCB的EMC設計原則,首先介紹了PCB設計的EMC基礎知識,其次闡述了PCB中EMC設計的重要性以及PCB中EMC設計相關項,最后詳細的介紹了關于高速PCB的EMC設計的47項原則,具體的跟隨小編一起來了解一下。

2018-05-25 15:58:19 4664

4664

4664

4664

電子發燒友App

電子發燒友App

評論