本帖最后由 gk320830 于 2015-3-5 06:07 編輯

如圖這樣能不能在哪里設置有些焊盤自動鋪銅有些焊盤自動連接,每次放著樣的過孔都是鋪銅好了再放上去,很麻煩。特別是有時候要修改下線路的時候,重新鋪銅就會是自動連接那種中間有空的。

2014-06-17 10:49:31

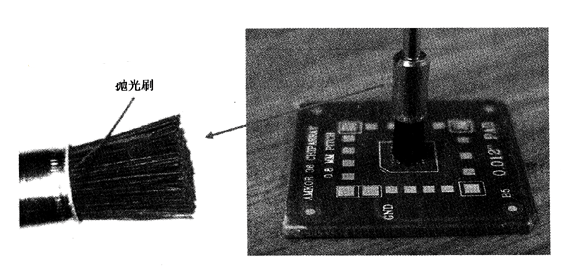

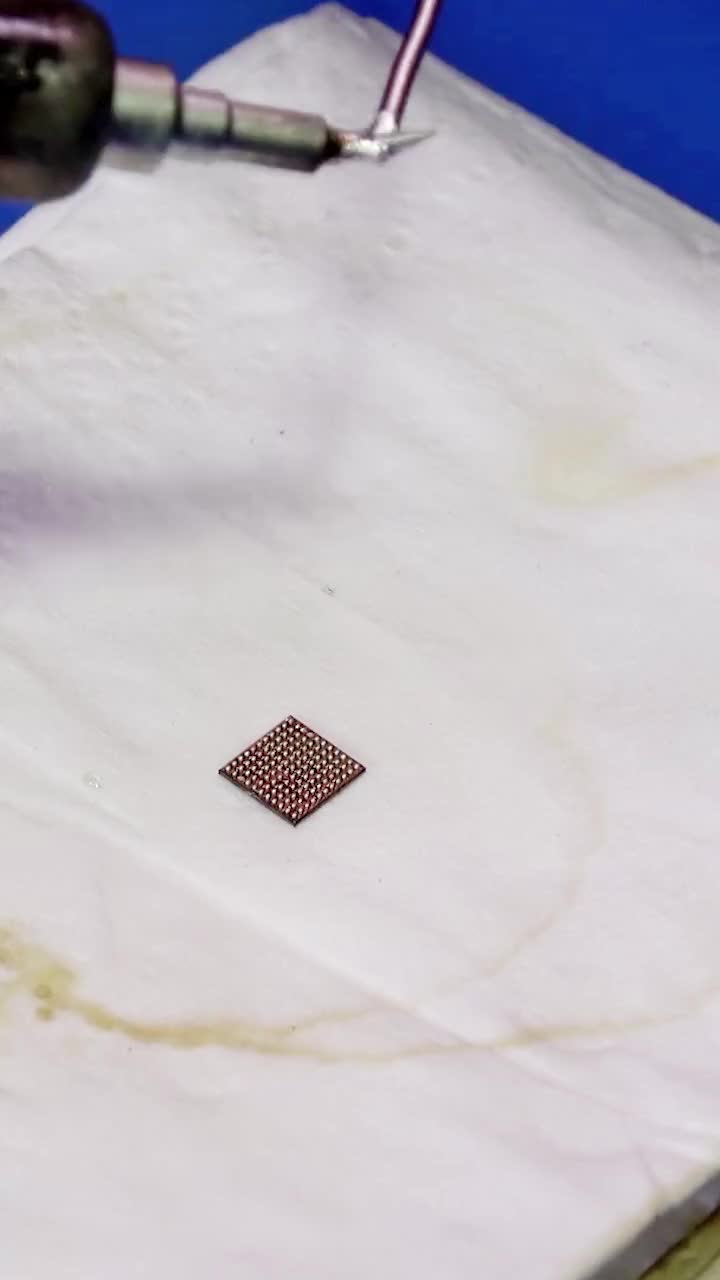

焊盤整理完成之后就可以重新貼裝元件了。這時我們又面臨了新的問題:如果選擇錫膏裝配的話,如何印刷錫膏呢?對于密間距的晶圓級CSP來說,這的確是一個難題。有采用小鋼網,采用手工的方式來局部印刷錫膏

2018-09-06 16:32:16

晶圓級CSP的返修工藝包括哪幾個步驟?晶圓級CSP對返修設備的要求是什么?

2021-04-25 08:33:16

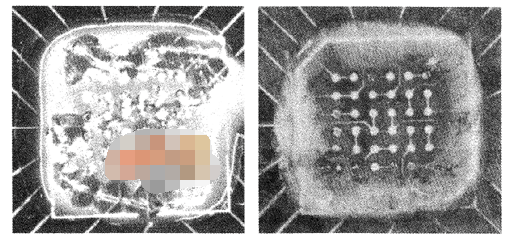

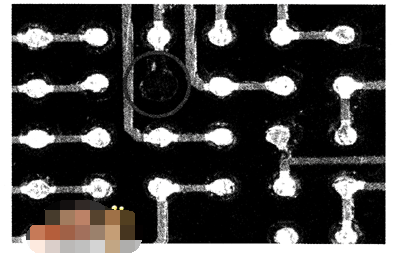

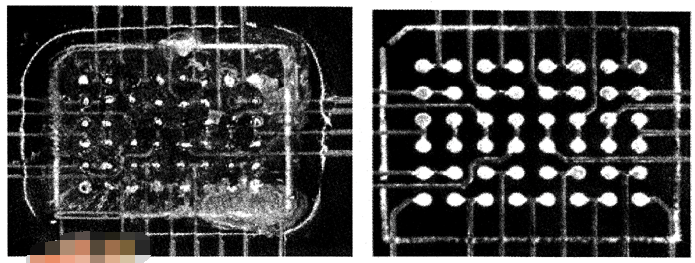

要比吸錫帶寬度略小一點。 焊盤重新整理完成之后需要目視檢查,確定是否仍然有殘留物附著在焊盤表面或臨近區域,焊盤是否清潔 平整,是否有焊盤剝離基材和助焊膜損壞等現象,以決定是否再重新整理焊盤或將組件

2018-09-06 16:33:15

晶圓級CSP的元件如何重新貼裝?怎么進行底部填充?

2021-04-25 06:31:58

細間距的晶圓級CSP時,將其當做倒裝晶片并采用助焊劑浸蘸的方法進行組裝,以取代傳統的焊膏印刷組裝,如圖2所示,首先將晶圓級CSP浸蘸在設定厚度的助焊劑薄膜中,然后貼裝,再回流焊接,最后底部填充(如果有要求)。關于錫膏裝配和助焊劑裝配的優缺點。圖1 工藝流程1——錫膏裝配圖2 工藝流程2——助焊劑裝配

2018-09-06 16:24:04

晶圓級CSP裝配回流焊接工藝控制,看完你就懂了

2021-04-25 06:28:40

; ·尺寸和位置精度受阻焊膜窗口的影響,不適合密間距元件的裝配。 NSMD焊盤的尺寸和位置不受阻焊膜窗口的影響,在焊盤和阻焊膜之間有一定空隙,如圖2和圖3所示。對于 密間距晶圓級CSP,印刷電路板上的焊盤

2018-09-06 16:32:27

低,這樣焊錫膏可以很容易地沉積。 對于0.5 mm和0.4 mm晶圓級CSP的裝配,錫膏印刷面臨挑戰,選擇合適的錫膏是關鍵之一。0.5 mmCSP的印 刷可以選用免洗型type3。0.4 mmCSP

2018-11-22 16:27:28

,溫度升至25℃需要約4 h。使用前需要攪拌,可以利用自動攪拌機攪拌2~4 min。 4)印刷刮刀的選擇 刮刀材料一般有不銹鋼片和橡膠兩種,對于晶圓級CSP的錫膏印刷,一股采用金屬刮刀。金屬刀刃

2018-09-06 16:32:20

的是CSP裝配的熱循環可靠性,利用晶圓級CSP,采用不同的裝配方式來比較其在熱循環測試中的 可靠性。依據IPC-9701失效標準,熱循環測試測試條件: ·0/100°C氣——氣熱循環測試

2018-09-06 16:40:03

考倒裝晶片的貼裝工藝。與倒裝晶片所不同的是,晶圓級CSP外形尺寸和焊球直徑一般都比它大,其基材和 倒裝晶片相同,也是表面平整光滑的硅。所以需要認真選擇恰當的吸嘴,確保足夠的真空,使吸嘴和元件在 影像

2018-09-06 16:32:18

一些可以重工的底部填充材,應用種類材料,便可以實現返修。盡管如此,返修工藝還是面臨是如何將 失效的CSP移除,以及如何重新整理焊盤,將上面殘留的底部填充材料和焊料清除的問題。 經過底部填充的CSP

2018-09-06 16:32:17

先進封裝發展背景晶圓級三維封裝技術發展

2020-12-28 07:15:50

晶圓級封裝技術Wafer Level Package Technology Board Mounting Application Note for 0.800mm pitch

2009-06-12 23:57:22

晶圓級封裝技術源自于倒裝芯片。晶圓級封裝的開發主要是由集成器件制造廠家(IBM)率先啟動。1964年,美國IBM公司在其M360計算器中最先采用了FCOB焊料凸點倒裝芯片器件。

2020-03-06 09:02:23

晶圓級封裝類型及涉及的產品

2015-07-11 18:21:31

晶圓級芯片封裝技術是對整片晶圓進行封裝測試后再切割得到單個成品芯片的技術,封裝后的芯片尺寸與裸片一致。

2019-09-18 09:02:14

在庫存回補需求帶動下,包括環球晶、臺勝科、合晶、嘉晶等硅晶圓廠第二季下旬出貨續旺,現貨價出現明顯上漲力道,合約價亦確認止跌回升。 新冠肺炎疫情對半導體材料的全球物流體系造成延遲影響,包括晶圓

2020-06-30 09:56:29

在于,生成焊凸前,需要將背面的連接觸點重新走線,引到晶圓的正面才能完成WLP封裝。重新走線需通過經電鍍和填充微小導通孔來實現,這就要求很薄的晶圓,以達致合適的縱橫比。如果導通孔直徑為300μm,就得

2011-12-01 14:33:02

`晶圓切割目的是什么?晶圓切割機原理是什么?一.晶圓切割目的晶圓切割的目的,主要是要將晶圓上的每一顆晶粒(Die)加以切割分離。首先要將晶圓(Wafer)的背面貼上一層膠帶(Wafer Mount

2011-12-02 14:23:11

圓比人造鉆石便宜多了,感覺還是很劃算的。硅的純化I——通過化學反應將冶金級硅提純以生成三氯硅烷硅的純化II——利用西門子方法,通過三氯硅烷和氫氣反應來生產電子級硅 二、制造晶棒晶體硅經過高溫成型,采用

2019-09-17 09:05:06

有人又將其稱為圓片級-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對象,在晶圓上封裝芯片。晶圓封裝中最關鍵的工藝為晶圓鍵合,即是通過化學或物理的方法將兩片晶圓結合在一起,以達到密封效果。如下

2021-02-23 16:35:18

` 誰來闡述一下晶圓有什么用?`

2020-04-10 16:49:13

晶圓的制造過程是怎樣的?

2021-06-18 07:55:24

` 硅是由石英沙所精練出來的,晶圓便是硅元素加以純化(99.999%),接著是將些純硅制成硅晶棒,成為制造積體電路的石英半導體的材料,經過照相制版,研磨,拋光,切片等程序,將多晶硅融解拉出單晶硅晶棒

2011-09-07 10:42:07

`晶圓的結構是什么樣的?1 晶格:晶圓制程結束后,晶圓的表面會形成許多格狀物,成為晶格。經過切割器切割后成所謂的晶片 2 分割線:晶圓表面的晶格與晶格之間預留給切割器所需的空白部分即為分割線 3

2011-12-01 15:30:07

晶圓表面各部分的名稱(1)器件或叫芯片(Chip,die,device,circuit,microchip,bar):這是指在晶圓表面占大部分面積的微芯片掩膜。(2)街區或鋸切線(Scribe

2020-02-18 13:21:38

晶圓針測制程介紹 晶圓針測(Chip Probing;CP)之目的在于針對芯片作電性功能上的 測試(Test),使 IC 在進入構裝前先行過濾出電性功能不良的芯片,以避免對不良品增加制造成

2020-05-11 14:35:33

`159-5090-3918回收6寸晶圓,8寸晶圓,12寸晶圓,回收6寸晶圓,8寸晶圓,12寸晶圓,花籃,Film Fram Cassette,晶元載具Wafer shipper,二手晶元盒

2020-07-10 19:52:04

本帖最后由 iamstrongman 于 2012-2-16 22:44 編輯

大家好偶是初學者,想請教下焊盤的畫法1.我們普通放置焊盤一般頂層和低層都會有焊盤;并且頂層和底層焊盤間中間的通孔

2012-02-16 22:32:40

重新整理了一下PIC單片機的資料,是我學習PIC單片機整個過程當中,收集,購買到的所有資料。包含PIC 16 18 32 型號單片機的各種版本的編程軟件(MPLAB 、MPLAB X)、編譯器

2015-02-12 11:46:05

請問下,為什么我放置焊盤的時候,捨取點一直是在焊盤的邊緣的,而不是在焊盤的中心的,我的焊盤是不規則焊盤,D-shape就是有矩形跟圓構成的,請問怎么破?

2016-08-12 15:50:09

請問有人用過Jova Solutions的ISL-4800圖像測試儀嗎,還有它可否作為CIS晶圓測試的tester,謝謝!

2015-03-29 15:49:20

晶圓級芯片級封裝; 49 bumps; 3.29×3.29×0.54mm(包括背面涂層)

2022-12-06 06:06:48

大)就會出現焊盤丟失的現象。問題解決方法:輸出光繪時將“填充線寬”改小。案例2:焊盤變形焊盤變形分析:輸出Gerber 文件D碼錯亂。解決方法:重新生成D碼表。`

2020-07-29 18:53:29

請教一下,有部分工程師使用的0402以上阻容件封裝焊盤呈子彈頭設計(焊盤內測導圓),這樣設計走什么優缺點呢?

2023-05-11 11:56:44

的尺寸已縮小到接近被封裝的芯片大小。封裝體與芯片的面積比為 1.2:1。此項技術就是芯片級封裝(CSP)或稱之為精細間距 BGA(FBGA)。芯片級封裝的最新發展是晶圓規模的芯片級封裝(WS-CSP

2023-04-25 18:13:15

焊接固定在PCB上,印制導線把焊盤連接起來,實現元件在電路中的電氣連接。在焊錫的過程中如果對這方面不懂的人就很容易把PCB上的焊盤破壞,嚴重導致整塊電路板報廢,下面小編就和大家來說說關于焊盤的一些

2020-06-01 17:19:10

PCB設計中焊盤孔徑與焊盤寬度設置多少?

2023-04-12 11:34:11

基本特征形式:即剛性基、柔性基、引線框架基和晶片級規模。 CSP技術可以取代SOIC和QFP器件而成為主流組件技術。 CSP組裝工藝有一個問題,就是焊接互連的鍵合盤很小。通常0.5mm間距CSP

2013-10-22 11:43:49

的熱門先進技術。 比如說,如何處理在CSP和0201組裝中常見的超小開孔(250um)問題,就是焊膏印刷以前從未有過的基本物理問題。板級光電子組裝,作為通信和網絡技術中發展起來的一大領域,其工藝非常精細

2018-09-10 15:46:13

SiC SBD 晶圓級測試 求助:需要測試的參數和測試方法謝謝

2020-08-24 13:03:34

小,擊穿電壓穩定,良率高,鉗位 電壓一般,電容有低容,普容和高容,6寸可以做回掃型ESD產品;第三代TVS主要以8寸晶圓流片為主,以CSP晶圓級封裝為主(DFN),這種產品是高性能的ESD,采用8寸的先進

2020-07-30 14:40:36

`在protel99se中,我用到了DC插頭,它的焊盤孔是橢圓形的,它是怎么畫出來的呢?我總是不會修改,老是圓的,愁!`

2011-10-26 16:57:04

【重新整理】——操作系統死機的幾大原因▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂▂平常我們上網的時候,經常會遇到死機情況,很多朋友可能經常迷迷糊糊不清楚到底是什么情況,小編今天列了一些比較經常

2013-08-06 16:26:31

焊盤與過孔設計元器件在印制板上的固定,是靠引線焊接在焊盤上實現的。過孔的作用是連接不同層面的電氣連線。(1)焊盤的尺寸焊盤的尺寸與引線孔、最小孔環寬度等因素有關。應盡量增大焊盤的尺寸,但同時還要考慮

2018-12-05 22:40:12

盤孔,兩焊盤周邊必須用阻焊漆圍住。9、設計多層板時要注意,金屬外殼的元件,插件時外殼與印制板接觸的,頂層的焊盤不可開,一定要用綠油或絲印油蓋住(例如兩腳的晶振、3只腳的LED)。10、PCB板

2018-08-20 21:45:46

的焊盤孔,兩焊盤周邊必須用阻焊漆圍住。9、設計多層板時要注意,金屬外殼的元件,插件時外殼與印制板接觸的,頂層的焊盤不可開,一定要用綠油或絲印油蓋住(例如兩腳的晶振、3只腳的LED)。10、PCB板

2022-06-23 10:22:15

異型焊盤的技術特點、對PCB制程中關鍵工序焊盤的制作精度及電測工藝展開研究,確保與阻焊等大的“D”字型異型焊盤PCB像常規方型或圓型焊盤PCB一樣具有優良的電接觸性能及焊接性能。

2019-08-08 11:04:53

,我們將采用穿硅通孔(TSV)用于晶圓級堆疊器件的互連。該技術基本工藝為高密度鎢填充穿硅通孔,通孔尺寸從1μm到3μm。用金屬有機化學汽相淀積(MOCVD)淀積一層TiN薄膜作為籽晶層,隨后同樣也采用

2011-12-02 11:55:33

了。重新再.pcb文件中進行修改保存后,再打開文件,還是不能保存長條狀焊盤,請問有遇到的大俠是怎么解決這個問題的,謝謝!

2019-09-30 04:38:33

納米到底有多細微?什么晶圓?如何制造單晶的晶圓?

2021-06-08 07:06:42

` 晶圓是指硅半導體集成電路制作所用的硅晶片,由于其形狀為圓形,故稱為晶圓;在硅晶片上可加工制作成各種電路元件結構,而成為有特定電性功能之IC產品。晶圓的原始材料是硅,而地殼表面有用之不竭的二氧化硅

2011-12-01 11:40:04

`晶圓級封裝(WLP)就是在其上已經有某些電路微結構(好比古董)的晶片(好比座墊)與另一塊經腐蝕帶有空腔的晶片(好比玻璃罩)用化學鍵結合在一起。在這些電路微結構體的上面就形成了一個帶有密閉空腔的保護

2011-12-01 13:58:36

`晶圓測試是對晶片上的每個晶粒進行針測,在檢測頭裝上以金線制成細如毛發之探針(probe),與晶粒上的接點(pad)接觸,測試其電氣特性,不合格的晶粒會被標上記號,而后當晶片依晶粒為單位切割成獨立

2011-12-01 13:54:00

` 晶圓電阻又稱圓柱型精密電阻、無感晶圓電阻、貼片金屬膜精密電阻、高精密無感電阻、圓柱型電阻、無引線金屬膜電阻等叫法;英文名稱是:Metal Film Precision Resistor-CSR

2011-12-02 14:57:57

是最流行的半導體,這是由于其在地球上的大量供應。半導體晶圓是從錠上切片或切割薄盤的結果,它是根據需要被摻雜為P型或N型的棒狀晶體。然后對它們進行刻劃,以用于切割或切割單個裸片或方形子組件,這些單個裸片或

2021-07-23 08:11:27

線鍵合連接至普通封裝的引腳上。普通封裝的設計原則要求鍵合焊盤位于芯片周界上。為避免同一芯片出現兩種設計(一種是普通封裝,另一種是CSP),需要重新分配層連接焊球和鍵合焊盤。4 晶片級封裝器件的可靠性

2018-08-27 15:45:31

1、為什么晶圓要做成圓的?如果做成矩形,不是更加不易產生浪費原料?2、為什么晶圓要多出一道研磨的工藝?為什么不能直接做成需求的厚度?

2014-01-20 15:58:42

單晶的晶圓制造步驟是什么?

2021-06-08 06:58:26

(見圖1),CSP封裝的芯片在設計時就為焊球提供了可以粘附的位置,CSP工藝包括以下一些步驟:?在每一個按照完整硅圓片流程完成的芯片的每一個I/O鍵合區上加上一層凸點下金屬化層(Under-bump

2018-11-23 16:58:54

晶圓劃片 (Wafer Dicing )將晶圓或組件進行劃片或開槽,以利后續制程或功能性測試。提供晶圓劃片服務,包括多項目晶圓(Multi Project Wafer, MPW)與不同材質晶圓劃片

2018-08-31 14:16:45

`***高價大量求購大量各種品牌Nand Flash/DRAM/DDR2/DDR3/GOOD DIE/INK DIE WAFER晶圓tF,SD卡晶圓(如三星,東芝,美光,SANDISK)各種品牌U盤

2020-12-29 08:27:02

怎么選擇晶圓級CSP裝配工藝的錫膏?

2021-04-25 08:48:29

``揭秘切割晶圓過程——晶圓就是這樣切割而成芯片就是由這些晶圓切割而成。但是究竟“晶圓”長什么樣子,切割晶圓又是怎么一回事,切割之后的芯片有哪些具體應用,這些可能對于大多數非專業人士來說并不是十分

2011-12-01 15:02:42

固態圖像傳感器要求在環境大氣中得到有效防護。第一代圖像傳感器安裝在帶玻璃蓋的標準半導體封裝中。這種技術能使裸片得到很好的密封和異常堅固的保護,但體積比較龐大,制造成本也比較高。引入晶圓級封裝后

2018-12-03 10:19:27

`各位大大:手頭上有顆晶圓的log如下:能判斷它的出處嗎?非常感謝!!`

2013-08-26 13:45:30

求晶圓劃片或晶圓分撿裝盒合作加工廠聯系方式:QQ:2691003439

2019-03-13 22:23:17

隨著集成電路設計師將更復雜的功能嵌入更狹小的空間,異構集成包括器件的3D堆疊已成為混合與連接各種功能技術的一種更為實用且經濟的方式。作為異構集成平臺之一,高密度扇出型晶圓級封裝技術正獲得越來越多

2020-07-07 11:04:42

看到了晶圓切割的一個流程,但是用什么工具切割晶圓?求大蝦指教啊 ?

2011-12-01 15:47:14

焊盤(land),表面貼裝裝配的基本構成單元,用來構成電路板的焊盤圖案(land pattern),即各種為特殊元件類型設計的焊盤組合。沒有比設計差勁的焊盤結構更令人沮喪的事情了。當一個焊盤結

2018-08-30 10:07:23

`什么是硅晶圓呢,硅晶圓就是指硅半導體積體電路制作所用的硅晶片。晶圓是制造IC的基本原料。硅晶圓和晶圓有區別嗎?其實二者是一個概念。集成電路(IC)是指在一半導體基板上,利用氧化、蝕刻、擴散等方法

2011-12-02 14:30:44

一份電路的基礎內容文檔,從網上下下來的,不記得作者是誰了!作者看見了請聯系我,我把你的名字給寫進去。這份文檔,我重新整理了下,把里面的內容重新編排了下。里面的內容還來不及查看,請大家多多提意見,大家共同來整理這份文檔!謝謝大家!

2014-03-06 20:54:12

SRAM中晶圓級芯片級封裝的需求

2020-12-31 07:50:40

如圖,別人抄板的原理圖,需要重新整理,里面的小方塊代表什么?有的是P+數字,有的是TP+數字,是代表板子上的焊盤嗎?還請大神解答

2017-07-26 10:27:07

allegro更改焊盤大小后如何更新焊盤?

2019-05-17 03:38:36

是均衡的。裸片的電接口是焊球陣列,也稱為球柵陣列(BGA),位于封裝的反面。在BGA和半導體裸片之間的連接建立方面采用了多種私有機制。包含焊球在內的封裝總厚度約為900μm。 圖2:圖像傳感器由晶圓級

2018-10-30 17:14:24

晶圓測溫系統,晶圓測溫熱電偶,晶圓測溫裝置一、引言隨著半導體技術的不斷發展,晶圓制造工藝對溫度控制的要求越來越高。熱電偶作為一種常用的溫度測量設備,在晶圓制造中具有重要的應用價值。本文

2023-06-30 14:57:40

焊盤整理完成之后就可以重新貼裝元件了。這時我們又面臨了新的問題:如果選擇錫膏裝配的話,如何印刷錫膏呢?對于密間距的晶圓級CSP來說,這的確是一個難題。

2023-09-28 15:45:12 660

660

正在加载...

電子發燒友App

電子發燒友App

評論