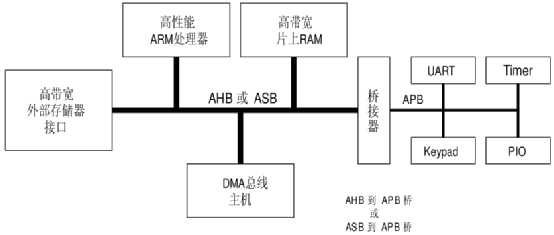

本文將說明高性能LCD控制器IP的模塊化設計概念(如圖一)。FTLCDC200 通過SDRAM控制器跟SoC內部總線通信,控制器把圖像數據從SDRAM讀到TFT顯示屏。CPU來控制整個系統的初始化與數據的流向,包括每個控制器內部的配置寄存器、更新SDRAM中幀緩存區的內容。通過傳遞輔助端口輸出的數據流,這套系統還可以為電視相關的終端提供視頻信號,這需要另外搭配TV 編碼器與三通道視頻DAC才能實現與TV的連接。

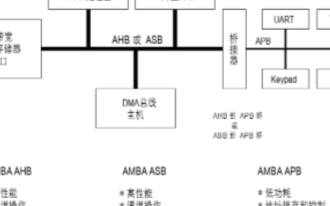

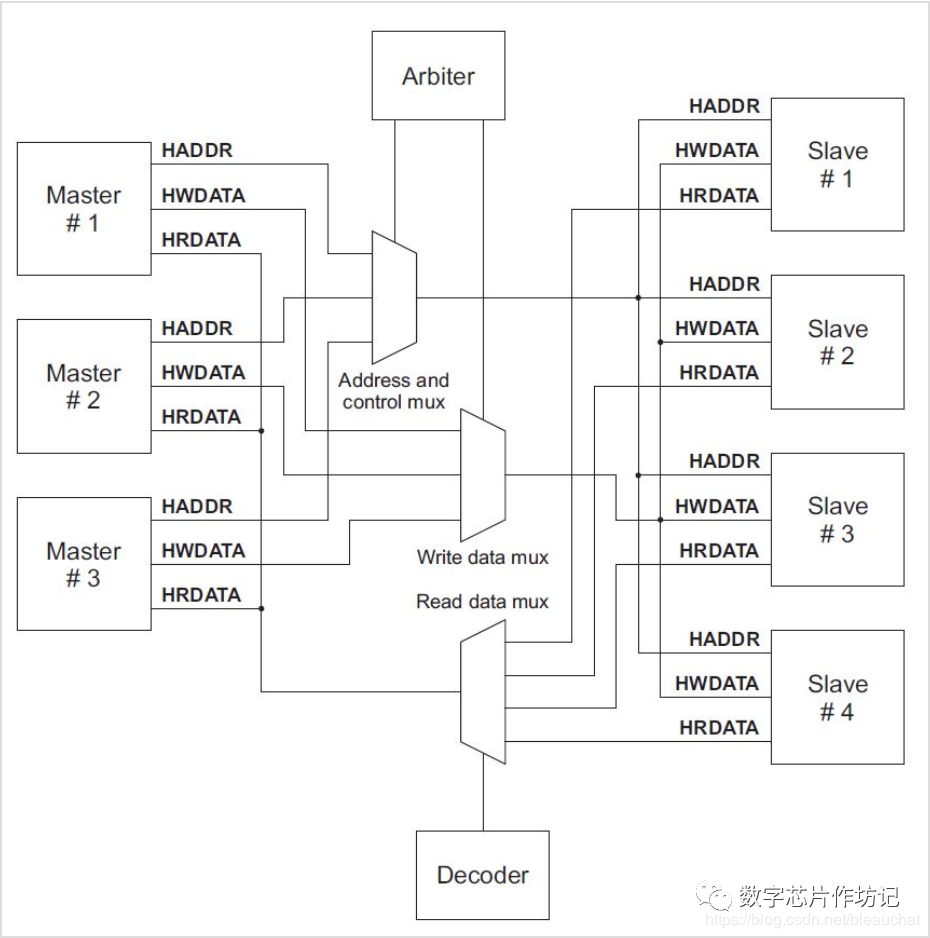

AHB 接口模塊的設計概念

AHB 接口可以分為兩個部分:一個是AHB 從接口,另一個是AHB 主接口。AHB 從 接口連接FTLCD200和AMBA AHB總線,并且允許系統中的AHB主接口的讀寫訪問,此時AHB只能進行OK的響應和字(WORD)位寬的傳輸。AHB 主接口可以把幀緩沖區中的圖像數據取出后放入到LCD控制器的FIFO中。AHB接口可以處理長度不確定的字符串,也能夠在處理出錯的時候發出主接口出錯斷言。當一個重試的應答收到后,第二次操作將開始被處理。

FIFO控制器和FIFO模塊的設計概念

數據被AHB主接口從外都存儲器讀取后會被放入FIFO。除了YCbCr420模式下,其他模式都只需要一個控制器/FIFO。Y、Cb、Cr需要有三個單獨的通道,因為每一個會放于不同的存儲單元。FIFO為32-bit位寬,深度則是可配置的。FIFO的輸入端連接在AHB 主接口的輸出端;FIFO的輸出端則被連接到了像素數據解包控制器。如果總線不能提供給像素流足夠的帶寬,那么一些圖像就會出現失真現象。因此,FIFO控制器會提供一個稱為“欠運行中斷”的信號,來通知微控制器解決總線阻塞的問題。

圖1 FTLCDC200的模組化方塊圖

像素數據解包

存儲在FIFO中的數據都是32-bit,但可以按照不同的格式打包,如24位、16位、8位、4位、2位和1位,這取決于像素格式的設定。當處于YCbCr420 和YcbCr422模式,像素格式是預先設定的且不能修改。根據操作模式,像素數據可以被用來對調色板RAM區進行尋址,或者構成初始的色彩值而被直接應用到LCD的面板上。下面的表格有一個例子來描述數據包的格式。FLCD200 提供了1位, 2位, 4位, 8位, 16位, 和24位BPP(每像素比特數),并且支持以下幾種格式:大端(也稱為大尾)字節和大端像素、小端(也稱為小尾)字節和大端像素、小端字節和小端像素。

數據模式

一、 原始的RGB模式

這種模式下有兩個類型:16bpp和24bpp,每一種都適用于初始數據RGB模式。數據流不需要任何處理,但必須根據不同的LCD面板的分辨率進行排序。

二、 YCbCr422模式

該模式中只允許16bpp。

三、 YCbCr420模式

該模式中只允許8bpp。Y,Cb,Cr每個分量都被放到單獨的存儲單元中。這三個圖像幀緩沖區的基地址在寄存器中都可以單獨配置。當YCbCr420數據從各自的FIFO中被讀出后,必須在行數據消失之前生成色度值。行緩沖器里面存儲著以前的數據,經過垂直插值后,可以得到缺失的色度值。這樣就可以把YCbCr420轉換成YCbCr422,然后輸出數據流,進行下一步的處理。

四、 RGB調色板模式

為了加強應用的靈活性,本控制器提供了“重新映射”的操作模式。該技術可以讓我們能夠在色彩的豐富度和存儲器帶寬兩個選擇之間進行切換。有四種類型可以選擇:8、4、2、1bpp。調色板存儲器里面存儲著一個查找表,用來重新生成所需要的RGB各個分量。因為物理上它的容量為128x32位,因此調色板存儲器最多可以保留256x16位的色彩值。從輸入FIFO而來的像素數據被用來對一個獨立的調色板單元進行尋址。1位像素數據可以尋址到最前端的兩個存儲空間,2位的像素數據可以尋址最前端的4個存儲空間,4位的可以尋到最前端的16個存儲空間。8位的可以尋遍整個256個存儲空間。在16位和24位的模式下調色板存儲器不被使用,通過配置可以把它去除以減小硬件開銷。

Scalar模塊的設計概念

圖2為Scalar 模塊的方塊圖,以下就其各個子模塊作介紹, 這里的設計特點在只是用了(1024+2048)x24大小的行緩沖區, 大幅減小了IP的面積。

圖2 Scalar 模塊

一、 濾波器

這是個128抽頭的濾波器,使用線性插值算法來對水平方向的像素數據進行第一步的縮小操作,系數可選:1/2,1/3,1/4……. ,1/128。

二、 1024x24 行緩沖區

該行緩沖區來存儲被濾波器處理過的一行數據。

三、 1024x24 行緩沖區控制器

該控制器控制著緩沖區數據的訪問。緩沖區中被讀出的數據會反饋到輸入端口,跟第二行的像素數據進行線性插值,也就是垂直插值的處理。

四、 2048x24 行緩沖區

這個行緩沖區是一個乒乓結構的存儲器,它由兩個1024x24位的單端口SRAM組成。因為我們放大的處理是基于雙線性算法,所以垂直放大系數被限制在2,乒乓結構可以提供同時進行讀/寫操作的機制,使得我們能夠把行緩沖區存儲器的大小壓縮到僅僅一行像素數據的規模。

五、 2048x24 行緩沖區控制器

該控制器提供必需的地址線和控制信號給乒乓結構的行緩沖區,以確保RGB像素數據能夠同時正確的被寫入和讀出。除了這個基本的控制功能以外,它也提供了一個可靠的外部LCD控制器訪問接口。

六、 垂直Scalar濾波器

該垂直Scalar濾波器是2抽頭,它執行一個“加-乘”混合計算(y[n] = a * x[n] + (1-a) * x[n-1])。x[n]是當前行的像素數據,x[n-1]是上一行的像素數據,y[n]是濾波器的輸出。a和(1-a)都是濾波器因子。由于R/G/B各數據是獨立進行處理的,所以每一種色彩像素數據處理需要兩個8x9位的乘法器和一個17位的加法器。

七、 垂直Scalar系數產生器

該發生器分為放大系數產生器和縮小系數產生器。他們都會產生一個9位的系數,MSB代表整數部分,其余的都是小數部分。這個系數為輸入圖像垂直分辨率和輸出圖像垂直分辨率的比值。

八、 Scalar數據FIFO

該數據FIFO的存儲深度為8,垂直縮放模塊輸入數據到FIFO,水平縮放模塊讀出數據用來處理后續的水平像素數據。

九、 水平Scalar濾波器

該濾波器也是2抽頭,它執行一個“加-乘”混合計算(y[n] = a * x[n] + (1-a) * x[n-1]),x[n]是當前的像素數據,x[n-1]是上一個的像素數據,y[n]是濾波器的輸出。a和(1-a)都是濾波器因子。由于R/G/B各數據是獨立進行處理的,所以每一種色彩像素數據處理需要兩個8x9位的乘法器和一個17位的加法器。

十、 水平Scalar系數發生器

該發生器分為放大系數產生器和縮小系數產生器。他們都會產生一個9位的系數,MSB代表整數部分,其余的都是小數部分。這個系數為輸入圖像水平分辨率和輸出圖像水平分辨率的比值。

Scalar的up scaling階段能夠任意的定量在1x1 和 2x2之間,也就是它scale up功能可以達到如1.5x1.8等。Scaling down分成兩級,第一級可以按比例縮減1/2*1/2, 1/4*1/4, 1/8*1/8, 1/16*1/16, 1/32*1/32, 1/64*1/64或1/128*1/128;而第二級可以從1*1~1/2*1/2做任意比例的縮減動作,也就是第二級可以有小數點,不過最低只能到1/2*1/2。因此,可以由第一級+第二級來搭配產生所想要的縮減比例。

例如:1/2.5 * 1/4 => 第一級做1/2*1/2,然后第二級做4/5*1/2 就可以達到你所想要的scaling ratio。有關第二級scale down給個Scal_ver_num /Scal_hor_num的例子, 如果我們想要scale由 100x200 down to 90x160.

Scal_ver_num = [mod((ver_no_in+1)/ver_no_out)]x256/ver_no_out

Scal_hor_num = [mod((hor_no_in+1)/hor_no_out)]x256/hor_no_out

Scal_ver_num = mod[ (100) / 90 ] x 256 / 90 = 28.44 --> 28

Scal_hor_num = mod[ (200) / 160 ] x 256 / 90 = 113.77 --> 114

中斷控制器

該控制器有四個內部中斷源,AHB Master出錯中斷、FIFO欠載中斷、垂直同步中斷和幀基地址改變中斷,這幾個中斷信號經過組合形成一個全局中斷信號,只要這四個中斷源中的任意一個出現中斷,全局中斷信號就會出現斷言。這四個中斷源可以通過寄存器的修改來開啟和關閉

STN面板控制信號

以下是LCD控制器和STN面板的接口信號

* LC_DATA[7:0]:LCD數據總線,發送給STN面板上面需要被顯示的像素數據。根據STN所選擇的模式,數據直接加載到該總線上

* LC_VS(FLM):LCD的幀同步信號,表明了一個新的幀的開始。在一幀的最后一個行脈沖結束后,FLM 變為有效并一直保持到下一行脈沖,FLM才撤銷斷言,并保持無效直到下一幀。FLM是高電平有效還是低電平有效是可以通過軟件配置的。

* LC_HS(LP):LCD的行同步信號,被用來鎖存STN面板上的行數據。LP是高電平有效還是低電平有效是可以通過軟件配置的。

* LC_DE(ACD):LCD數據使能信號。該信號可以配置成每一幀切換或者每隔N行切換。

* LC_PCLK:LCD輸出的移位時鐘,是讓STN面板用來同步LCD輸出的數據。LC_PCLK是高電平有效還是低電平有效是可以通過軟件配置的。

STN面板的接口時序

LCD控制器通過LCD的數據總線持續的傳送像素數據到LCD面板。總線的時序由LC_PCLK、LC_HS、LC_VS組成。LC_PCLK信號把像素數據打入到LCD面板內部的移位寄存器。LC_HS指示每一行的開始,LC_VS則指示幀的第一行的開始。本LCD控制器可以支持絕大部分的單色LCD屏。圖3解釋了1位、2位、4位、8位LCD數據總線的接口時序。LC_HS信號再加上LC_VS信號表明了當前幀第一行的結束。在真實顯示行中插入啞元行可以調節幀率。用戶可以自己配置啞元行的數量。

圖3 STN在8位, 4位, 2位以及1位數據寬度的接口時序。

LCD屏的寬度(PL)和高度(LF)寄存器里面定義了LCD面板的尺寸。LCD控制器將會以“LCD屏開始地址寄存器”(LCDImage0FrameBase)中的值為首地址來掃描顯存,因此,被打上影音的區域將會最終顯示在LCD面板上。

LCD虛擬頁面寬度參數指定了最大顯示頁面寬度。通過修改LCDImage0FrameBase,可以使得真實顯示的窗口大小和位置在虛擬頁面邊界的范圍內變化。然后,對于編程人員來說,在軟件設置定義顯存掃描起地址的時候,是不能超多虛擬頁面的高度和寬度,否則,屏幕上可能會有一些意想不到的景象。

這個IP在LCD屏的接口上還比一般的LCD控制器多了對串口RGB屏的支持,我們在FPGA開發板上就是使用AUO A036QN01串口RGB屏來驗證。A036QN01的規格書上沒有Dummy data(LCD Serial panel pixel Parameters: offset=0200H),但我們的design是有dummy data跟沒有dummy data的可以支持的。

IP內部的接口時鐘關系

以上就這個IP的原理與子模塊作了充分的說明, 再接著介紹IP內部的接口時鐘關系。

FTLCDC200包含了三個時鐘域分別為HCLK, LC_SCALER_CLK以及LC_CLK。HCLK時鐘使用于AHB接口而且這個時鐘與AHB接口是一致的。AHB必須為SoC上的LCD控制器提供足夠的帶寬用以由幀緩存區捕獲足夠的數據。

LC_SCALER_CLK提供時鐘給scaler模塊同時對scaler模塊也要足夠快來處理數據。LC_CLK用于產生像素時鐘。像素時鐘(LC_PCLK是由LC_CLK產生并且除以1, 2, 3等等。

此外, 這三個時鐘域必須按照下面的兩個原則才能運行順暢:

? 1. HCLK ≥ LC_SCALER_CLK ≥ LC_CLK (頻率)

? 2. LC_SCALER ≥ HCLK/16 (頻率)

LC_CLK的頻率變化依靠LCD屏的選擇與使用。使用這個IP在頻率上必須根據所選用的LCD屏的規格,下面兩個例子介紹選擇時鐘頻率的方法

范例1.

假設輸入的分辨率是640x480, 每個在幀緩存區內的像素是16-bpp, AHB總線的帶寬是32 bits, LCD屏的分辨率是320x240而顯示的幀刷新率是30幀每秒。

在這個范例, scaling-down功能必須打開并且操作在1/2x1/2的步驟。

HCLK必須大于640x480 (輸入的分辨率) x 16 (bpp) x 30 (幀刷新率)/32 (總線帶寬) = 4.6 MHz

LC_SCALER_CLK必須大于640x480 (最大的 {輸入的分辨率, 輸出的分辨率}) x 30 (幀刷新率) = 9.2 MHz

LC_CLK必須大于320x240 (輸出的分辨率) x 30 (幀刷新率) x 1.2 (門廊的空白) = 2.8MHz

因此, 針對這個范例, 使用者能選擇以下的兩個條件

HCLK ≥ LC_SCALER_CLK ≥ 9.2 MHz

LC_CLK ≥ 2.8 MHz

范例2.

假設輸入的分辨率是640x480, 每個在幀緩存區內的像素是16-bpp, AHB總線的帶寬是32 bits, LCD屏的分辨率是1280x960而顯示的幀刷新率是30幀每秒。

在這個范例, scaling-down功能必須打開并且操作在2x2的步驟。

HCLK必須大于640x480 (輸入的分辨率) x 16 (bpp) x 30 (幀刷新率)/32 (總線帶寬) = 4.6 MHz

LC_SCALER_CLK必須大于1280x960 (最大的{輸入的分辨率, 輸出的分辨率}) x 30(幀刷新率) = 36.8 MHz

LC_CLK必須大于1280x960 (輸出的分辨率) x 30 (幀刷新率) x 1.2 (門廊的空白) = 44.2 MHz

因此, 針對這個范例, 使用者能選擇以下的條件

HCLK ≥ LC_SCALER_CLK ≥ LC_CLK ≥ 44.2 MHz

在我們的FPGA上驗證配置FTLCDC200以顯示圖象的參數條件如下

FTLCDC200 ngo 以45 MHz的綜合條件來產生。

HCLK = 40 MHz

LC_CLK = 24 MHz

LC_SCALER_CLK = 24 MHz

如果有影像失真, 一般來說都是LC_CLK太快而違反了綜合的條件,放慢LC_CLK的時鐘就能解決問題。如果客戶使用的LCD 屏最慢的時鐘頻率是21MHz (46.5 ns) ,然而, LC_CLK是24 MHz 以及 divNo配置為 3所以最終LC_CLK 輸入LCD屏的時鐘頻率大約是8MHz, 這跟LCD屏的規格是不符的。

作者:汪子凌,陳宏銘

技術咨詢部

電子發燒友App

電子發燒友App

評論