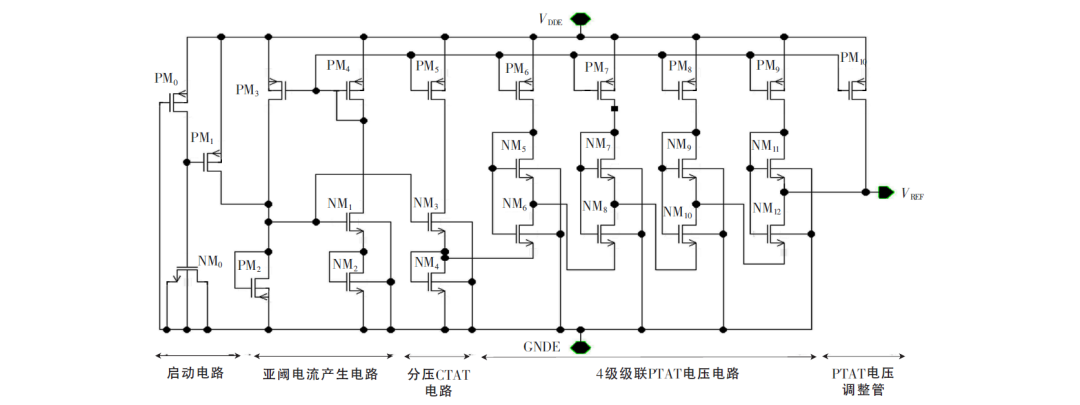

傳統(tǒng)的帶隙電壓基準(zhǔn)源面積大、功耗大、不適應(yīng)低功耗小面積的要求。本文立足于低功耗、小面積、利用工作于弱反型區(qū)晶體管的特點(diǎn),對(duì)傳統(tǒng)的帶隙電壓基準(zhǔn)源做出改進(jìn),設(shè)計(jì)了一款

2011-10-09 11:22:04 1762

1762

帶隙基準(zhǔn)電壓源的目的是產(chǎn)生一個(gè)對(duì)溫度變化保持恒定的量,由于雙極型晶體管的基極電壓VBE,其溫度系數(shù)在室溫(300 K)時(shí)大約為-2.2 mV/K

2011-11-23 09:19:32 3218

3218

基準(zhǔn)電壓是集成電路設(shè)計(jì)中的一個(gè)重要部分,特別是在高精度電壓比較器、數(shù)據(jù)采集系統(tǒng)以及A/D和 D/A轉(zhuǎn)換器等中,基準(zhǔn)電壓隨溫度和電源電壓波動(dòng)而產(chǎn)生的變化將直接影響到整個(gè)系統(tǒng)的性能。因此,在高精度的應(yīng)用場(chǎng)合,擁有一個(gè)具有低溫度系數(shù)、高電源電壓抑制的基準(zhǔn)電壓是整個(gè)系統(tǒng)設(shè)計(jì)的前提。

2021-02-22 10:36:41 3721

3721

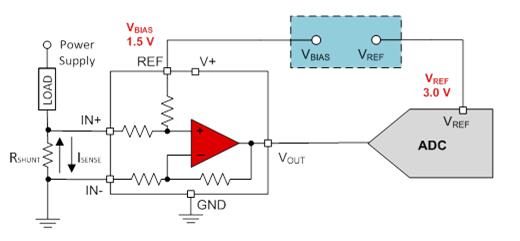

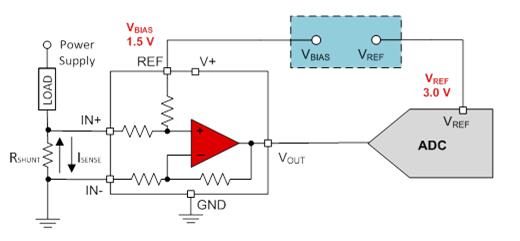

今天和大家分享一下基準(zhǔn)電壓源(一般稱為Vref)的一些設(shè)計(jì)知識(shí)。首先基準(zhǔn)電壓源,顧名思義,其輸出電壓是很穩(wěn)定的,可以作為穩(wěn)定性要求高的一些場(chǎng)合,作為基準(zhǔn)源使用,尤其是一些需要穩(wěn)定電源的ADC芯片

2022-09-06 17:00:56 3491

3491

電子設(shè)備必須能夠?qū)⒄鎸?shí)世界的測(cè)量結(jié)果(速度、壓力、長(zhǎng)度、溫度)映射到電子世界中的可測(cè)的量(電壓)。當(dāng)然,要測(cè)量電壓,您需要一個(gè)衡量標(biāo)準(zhǔn),該標(biāo)準(zhǔn)就是基準(zhǔn)電壓。對(duì)系統(tǒng)設(shè)計(jì)人員而言,問(wèn)題不在于是否需要基準(zhǔn)

2023-07-17 11:40:00 1247

1247

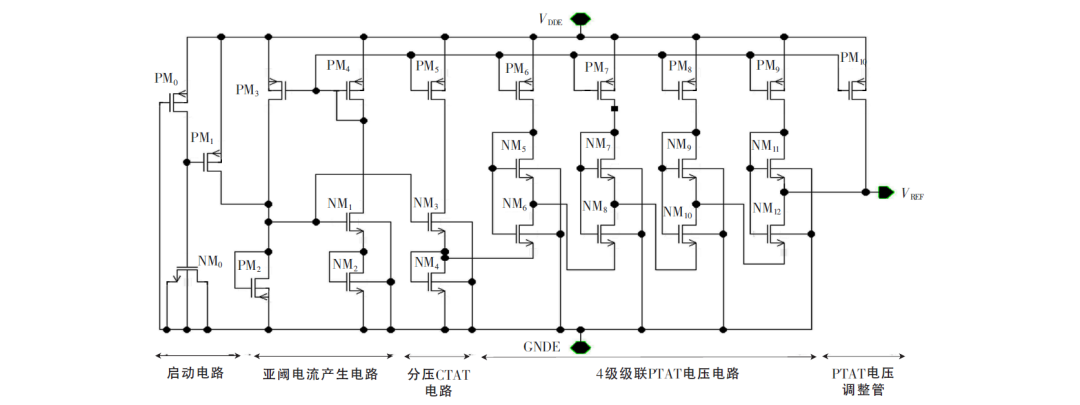

本次仿真的是2018年的論文[1],無(wú)三極管和電阻的,利用CMOS亞閾值導(dǎo)電指數(shù)特性做溫度補(bǔ)償替代三極管,極大減小了面積和功耗,能在低壓工作,溫度特性好,但基準(zhǔn)輸出值不太好調(diào)節(jié)。

2023-11-21 18:25:33 751

751

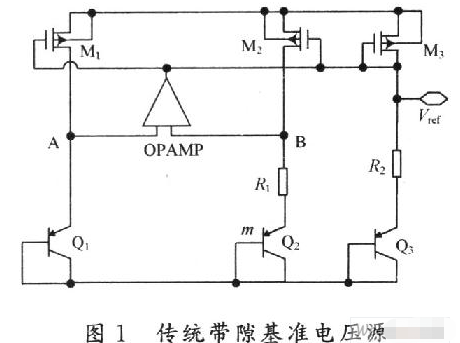

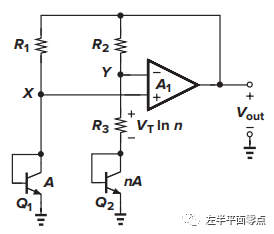

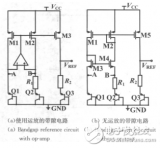

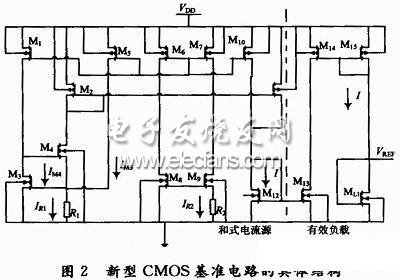

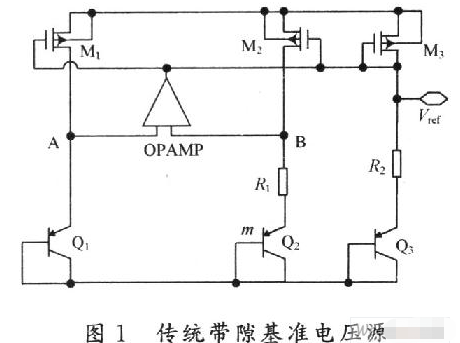

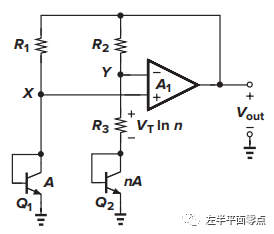

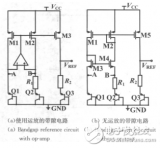

傳統(tǒng)的帶隙電壓基準(zhǔn)如圖1所示,雙極型晶體管基極-發(fā)射極電壓差ΔVBE具有正溫度系數(shù),而雙極型晶體管基極-發(fā)射極電壓VBE具有負(fù)溫度系數(shù),如果將兩個(gè)電壓進(jìn)行相加,理論上就可以通過(guò)設(shè)計(jì)合適的參數(shù)實(shí)現(xiàn)零溫度系數(shù)電壓,如圖2。具體可以參考拉扎維模集的第12章的內(nèi)容。

2023-12-15 15:47:27 435

435

一般IC中都有一個(gè)引腳為Vref,基準(zhǔn)電壓的意思。那么基準(zhǔn)電壓有什么作用呢? 一般怎么連接呢?

2017-04-20 17:43:45

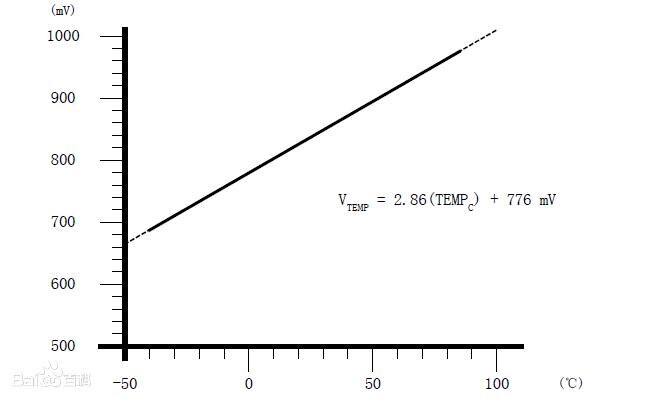

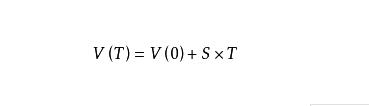

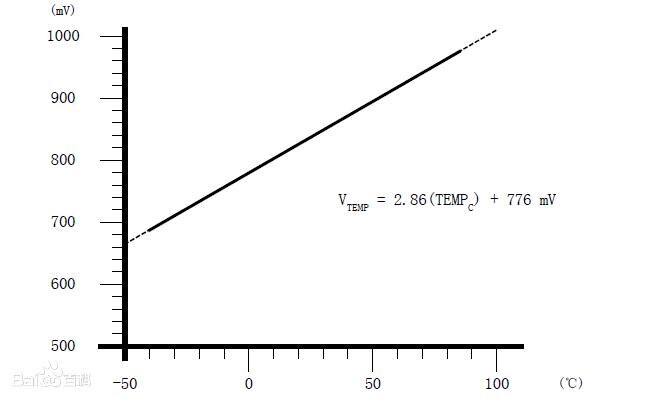

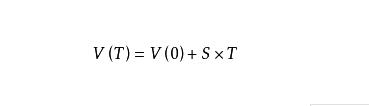

基準(zhǔn)電壓簡(jiǎn)介 基準(zhǔn)電壓是指?jìng)鞲衅髦糜?℃的溫場(chǎng)(冰水混合物),在通以工作電流(100μA)的條件下,傳感器上的電壓值。實(shí)際上就是0點(diǎn)電壓。其表示符號(hào)為V(0),該值出廠時(shí)標(biāo)定,由于傳感器的溫度系數(shù)

2021-11-12 09:11:30

電壓之間的差異 (VGS-VTH)。與雙極性器件不同,無(wú)論在弱反相情況下還是在強(qiáng)反相情況下,失調(diào)和失調(diào)漂移在 CMOS 器件中都沒(méi)有關(guān)聯(lián)性。 CMOS 放大器設(shè)計(jì)中的其它挑戰(zhàn)還包括較高的電壓噪聲閃爍與白

2018-09-13 10:08:21

電源基準(zhǔn)芯片常用于輸出所要求的電壓值,能夠比用電阻直接分壓獲得更精確的電壓輸出,更小的電壓紋波。那么電壓基準(zhǔn)芯片有什么其他方面的用處,例如可以用來(lái)當(dāng)作可控開(kāi)關(guān)使用,三端基準(zhǔn)芯片正負(fù)加上負(fù)載電壓,基準(zhǔn)

2024-01-17 23:10:59

忽視或錯(cuò)誤規(guī)定的長(zhǎng)期漂移和遲滯能成為系統(tǒng)準(zhǔn)確度的限制。系統(tǒng)校準(zhǔn)雖然能夠消除 TC 和初始準(zhǔn)確度誤差,但只有頻繁的校準(zhǔn)才能消除長(zhǎng)期漂移和遲滯。亞表齊納基準(zhǔn) (如 LT1236 ) 具有最好的長(zhǎng)期漂移和遲滯特性,但它們不像這些新型帶隙基準(zhǔn)那樣能夠提供低輸出電壓選項(xiàng)、低電源電流和低壓工作電源。

2019-08-02 06:36:09

的,AD7606的輸出方式是二進(jìn)制補(bǔ)碼,對(duì)吧?轉(zhuǎn)化為實(shí)際十進(jìn)制值的時(shí)候,按照手冊(cè)上圖中的公式是不是有錯(cuò)誤啊?

我的想法是:輸出十進(jìn)制數(shù)值=(AD7606的輸出碼)/65536*基準(zhǔn)電壓

我的這個(gè)式子對(duì)么?但是這個(gè)基準(zhǔn)電壓到底帶入什么值?2.5還是4.5????

求工程師解答啊。感謝!!!

2023-12-13 06:24:26

AD7674芯片使用外部基準(zhǔn)電壓,在ADC工作的時(shí)候基準(zhǔn)電壓對(duì)地值會(huì)被拉低,ADC不工作的時(shí)候恢復(fù)正常。ADC摘掉基準(zhǔn)電壓也恢復(fù)正常。

基準(zhǔn)電壓芯片位REF02,推測(cè)它的帶載能力不夠,在后面加了電壓跟隨電路。加入電壓跟隨電路后,基準(zhǔn)電壓正常工作,跟隨電路輸出電壓會(huì)被拉低。

請(qǐng)問(wèn)如何解決?

2023-12-08 07:46:26

請(qǐng)問(wèn)各位,我想知道ADUC361的外部基準(zhǔn)電壓最大值是多少,手冊(cè)上只提到了2.5V,我想用3V的是否可以?謝謝各位。

2024-01-11 08:27:33

在嵌入式芯片AD采樣的時(shí)候,需要根據(jù)基準(zhǔn)電壓確定采樣值和顯示值反映實(shí)際的數(shù)值關(guān)系;

1、基準(zhǔn)電壓是3V,2^12次方4096級(jí)采樣,也就是0-3V對(duì)應(yīng)0-4095,假設(shè)此時(shí)軟件依舊按照3.3V的基準(zhǔn)

2024-03-21 21:54:19

指示出什么顏色代表什么區(qū)域,謝謝了!舉例,VIHX線往上方邊界Vcc看,中間包含的藍(lán)色和條紋帶都能被認(rèn)為是高電平。是可靠電平。左邊2個(gè)是ttl邏輯電路不同供電電壓時(shí)情況;右邊2個(gè)是cmos邏輯電路

2008-07-21 10:22:44

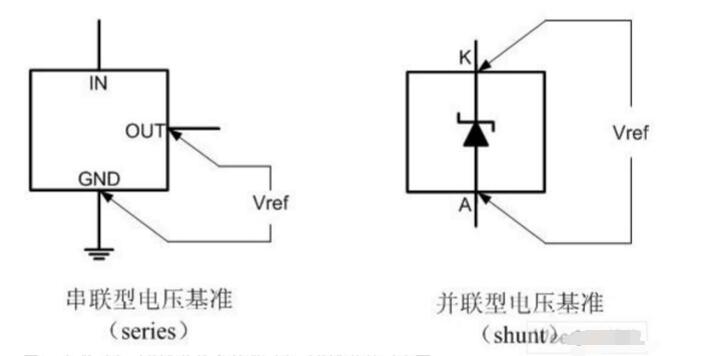

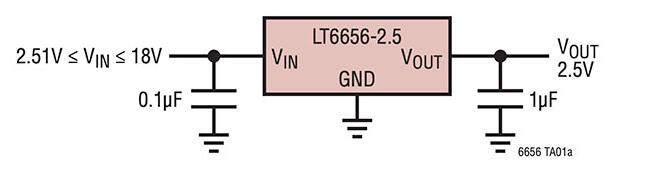

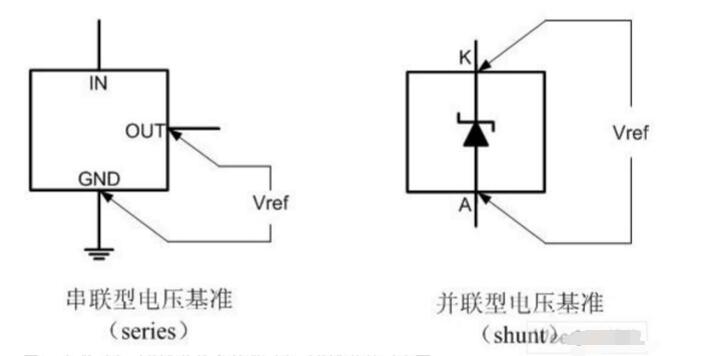

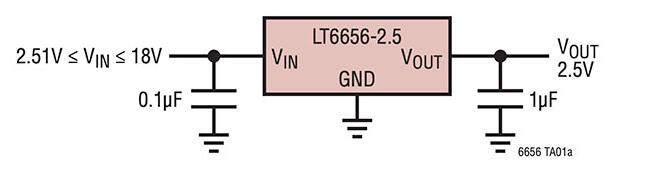

端之間的壓控電阻。通過(guò)調(diào)整其內(nèi)部電阻,使VIN值與內(nèi)部電阻的壓降之差(等于VOUT端的基準(zhǔn)電壓)保持穩(wěn)定。因?yàn)殡娏魇钱a(chǎn)生壓降所必需的,因此器件需汲取少量的靜態(tài)電流以確保空載時(shí)的穩(wěn)壓。串聯(lián)型電壓基準(zhǔn)具有

2009-11-20 11:04:08

基準(zhǔn)電壓源有很多形式并提供不同的特性,但歸根結(jié)底,精度和穩(wěn)定性是基準(zhǔn)電壓源最重要的特性,因?yàn)槠渲饕饔檬翘峁┮粋€(gè)已知輸出電壓。相對(duì)于該已知值的變化是誤差。為什么需要基準(zhǔn)電壓源?

2019-07-30 07:40:43

什么是基準(zhǔn)電壓源?看到了論壇有電壓源的貼子,想問(wèn)下什么是基準(zhǔn)電壓源?求大蝦指教啊

2011-12-27 13:48:15

具有低漂移滿量程調(diào)整的LT1021BCH-5 CMOS DAC參考的典型應(yīng)用。 LT1021是一款精密基準(zhǔn)電壓源,具有超低漂移和低噪聲特性,極佳的長(zhǎng)期穩(wěn)定性以及對(duì)輸入電壓變化的幾乎完全抗擾度。參考輸出的源電流和吸收電流均高達(dá)10mA

2020-04-02 10:00:45

AP2138超低靜態(tài)電流CMOS Ldo的典型應(yīng)用。 AP2138 / 2139系列是基于CMOS的正電壓穩(wěn)壓器IC。這些IC中的每一個(gè)都包括一個(gè)電壓基準(zhǔn),一個(gè)誤差放大器,一個(gè)用于設(shè)置輸出電壓的電阻網(wǎng)絡(luò)和一個(gè)用于電流保護(hù)的限流電路

2020-07-31 09:56:46

基準(zhǔn);LDO穩(wěn)壓器;溫度系數(shù);電源抑制比;運(yùn)算放大器 CMOS帶隙基準(zhǔn)電壓源不但能夠提供系統(tǒng)要求的基準(zhǔn)電壓或電流,而且具有功耗很小、高集成度和設(shè)計(jì)簡(jiǎn)便等優(yōu)點(diǎn),廣泛應(yīng)用于模擬集成電路和混合集成電路中。帶隙

2018-10-09 14:42:54

始于室溫條件。在返至室溫前,環(huán)境溫度會(huì)斜降/斜升到設(shè)備的最小值和最大值。溫度循環(huán)前后,在25℃條件下測(cè)量基準(zhǔn)電壓,并將差值記錄為熱滯后。熱滯后是由施加于封裝的應(yīng)力和由于熱膨脹等熱效應(yīng)應(yīng)力消失

2019-07-22 04:45:03

想請(qǐng)教各位大神,想看掃描溫度,然后用hspice看vth值,語(yǔ)句怎么寫(xiě)?

2021-06-25 06:57:34

作熱遲滯。熱遲滯不受溫度系數(shù)和時(shí)間漂移影響,降低了初始電壓校準(zhǔn)的有效性。在接下來(lái)的溫度周期中,大多數(shù)基準(zhǔn)都會(huì)圍繞標(biāo)稱輸出電壓變化,因此熱遲滯通常限制到一個(gè)可預(yù)測(cè)的最大值上。每個(gè)制造商都用自己的方法規(guī)定熱

2018-06-29 09:48:54

是基于BSIM,參數(shù)超級(jí)多,有考慮到很多二級(jí)效應(yīng)。如果直接用工藝庫(kù)的參數(shù)vth0,UnCox來(lái)計(jì)算的話,會(huì)發(fā)現(xiàn)計(jì)算的值和仿真的值相差比較大(我覺(jué)得可能是因?yàn)榉抡嬗玫墓讲皇俏覀儗W(xué)的平方率公式)。因此就需要

2022-07-15 17:54:48

的閾值電壓,也有些工程師稱之為門(mén)坎電壓,就是功率MOSFET的導(dǎo)通電壓,從字面上來(lái)理解,如果柵極的驅(qū)動(dòng)電壓VGS到了VTH值,功率MOSFET就會(huì)導(dǎo)通,那么這里的導(dǎo)通,是完全導(dǎo)通,還是沒(méi)有完全導(dǎo)

2016-11-08 17:14:57

集中度,決定了閾值電壓VTH的大小。在很多電力電子和電源系統(tǒng)中,使用得最多的是通用驅(qū)動(dòng)的功率MOSFET,也就是使用12V或15V的柵極驅(qū)動(dòng)電壓。這種類型功率MOSFET的VGS的額定值為±30V

2016-11-14 14:09:26

索尼公司近日在日本發(fā)布了一枚新型CMOS傳感器,該傳感器最大的特點(diǎn)是采用了類似富士Super CCD一樣的像素排列方式,每個(gè)感光元件都是以45度角安置的。 這種設(shè)計(jì)的主要目的是提高點(diǎn)位面積

2018-11-20 17:00:12

AD7674芯片使用外部基準(zhǔn)電壓,在ADC工作的時(shí)候基準(zhǔn)電壓對(duì)地值會(huì)被拉低,ADC不工作的時(shí)候恢復(fù)正常。ADC摘掉基準(zhǔn)電壓也恢復(fù)正常。基準(zhǔn)電壓芯片位REF02,推測(cè)它的帶載能力不夠,在后面加了電壓跟隨電路。加入電壓跟隨電路后,基準(zhǔn)電壓正常工作,跟隨電路輸出電壓會(huì)被拉低。請(qǐng)問(wèn)如何解決?

2018-07-24 10:40:58

式是二進(jìn)制補(bǔ)碼,對(duì)吧?轉(zhuǎn)化為實(shí)際十進(jìn)制值的時(shí)候,按照手冊(cè)上圖中的公式是不是有錯(cuò)誤啊?我的想法是:輸出十進(jìn)制數(shù)值=(AD7606的輸出碼)/65536*基準(zhǔn)電壓我的這個(gè)式子對(duì)么?但是這個(gè)基準(zhǔn)電壓到底帶入什么值?2.5還是4.5????求工程師解答啊。感謝!!!

2018-08-16 07:05:38

為什么要設(shè)計(jì)一種新型電壓基準(zhǔn)電路?怎樣去設(shè)計(jì)一種新型電壓基準(zhǔn)電路?

2021-04-22 06:37:20

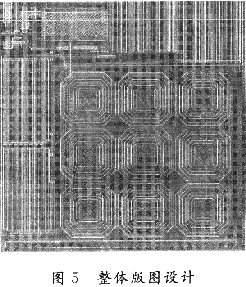

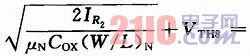

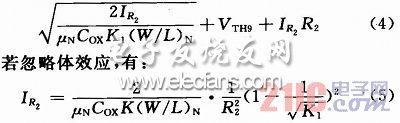

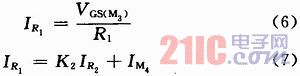

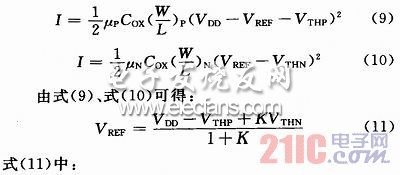

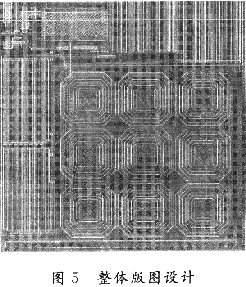

摘要:隨著深亞微米CMOS工藝的發(fā)展,尺寸按比例不斷縮小,對(duì)芯片面積的挑戰(zhàn)越來(lái)越嚴(yán)重,雙極型晶體管以及高精度電阻所占用的面積則成為一個(gè)非常嚴(yán)重的問(wèn)題。鑒于此,本文提出了一款高精度的基準(zhǔn)電壓源

2018-11-30 16:38:24

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問(wèn)題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-04-27 11:12:06 42

42 高級(jí)基準(zhǔn)電壓Vbandgap IC設(shè)計(jì):在本文中,主要討論在CMOS 技術(shù)中基準(zhǔn)產(chǎn)生的設(shè)計(jì)著重于公認(rèn)的“帶隙”技術(shù),即是與電壓,溫度變化無(wú)關(guān)的基準(zhǔn)電壓。[關(guān)鍵詞]電壓基準(zhǔn),電流基

2009-11-01 14:35:44 34

34 選擇最佳的電壓基準(zhǔn)源摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問(wèn)題并作出折衷。本文討論了

2009-12-07 14:32:23 45

45 一種抵消曲率系數(shù)的高精度低溫漂CMOS帶隙基準(zhǔn)的設(shè)計(jì):傳統(tǒng)的帶隙基準(zhǔn)使用PTAT電壓對(duì)三極管Vbe的溫度系數(shù)進(jìn)行線性補(bǔ)償來(lái)得到與溫度無(wú)關(guān)的基準(zhǔn)電壓,但由于忽略了Vbe的曲率系數(shù)

2009-12-21 10:15:46 20

20 選擇最佳的電壓基準(zhǔn)源供稿:美信摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問(wèn)題并作出折衷。本文討

2010-01-08 23:02:30 77

77 電壓基準(zhǔn)是模擬集成電路的重要單元模塊,本文在0.35um BiCMOS 工藝下設(shè)計(jì)了一個(gè)帶隙基準(zhǔn)電壓源。仿真結(jié)果表明,該基準(zhǔn)源電路在典型情況下輸出電壓為1.16302V,在-45℃~105℃范圍

2010-01-11 11:42:05 31

31 本文提出了一種結(jié)構(gòu)簡(jiǎn)單高電源抑制比的CMOS 帶隙基準(zhǔn)電壓源,供電電源3.3V。采用CSMC 0.5um CMOS 工藝。Spectre 仿真結(jié)果表明,基準(zhǔn)輸出電壓在溫度為-40~+80℃時(shí),溫度系數(shù)為45.53×10-6/

2010-01-11 14:20:43 27

27 采用二級(jí)溫度補(bǔ)償對(duì)傳統(tǒng)電流模式結(jié)構(gòu)的帶隙基準(zhǔn)電壓電路進(jìn)行改進(jìn),基于chartered 0.35um cmos工藝,使用cadence spectre進(jìn)行仿真,結(jié)果表明工作電壓為2v時(shí),電路可以輸出100mv—1.8v的寬范

2010-02-23 11:39:54 28

28 電壓基準(zhǔn)及時(shí)間基準(zhǔn)基礎(chǔ)知識(shí)

所有模數(shù)轉(zhuǎn)換器和數(shù)模轉(zhuǎn)換器都需要一個(gè)基準(zhǔn)信號(hào),通常為電壓基準(zhǔn).

2010-06-11 15:01:31 39

39 本文提出了一種結(jié)構(gòu)簡(jiǎn)單高電源抑制比的CMOS帶隙基準(zhǔn)電壓源,供電電源3.3V。采用CSMC 0.5um CMOS工藝。Spectre仿真結(jié)果表明,基準(zhǔn)輸出電壓在溫度為-40~+80℃時(shí),溫度系數(shù)為45.53×10-6/℃

2010-07-14 16:14:36 41

41 在對(duì)傳統(tǒng)典型CMOS帶隙電壓基準(zhǔn)源電路分析基礎(chǔ)上提出了一種高精度,高電源抑制帶隙電壓基準(zhǔn)源。電路運(yùn)用帶隙溫度補(bǔ)償技術(shù),采用共源共柵電流鏡,兩級(jí)運(yùn)放輸出用于自身偏置電路

2010-08-03 10:51:34 0

0 基于工作在亞閾值區(qū)的MOS器件,運(yùn)用CMOS電流模基準(zhǔn)對(duì)CATA和PTAT電流求和的思想,提出一種具有低溫漂系數(shù)、高電源抑制比(PSRR)的CMOS電壓基準(zhǔn)源,該電路可同時(shí)提供多個(gè)輸出基準(zhǔn)電

2010-12-30 10:25:53 26

26 結(jié)合工作在亞閾值區(qū)、飽和區(qū)和線性區(qū)的MOS管,提出一種純MOS結(jié)構(gòu)的基準(zhǔn)電壓源,其結(jié)構(gòu)能有效補(bǔ)償MOS管的載流子遷移率和亞閾值斜率的溫度系數(shù)。基于SMIC0.13μm的CMOS工藝的仿真結(jié)

2011-01-04 16:17:31 27

27 選擇最佳的電壓基準(zhǔn)源

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問(wèn)題并作出

2009-01-23 22:03:12 1804

1804

精密基準(zhǔn)方波基準(zhǔn)電壓源電路圖

2009-04-15 09:00:27 1216

1216

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問(wèn)題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-04-29 11:30:23 595

595

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問(wèn)題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-05-03 14:42:34 474

474

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問(wèn)題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-05-06 09:29:30 535

535

引言

模擬電路中廣泛地包含電壓基準(zhǔn)(reference voltage)和電流基準(zhǔn)(current reference)。在數(shù)/模轉(zhuǎn)換器、模/數(shù)轉(zhuǎn)換器等電路中,基準(zhǔn)電壓的精度直接決定著這些電路的

2010-09-30 10:11:55 3772

3772

低電壓高精度CMOS基準(zhǔn)電流源設(shè)計(jì)

2011-01-24 15:10:17 95

95 基準(zhǔn)電壓源是集成電路系統(tǒng)中一個(gè)非常重要的構(gòu)成單元。結(jié)合近年來(lái)的設(shè)計(jì)經(jīng)驗(yàn),首先給出了帶隙基準(zhǔn)源曲率產(chǎn)生的主要原因,而后介紹了在高性能CMOS 帶隙基準(zhǔn)電壓源中所廣泛采用的幾種

2011-05-25 14:52:44 34

34 基準(zhǔn)電壓源電路作為模擬集成電路不可缺少的模塊,對(duì)其進(jìn)行分析和研究具有重要意義。本文通過(guò)Hspice對(duì)四種MOS管基準(zhǔn)電壓源電路進(jìn)行仿真,給出了電路圖、電路參數(shù)和仿真結(jié)果。

2011-08-11 10:24:17 1551

1551

基準(zhǔn)電壓源是集成電路系統(tǒng)中一個(gè)非常重要的構(gòu)成單元。結(jié)合近年來(lái)的設(shè)計(jì)經(jīng)驗(yàn),首先給出了帶隙基準(zhǔn)源曲率產(chǎn)生的主要原因,而后介紹了在高性能CMOS 帶隙基準(zhǔn)電壓源中所廣泛采用的幾種

2011-09-27 14:30:52 58

58 在傳統(tǒng)帶隙基準(zhǔn)電壓源電路結(jié)構(gòu)的基礎(chǔ)上,通過(guò)在運(yùn)放中引入增益提高級(jí),實(shí)現(xiàn)了一種用于音頻-A/D轉(zhuǎn)換器的CMOS帶隙電壓基準(zhǔn)源。在一階溫度補(bǔ)償下實(shí)現(xiàn)了較高的電源抑制比(PSRR)和較

2012-10-10 14:49:50 43

43 在數(shù)/模混合集成電路設(shè)計(jì)中電壓基準(zhǔn)是重要的模塊之一。針對(duì)傳統(tǒng)電路產(chǎn)生的基準(zhǔn)電壓易受電源電壓和溫度影響的缺點(diǎn),提出一種新的設(shè)計(jì)方案,電路中不使用雙極晶體管,利用PMOS和

2012-10-10 16:38:05 4693

4693

基于SMIC0.35 m的CMOS工藝,設(shè)計(jì)了一種高電源抑制比,同時(shí)可在全工藝角下的得到低溫漂的帶隙基準(zhǔn)電路。首先采用一個(gè)具有高電源抑制比的基準(zhǔn)電壓,通過(guò)電壓放大器放大得到穩(wěn)定的電壓,以提供給

2013-01-22 14:52:12 52

52 根據(jù)汽車發(fā)動(dòng)機(jī)控制芯片的工作環(huán)境,針對(duì)常見(jiàn)的溫度失效問(wèn)題,提出了一種應(yīng)用在發(fā)動(dòng)機(jī)控制芯片中的帶隙基準(zhǔn)電壓源電路。該電路采用0.18 m CMOS工藝,采用電流型帶隙基準(zhǔn)電壓源結(jié)構(gòu)

2013-09-26 17:06:12 33

33 。本電路采用TSMC 0.18 μm混合信號(hào)CMOS工藝,仿真結(jié)果顯示,輸出基準(zhǔn)電壓為1.213 V,靜態(tài)電流為538 nA,在-55~125 ℃溫度范圍內(nèi),溫度系數(shù)僅為10.58 ppm/℃,低頻時(shí)的電源抑

2015-12-08 11:40:25 17

17 一種低溫度系數(shù)的全CMOS基準(zhǔn)電流源_羅彥彬

2017-01-08 10:18:57 4

4 低溫漂系數(shù)共源共柵CMOS帶隙基準(zhǔn)電壓源_鄧玉斌

2017-01-08 10:24:07 5

5 一種低功耗差動(dòng)CMOS帶隙基準(zhǔn)源

2017-01-14 12:38:40 6

6 CMOS基準(zhǔn)電流源

2017-01-22 20:29:21 31

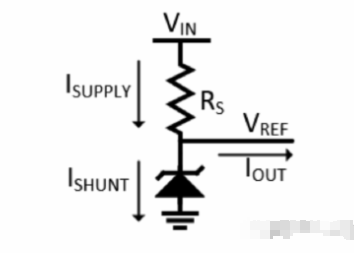

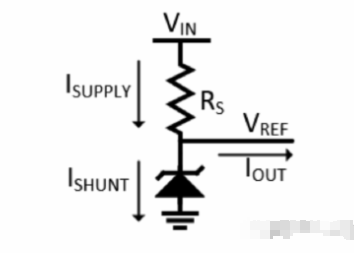

31 首先,考慮您的應(yīng)用是否需要一個(gè)并聯(lián)電壓基準(zhǔn)或一個(gè)串聯(lián)電壓基準(zhǔn)。您不必立即選定一個(gè)拓?fù)浣Y(jié)構(gòu),但它有助于了解每一應(yīng)用的最佳用例。若您不熟悉并聯(lián)電壓基準(zhǔn)和串聯(lián)電壓基準(zhǔn)之間的差異,就此話題我寫(xiě)了

2018-07-10 09:26:00 3061

3061 一種新型的高電源抑制比基準(zhǔn)電流源電路的設(shè)計(jì)

2017-05-03 15:02:36 8

8 帶隙是導(dǎo)帶的最低點(diǎn)和價(jià)帶的最高點(diǎn)的能量之差。也稱能隙。帶隙越大,電子由價(jià)帶被激發(fā)到導(dǎo)帶越難,本征載流子濃度就越低,電導(dǎo)率也就越低帶隙主要作為帶隙基準(zhǔn)的簡(jiǎn)稱,帶隙基準(zhǔn)是所有基準(zhǔn)電壓中最受歡迎的一種

2017-11-24 15:45:20 22131

22131

本文為大家介紹一個(gè)cmos無(wú)運(yùn)放帶隙基準(zhǔn)源電路。

2018-01-11 16:52:50 14756

14756

基準(zhǔn)電壓是指?jìng)鞲衅髦糜?℃的溫場(chǎng)(冰水混合物),在通以工作電流(100μA)的條件下,傳感器上的電壓值。本文介紹了基準(zhǔn)電壓定義、基準(zhǔn)電壓用途以及常見(jiàn)基準(zhǔn)電壓芯片。

2018-01-29 09:14:18 37136

37136

本文介紹了基準(zhǔn)電壓芯片的作用,詳細(xì)介紹了電壓基準(zhǔn)芯片的分類與電壓基準(zhǔn)芯片參數(shù)解析,最后介紹了TL431-2.5v基準(zhǔn)電壓芯片幾種基本用法。

2018-01-29 09:25:53 109489

109489

本文介紹了基準(zhǔn)電壓計(jì)算方式、基準(zhǔn)電壓與系統(tǒng)的相關(guān)性與2.5v基準(zhǔn)電壓芯片及5v基準(zhǔn)電壓芯片型號(hào)大全,最后介紹了5V與10v的基準(zhǔn)電壓源電路圖。

2018-01-29 10:03:51 35484

35484

本文主要詳解單電壓基準(zhǔn)與雙電壓基準(zhǔn)區(qū)別,分別從三個(gè)拓?fù)浣Y(jié)構(gòu),性能方面的不同以及占用的空間和成本方面來(lái)詳細(xì)的解說(shuō)。

2018-04-16 10:57:30 18373

18373

基準(zhǔn)電壓是指?jìng)鞲衅髦糜?℃的溫場(chǎng)(冰水混合物),在通以工作電流(100μA)的條件下,傳感器上的電壓值。實(shí)際上就是0點(diǎn)電壓。其表示符號(hào)為V(0),該值出廠時(shí)標(biāo)定,由于傳感器的溫度系數(shù)S相同,則只要知道基準(zhǔn)電壓值V(0),即可求知任何溫度點(diǎn)上的傳感器電壓值,而不必對(duì)傳感器進(jìn)行分度。

2018-04-16 11:12:11 33867

33867 本文將簡(jiǎn)要介紹電壓基準(zhǔn)的結(jié)構(gòu)和特性,并描述如何選擇電壓基準(zhǔn)。舉例來(lái)說(shuō),它將引入ADI公司ADR43x系列的電壓基準(zhǔn),以說(shuō)明設(shè)計(jì)人員可利用的各種特性,增強(qiáng)功能和特性,以充分利用現(xiàn)代電壓基準(zhǔn)。在此過(guò)程中

2019-09-29 14:46:19 9117

9117

的新型絕對(duì)溫度互補(bǔ)(ctat)電壓發(fā)生器和一種基于子vth mosfet的vgs疊加的改進(jìn)的絕對(duì)溫度比例(ptat)電壓發(fā)生器。由于ctat電路實(shí)現(xiàn)負(fù)tc的減小絕對(duì)值,ptat電路在不消耗較大芯片面積的情況下實(shí)現(xiàn)了降低功耗。該子bgr電路采用標(biāo)準(zhǔn)的0.18μm cmos工藝實(shí)現(xiàn)。測(cè)試結(jié)果表明,在功耗僅為8

2019-09-30 08:00:00 2

2 電壓基準(zhǔn)

2021-04-12 21:20:38 5

5 電壓基準(zhǔn)

2021-06-16 10:56:24 25

25 基準(zhǔn)電壓簡(jiǎn)介 基準(zhǔn)電壓是指?jìng)鞲衅髦糜?℃的溫場(chǎng)(冰水混合物),在通以工作電流(100μA)的條件下,傳感器上的電壓值。實(shí)際上就是0點(diǎn)電壓。其表示符號(hào)為V(0),該值出廠時(shí)標(biāo)定,由于傳感器的溫度系數(shù)

2021-11-07 18:21:03 7

7 QA 問(wèn):ADC和DAC的基準(zhǔn)類型 所有模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)都需要具備基準(zhǔn)電壓(通常是一個(gè)電壓)。該基準(zhǔn)電壓源是ADC和DAC系統(tǒng)中的必要模塊。有些轉(zhuǎn)換器需要內(nèi)部基準(zhǔn),而有

2021-12-10 09:41:27 4431

4431 還有什么比基準(zhǔn)電壓源(簡(jiǎn)單、恒定的基準(zhǔn)電壓)更基本的呢?與所有設(shè)計(jì)主題一樣,需要權(quán)衡取舍。本文討論不同類型的基準(zhǔn)電壓源、其關(guān)鍵規(guī)格以及設(shè)計(jì)權(quán)衡,包括精度、溫度獨(dú)立性、電流驅(qū)動(dòng)能力、功耗、穩(wěn)定性、噪聲和成本。

2023-02-27 14:37:20 790

790

還有什么比基準(zhǔn)電壓源(簡(jiǎn)單、恒定的基準(zhǔn)電壓)更基本的呢?與所有設(shè)計(jì)主題一樣,需要權(quán)衡取舍。本文討論不同類型的基準(zhǔn)電壓源、其關(guān)鍵規(guī)格以及設(shè)計(jì)權(quán)衡,包括精度、溫度獨(dú)立性、電流驅(qū)動(dòng)能力、功耗、穩(wěn)定性、噪聲和成本。

2023-03-15 11:29:43 935

935

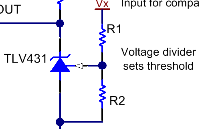

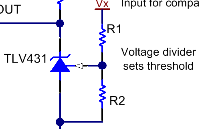

在圖 1 所示的原理圖中,TLV431 可調(diào)分流基準(zhǔn)配置為開(kāi)環(huán)操作,這意味著輸出未連接到反饋引腳。 相反,信號(hào)VX通過(guò)電阻分壓器驅(qū)動(dòng)反饋引腳。 電阻分壓器的設(shè)置使得當(dāng)VX處于閾值電壓VTH時(shí),反饋引腳上的值等于內(nèi)部基準(zhǔn)電壓。

2023-04-11 09:17:28 1518

1518

并 聯(lián)電壓基準(zhǔn) 高精度微功耗 在 新 能源汽車與光伏等應(yīng)用場(chǎng)景中需要收集聲、光、溫度等模擬環(huán)境數(shù)據(jù),后通過(guò)模數(shù)轉(zhuǎn)換器將其轉(zhuǎn)換成數(shù)字信號(hào)再進(jìn)行處理。在此過(guò)程中,不受輸入電壓或環(huán)境溫度等條件影響的高性能

2023-08-01 12:15:02 753

753 高、速度快等優(yōu)點(diǎn),在眾多電子設(shè)備中應(yīng)用廣泛。其中,基準(zhǔn)電壓就是一個(gè)比較重要的參數(shù),而基準(zhǔn)電壓的溫度系數(shù)是指在不同溫度下電路帶來(lái)的基準(zhǔn)電壓變化情況。 通常來(lái)說(shuō),CMOS電路中使用的帶隙基準(zhǔn)技術(shù),具有多晶硅、硅谷能帶、亞穩(wěn)態(tài)等技術(shù),但是這些技術(shù)都存在著一定的溫度漂移問(wèn)題。而在實(shí)際

2023-10-23 10:29:11 318

318

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論