為了避免電源噪聲影響信號鏈模數轉換器(ADC)中的信號完整性,測量ADC的電源抑制(PSR)非常重要。本博文將重點介紹此測量所需的技術,并描述如何推導出ADC的PSR。

ADC需要一個或多個電源,如果不采取預防措施,其靈敏度可能會影響ADC的數據采集。電源靈敏度與時鐘抖動問題無關,目前可以很好地理解。我們將僅以高速ti?ADC3444 ADC為例,重點介紹本文中的電源靈敏度。的ADC3444是一個四信道14位的125Mbps ADC設計用于高性能多通道應用。

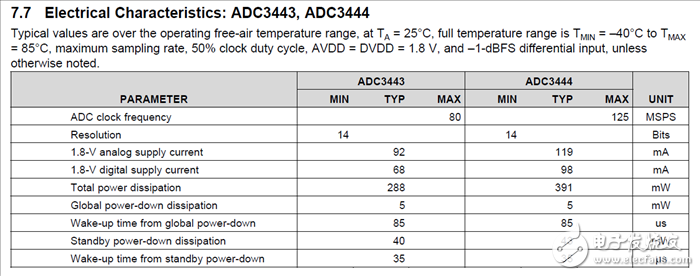

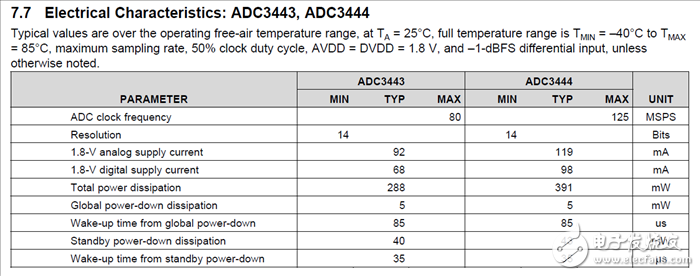

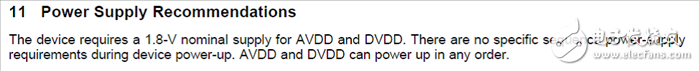

從數據手冊來看,ADC3444具有兩個不同的電源:1.8V模擬電源和1.8V數字電源。數據表提供了電氣特性(第7.7節)部分和應用部分(第11節)中的以下信息。

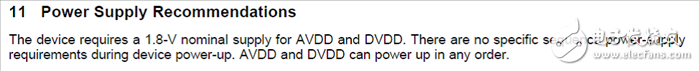

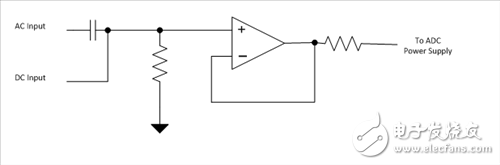

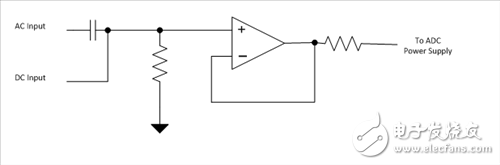

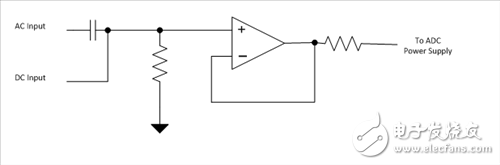

在評估ADC的性能時,ADC具有成為自己的數字轉換器的優勢。我們感興趣的是快速傅里葉變換(FFT)會發生什么,同時將單音信號數字化并向ADC電源引腳添加噪聲音。為了簡化,我們不會擔心電源噪聲,但會發出疊加在直流電源電壓上的正弦波。我們可以使用功率放大器實現這種疊加,如圖1所示。

圖1:功率放大器簡化原理圖

請注意,DC增益設置為1V / V. 輸出端使用小型隔離電阻,有助于防止由電容負載引起的放大器不穩定。

在這一點上,我們只關注在單一頻率下測量ADC的電源特性,為以后留下完整的PSRR頻率圖。由于ADC具有非常高的模擬帶寬,因此我們期望模擬電源的PSRR為高頻 - 或至少超出設計電源時所關注的最大頻率。對于ADC3444,模擬輸入帶寬為540MHz。請注意,在電源引腳上添加任何旁路電容將改善高頻下的測量PSR,因為電容會繞過任何高頻。

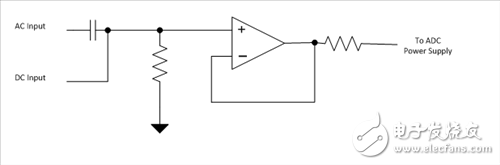

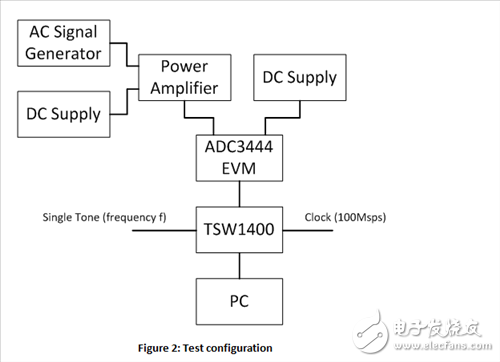

測試配置如圖2所示,在模擬電源引腳(AVDD)和數字電源引腳(DVDD)之間沒有任何區別。為了隔離AVDD和DVDD電源之間可能的相互作用,測量程序一次在單個電源上引入噪聲音。每個電源的去耦遵循ADC3444數據表的建議。十三個AVDD引腳將使用0.1μF的X7R電容,總電流為1.3μF。同樣,四個DVDD電源引腳每個都有0.22μF,DVDD電源總共為0.88μF。

圖2:測試配置

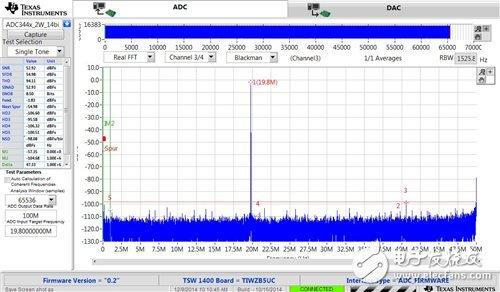

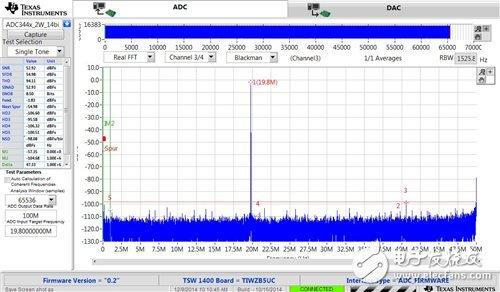

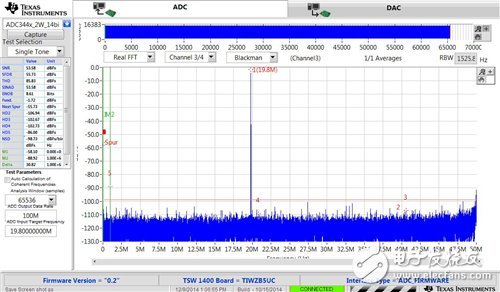

圖3顯示了ADC3444電源的結果。下面的每個圖表都是模擬信號的快速傅里葉變換(FFT)。FFT是信號的分解,是正弦波的總和。簡而言之,圖表顯示了信號的頻率成分。因此,x軸是頻率,y軸表示每個正弦波的幅度。在下面的示例中,我們使用100MHz時鐘,從而獲得50MHz的采集帶寬。

饋入ADC的信號為19.8MHz,幅度為-2dBFS(dB低于滿量程)。這在圖3中示出,其是沒有噪聲音調的參考信號。

圖3:ADC3444 AVDD參考FFT

為了評估ADC的PSR,為每個電源設計了以下程序:

1-將放大器連接到被評估的電源[這里將是AVDD或DVDD]

2-將直流電源連接到其他電源。[此直流電源是一種清潔電源,因其低噪聲特性而被選中]

3-打開噪音并捕獲FFT。[已選擇噪聲音調,以最大限度地抑制被測電源引腳上的干擾,同時仍然符合電源容差。

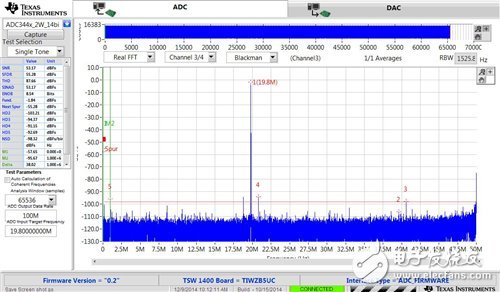

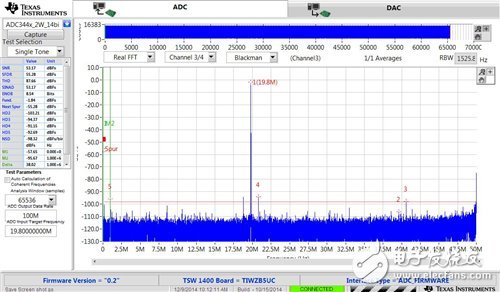

圖4顯示了與ADC相同的信號音,但這次在AVDD電源引腳中增加了一個噪聲音。由于所有其他條件相同,因此FTT上的任何降級都可以與AVDD電源上的噪聲音調相關聯。

圖4:ADC3444 AVDD響應100mVpp 1MHz正弦波疊加到1.8V

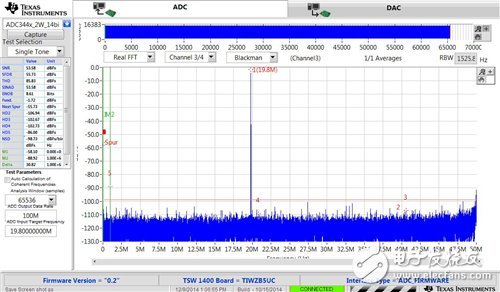

然后我們在DVDD電源引腳上重復相同的實驗,并獲得圖5所示的圖表。這次噪聲音僅出現在DVDD電源上。

圖5:ADC3444 DVDD響應100mVpp 1MHz正弦波疊加到1.8V

請注意,對于AVDD電源(圖4),出現了三個額外的雜散:1MHz,18.8MHz和20.8MHz。隨著噪聲音調被添加到獲取的頻譜中,可以預期第一個音調。另外兩個不需要的音調正好在右側和左側1MHz,與中心頻率對稱。

對于DVDD電源,圖3和圖5之間的唯一區別是1MHz的新雜散。

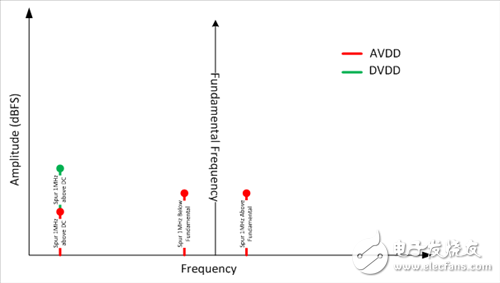

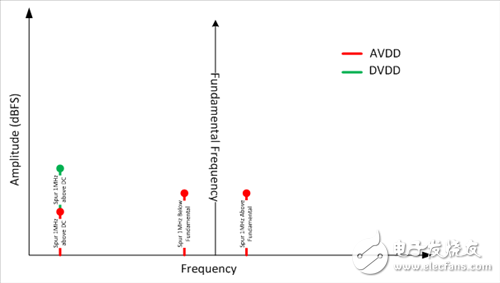

圖6總結了馬刺的位置。請注意,馬刺的幅度旨在純粹是描述性的而非定量的。

圖6:AVDD和DVDD電源的馬刺位置

現在我們已經進行了初始測量,我們仍然需要解釋它以便能夠提取所需的PSRR規范。100mV交流信號稱為干擾信號,可確保其足夠大,足以伸出ADC本底噪聲,同時又不會超過AVDD和DVDD上的工作電壓范圍。

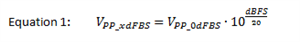

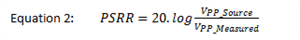

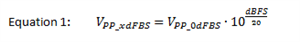

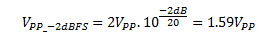

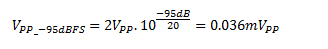

讓我們使用圖6和圖7來幫助我們解釋結果并將dB低于滿量程(dBFS)轉換為PSRR規范。假設基波幅度為-2dBFS。由于圖7中的ADC3444數據手冊告訴我們0dBFS(或滿量程)是2Vpp,我們可以將dBFS轉換為Vpp。這可以通過下面的等式1來實現:

將此應用于-2dBFS基波,ADC輸入端的差分電壓擺幅為:?

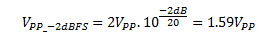

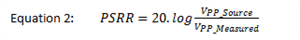

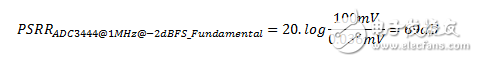

我們現在可以將ADC FFT結果中的dBFS測量結果轉換為可以與AC輸入信號進行比較的信號,從而計算出ADC電源的抑制程度。AVDD電源上的100mV信號對-2dBFS信號的影響為-95dBFS。數據手冊告訴我們0dBFS是2Vpp(見圖5),所以-95dBFS可以通過以下公式計算:

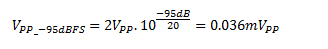

然后可以使用公式2計算PSRR:?

? ???

? ???

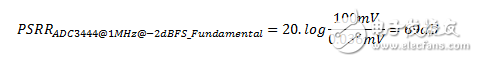

將數字插入等式2給出了PSRR(電源抑制比),其中-2dBFS基本幅度和電源上的1MHz干擾信號。

圖7:模擬輸入電氣特性

通過針對每個電源和多個頻率重復此處描述的過程,可以輕松地為任何ADC開發PSR模型。請注意,PSR模型包括推薦的旁路電容的影響。

這篇文章中的技術只是評估ADC電源PSR的第一步。接下來的文章將介紹如何使用此信息來表征ADC電源并指導產品和外部元件選擇。

ADC需要一個或多個電源,如果不采取預防措施,其靈敏度可能會影響ADC的數據采集。電源靈敏度與時鐘抖動問題無關,目前可以很好地理解。我們將僅以高速ti?ADC3444 ADC為例,重點介紹本文中的電源靈敏度。的ADC3444是一個四信道14位的125Mbps ADC設計用于高性能多通道應用。

從數據手冊來看,ADC3444具有兩個不同的電源:1.8V模擬電源和1.8V數字電源。數據表提供了電氣特性(第7.7節)部分和應用部分(第11節)中的以下信息。

在評估ADC的性能時,ADC具有成為自己的數字轉換器的優勢。我們感興趣的是快速傅里葉變換(FFT)會發生什么,同時將單音信號數字化并向ADC電源引腳添加噪聲音。為了簡化,我們不會擔心電源噪聲,但會發出疊加在直流電源電壓上的正弦波。我們可以使用功率放大器實現這種疊加,如圖1所示。

圖1:功率放大器簡化原理圖

請注意,DC增益設置為1V / V. 輸出端使用小型隔離電阻,有助于防止由電容負載引起的放大器不穩定。

在這一點上,我們只關注在單一頻率下測量ADC的電源特性,為以后留下完整的PSRR頻率圖。由于ADC具有非常高的模擬帶寬,因此我們期望模擬電源的PSRR為高頻 - 或至少超出設計電源時所關注的最大頻率。對于ADC3444,模擬輸入帶寬為540MHz。請注意,在電源引腳上添加任何旁路電容將改善高頻下的測量PSR,因為電容會繞過任何高頻。

測試配置如圖2所示,在模擬電源引腳(AVDD)和數字電源引腳(DVDD)之間沒有任何區別。為了隔離AVDD和DVDD電源之間可能的相互作用,測量程序一次在單個電源上引入噪聲音。每個電源的去耦遵循ADC3444數據表的建議。十三個AVDD引腳將使用0.1μF的X7R電容,總電流為1.3μF。同樣,四個DVDD電源引腳每個都有0.22μF,DVDD電源總共為0.88μF。

圖2:測試配置

圖3顯示了ADC3444電源的結果。下面的每個圖表都是模擬信號的快速傅里葉變換(FFT)。FFT是信號的分解,是正弦波的總和。簡而言之,圖表顯示了信號的頻率成分。因此,x軸是頻率,y軸表示每個正弦波的幅度。在下面的示例中,我們使用100MHz時鐘,從而獲得50MHz的采集帶寬。

饋入ADC的信號為19.8MHz,幅度為-2dBFS(dB低于滿量程)。這在圖3中示出,其是沒有噪聲音調的參考信號。

圖3:ADC3444 AVDD參考FFT

為了評估ADC的PSR,為每個電源設計了以下程序:

1-將放大器連接到被評估的電源[這里將是AVDD或DVDD]

2-將直流電源連接到其他電源。[此直流電源是一種清潔電源,因其低噪聲特性而被選中]

3-打開噪音并捕獲FFT。[已選擇噪聲音調,以最大限度地抑制被測電源引腳上的干擾,同時仍然符合電源容差。

圖4顯示了與ADC相同的信號音,但這次在AVDD電源引腳中增加了一個噪聲音。由于所有其他條件相同,因此FTT上的任何降級都可以與AVDD電源上的噪聲音調相關聯。

圖4:ADC3444 AVDD響應100mVpp 1MHz正弦波疊加到1.8V

然后我們在DVDD電源引腳上重復相同的實驗,并獲得圖5所示的圖表。這次噪聲音僅出現在DVDD電源上。

圖5:ADC3444 DVDD響應100mVpp 1MHz正弦波疊加到1.8V

請注意,對于AVDD電源(圖4),出現了三個額外的雜散:1MHz,18.8MHz和20.8MHz。隨著噪聲音調被添加到獲取的頻譜中,可以預期第一個音調。另外兩個不需要的音調正好在右側和左側1MHz,與中心頻率對稱。

對于DVDD電源,圖3和圖5之間的唯一區別是1MHz的新雜散。

圖6總結了馬刺的位置。請注意,馬刺的幅度旨在純粹是描述性的而非定量的。

圖6:AVDD和DVDD電源的馬刺位置

現在我們已經進行了初始測量,我們仍然需要解釋它以便能夠提取所需的PSRR規范。100mV交流信號稱為干擾信號,可確保其足夠大,足以伸出ADC本底噪聲,同時又不會超過AVDD和DVDD上的工作電壓范圍。

讓我們使用圖6和圖7來幫助我們解釋結果并將dB低于滿量程(dBFS)轉換為PSRR規范。假設基波幅度為-2dBFS。由于圖7中的ADC3444數據手冊告訴我們0dBFS(或滿量程)是2Vpp,我們可以將dBFS轉換為Vpp。這可以通過下面的等式1來實現:

將此應用于-2dBFS基波,ADC輸入端的差分電壓擺幅為:?

我們現在可以將ADC FFT結果中的dBFS測量結果轉換為可以與AC輸入信號進行比較的信號,從而計算出ADC電源的抑制程度。AVDD電源上的100mV信號對-2dBFS信號的影響為-95dBFS。數據手冊告訴我們0dBFS是2Vpp(見圖5),所以-95dBFS可以通過以下公式計算:

然后可以使用公式2計算PSRR:?

? ???

? ???將數字插入等式2給出了PSRR(電源抑制比),其中-2dBFS基本幅度和電源上的1MHz干擾信號。

圖7:模擬輸入電氣特性

通過針對每個電源和多個頻率重復此處描述的過程,可以輕松地為任何ADC開發PSR模型。請注意,PSR模型包括推薦的旁路電容的影響。

這篇文章中的技術只是評估ADC電源PSR的第一步。接下來的文章將介紹如何使用此信息來表征ADC電源并指導產品和外部元件選擇。

電子發燒友App

電子發燒友App

評論