大家好,歡迎回來。

上一期我們分析了DC-DC開關電源的靜態紋波產生的原因、動態響應時產生的過沖和下沖,并提供一些改善方法:技術分享 | DCDC開關電源實戰經驗之靜態紋波及動態響應調試方法

這一期為大家分享的是:DC-DC開關電源的開關波形產生高頻振蕩的原因,以及優化方案。

BPSemi

- DC-DC開關波形-

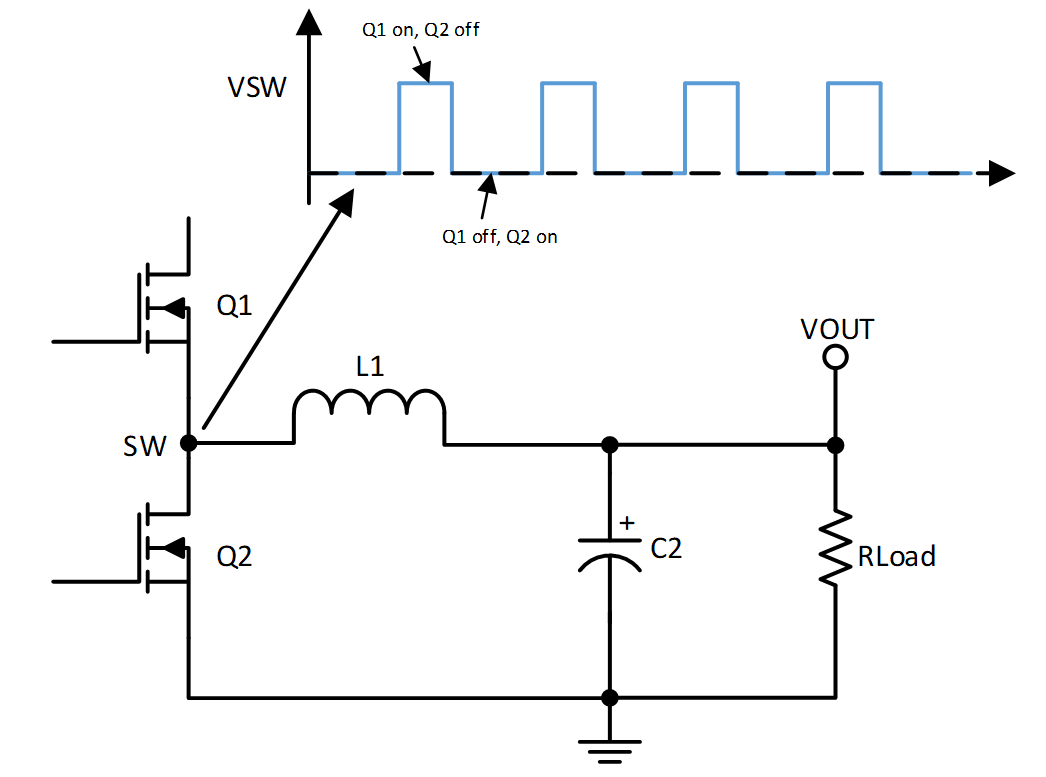

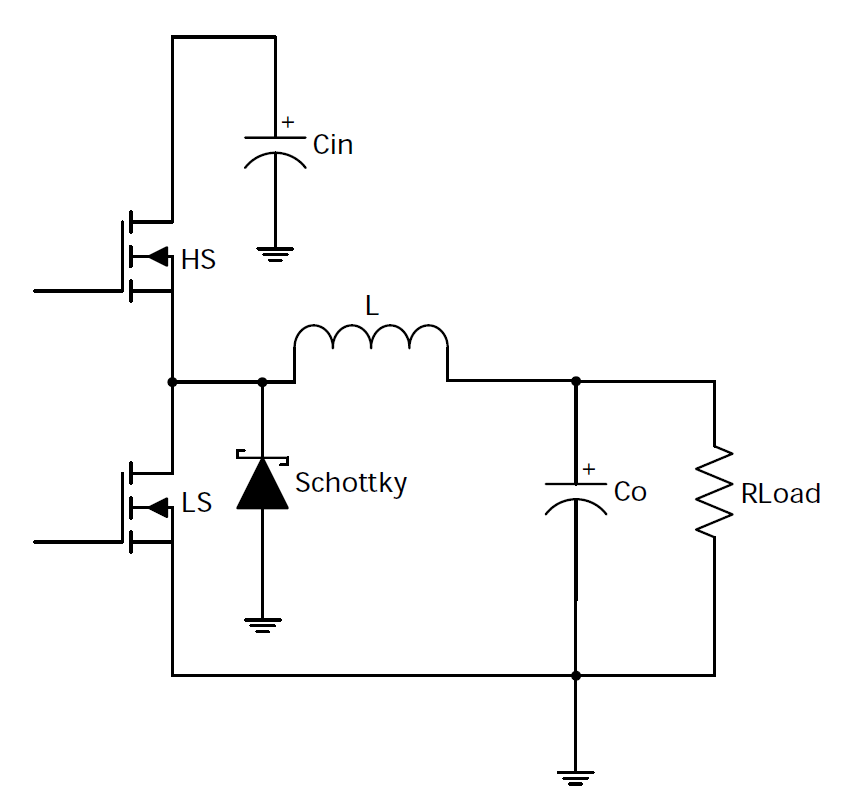

開關波形,顧名思義就是開關節點的波形,是上下管交替導通產生的周期性脈沖波,也是考量電源設計可靠性的重要指標:

為何要測量開關波形?從開關波形我們能得到什么信息呢?下面為大家介紹一下測量開關波形的目的:

01

判斷上下管是否有直通的風險

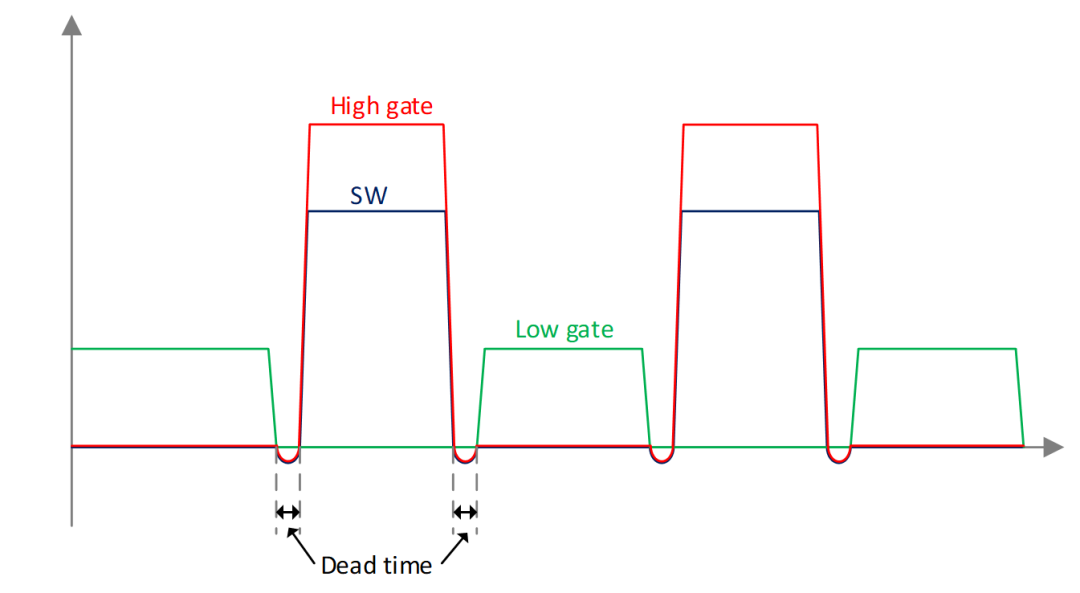

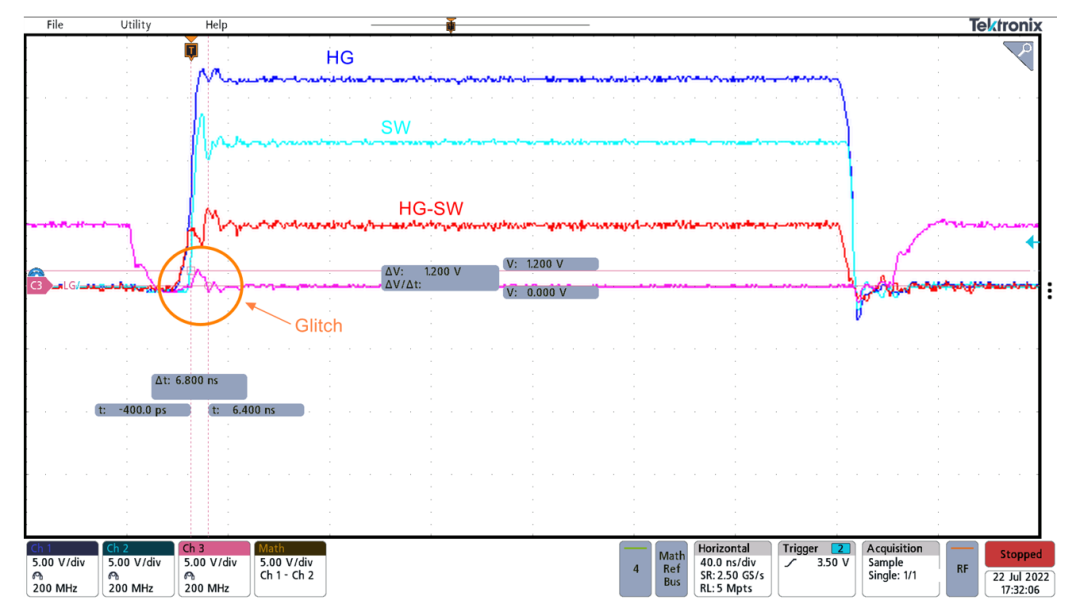

MOS驅動信號和SW波形如下圖所示:

為了避免上管和下管同時導通,MOS驅動在上下管切換時加上死區時間(dead time),此時上管和下管同時關斷,電流從下管的體二極管(body diode)流過,因此可以看到SW有一個小的負電壓(體二極管導通壓降)。

通常情況下,由于存在死區時間,不會有同時導通的風險,但是有的MOS開關速度較慢,在沒有完全關斷時,另外一個MOS就開始導通,從而導致出現直通,這種情況需要更換MOS搭配。

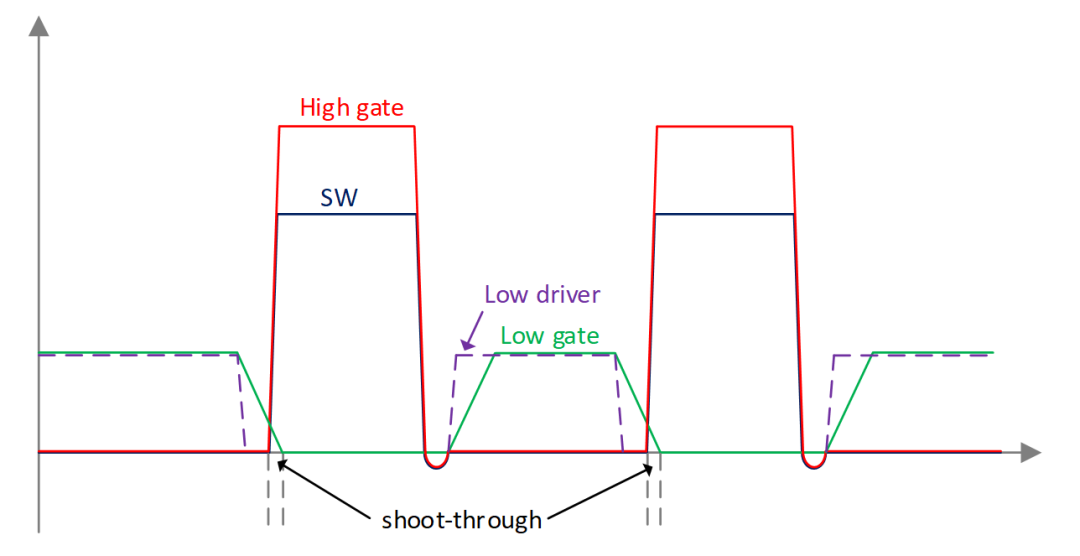

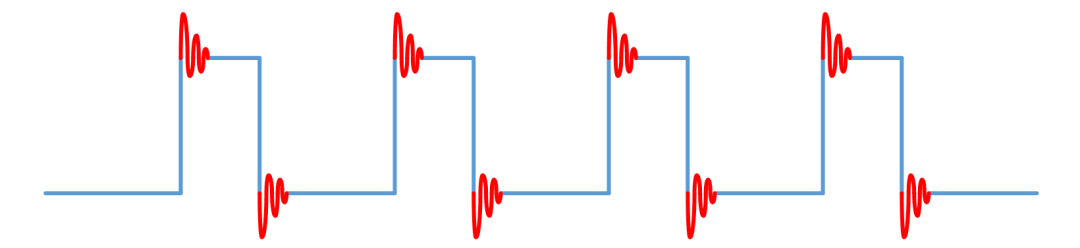

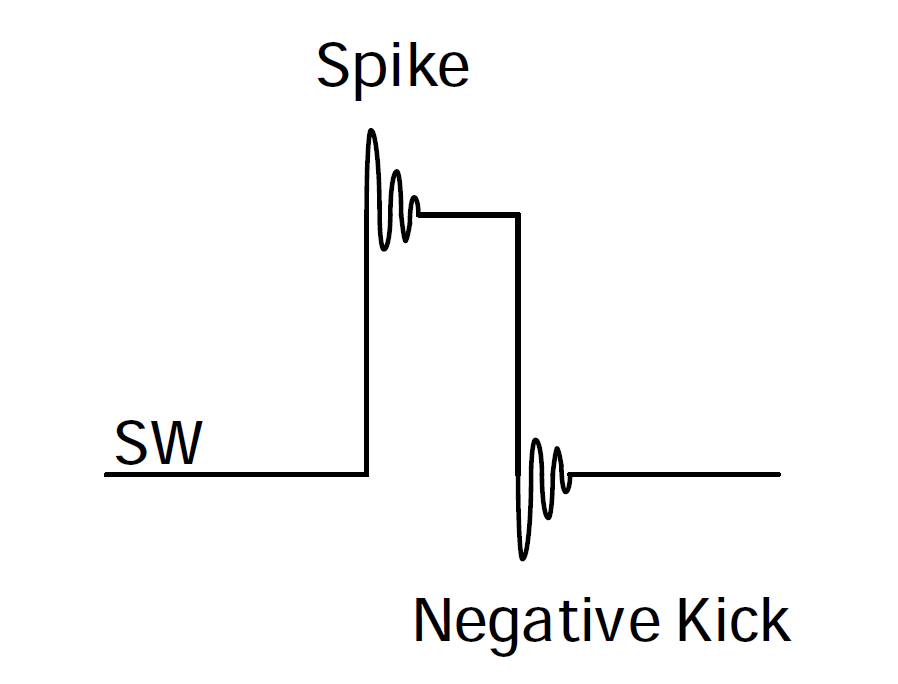

另外,理想狀態下,開關波形是標準的脈沖波,但是由于PCB走線和元器件存在各種寄生參數,實際的開關波形一般會存在一些振蕩,如下圖所示:

在上管導通時可能會導致下管驅動信號出現一個小尖刺,如果電壓足夠高,并且持續時間較長,就會導致下管導通,出現直通。

02

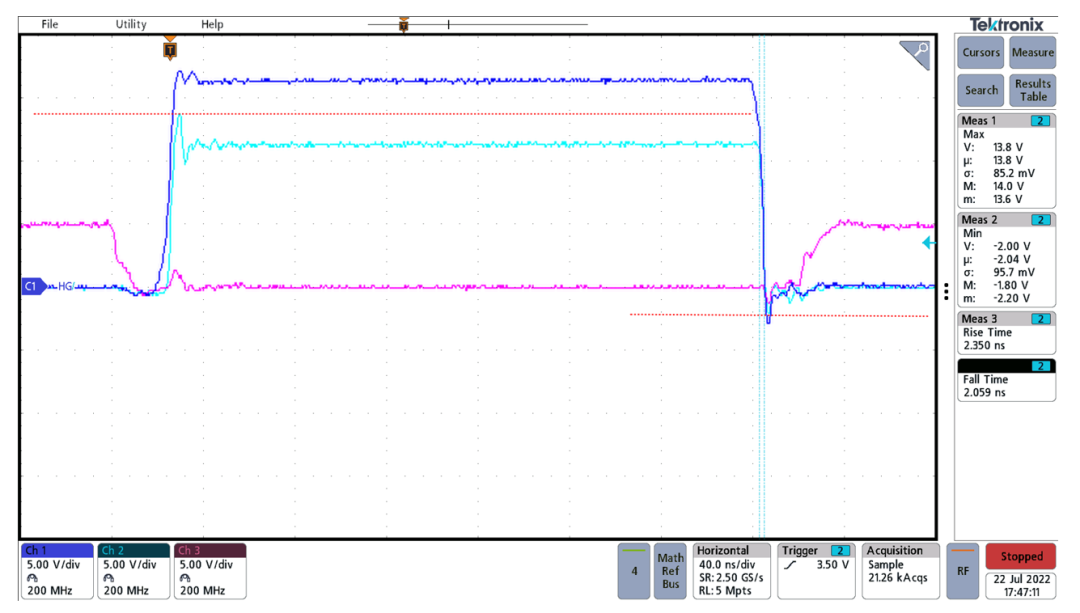

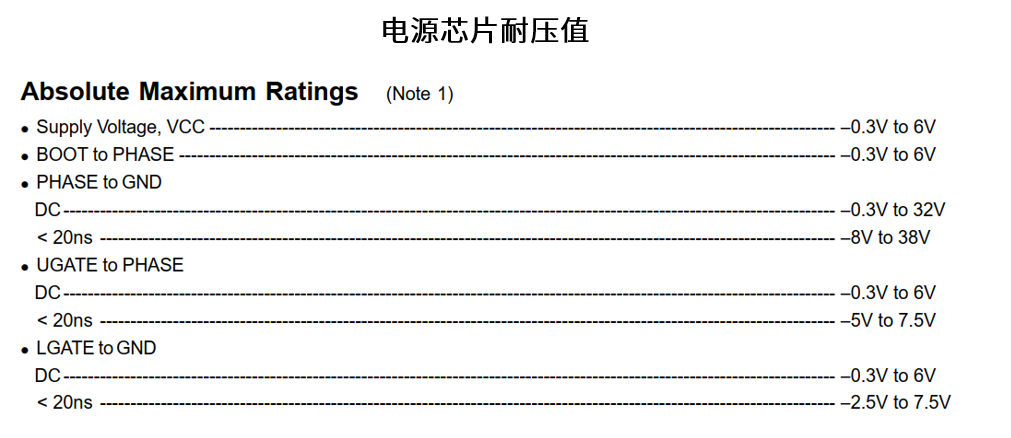

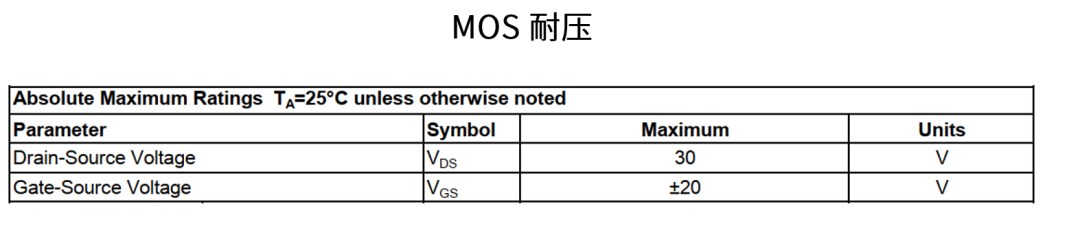

判斷是否超過器件耐壓

電源芯片或者MOS都有自身的耐壓,超過耐壓可能會導致器件失效,因此需要通過量測開關波形來確認是否有超過耐壓的風險。

03

判斷系統穩定性

通過量測開關波形的抖動,可以確認系統的穩定性,抖動越小則越穩定(此方法需要在穩態負載下測試)。

BPSemi

- 開關波形高頻振蕩-

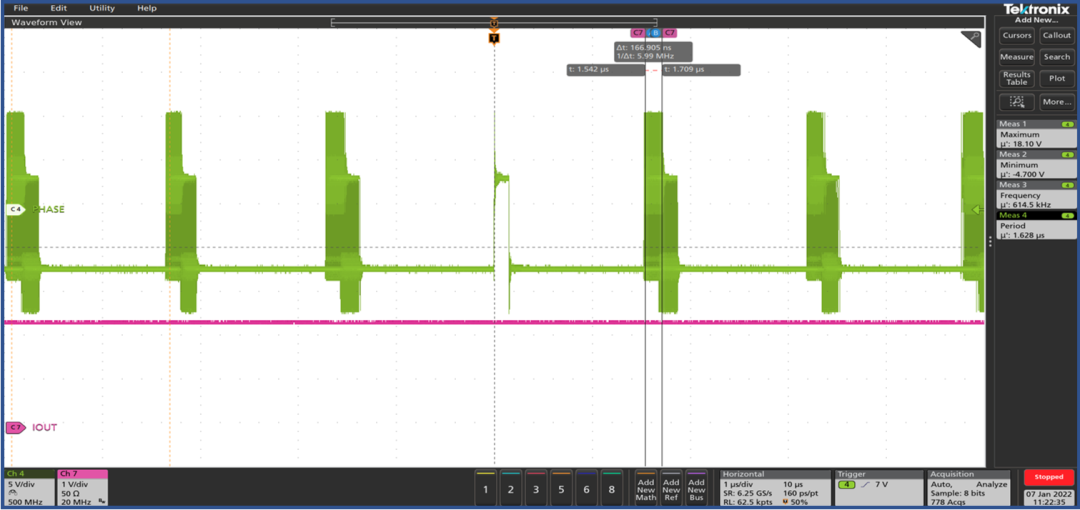

通過一些實測波形我們可以看到,在上管導通或者關斷時,開關波形都會產生較明顯的振蕩,那么這些振蕩產生的原因是什么呢?又會造成什么影響?下面將為大家詳細介紹一下。

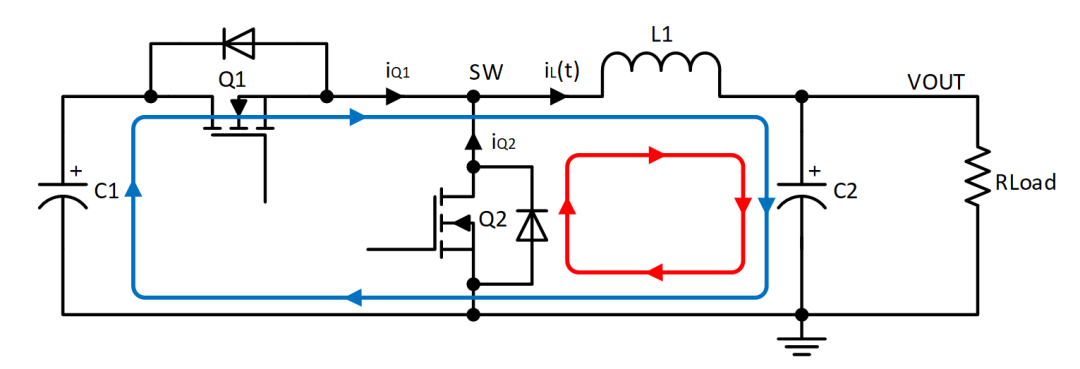

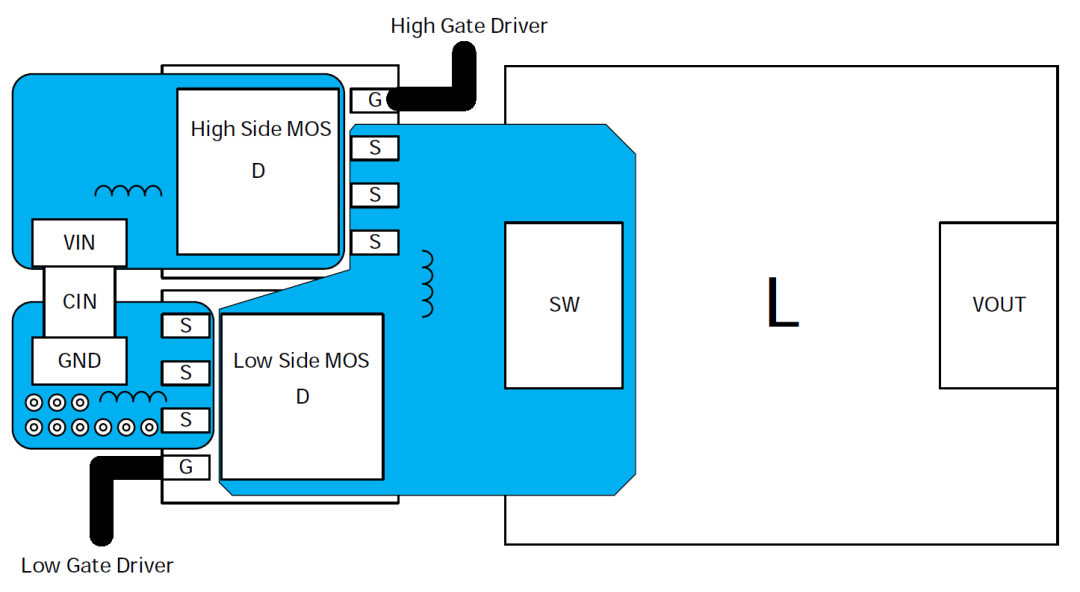

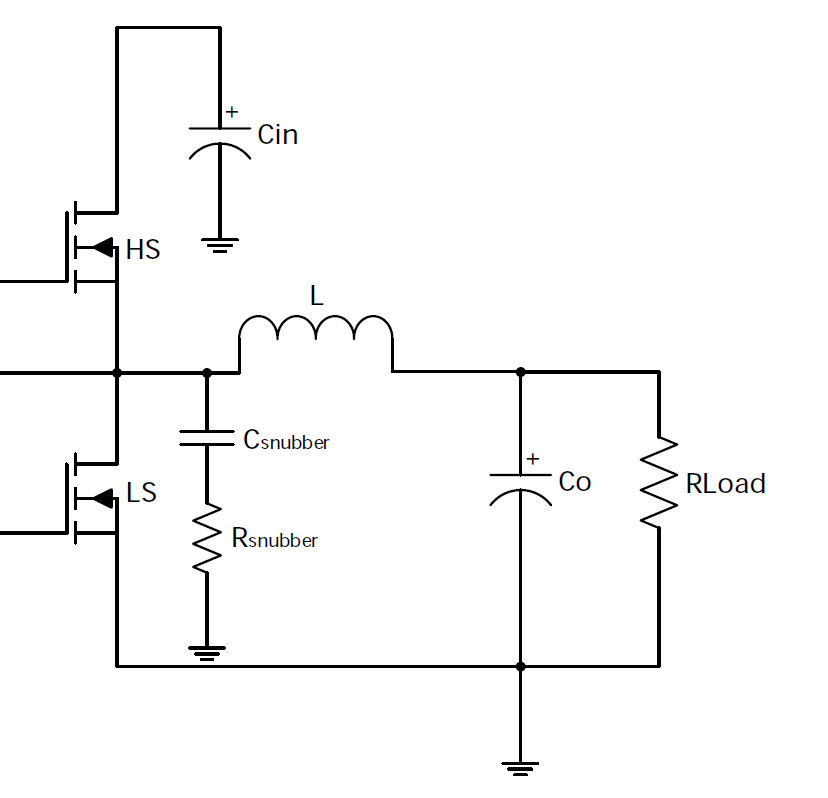

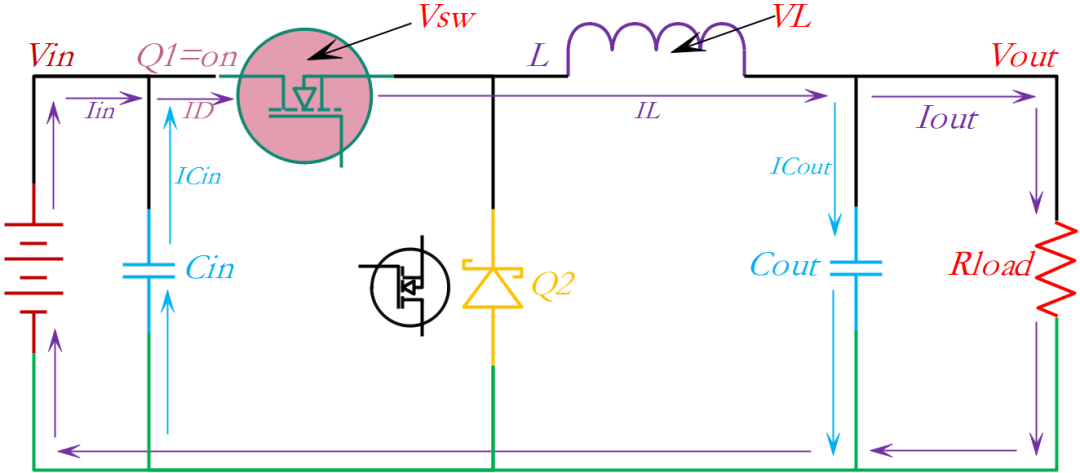

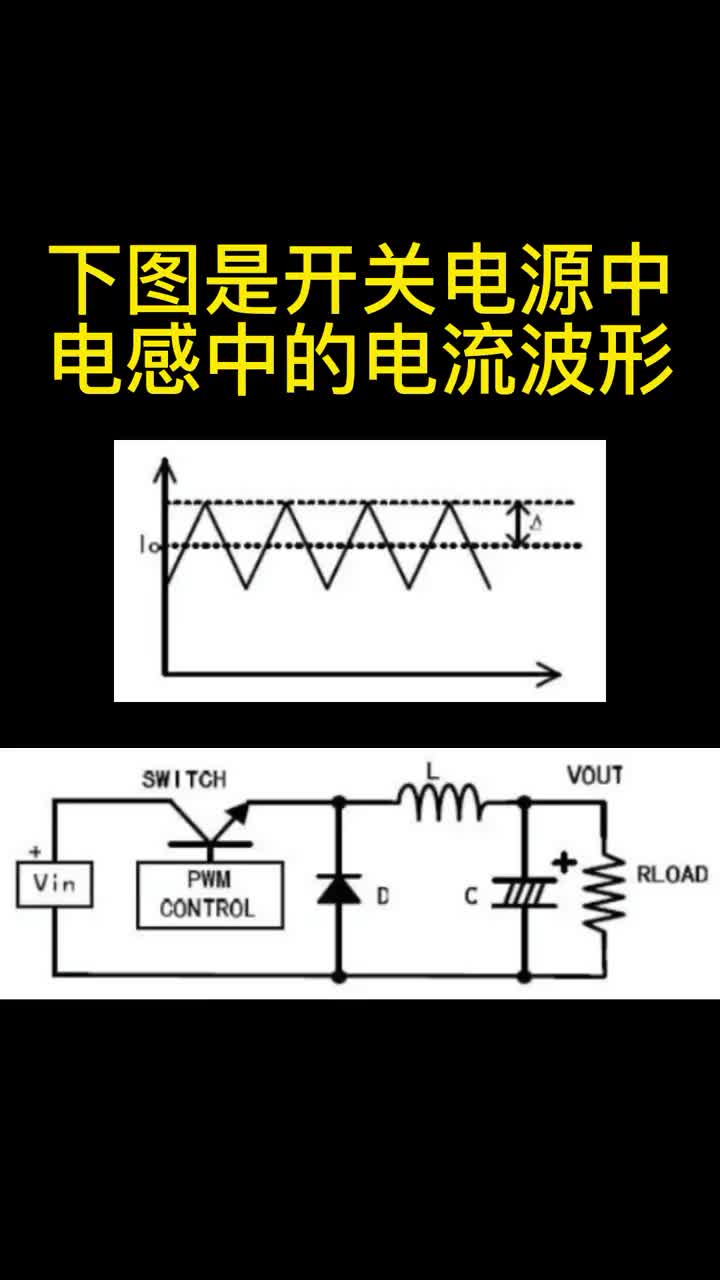

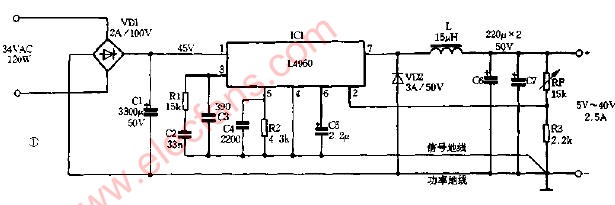

在這之前,我們先回顧一下開關電源的工作原理,如下圖所示:

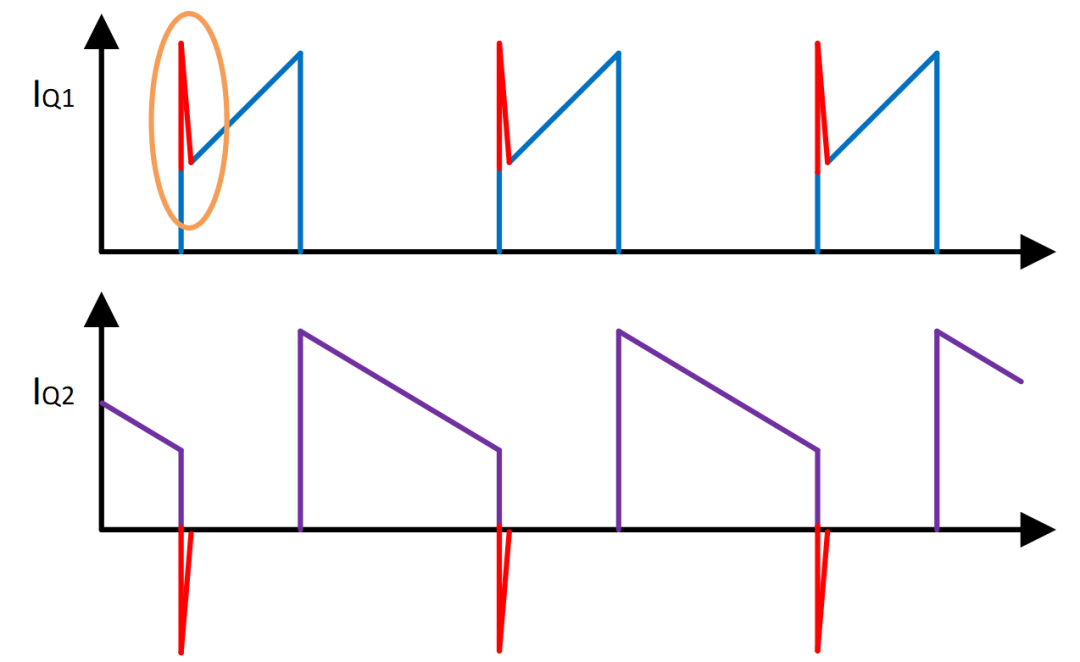

可以看到MOS在導通和關斷時,MOS的電流在非常短的時間內出現劇烈變化(從0到電感電流),這就導致了很大的電流變化率di/dt。

并且,由于下管存在體二極管,在上管導通時會存在反向恢復電流,這就導致了上管的電流在導通瞬間出現一個非常大的電流尖峰,這就形成了更大的電流變化率di/dt。

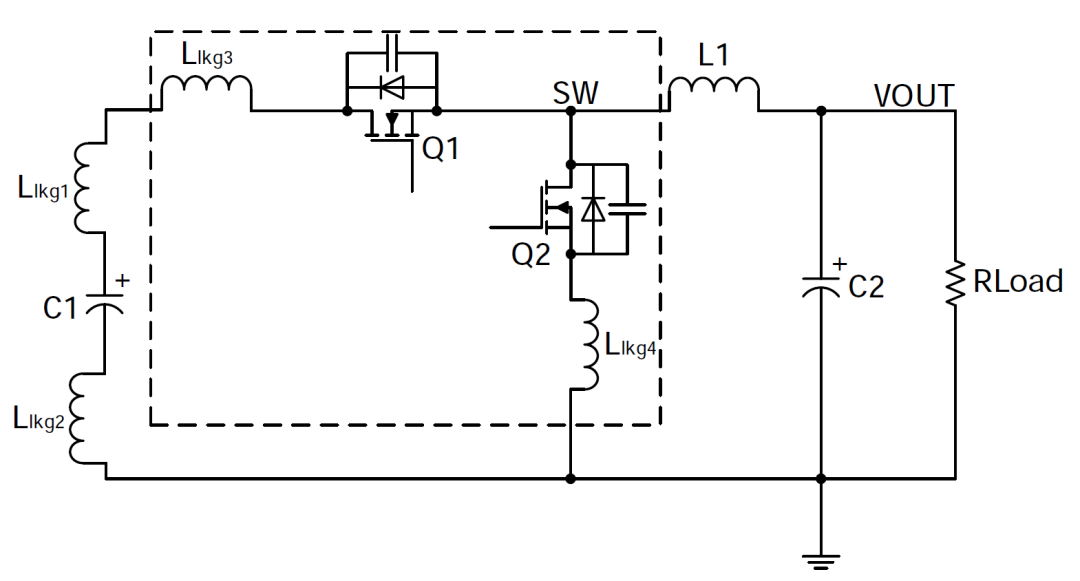

前面有提到,由于PCB走線和元器件存在寄生電感和寄生電容,在如此劇烈的電流變化條件下,會形成明顯的LC振蕩(同時有寄生電阻,實際為RLC阻尼振蕩)。

可以看到,寄生電感主要有PCB走線引起的Llkg1和Llkg2,以及MOS內部打線引起的Llkg3和Llkg4。這些寄生電感跟MOS本身的寄生電容形成LC諧振電路,當路徑上的電流發生劇烈跳變時,發生振蕩,并且形成很高的電壓尖峰。

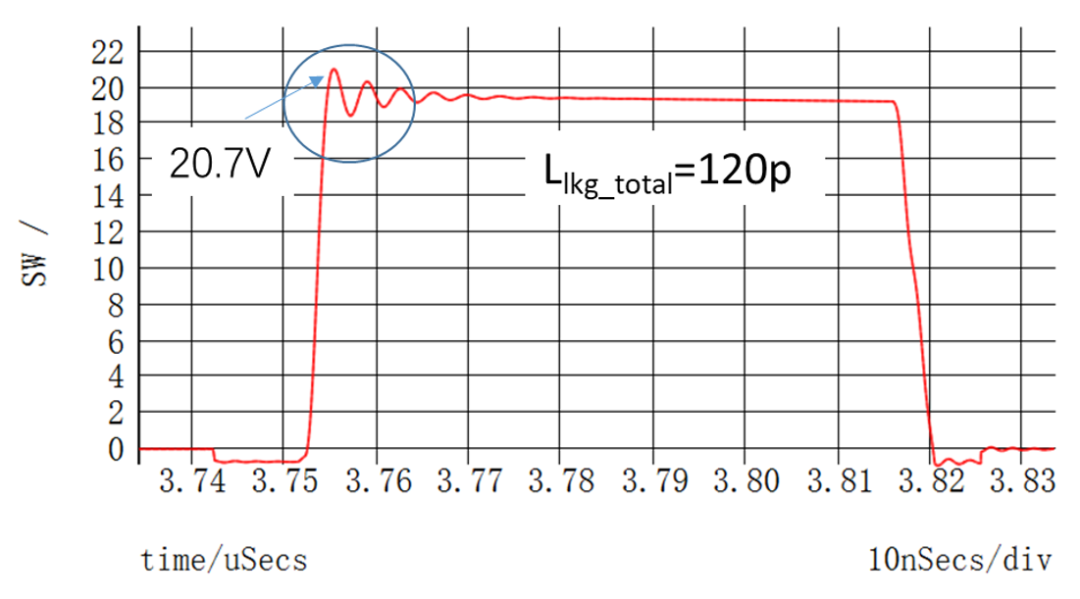

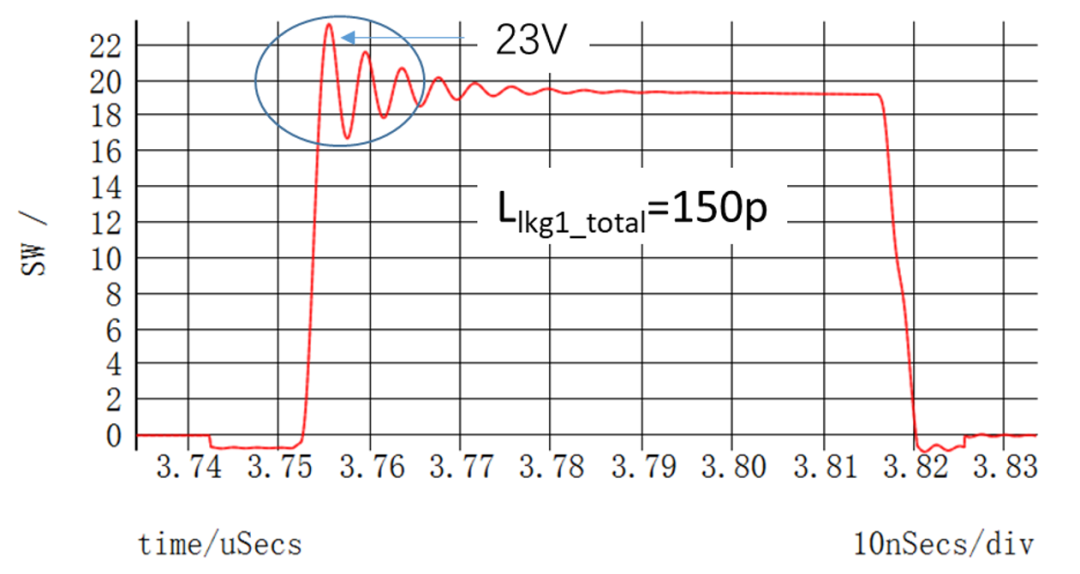

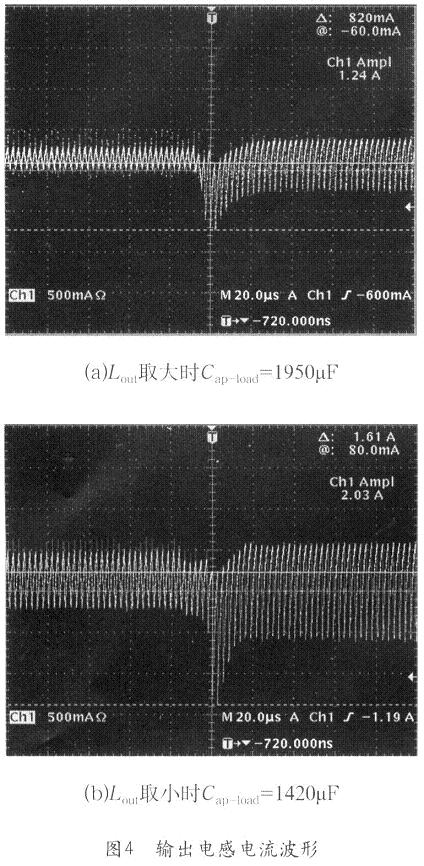

通過仿真對比,我們看到,總的寄生電感值Llkg_total影響正的電壓尖峰,增大Llkg_total,正向電壓尖峰也會變大。

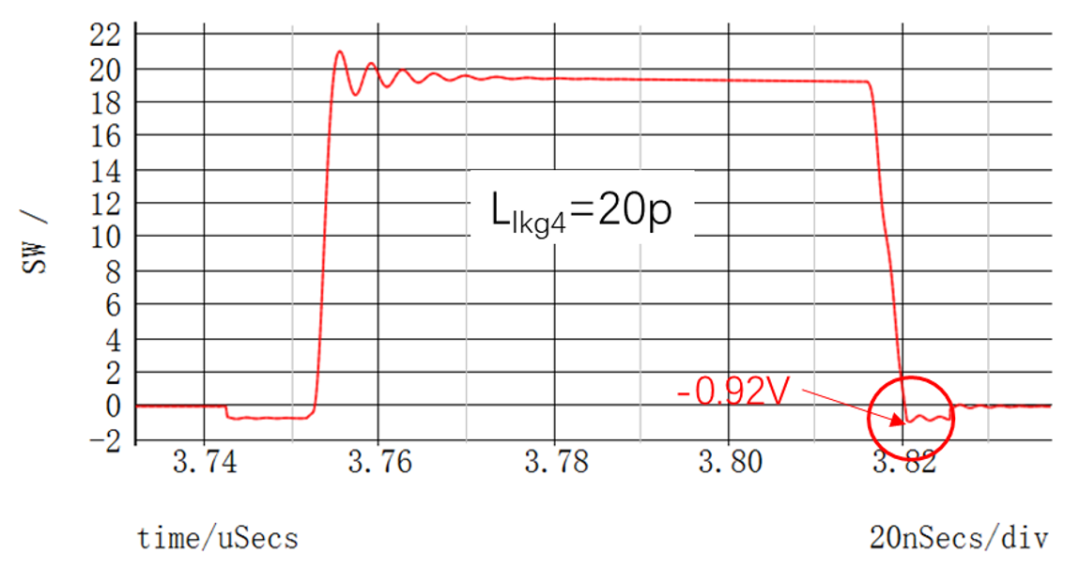

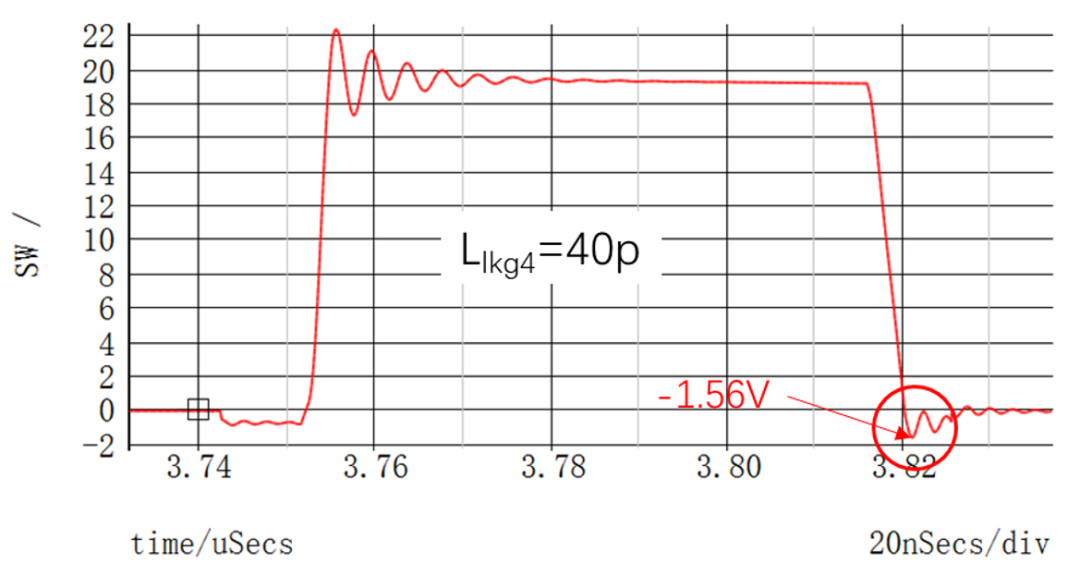

而下管到GND的路徑上的寄生電感對負壓影響比較大,增大這個寄生電感,負壓也會變大。

產生振蕩的原因我們已經了解了,那這個振蕩會對電源系統造成什么影響呢?主要有如下幾點:

振蕩形成的正向尖峰電壓和負壓,可能會超過器件耐壓,造成器件損壞;

振蕩波形干擾MOS驅動信號,可能會導致上下管直通的風險

高頻振蕩造成強烈的EMI,影響其他器件工作

因此,為了系統能更穩定的工作,我們需要盡量減小開關波形的高頻振蕩。

BPSemi

- 如何改善高頻振蕩-

從前面的分析,我們可以看到,振蕩的主要原因是寄生電感和快速的電流變化,因此改善方案也主要從這幾個方面入手:

01

減小寄生電感

這個可以分為兩個方面:PCB走線,MOS內部封裝。

對于PCB走線,需要盡量減小輸入電容VIN→上管→下管→GND的環路,并且下管的GND盡量多打過孔,以減小寄生電感。

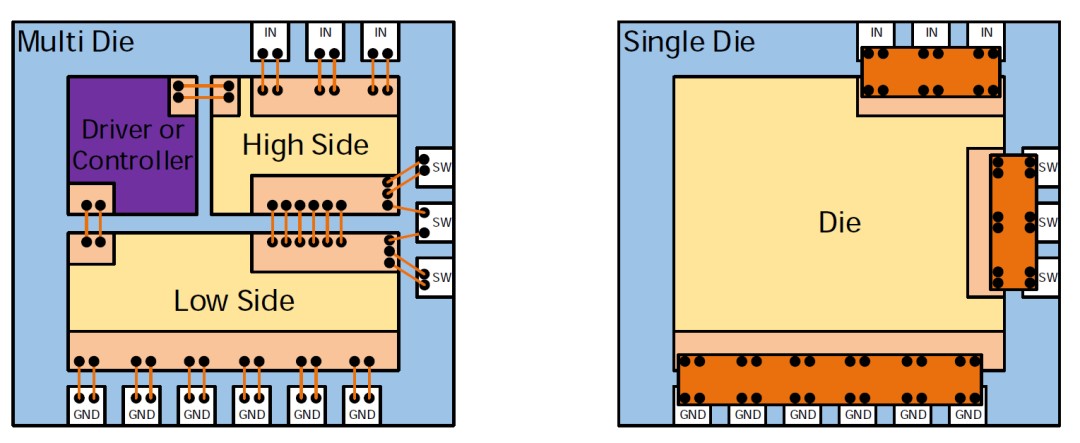

而對于MOS部分,則盡量選用集成方案,比如DrMOS,converter等。single die的DrMOS和converter,由于基本沒有打線,寄生電感比multi die的更低。

晶豐明源提供的功率級方案(DrMOS,POL等)都是采用singledie的設計,因此可以獲得更好的性能。

02

降低MOS導通和關斷的速度

另外一個減小振蕩的方法,則是通過降低MOS的開關速度,從而減小電流變化率(涉及到MOS的開關過程,此處不作詳細描述,如有興趣可以持續關注晶豐明源公眾號)。

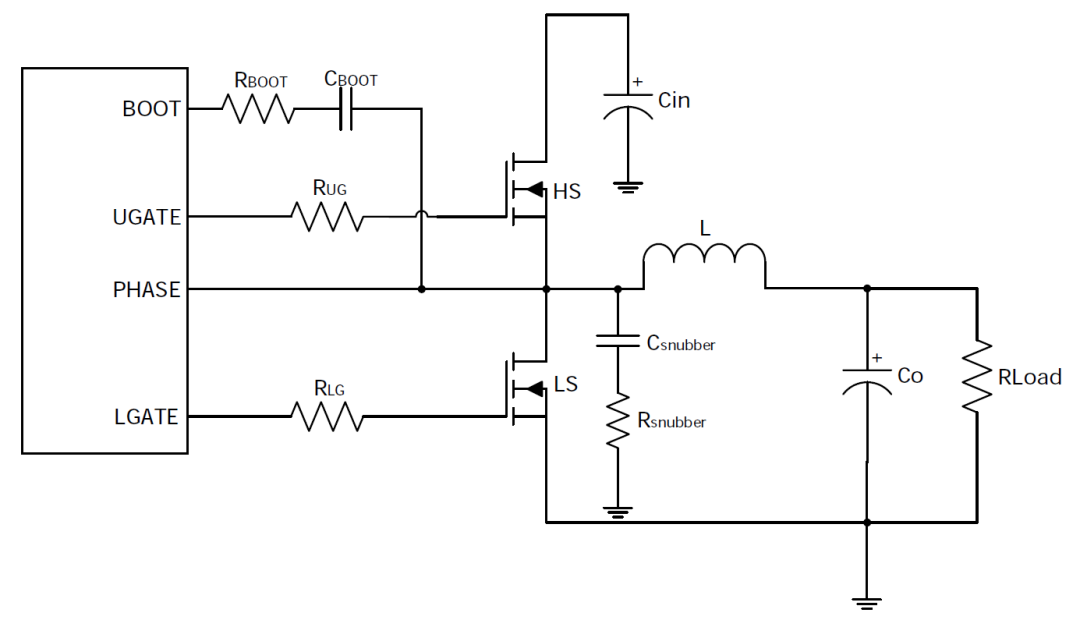

通常我們的原理圖上都會增加BOOT電阻和驅動電阻,通過增大這兩個電阻的阻值,可以有效降低MOS的開關速度。

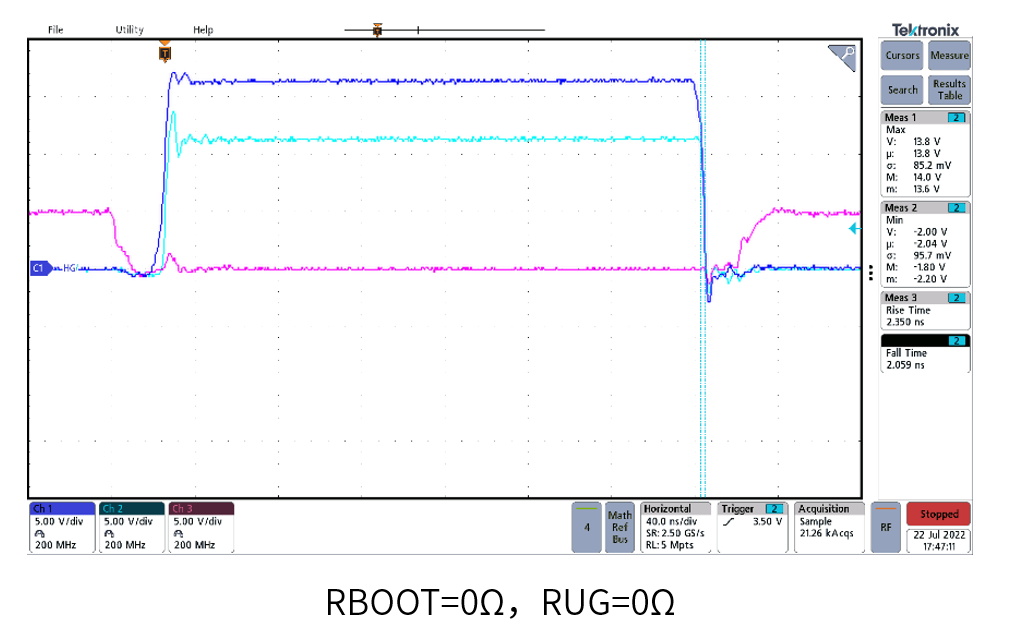

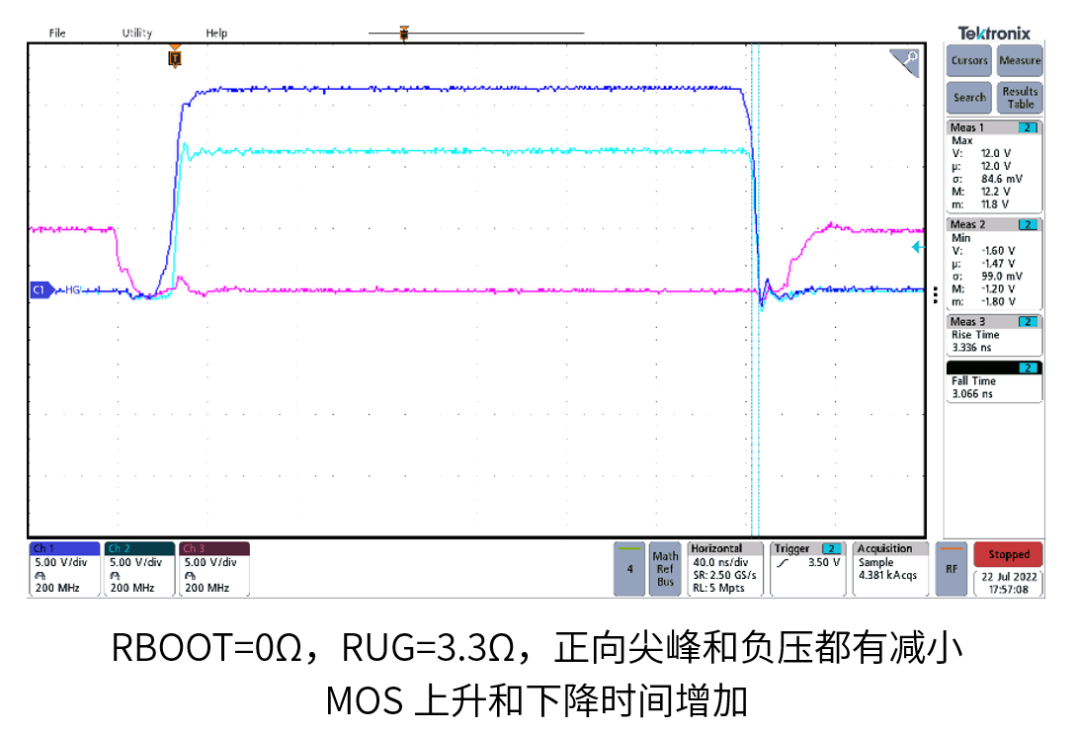

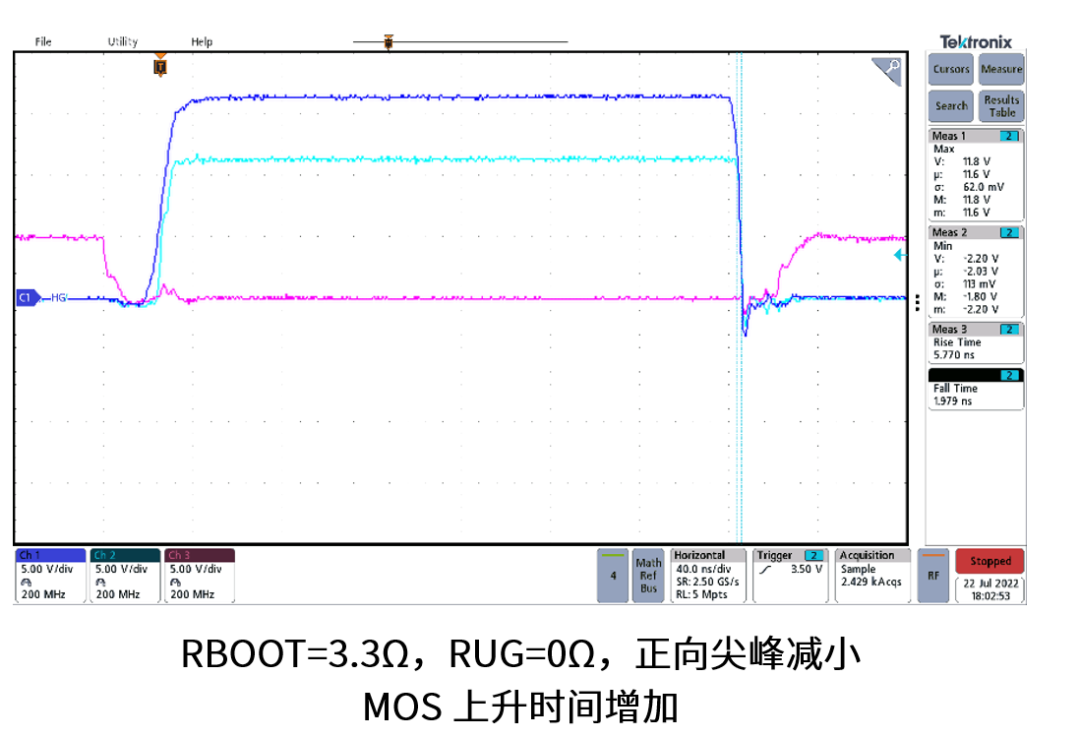

其中,增大BOOT電阻只對上管導通的速度有影響,對關斷的速度沒有影響;增大驅動電阻RUG,則同時影響上管的導通和關斷速度,實際對比如下:

03

增加RC吸收電路

第三種方法,則是在SW增加對地的RC電路,吸收振蕩能量。不過需要注意的是,RC接地盡量單獨接到公共的地平面,避免下管接地引起的寄生電感影響效果。

RC的參數,電阻一般選擇1~10Ω,電容在nF級,需要經過實測確認。

04

下管并聯肖特基二極管

除了降低MOS開關速度,還有個辦法可以減小電流尖峰:在下管并聯一顆肖特基二極管。肖特基二極管的反向恢復特性比普通二極管好(一般MOS內部寄生的二極管是普通二極管),因此可以有效降低反向恢復電流。同理,肖特基二極管的地也盡量單獨接到功率地。

BPSemi

- 總結-

降低開關波形高頻振蕩的方法總結如下:

優化PCB布局和走線,盡可能減小輸入電容和MOS的電流環路

選用集成MOS方案,最好是single die

增加MOS驅動電阻和BOOT電阻

增加RC snubber

下管并聯肖特基二極管

其中增加驅動電阻和snubber會造成效率下降,需要取舍;下管并聯肖特基二極管還可以提高效率,但是會增加成本和PCB空間,因此最好是layout優化和采用single die集成方案。

晶豐明源DCDC,超過100位行業頂尖精英的強大團隊,構建研發、運營、銷售的完整產業鏈條,擁有數字控制IP、大電流設計IP、BCD工藝、封裝等核心技術。高標準可靠性實驗室,具備高溫老化、高加速應力、溫度循環等多種可靠性鑒定和可靠性監控能力,每一款量產產品,都經過嚴苛的測試,確保產品的穩定可靠。我們志在追趕國際巨頭的技術優勢,躋身計算電源的重磅玩家。

電子發燒友App

電子發燒友App

評論