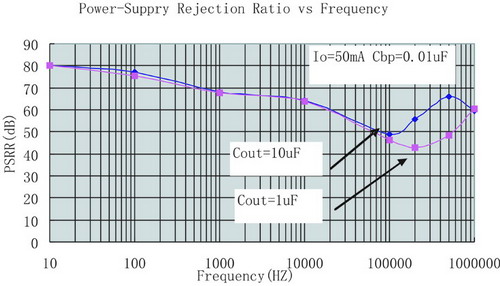

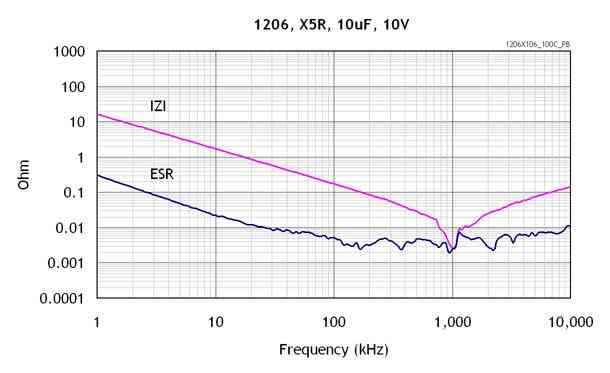

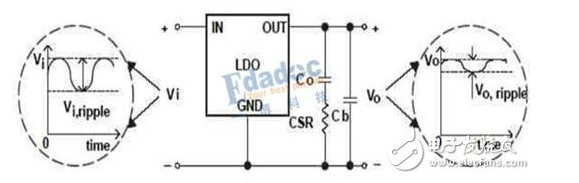

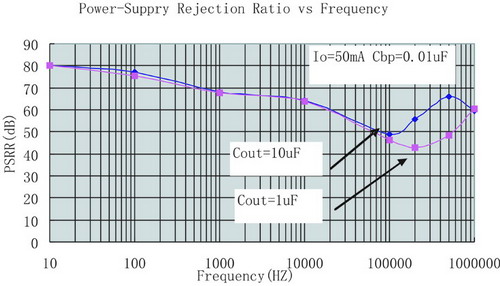

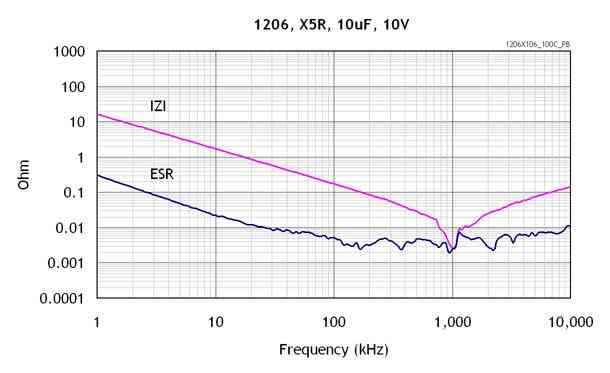

LDO的輸出電容對(duì)性能至關(guān)重要,除了會(huì)提高電源抑制比PSRR抑制噪聲外,對(duì)環(huán)路穩(wěn)定性也至關(guān)重要,電容除了容值參數(shù)外還有ESR(Equivalent Series Resistance)等效串聯(lián)電阻參數(shù),二者在選型設(shè)計(jì)時(shí)都要仔細(xì)考慮。

2022-07-12 18:31:24 4741

4741

LDO是一種微功耗的低壓差線性穩(wěn)壓器,它通常具有極低的自有噪聲和較高的電源抑制比PSRR(PowerSupplyRejectionRatio)。

2011-09-29 10:46:00 3601

3601

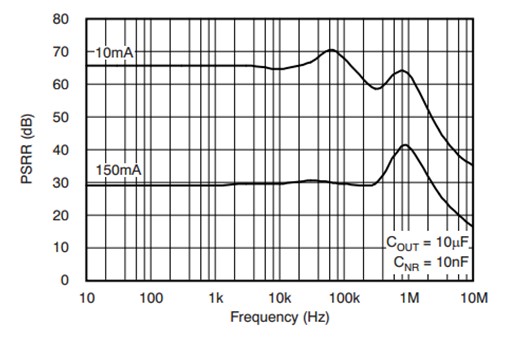

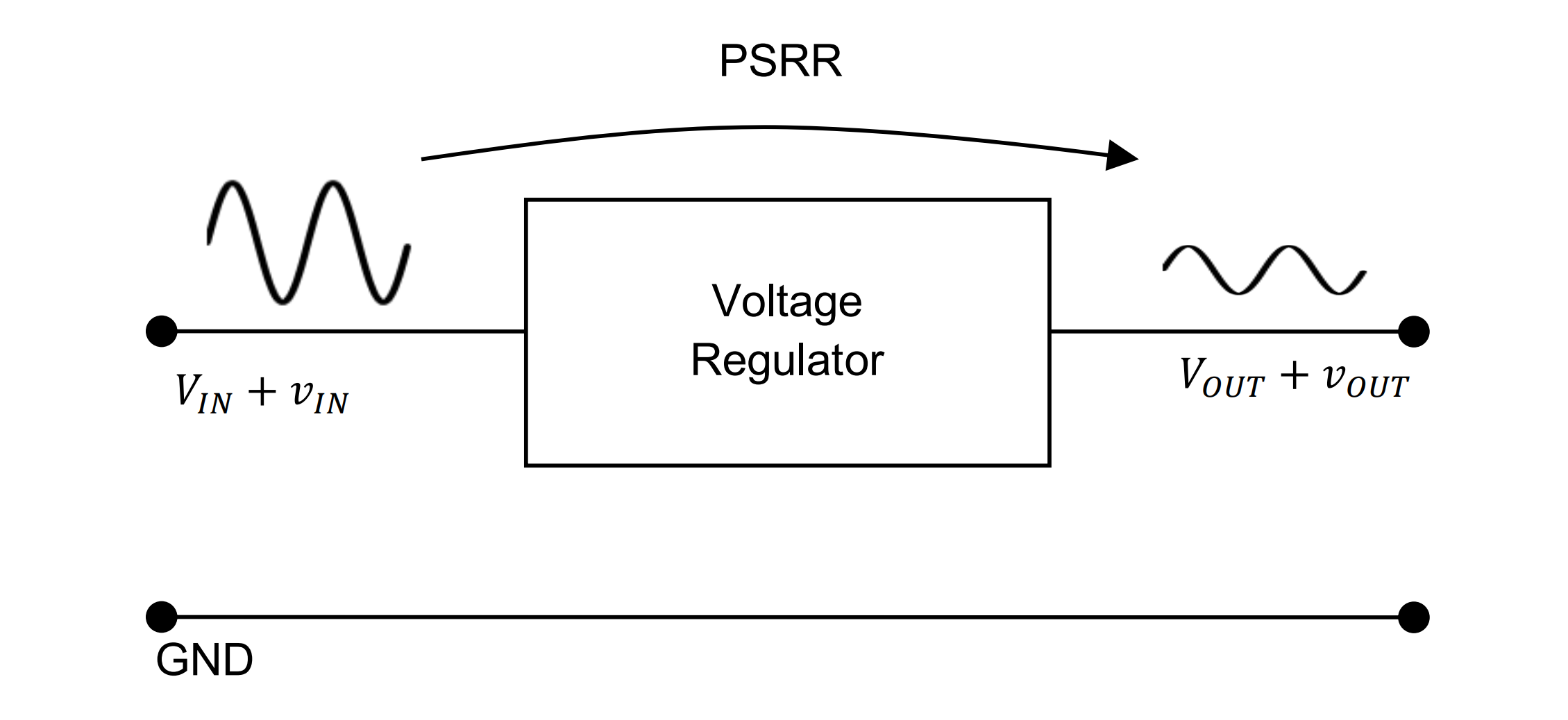

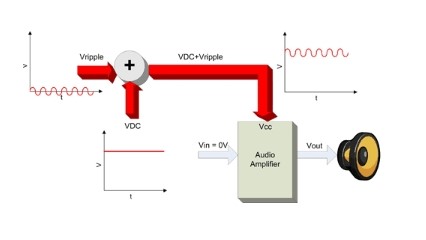

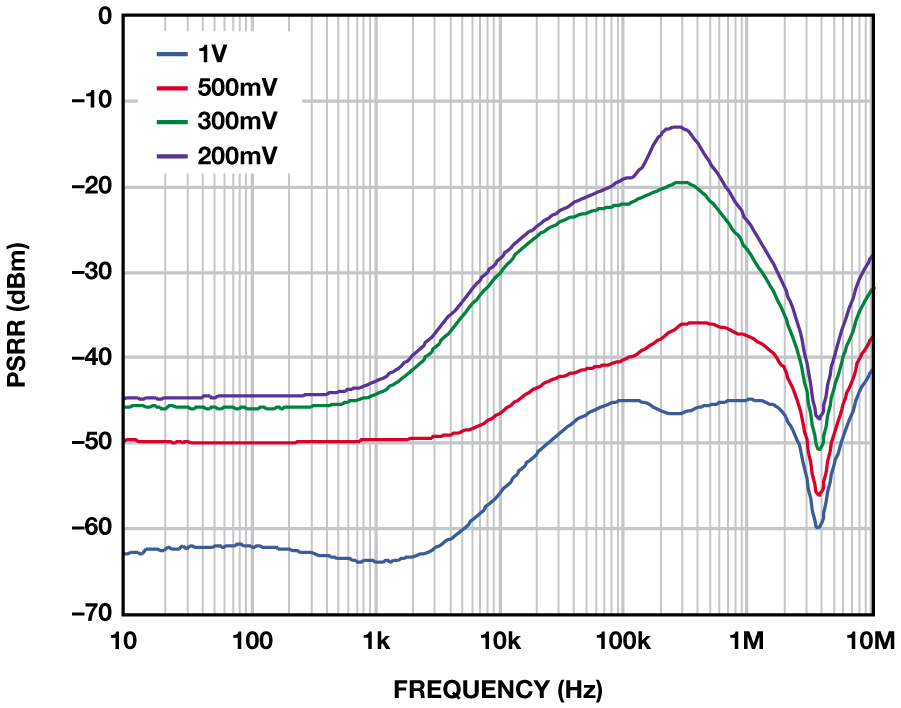

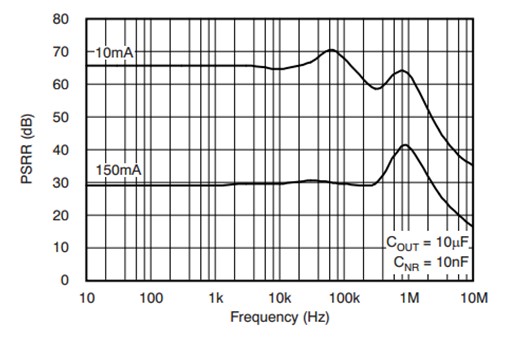

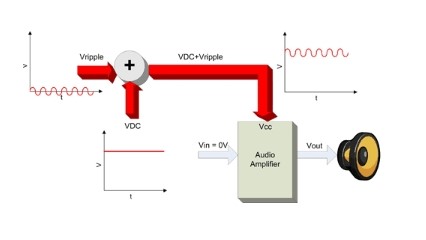

Ramus在博客中介紹了噪音對(duì)信號(hào)調(diào)節(jié)設(shè)備的不利影響:減少高速信號(hào)鏈電源問(wèn)題。然而,電源抑制比(PSRR)仍然通常被誤認(rèn)為單一的靜態(tài)值。在這篇文章中,我將嘗試說(shuō)明什么是PSRR以及影響它的變量有哪些。 什么是 PSRR ? PSRR是許多LDO數(shù)據(jù)手冊(cè)中的公

2018-06-28 10:16:00 24712

24712

如果LDO電源也輸出那么高電流的時(shí)候還不是一樣比較差?答案是。。.。.LDO電源一般不可能有那么高的電流輸出,為什么呢?繼續(xù)以LM2941模型進(jìn)行下面的仿真。

2020-09-14 11:17:26 2313

2313

電源抑制比 (PSRR) 用于衡量 LDO 清除或抑制由上游其他元件傳入噪聲的能力。對(duì)于高端 ADC,為了更大限度地減少位錯(cuò)誤,輸入電源噪聲要求不斷提高。

2022-03-09 09:24:03 1093

1093

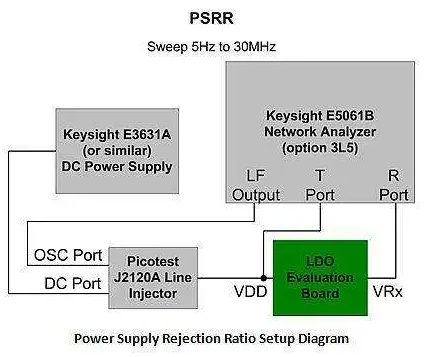

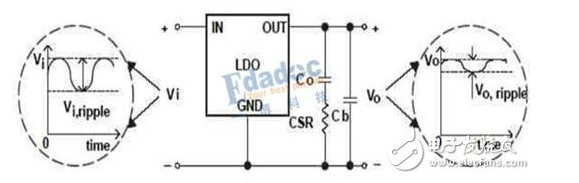

低壓差線性穩(wěn)壓器(LDO)相比 DC-DC 的優(yōu)點(diǎn)之一,是輸出電壓紋波小。但是高速電路下,LDO 的電源抑制比(PSRR)也是不可忽略的因素,通常被誤認(rèn)為是單一的靜態(tài)值,本篇文章將詳細(xì)講解電源抑制比(PSRR)及如何測(cè)量它。

2022-08-30 17:09:25 14841

14841

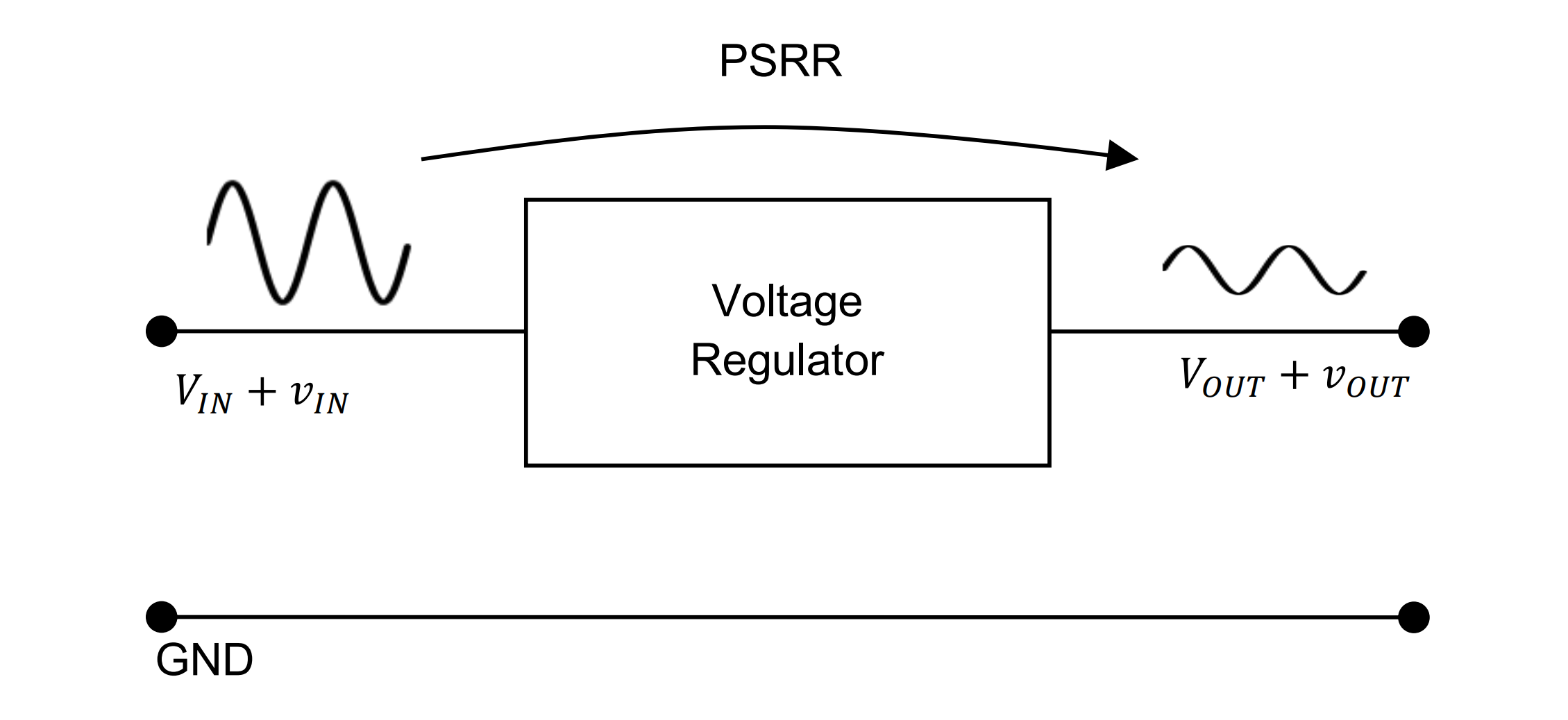

電源抑制比 ,英文名Power Supply Rejection Ratio,簡(jiǎn)稱(chēng)PSRR,它描述了電路抑制任何電源變化傳遞到其輸出信號(hào)的能力,通常以dB為單位進(jìn)行測(cè)量,用來(lái)描述輸出信號(hào)受電源

2022-09-09 15:37:05 34936

34936

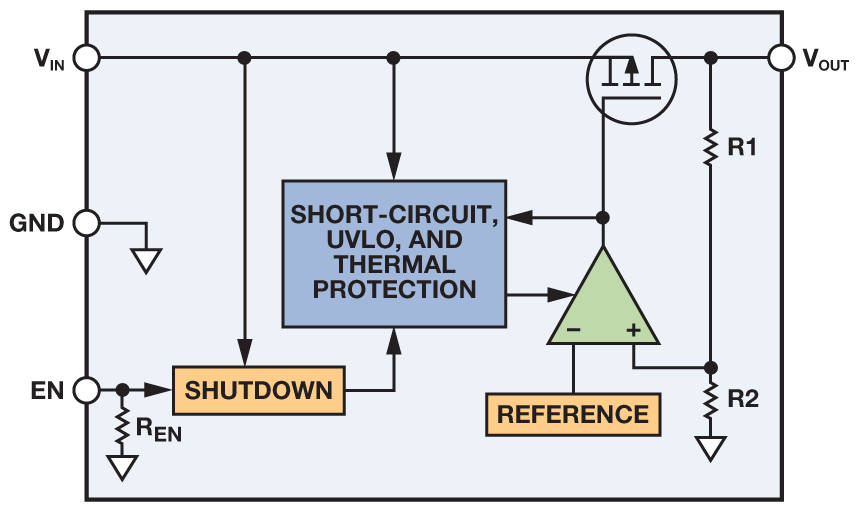

在本文中,我們將介紹噪聲和電源抑制比 (PSRR) 在低壓差 (LDO) 穩(wěn)壓器中的影響。讓我們簡(jiǎn)要討論一下什么是 LDO。

2023-09-26 14:29:43 2236

2236

在本文中,我們將介紹低壓差 (LDO) 穩(wěn)壓器中噪聲和電源抑制比 (PSRR) 的影響。讓我們簡(jiǎn)單討論一下什么是 LDO。

2024-03-15 17:12:08 638

638

的PSRRLDO 的一個(gè)重要的指標(biāo),就是PSRR。這是一個(gè)電源電壓噪聲抑制系數(shù)。簡(jiǎn)單的說(shuō),輸入電源上的紋波【很多情況下,不是系統(tǒng)需要的,或則是系統(tǒng)希望沒(méi)有的】,經(jīng)過(guò)LDO 以后,能夠得到至少幾十個(gè)dB 的抑制

2017-04-01 16:11:04

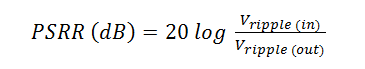

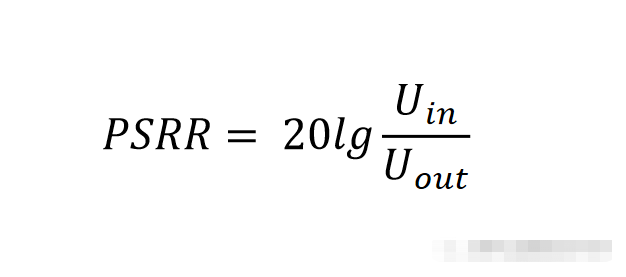

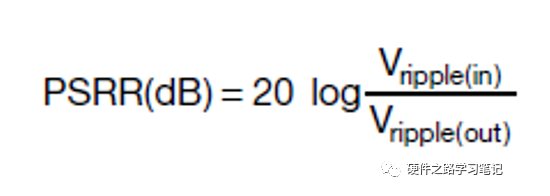

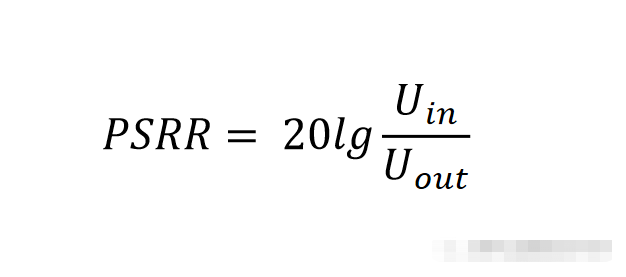

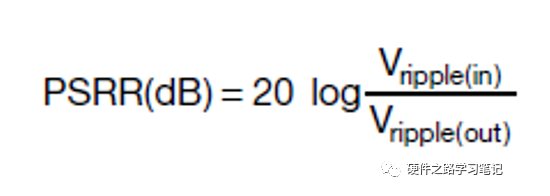

作者:Hao Wang深圳模擬工程師PSRR是什么PSRR(Power supply rejection ratio)又稱(chēng)電源抑制比,是衡量電路對(duì)于輸入電源中紋波抑制大小的重要參數(shù),表示為輸出紋波

2019-03-20 06:45:01

PSRR(Power supply rejection ratio)又稱(chēng)電源抑制比,是衡量電路對(duì)于輸入電源中紋波抑制大小的重要參數(shù),表示為輸出紋波和輸入紋波的對(duì)數(shù)比,單位為分貝(dB)[1],其

2022-11-11 06:09:55

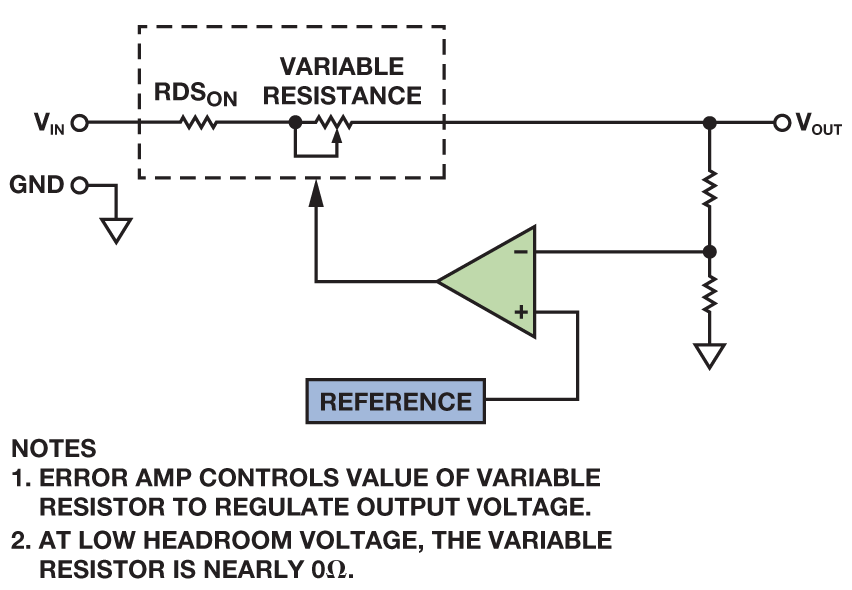

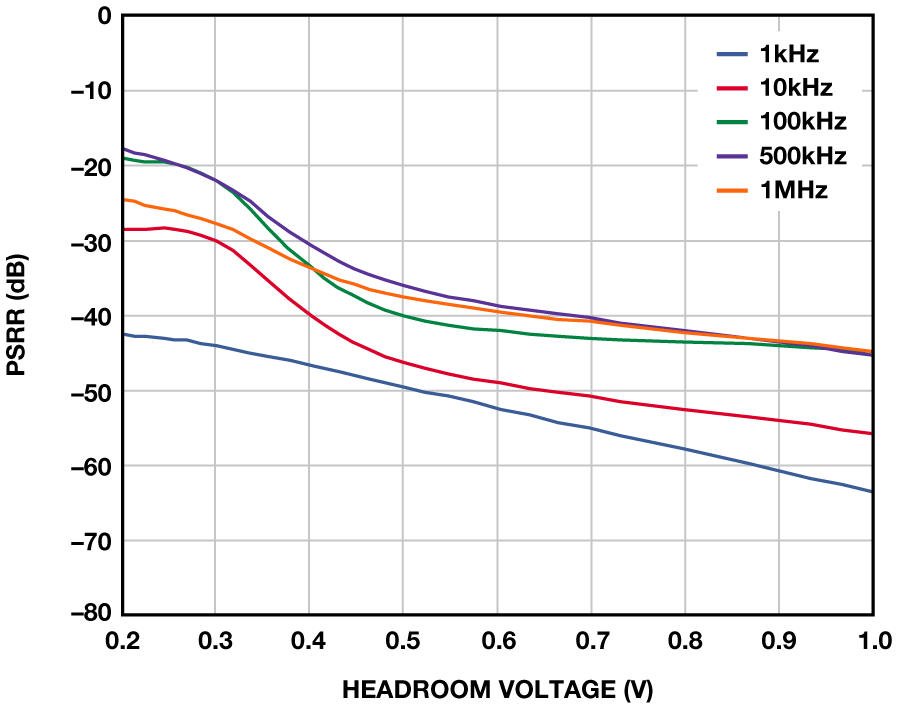

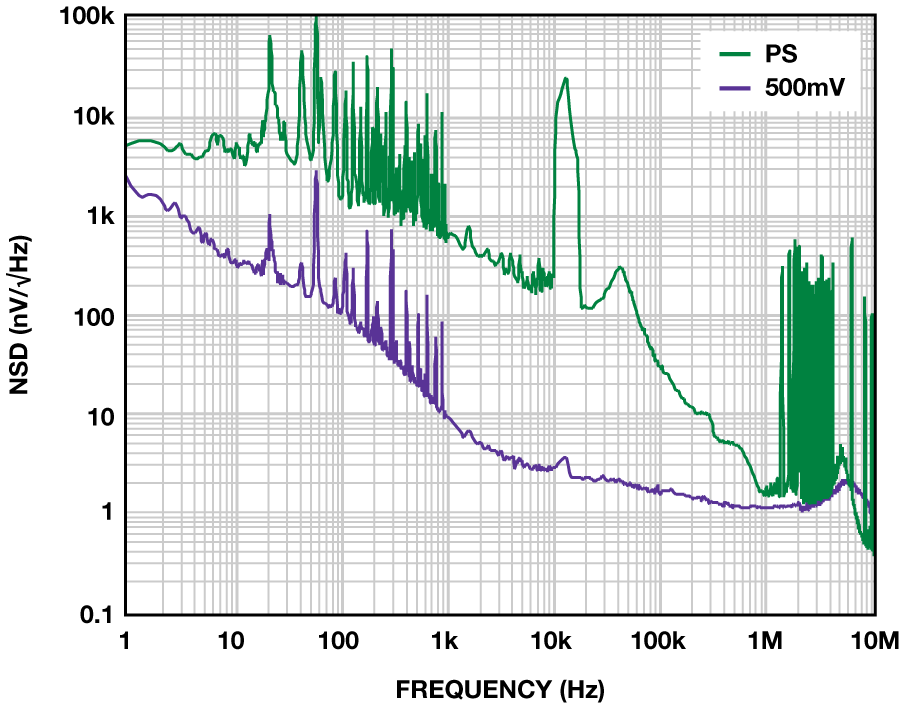

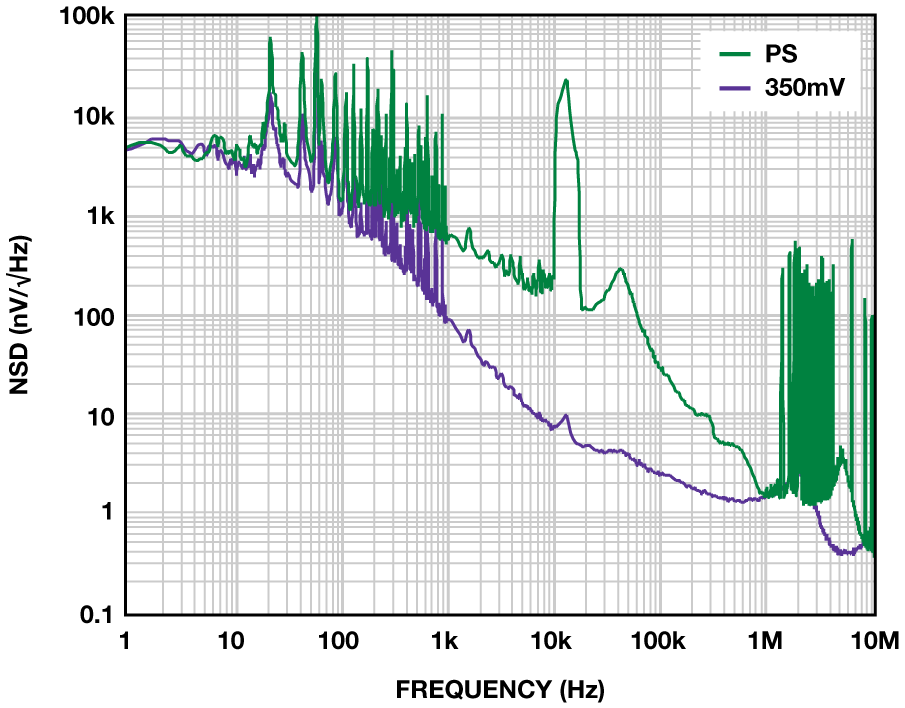

中的噪聲,但也需要,在功耗和增加的系統(tǒng)熱負(fù)荷之間做出權(quán)衡。為了緩解這些問(wèn)題,使用 LDO 時(shí),可使輸入和輸出電壓之間存在較小的壓差(裕量電壓)本文旨在討論低裕量電壓對(duì)電源抑制和總輸出噪聲的影響。LDO

2018-10-23 17:07:54

本文介紹了低壓差線性穩(wěn)壓器(LDO)的基本原理及選用原則,并將其應(yīng)用于開(kāi)關(guān)電源設(shè)計(jì)之中。這種設(shè)計(jì)方案簡(jiǎn)化了開(kāi)關(guān)電源的多路輸出設(shè)計(jì),減小了負(fù)載調(diào)整率,有效地抑制了電磁干擾(EMI),并加強(qiáng)了開(kāi)關(guān)電源的過(guò)流保護(hù)功能。

2021-04-13 06:47:16

1. 簡(jiǎn)化開(kāi)關(guān)電源設(shè)計(jì) 開(kāi)關(guān)電源多路輸出一般通過(guò)增加高頻變壓器反饋端來(lái)實(shí)現(xiàn),這使得開(kāi)關(guān)電源在設(shè)計(jì)過(guò)程中增加了設(shè)計(jì)者的工作量。應(yīng)用LDO作為開(kāi)關(guān)電源的輸出終端,可以極大地簡(jiǎn)化開(kāi)關(guān)電源

2021-10-29 09:25:50

如圖,請(qǐng)問(wèn)下LDO的紋波抑制比是否可以這樣測(cè)試,測(cè)試的LDO為3.3V輸出,規(guī)格書(shū)紋波抑制比40dB但實(shí)際上計(jì)算數(shù)差很多

2021-11-20 09:50:15

LDO線性穩(wěn)壓器的研究與設(shè)計(jì)隨著信息科學(xué)的快速發(fā)展,電源技術(shù)變得越來(lái)越重要。因低壓差線性穩(wěn)壓器(LDO)的體積小,高電源抑制比,功耗小,低噪聲以及應(yīng)用端電路簡(jiǎn)單等優(yōu)點(diǎn)在眾多電源中,受到人們的普遍關(guān)注

2009-12-02 11:07:59

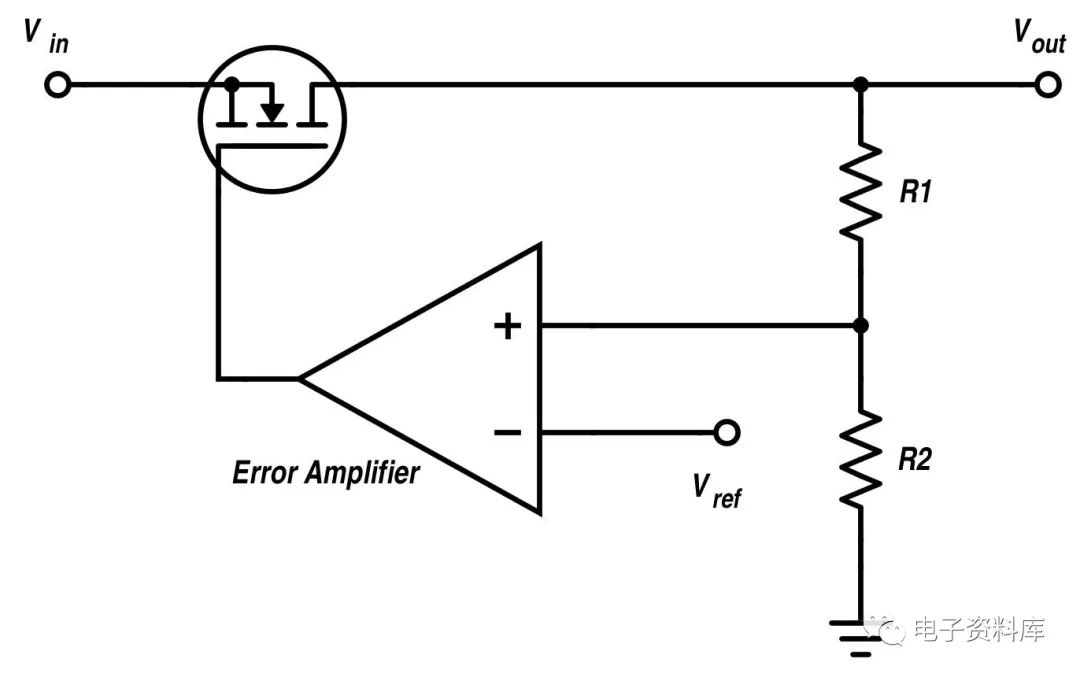

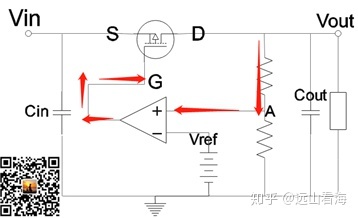

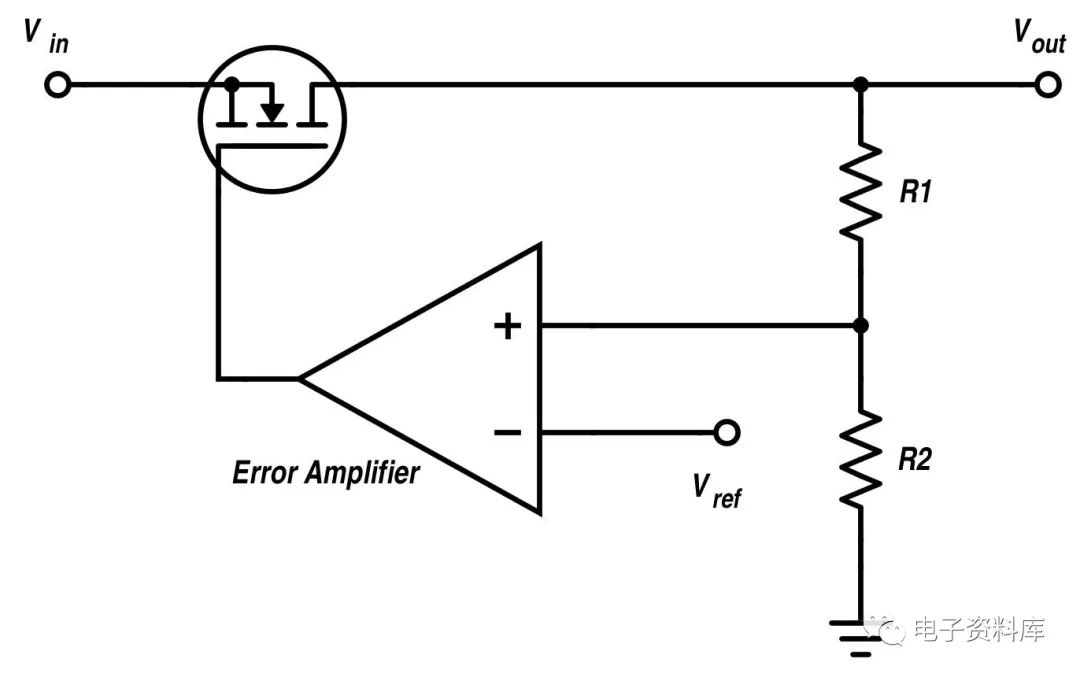

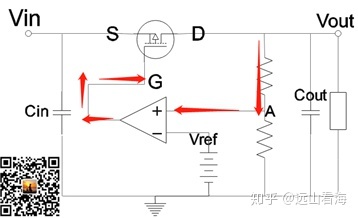

Dropout Regulator),屬于線性電源,應(yīng)用時(shí)所需要的外接元件比較少,大部分型號(hào)的LDO只需在輸入端和輸出端各接一個(gè)濾波電容。如下圖所示: 其內(nèi)部結(jié)構(gòu)如下圖所示: 從原理框圖中我們可以看到

2023-04-04 14:52:41

近期,項(xiàng)目遇到的問(wèn)題,不得不考慮ldo的紋波抑制比問(wèn)題,在選型時(shí),確實(shí)沒(méi)有仔細(xì)研究,咨詢所選電源芯片的廠家后,才得知,自己選的這個(gè)芯片,紋波抑制不是很好。具體什么是紋波抑制比,腦子里倒是有,還是準(zhǔn)確

2021-07-30 06:38:39

輸出電壓就是我們所希望得到的電壓。但是這樣在電源系統(tǒng)內(nèi)部引入了一個(gè)電感和一個(gè)電容,有可能會(huì)導(dǎo)致系統(tǒng)不穩(wěn)定。關(guān)于系統(tǒng)穩(wěn)定,很多資料有介紹,這里不詳細(xì)寫(xiě)了。3、開(kāi)關(guān)電源輸出之后,接LDO濾波這是減少紋波

2015-12-21 11:23:49

DC/DC是應(yīng)用場(chǎng)景較多的電源方案,資料節(jié)選于網(wǎng)上電源與LDO電源的比較DC/DC電源指直流變換為直流的電源,從定義看,LDO也應(yīng)歸屬于DC/DC電源,但一般只將由開(kāi)關(guān)方式實(shí)現(xiàn)直流變換到直流的電源

2021-10-28 06:43:10

電源方案選擇LDO與DC/DC

2021-03-04 07:24:27

1. 高的噪音和紋波抑制;2. 占用PCB板面積小,如手機(jī)等手持電子產(chǎn)品;3. 電路電源不允許使用電感器,如手機(jī);4. 電源需要具有瞬時(shí)校準(zhǔn)和輸出狀態(tài)自檢功能;5. 要求穩(wěn)壓器低壓降,自身功耗低;6. 要求線路成本低和方案簡(jiǎn)單;此時(shí),選用LDO是最恰當(dāng)?shù)倪x擇,同時(shí)滿足產(chǎn)品設(shè)計(jì)的各種要求。二、再

2021-11-17 07:07:52

電源主要分為哪幾種呢?DC/DC電源輸出與LDO電源輸出有哪些不同呢?

2022-03-10 08:41:06

電源紋波有一個(gè)很正經(jīng)的技術(shù)指標(biāo),叫做電源抑制比(PSRR),用輸入電源變化量與轉(zhuǎn)換器輸出變化量的比值來(lái)表征,通常以分貝為單位,如下圖:它描述的是在很寬的頻域范圍內(nèi)的PSRR(如下文公式)需要滿足對(duì)應(yīng)

2018-09-21 11:55:39

引言便攜產(chǎn)品電源設(shè)計(jì)需要系統(tǒng)級(jí)思維,在開(kāi)發(fā)由電池供電的設(shè)備時(shí),諸如手機(jī)、MP3、PDA、PMP、DSC等低功耗產(chǎn)品,如果電源系統(tǒng)設(shè)計(jì)不合理,將影響到整個(gè)系統(tǒng)的架構(gòu)、產(chǎn)品的特性組合、元件的選擇、軟件

2019-07-05 06:22:55

Hi,用到TI的電源芯片TPS54329,原理圖設(shè)計(jì)、環(huán)路測(cè)試結(jié)果如附件。 在測(cè)試環(huán)路穩(wěn)定性時(shí),將C20分別焊上22pF和68pF。測(cè)得結(jié)果22pF相位裕量不足,68pF相位裕量較好。但是參考其

2019-07-25 14:08:42

描述此參考設(shè)計(jì)可輕松實(shí)現(xiàn)支持電壓裕量調(diào)節(jié)功能的 USB Type-C? 電源的系統(tǒng)集成。TPS62136 降壓轉(zhuǎn)換器可高效地將電源從常用 9V、12V 或 15V 適配器轉(zhuǎn)換為 USB Type-C

2018-10-26 10:38:28

是十分強(qiáng)大了,還不趕快學(xué)習(xí)起來(lái)?3、看完這篇文章,別再說(shuō)你不懂LDO了!作者:dsgfa閱讀量:3681推薦理由:文章詳細(xì)解析了LDO工作原理、特性、及參考設(shè)計(jì),讓讀者能輕松了解LDO4、怎么抑制電源

2022-01-12 16:40:20

。對(duì)于8Gbps及以上的高速應(yīng)用更應(yīng)該注意避免此類(lèi)問(wèn)題,為高速數(shù)字傳輸鏈路提供更多裕量。本文針對(duì)PCB設(shè)計(jì)中由小間距QFN封裝引入串?dāng)_的抑制方法進(jìn)行了仿真分析,為此類(lèi)設(shè)計(jì)提供參考。那么,什么是小間距QFN封裝PCB設(shè)計(jì)串?dāng)_抑制呢?

2019-07-30 08:03:48

低壓差穩(wěn)壓器(LDO)看似簡(jiǎn)單,但可提供重要功能,例如將負(fù)載與不干凈的電源隔離開(kāi)來(lái)或者構(gòu)建低噪聲電源來(lái)為敏感電路供電。本簡(jiǎn)短教程介紹了一些常用的LDO 相關(guān)術(shù)語(yǔ),以及一些基本概念,如壓差、裕量電壓

2021-11-12 06:07:44

我們將重點(diǎn)談?wù)劦蛪航捣€(wěn)壓器(LDO)參數(shù)和電源抑制比(PSRR)特性,以及它如何受到應(yīng)用的條件影響。

2021-03-17 07:55:31

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運(yùn)放性能的重要指標(biāo),關(guān)于他們的具體仿真

2021-12-27 07:24:51

NCP4688 150 mA,低噪聲,LDO線性穩(wěn)壓器的典型應(yīng)用。 NCP4688是一款CMOS 150 mA LDO線性穩(wěn)壓器,具有高輸出電壓精度,具有低噪聲輸出電壓和高紋波抑制性能。低電平輸出噪聲10 Vrms通常保持在任何輸出電壓

2020-07-25 11:12:30

可設(shè)計(jì)成對(duì)地電阻明顯大于對(duì)VDD的電阻,以使得調(diào)整管的柵極能夠跟隨電源的變化,從而得到更好的電源抑制性。為了產(chǎn)生一個(gè)較小的對(duì)VDD的電阻,可用R和M串聯(lián)接在柵極與VDD之間。如果LDO的負(fù)載電流很小

2018-09-25 14:33:35

`隨著我國(guó)電子工業(yè)的不斷發(fā)展,開(kāi)關(guān)電源市場(chǎng)需求量越來(lái)越大。開(kāi)關(guān)電源相對(duì)于LDO,有效率高、功率密度高等優(yōu)勢(shì)。測(cè)試開(kāi)關(guān)電源的輸出噪聲偏大,應(yīng)該如何抑制噪聲呢。噪音主要有以下來(lái)源于:一、變壓器產(chǎn)生的音頻

2017-07-04 09:59:30

如何使用EN引腳的LDO來(lái)設(shè)計(jì)可靠電源

2021-03-11 07:47:54

低壓差穩(wěn)壓器(LDO)看似簡(jiǎn)單,但可提供重要功能,例如將負(fù)載與不干凈的電源隔離開(kāi)來(lái)或者構(gòu)建低噪聲電源來(lái)為敏感電路供電。本簡(jiǎn)短教程介紹了一些常用的LDO相關(guān)術(shù)語(yǔ),以及一些基本概念,如壓差、裕量電壓

2019-01-12 14:36:47

低壓差穩(wěn)壓器(LDO)看似簡(jiǎn)單,但可提供重要功能,例如將負(fù)載與不干凈的電源隔離開(kāi)來(lái)或者構(gòu)建低噪聲電源來(lái)為敏感電路供電。本簡(jiǎn)短教程介紹了一些常用的LDO 相關(guān)術(shù)語(yǔ),以及一些基本概念,如壓差、裕量電壓

2021-11-15 07:38:55

開(kāi)關(guān)電源EMI整改中,關(guān)于不同頻段干擾原因及抑制辦法:一、1MHZ以內(nèi)----以差模干擾為主(整改建議)增大X電容量;添加差模電感;小功率電源可采用PI型濾波器處理(建議靠近變壓器的電解電容可選

2021-10-28 07:14:23

作者:黃剛上期文章講完了開(kāi)關(guān)電源和LDO電源效率的比較,顯然是開(kāi)關(guān)電源占了上風(fēng),它普遍維持在85%以上的效率而且加上之前說(shuō)的輸出電壓可升可降的屬性,看上去LDO電源已經(jīng)不是它的對(duì)手。但是實(shí)際上

2019-07-17 06:10:15

電源紋波有一個(gè)很正經(jīng)的技術(shù)指標(biāo),叫做電源抑制比(PSRR),用輸入電源變化量與轉(zhuǎn)換器輸出變化量的比值來(lái)表征,通常

2021-10-29 06:02:50

能力的LDO的電源抑制比在100KHz以上都不太好開(kāi)關(guān)電源如果選用類(lèi)似LM2596這樣的芯片,看到紋波輸出大概在150KHz以上,求大神指點(diǎn)迷津,開(kāi)關(guān)電源的紋波和噪聲可以抑制到什么程度呢?可不可以不用開(kāi)關(guān)電源,直接用LDO來(lái)抑制適配器的噪聲呢?開(kāi)關(guān)電源芯片有沒(méi)有開(kāi)關(guān)頻率比較低的呢?

2014-04-22 22:30:52

之后(Pb),這樣輸出電壓就是我們所希望得到的電壓。但是這樣在電源系統(tǒng)內(nèi)部引入了一個(gè)電感和一個(gè)電容,有可能會(huì)導(dǎo)致系統(tǒng)不穩(wěn)定。關(guān)于系統(tǒng)穩(wěn)定,很多資料有介紹,這里不詳細(xì)寫(xiě)了。3,開(kāi)關(guān)電源輸出之后,接LDO

2019-04-15 08:30:00

測(cè)量上述兩種紋波(噪聲)的軟件,可以看一下參考資料5。同樣,關(guān)于示波器的接地,電源測(cè)試的相關(guān)知識(shí),也可以看一下。 開(kāi)關(guān)電源紋波的抑制 對(duì)于開(kāi)關(guān)紋波,理論上和實(shí)際上都是一定存在的。通常抑制或減少它

2012-11-04 20:49:36

開(kāi)關(guān)電源設(shè)計(jì)中,相位裕度和瞬時(shí)響應(yīng)的關(guān)系如何?是不是相位裕度越大,瞬時(shí)響應(yīng)也就越快,越好?有什么理論依據(jù)嗎?請(qǐng)專(zhuān)家們?cè)敿?xì)指導(dǎo)下,謝謝!!

2024-01-08 07:37:31

什么是紋波抑制比PSRR?如何確定應(yīng)用的紋波抑制比PSRR呢?怎樣去測(cè)量LDO芯片的紋波抑制比PSRR呢?

2021-11-03 06:48:15

精通LDO的PSRR,所有關(guān)于LDO的psrr的文章都在此了什么PDK會(huì)這么大?不可思議

2021-06-22 06:32:31

的 LDO 1117 電源抑制比與頻率關(guān)系,可見(jiàn) 1117 在 1KHz 處電源抑制比最強(qiáng),達(dá)到 84dB,頻率為 100KHz 的電源抑制比僅為 40dB,高于 100KHz 的電源抑制比性能沒(méi)有提供

2020-11-24 09:20:54

能抑制電源波形影響的放大器

2019-11-07 05:11:43

何謂LDO?何謂LDO?LDO是Low Dropout的縮寫(xiě),是即使較低的輸入輸出間電位差也可進(jìn)行工作的線性穩(wěn)壓器。有時(shí)也稱(chēng)為低損耗型線性穩(wěn)壓器或低飽和型線性穩(wěn)壓器。關(guān)于LDO的輸入輸出間電位差并無(wú)

2019-05-29 21:43:34

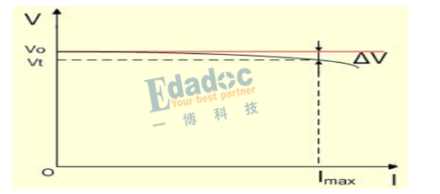

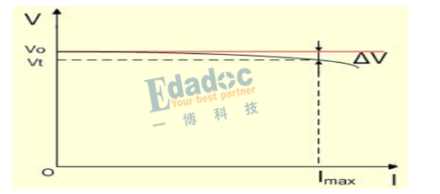

Vo 到Vmax, 輸出電壓最大值和最小值之差g.電源抑制比(Power Supply Rejection Ratio. PSRR)LDO 的輸入源往往許多干擾信號(hào)存在。PSRR 反映了LDO 對(duì)于這些

2019-09-17 09:05:03

][/img]圖13. ADM7172 電源抑制與裕量的關(guān)系(VOUT = 5 V,2 A 負(fù)載電流)比較LDO PSRR 規(guī)格比較LDO 的PSRR 規(guī)格時(shí),應(yīng)確保測(cè)量是在相同的測(cè)試條件下進(jìn)行

2019-10-18 08:30:00

時(shí)輸入電流。好的LDO和差的LDO相比較,是在電源紋波抑制比PSRR差不多的時(shí)候,靜態(tài)耗流會(huì)更低。關(guān)閉功耗:英文Shut down Current,使能腳拉低,VOUT=0V時(shí),VIN上消耗的電流即為

2021-01-22 07:00:00

` 1. 簡(jiǎn)化開(kāi)關(guān)電源設(shè)計(jì) 開(kāi)關(guān)電源多路輸出一般通過(guò)增加高頻變壓器反饋端來(lái)實(shí)現(xiàn),這使得開(kāi)關(guān)電源在設(shè)計(jì)過(guò)程中增加了設(shè)計(jì)者的工作量。應(yīng)用LDO作為開(kāi)關(guān)電源的輸出終端,可以極大地簡(jiǎn)化開(kāi)關(guān)電源

2019-03-07 11:25:13

=Vin-Vout,這個(gè)差值不能太大,要不然穩(wěn)壓精度會(huì)受到影響,可以看出LDO只能降壓而不能升壓; 3、噪聲 噪聲其實(shí)是一個(gè)統(tǒng)稱(chēng),是衡量一款電源產(chǎn)品優(yōu)秀的重要參考因素,它里面包含耦合、諧振等; 4、紋波抑制比 電源變化量與輸出變化量的比值,是輸出信號(hào)受電源影響比值,反映LDO抑制信號(hào)源的能力。

2020-06-28 14:53:05

問(wèn)題:采用單電源供電時(shí),我的運(yùn)算放大器輸出會(huì)高度失真。這可能是因?yàn)槟撤N裕量問(wèn)題嗎?答案:裕量(headroom)肯定是輸出失真的眾多原因之一。有些人可能還不熟悉裕量的概念,它用于衡量放大器的輸入

2018-10-31 10:23:35

具有高電源抑制比性能的線性穩(wěn)壓器

低壓降穩(wěn)壓器(LDO)主要用于產(chǎn)生供音頻和射頻電路使用的低紋波、低噪聲電源,也可以作為頻率合成器和VCO的局部純凈電源。一般

2010-01-14 16:54:00 621

621

電源抑制比(PSRR),電源抑制比(PSRR)是什么意思

電源抑制比

電源抑制比(Power Supply Rejection Ratio):把電源的輸入與輸出看作獨(dú)

2010-03-09 16:41:06 15708

15708 RF電路中LDO電源抑制比和噪聲原理及選擇

本文討論LDO的特點(diǎn)以及RF電路對(duì)LDO的電源抑制比和噪聲的選擇。引言便攜產(chǎn)品電源設(shè)計(jì)需

2010-03-09 16:51:32 2157

2157

LDO是一種微功耗的低壓差線性穩(wěn)壓器,它具有極低的自有噪聲和較高的電源抑制比(

2010-11-11 17:35:42 1917

1917

關(guān)于反激式電源中電磁干擾及其抑制的分析。

2011-10-21 18:17:54 136

136 LDO即low dropout regulator,是一種低壓差線性穩(wěn)壓器。這是相對(duì)于傳統(tǒng)的線性穩(wěn)壓器來(lái)說(shuō)的。傳統(tǒng)的線性穩(wěn)壓器,如78XX系列的芯片都要求輸入電壓要比輸出電壓至少高出2V~3V,否則

2017-05-15 15:46:52 29

29 模塊對(duì)外部電源進(jìn)行處理,得到模塊所需性能標(biāo)準(zhǔn)的電壓。 設(shè)計(jì)了一種可用于射頻前端芯片供電的高電源抑制比(PSR)無(wú)片外電容CMOS低壓差線性穩(wěn)壓器(LDO)。基于對(duì)全頻段電源抑制比的詳細(xì)分析,提出了一種PSR增強(qiáng)電路模塊,使100

2018-02-23 11:41:48 0

0 關(guān)于開(kāi)關(guān)電源認(rèn)證中遇到的這些電磁兼容問(wèn)題,都是近年開(kāi)關(guān)電源業(yè)界討論的熱點(diǎn),其中開(kāi)關(guān)電源的諧波抑制的話題,在每年都有大量的文章見(jiàn)諸于技術(shù)雜志和書(shū)刊。

2018-09-18 17:34:04 10067

10067

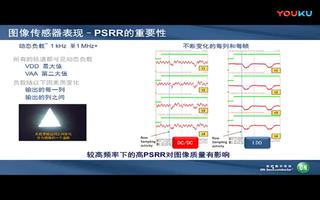

視頻簡(jiǎn)介:圖像傳感器的圖像質(zhì)量直接受到高頻、高PSRR LDO穩(wěn)壓器的影響。本網(wǎng)上廣播講解電源抑制比(PSRR)的基本知識(shí),以及在您的圖像傳感器設(shè)計(jì)中如何最大程度地降低噪聲。

2019-03-14 06:10:00 5086

5086

紋波小是我們通常的說(shuō)法,其實(shí)衡量電源,尤其是LDO電源紋波有一個(gè)很正經(jīng)的技術(shù)指標(biāo),叫做電源抑制比(PSRR)。

2019-08-27 11:41:06 19002

19002

LT3094演示電路-超低噪聲、超高電源抑制比負(fù)LDO穩(wěn)壓器(-20V至-3.3V@500 mA)

2021-03-23 14:27:09 14

14 原文來(lái)自公眾號(hào):硬件工程師看海 公眾號(hào)后臺(tái)回復(fù):LDO仿真文件 1. 前言 目前市場(chǎng)上無(wú)論什么電子產(chǎn)品,只要涉及到電就必須用到電源,電源的分類(lèi)有很多種,比如開(kāi)關(guān)電源、逆變電源、交流電源等等。在移動(dòng)

2021-04-30 09:38:00 8922

8922

ADM7172:6.5 V,2 A,超低噪聲,高電源抑制比,快速瞬態(tài)響應(yīng)CMOS LDO數(shù)據(jù)表

2021-05-14 17:01:48 6

6 ADM7170:6.5 V,500 mA,超低噪聲,高電源抑制比,快速瞬態(tài)響應(yīng)CMOS LDO數(shù)據(jù)表

2021-05-21 19:19:34 7

7 ADM7171:6.5 V,1 A,超低噪聲,高電源抑制比,快速瞬態(tài)響應(yīng)CMOS LDO數(shù)據(jù)表

2021-05-21 19:33:05 12

12 1. 簡(jiǎn)化開(kāi)關(guān)電源設(shè)計(jì) 開(kāi)關(guān)電源多路輸出一般通過(guò)增加高頻變壓器反饋端來(lái)實(shí)現(xiàn),這使得開(kāi)關(guān)電源在設(shè)計(jì)過(guò)程中增加了設(shè)計(jì)者的工作量。應(yīng)用LDO作為開(kāi)關(guān)電源的輸出終端,可以極大地簡(jiǎn)化開(kāi)關(guān)電源

2021-10-21 21:06:06 16

16 上期文章講完了開(kāi)關(guān)電源和LDO電源效率的比較,顯然是開(kāi)關(guān)電源占了上風(fēng),它普遍維持在85%以上的效率而且加上之前說(shuō)的輸出電壓可升可降的屬性,看上去LDO電源已經(jīng)不是它的對(duì)手。但是實(shí)際上并非如此,至少

2021-10-22 13:06:01 8

8 ? ? ? ? 我們常用的電源類(lèi)型有LDO和DCDC兩種。DCDC包含buck,boost,buckboost,隔離,非隔離等拓?fù)洌偌由螾WM,PFM,同步整流,軟開(kāi)關(guān),磁芯復(fù)位等多種關(guān)鍵技術(shù)

2021-10-22 17:06:13 23

23 電源(LDO)的管子是工作在放大區(qū)的,處于放大狀態(tài)。線性電源LDO只能降壓,不能升壓。開(kāi)關(guān)電源(DC-DC)的管子是工作在飽和區(qū)、截止區(qū)的,處于開(kāi)關(guān)狀態(tài)。開(kāi)關(guān)電源(DC-DC)既可以升壓也可以降...

2021-11-07 19:06:03 27

27 LDO線性電源

2021-11-07 20:21:00 17

17 1. 高的噪音和紋波抑制;2. 占用PCB板面積小,如手機(jī)等手持電子產(chǎn)品;3. 電路電源不允許使用電感器,如手機(jī);4. 電源需要具有瞬時(shí)校準(zhǔn)和輸出狀態(tài)自檢功能;5. 要求穩(wěn)壓器低壓降,自身功耗低;6. 要求線路成本低和方案簡(jiǎn)單;此時(shí),選用LDO是最恰當(dāng)?shù)倪x擇,同時(shí)滿足產(chǎn)品設(shè)計(jì)的各種要求。二、再

2021-11-09 21:05:59 18

18 共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運(yùn)放性能的重要指標(biāo),關(guān)于他們的具體仿真

2022-01-05 14:22:58 5

5 理解LDO的電源組成及概念 學(xué)會(huì)分析LDO的電路的主干道及布局要點(diǎn) 熟悉LDO主干道布線要點(diǎn)。

2022-04-06 14:50:10 26

26 LDO基礎(chǔ)知識(shí):電源抑制比

2022-11-01 08:26:41 2

2 在便攜式通信中,低壓差線性穩(wěn)壓器(LDO)為RF電路產(chǎn)生電源電壓;為頻率合成器和壓控振蕩器(VCO)供電時(shí),這些電壓必須特別干凈。為穩(wěn)壓器供電的電源通常包括疊加在直流上的寬帶交流紋波。預(yù)計(jì)LDO會(huì)抑制這些偽影。本文介紹了三種提高LDO電源抑制比(PSRR)的方法。

2023-03-13 09:32:37 980

980

低壓差線性穩(wěn)壓器(LDO)最大的優(yōu)點(diǎn)之一是它們能夠衰減開(kāi)關(guān)模式電源產(chǎn)生的電壓紋波。這對(duì)鎖相環(huán)(PLL)和時(shí)鐘等信號(hào)調(diào)節(jié)器件在內(nèi)的數(shù)據(jù)轉(zhuǎn)換器尤為重要,因?yàn)樵肼?b class="flag-6" style="color: red">電源電壓會(huì)影響性能。電源抑制比(PSRR)仍然通常被誤認(rèn)為單一的靜態(tài)值。在這篇文章中,我將嘗試說(shuō)明什么是PSRR以及影響它的變量有哪些。

2023-04-04 10:25:33 1247

1247

電源抑制比又叫做電源紋波抑制比(power supply rejection ratio)簡(jiǎn)稱(chēng)PSRR。不少電源芯片手冊(cè)中有此參數(shù),比如LDO芯片,很多人在閱讀LDO手冊(cè)的時(shí)候忽略了此參數(shù),其實(shí)這個(gè)

2023-04-24 12:57:43 3653

3653

在便攜式通信中,低壓差線性穩(wěn)壓器(LDO)為RF電路產(chǎn)生電源電壓;為頻率合成器和壓控振蕩器(VCO)供電時(shí),這些電壓必須特別干凈。為穩(wěn)壓器供電的電源通常包括疊加在直流上的寬帶交流紋波。預(yù)計(jì)LDO會(huì)抑制這些偽影。本文介紹了三種提高LDO電源抑制比(PSRR)的方法。

2023-06-10 11:38:35 1319

1319

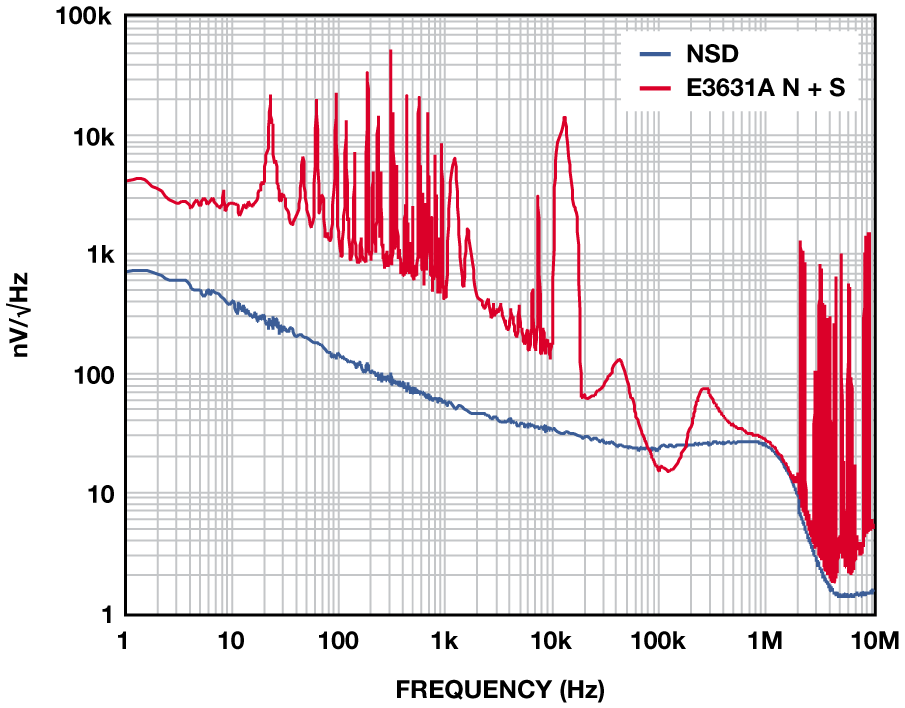

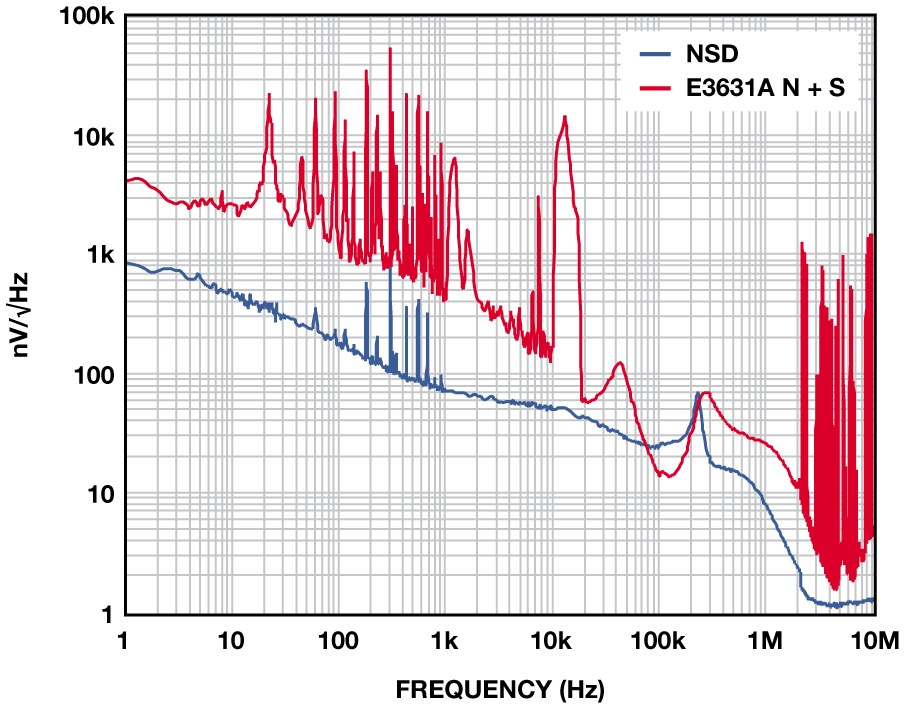

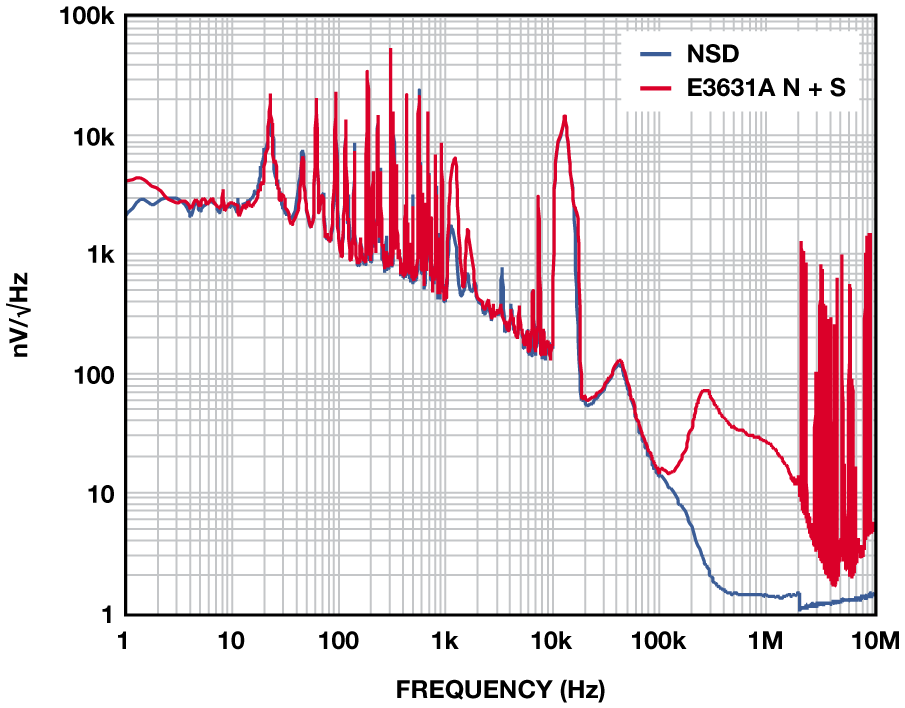

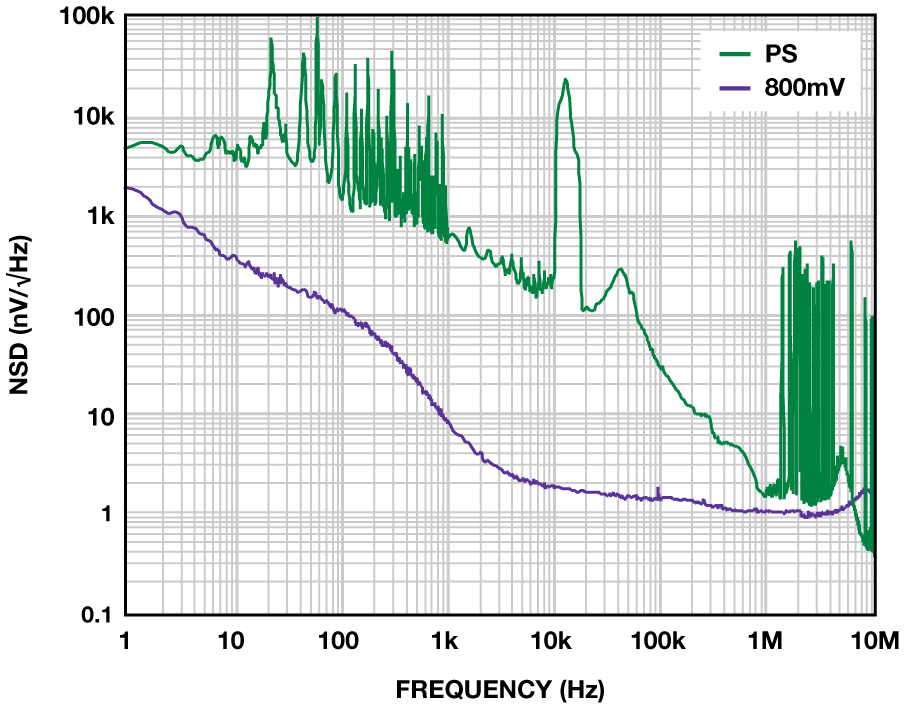

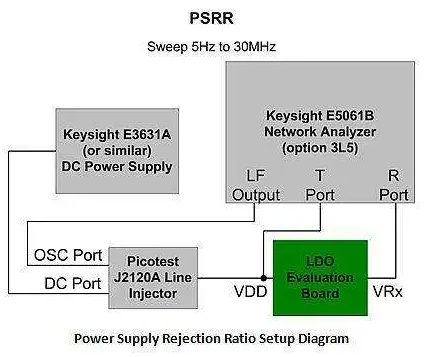

為了在LDO上執(zhí)行PSRR測(cè)量,需要兩臺(tái)設(shè)備。第一種是直流電源,用于為 LDO 輸入電壓供電。再次使用是德科技 (安捷倫) E3631A 直流電源。第二款也是最重要的設(shè)備是德科技 E5061B

2023-06-30 14:54:48 1004

1004

LDO的電源抑制比基本概念與應(yīng)用

2023-07-24 16:15:14 1271

1271

電源抑制比是什么意思?電源抑制比怎么提高? 一、電源抑制比的概念 電源抑制比(PSRR)又稱(chēng)電源噪聲抑制比,是指在電路中,當(dāng)電源發(fā)生噪聲時(shí),電路輸出端對(duì)電源噪聲的抑制程度,一般使用分貝(dB)單位

2023-09-02 17:50:32 3364

3364 什么是共模抑制比CMRR?什么是電源抑制比PSRR? 共模抑制比(common mode rejection ratio,CMRR)和電源抑制比(power supply rejection

2023-10-29 11:45:48 2995

2995 低壓降穩(wěn)壓器(LDO)最受歡迎的優(yōu)勢(shì)之-是,能夠衰減開(kāi)關(guān)模式電源生成的電壓紋波。這對(duì)于數(shù)據(jù)轉(zhuǎn)換器、鎖相環(huán)(PLL)和時(shí)鐘等信號(hào)調(diào)節(jié)器件而言尤為重要,因?yàn)楹性肼暤?b class="flag-6" style="color: red">電源電壓會(huì)影響這類(lèi)器件的性能。

2023-11-09 12:23:15 132

132 電源抑制比怎么提高? 電源抑制比是衡量電源噪聲抑制效果的重要指標(biāo)。提高電源抑制比可以有效降低電源噪聲對(duì)電子設(shè)備的影響,提升設(shè)備的穩(wěn)定性和性能。本文將從信號(hào)處理、濾波器設(shè)計(jì)、抑制電路、電源線布局等多個(gè)

2023-12-12 14:33:28 369

369

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論