Verilog HDL 數(shù)字系統(tǒng)設(shè)計(jì)

2012-08-17 21:10:51

Verilog HDL 高級(jí)數(shù)字設(shè)計(jì)源碼

2018-02-02 09:44:52

本帖最后由 lee_st 于 2017-11-30 12:35 編輯

講授內(nèi)容EDA設(shè)計(jì)方法學(xué);Verilog HDL語言;數(shù)字電路與系統(tǒng)設(shè)計(jì);高級(jí)描述語言及工具使用;

2017-11-30 12:33:55

講授內(nèi)容EDA設(shè)計(jì)方法學(xué);Verilog HDL語言;數(shù)字電路與系統(tǒng)設(shè)計(jì);高級(jí)描述語言及工具使用;

2017-11-30 12:36:07

講授內(nèi)容EDA設(shè)計(jì)方法學(xué);Verilog HDL語言;數(shù)字電路與系統(tǒng)設(shè)計(jì);高級(jí)描述語言及工具使用;

2017-11-30 12:38:44

本帖最后由 lee_st 于 2017-11-30 12:42 編輯

講授內(nèi)容EDA設(shè)計(jì)方法學(xué);Verilog HDL語言;數(shù)字電路與系統(tǒng)設(shè)計(jì);高級(jí)描述語言及工具使用;

2017-11-30 12:41:35

講授內(nèi)容EDA設(shè)計(jì)方法學(xué);Verilog HDL語言;數(shù)字電路與系統(tǒng)設(shè)計(jì);高級(jí)描述語言及工具使用;

2017-11-30 12:44:09

講授內(nèi)容EDA設(shè)計(jì)方法學(xué);Verilog HDL語言;數(shù)字電路與系統(tǒng)設(shè)計(jì);高級(jí)描述語言及工具使用;

2017-11-30 12:46:17

講授內(nèi)容EDA設(shè)計(jì)方法學(xué);Verilog HDL語言;數(shù)字電路與系統(tǒng)設(shè)計(jì);高級(jí)描述語言及工具使用;

2017-11-30 12:48:48

Verilog數(shù)字VLSI設(shè)計(jì)教程

2017-09-26 14:11:58

Verilog數(shù)字系統(tǒng)設(shè)計(jì)六時(shí)序邏輯實(shí)驗(yàn)2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計(jì)六前言一、可控的移位寄存器是什么?二、編程1.要求:2.設(shè)計(jì)思路:3.實(shí)現(xiàn)代碼:4.仿真測(cè)試:總結(jié)前言隨著人工智能

2022-01-25 08:30:30

Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程

2018-07-16 12:29:20

《Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程》本書講述利用硬件描述語言(Verilog HDL)設(shè)計(jì)復(fù)雜數(shù)字系統(tǒng)的方法。這種方法源自 20 世紀(jì)90年代的美國,取得成效后迅速在其他先進(jìn)工業(yè)國得到推廣和普及。利用

2022-03-21 13:46:22

Verilog數(shù)字系統(tǒng)設(shè)計(jì)十二復(fù)雜數(shù)字電路設(shè)計(jì)2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計(jì)十二前言一、什么是FIFO控制器?二、編程1.要求:2.設(shè)計(jì)思路:3.FIFO控制器實(shí)現(xiàn):總結(jié)前言隨著人工智能

2022-02-09 07:23:50

、韓國、美國等區(qū)域應(yīng)用很普遍。本文簡(jiǎn)要地介紹國內(nèi)數(shù)字電路設(shè)計(jì)普遍使用的Verilog語言。verilog是什么。Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言

2021-07-26 06:39:56

在學(xué)習(xí)了數(shù)字信號(hào)處理之后,在底部使用verilog實(shí)現(xiàn)了FFT的應(yīng)用

2023-09-28 06:49:55

數(shù)字電路設(shè)計(jì)與Verilog HDL

2015-07-16 16:21:19

很好的verilog學(xué)習(xí)資料,并結(jié)合數(shù)字電路講述。

2013-05-07 22:00:52

數(shù)字系統(tǒng)設(shè)計(jì):Verilog HDL實(shí)現(xiàn)

2015-07-16 16:19:59

DCT實(shí)現(xiàn)Verilog HDL的數(shù)字圖像處理源代碼

2012-08-11 09:30:53

博主最近剛開始學(xué)習(xí)FPGA設(shè)計(jì),選用的開發(fā)語言是目前比較流行的Verilog,教材選用的是北京航空航天大學(xué)出版的《夏宇聞Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)教程》(第四版),這本書也是比較經(jīng)典的一本

2022-03-22 10:26:00

數(shù)碼管前三位顯示一個(gè)000-999每隔1%s走一次的跑表,鍵盤按下跑表停止,松開跑表繼續(xù)走。我的代碼如下:編譯的時(shí)候總是顯示switch循環(huán)第一個(gè)case那里語句無效,而且等號(hào)附近出現(xiàn)語法錯(cuò)誤,但是

2017-08-26 16:08:43

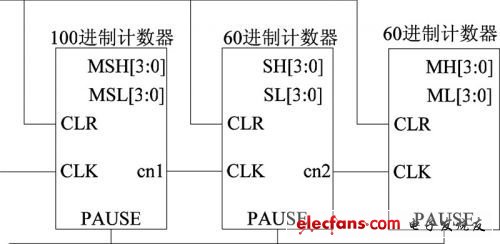

數(shù)字跑表1.實(shí)驗(yàn)要求:l設(shè)計(jì)一個(gè)數(shù)字跑表,該跑表具有復(fù)位、暫停、秒表計(jì)時(shí)等功能。l跑表設(shè)三個(gè)輸入端,分別為時(shí)鐘輸入(CLK)、復(fù)位(CLR)和啟動(dòng)/暫停(PAUSE)按鍵。復(fù)位信號(hào)高電平有效,可對(duì)

2012-06-03 15:10:28

基于51單片機(jī)的時(shí)鐘-跑表設(shè)計(jì)方案(程序+仿真)

2018-11-29 12:07:49

次按鍵調(diào)整不出現(xiàn)數(shù)字跳變情形(防抖)。 后臺(tái)走時(shí):切換至其他功能,仍能后臺(tái)正確走時(shí)。2、 跑表顯示格式為000.0,計(jì)時(shí)單位為0.1秒,范圍為0.1秒~999.9秒后臺(tái)計(jì)時(shí):計(jì)時(shí)中的跑表,切換至其他

2017-07-05 22:00:16

什么是數(shù)字系統(tǒng)?verilog hdl又是什么?基于verilog hdl的數(shù)字系統(tǒng)應(yīng)用該如何去設(shè)計(jì)?

2021-06-21 06:54:02

基于verilog的數(shù)字時(shí)鐘程序,時(shí)鐘芯片基礎(chǔ)——60進(jìn)制計(jì)數(shù)器設(shè)計(jì)目的讓nexys 4板上的7段碼LED顯示時(shí)鐘信息,其中包括時(shí)鐘的小時(shí),分鐘,秒鐘部分,且能夠?qū)崿F(xiàn)時(shí)鐘的停止計(jì)時(shí)信號(hào),手動(dòng)調(diào)整小時(shí)

2021-07-22 07:37:01

夏宇聞 Verilog 數(shù)字系統(tǒng)設(shè)計(jì)教程

2012-08-20 16:36:31

如何采用Verilog語言創(chuàng)建1-Wire主機(jī)?

2021-04-29 06:42:19

本文介紹了一種基于SoPC的數(shù)字示波器設(shè)計(jì),在設(shè)計(jì)過程中采用了FPGA芯片、嵌入式NiosⅡ處理器以及Verilog HDL語言,簡(jiǎn)化了電路的設(shè)計(jì),提高了靈活性,縮短了設(shè)計(jì)周期。

2021-05-11 06:07:16

/*-----------------------------------------------名稱:電子跑表系統(tǒng)編寫:E2.0日期:19/6/11內(nèi)容:基于單片機(jī)試驗(yàn)板設(shè)計(jì)一個(gè)電子跑表系統(tǒng),用

2022-01-12 06:05:17

本節(jié)通過Verilog HDL語言編寫一個(gè)具有“百分秒、秒、分”計(jì)時(shí)功能的數(shù)字跑表,可以實(shí)現(xiàn)一個(gè)小時(shí)以內(nèi)精確至百分之一秒的計(jì)時(shí)。

2019-09-29 09:18:55

隨著數(shù)字技術(shù)的高速發(fā)展,人們已經(jīng)不再采用各種功能固定的通用中、小規(guī)模集成電路和電路圖輸入方法設(shè)計(jì)數(shù)字系統(tǒng),而是廣泛地采用硬件描述語言對(duì)數(shù)字電路的行為進(jìn)行建模,并使用電子設(shè)計(jì)自動(dòng)化

2022-04-19 14:40:04

題目是這樣的。數(shù)碼管前三位顯示一個(gè)跑表,從000到999之間以1%秒速度運(yùn)行,當(dāng)按下個(gè)獨(dú)立鍵盤時(shí)跑表停止,按下第二個(gè)時(shí)計(jì)時(shí)開始,按下第三個(gè)時(shí)計(jì)數(shù)值清零從頭開始。本人編寫的程序如下

2013-08-08 00:07:23

求助……要求:利用89C51的計(jì)數(shù)器實(shí)現(xiàn)數(shù)字跑表功能,通過6個(gè)LED數(shù)碼管顯示計(jì)時(shí)的時(shí)間,最大計(jì)時(shí)時(shí)間為59’59”99,計(jì)時(shí)分辨率0.01秒。控制功能:利用開關(guān)S27控制數(shù)字跑表的工作方式(S27

2017-07-02 19:01:07

1.eda 用Verilog設(shè)計(jì)數(shù)字溫度計(jì)2.子模塊設(shè)計(jì)3.整機(jī)系統(tǒng)設(shè)計(jì)4.仿真驗(yàn)證5.在實(shí)驗(yàn)裝置上進(jìn)行硬件測(cè)試6.設(shè)計(jì)報(bào)告

2022-06-17 13:52:10

stc89c52電子跑表題目九:電子跑表的設(shè)計(jì)功能:1、做時(shí)鐘時(shí)在6位LED 顯示器上顯示分、秒;2、做跑表時(shí)顯示范圍10000.0秒~10999.9秒;3、當(dāng)按下啟動(dòng)按鈕跑表開始計(jì)時(shí),按下停止按鈕停止計(jì)時(shí),當(dāng)按下復(fù)位按鈕跑表回零。按鍵控制秒表部分寫不出,跪求程序,謝謝啦!

2016-12-23 10:36:52

FPGA秒表——跑表verilog

2013-06-11 14:10:12

跪求用51單片機(jī)帶DS1302 DS18B20 LCD1602帶跑表功能的數(shù)字鐘(帶圖和程序),本人十分感激!有的話麻煩發(fā)到我郵箱1311566283@qq.com,再次感謝!

2012-05-09 12:12:47

This book is on the IEEE Standard Hardware Description Languagebased on the Verilog® Hardware

2009-07-23 09:01:32 0

0 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 復(fù)雜數(shù)字邏輯系統(tǒng)的Verilog

2010-11-01 17:03:59 0

0

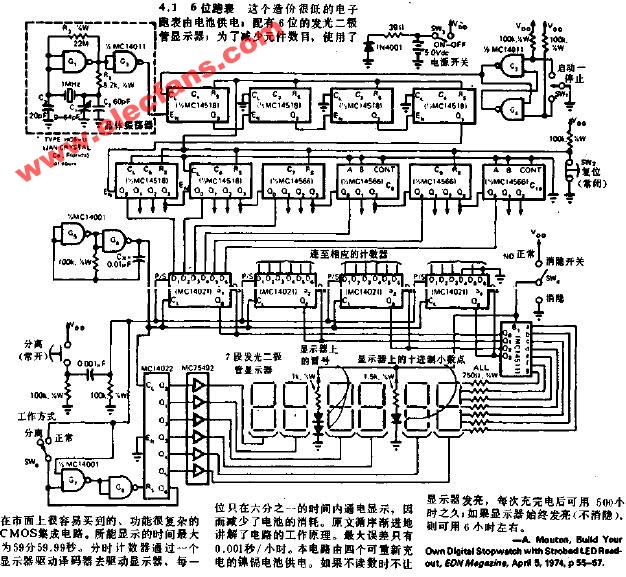

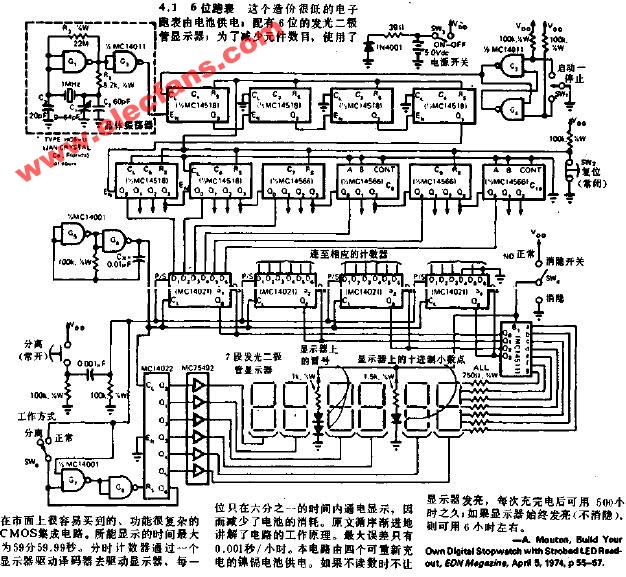

6位跑表電路圖

2009-01-13 19:48:56 1243

1243

什么是Verilog HDL?

Verilog HDL是一種硬件描述語言,用于從算法級(jí)、門級(jí)到開關(guān)級(jí)的多種抽象設(shè)計(jì)層次的數(shù)字系統(tǒng)建模。被建模的數(shù)字系統(tǒng)

2009-01-18 14:53:26 3677

3677

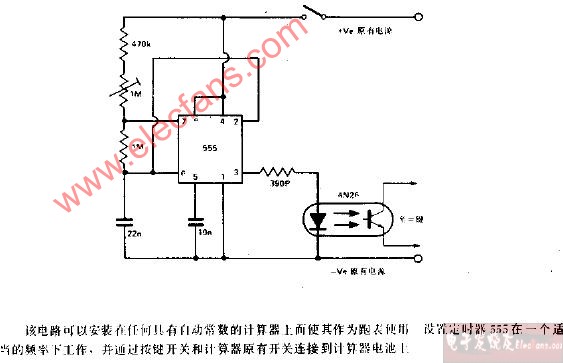

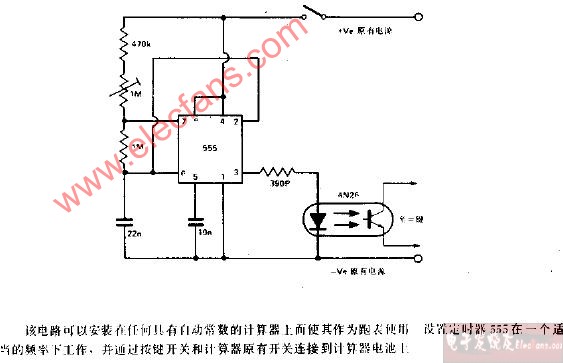

計(jì)算器跑表變換器電路圖

2009-03-25 09:02:46 935

935

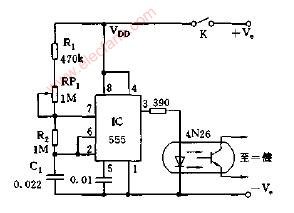

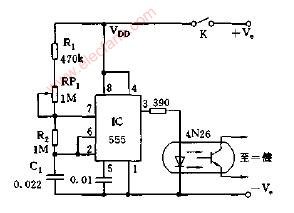

積算器跑表變換器電路圖1

2009-05-23 13:57:01 523

523

Verilog HDL程序基本結(jié)構(gòu)與程序入門

Verilog HDL程序基本結(jié)構(gòu)

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的

2010-02-08 11:43:30 2185

2185 數(shù)字跑表原理

實(shí)例的內(nèi)容及目標(biāo)

1.實(shí)例的主要內(nèi)容本節(jié)通過Verilog HDL語言編寫一個(gè)具有“百分秒、秒、分”計(jì)時(shí)功能的數(shù)字跑表,可以實(shí)現(xiàn)一個(gè)小時(shí)以

2010-02-09 09:15:35 3510

3510 本教程講解了如何利用VERILOG硬件描述語言來設(shè)計(jì)和驗(yàn)證一個(gè)復(fù)雜的數(shù)字系統(tǒng)的方法。下面就復(fù)雜數(shù)字系統(tǒng)的概念、用途和幾個(gè)有關(guān)的基本問題做一些說明

2011-05-09 17:01:37 0

0 本內(nèi)容介紹了應(yīng)用Verilog HDL進(jìn)行數(shù)字系統(tǒng)設(shè)計(jì)實(shí)例

2011-09-27 16:30:29 87

87 電子發(fā)燒友網(wǎng)站提供《Verilog HDL數(shù)字設(shè)計(jì)與綜合(第二版).txt》資料免費(fèi)下載

2012-04-04 15:57:24 0

0 電子發(fā)燒友網(wǎng)站提供《Verilog HDL_數(shù)字設(shè)計(jì)與綜合第二版.txt》資料免費(fèi)下載

2012-08-07 15:17:15 0

0 Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結(jié)

2012-10-08 14:48:31 0

0 電子發(fā)燒友網(wǎng)站提供《Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第二版) 夏宇聞.txt》資料免費(fèi)下載

2012-10-31 15:57:58 0

0 Verilog HDL 數(shù)字設(shè)計(jì)教程【作者:賀敬凱;出版社:西安電子科技大學(xué)出版社】(本資料為ppt) 內(nèi)容簡(jiǎn)介:介紹了Verilog HDL語言,狀態(tài)機(jī)設(shè)計(jì),仿真,還有好幾個(gè)可綜合設(shè)計(jì)的舉例,除了

2012-11-28 13:43:11 489

489 電子發(fā)燒友網(wǎng)站提供《Verilog_HDL數(shù)字設(shè)計(jì)與綜合_夏宇聞譯(第二版).txt》資料免費(fèi)下載

2013-01-23 12:45:01 0

0 電子發(fā)燒友網(wǎng)站提供《夏宇聞譯(第二版)-Verilog HDL數(shù)字設(shè)計(jì)與綜合.txt》資料免費(fèi)下載

2014-09-17 00:08:46 0

0 電子發(fā)燒友網(wǎng)站提供《詳解Verilog HDL數(shù)字設(shè)計(jì)與綜合 夏宇聞譯(第二版).txt》資料免費(fèi)下載

2014-09-25 22:19:09 0

0 電子發(fā)燒友網(wǎng)站提供《數(shù)字邏輯基礎(chǔ)與Verilog設(shè)計(jì)(原書第2版).txt》資料免費(fèi)下載

2014-10-22 15:30:31 0

0 電子發(fā)燒友網(wǎng)站提供《Verilog HDL數(shù)字設(shè)計(jì)與綜合_夏宇聞譯(第二版).txt》資料免費(fèi)下載

2015-09-08 17:43:22 0

0 基于FPGA數(shù)字跑表的設(shè)計(jì) VHDL語言

2015-10-30 10:39:27 25

25 verilog verilog verilog verilog verilog verilog verilog verilog

2015-11-12 14:43:51 0

0 數(shù)字系統(tǒng)設(shè)計(jì):VERILOG實(shí)現(xiàn) (第2版)

2015-11-30 10:21:33 0

0 基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)

2015-12-08 15:57:23 0

0 介紹Verilog HDL數(shù)字設(shè)計(jì)與綜合的課件

2015-12-23 10:58:54 0

0 數(shù)字電路中的FPGA和verilog教程,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 17:44:30 42

42 Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版),分享給在或者需要學(xué)習(xí)verilog的伙伴們。

2016-05-11 16:40:55 0

0 Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版),分享給在或者需要學(xué)習(xí)verilog的伙伴們。

2016-05-11 16:40:55 0

0 Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版),分享給在或者需要學(xué)習(xí)verilog的伙伴們。

2016-05-11 16:40:55 0

0 FPGA學(xué)習(xí)資料教程——華清遠(yuǎn)見FPGA代碼-數(shù)字跑表

2016-10-27 18:07:54 10

10 Verilog HDL數(shù)字設(shè)計(jì)與綜合 夏宇聞譯(第二版),感興趣的小伙伴們可以瞧一瞧。

2016-11-11 11:20:11 0

0 自行設(shè)計(jì)的純基本數(shù)字邏輯跑表

2017-05-17 08:43:19 15

15 EDA技術(shù)及其應(yīng)用——數(shù)字跑表畢業(yè)設(shè)計(jì)論文

2018-01-22 16:18:41 31

31 本文首先介紹了verilog的概念和發(fā)展歷史,其次介紹了verilog的特征與Verilog的邏輯門級(jí)描述,最后介紹了Verilog晶體管級(jí)描述與verilog的用途。

2018-05-14 14:22:44 43434

43434

此文件時(shí)間的Verilog數(shù)字系統(tǒng)設(shè)計(jì)的一些案例和教程,適合初學(xué)者學(xué)習(xí)和參考。

2018-06-25 08:00:00 9

9 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL入門教程之Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)教程。

2018-09-20 15:51:26 80

80 1. 工作原理

1.利用555計(jì)時(shí)器構(gòu)成能產(chǎn)生特定脈沖的多謝振蕩器,產(chǎn)生100Hz的脈沖信號(hào),滿足數(shù)字跑表的脈沖需求;2.用多功能計(jì)數(shù)器產(chǎn)生一百進(jìn)制和六十進(jìn)制,實(shí)現(xiàn)數(shù)字跑表的計(jì)數(shù)功能;3.利用各種門電路的組合,實(shí)現(xiàn)數(shù)字跑表的啟動(dòng)、暫停和清零;4.利用譯碼器和數(shù)碼管實(shí)現(xiàn)譯碼及顯示功能。

2018-11-16 08:00:00 17

17 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述的語言。

2019-03-08 14:29:12 12093

12093 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字式跑表的設(shè)計(jì)資料合集免費(fèi)下載,由8個(gè)74LS162芯片和8個(gè)LED四端顯示數(shù)碼管組成,用555定時(shí)器組成單穩(wěn)態(tài)觸發(fā)器提供100Hz的脈沖。其中四片芯片構(gòu)成兩個(gè)60進(jìn)制

2019-05-23 08:00:00 5

5 從數(shù)字電路中學(xué)到的邏輯電路功能,使用硬件描述語言(Verilog/VHDL)描述出來,這需要設(shè)計(jì)人員能夠用硬件編程思維來編寫代碼,以及擁有扎實(shí)的數(shù)字電路功底。

2019-12-05 07:10:00 2977

2977

數(shù)字系統(tǒng)設(shè)計(jì)與VerilogHDL根據(jù)EDA課程教學(xué)要求,以提高數(shù)字設(shè)計(jì)能力為目的,系統(tǒng)闡述數(shù)字系統(tǒng)開發(fā)的相關(guān)知識(shí),主要內(nèi)容包括EDA技術(shù)、FPGA/CPLD器件、Verilog硬件描述

2019-10-29 08:00:00 102

102 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog教程之Verilog HDL數(shù)字集成電路設(shè)計(jì)方法和基礎(chǔ)知識(shí)課件

2020-12-09 11:24:19 52

52 在現(xiàn)階段,作為設(shè)計(jì)人員熟練掌握 Verilog HDL程序設(shè)計(jì)的多樣性和可綜合性,是至關(guān)重要的。作為數(shù)字集成電路的基礎(chǔ),基本數(shù)字邏輯電路的設(shè)計(jì)是進(jìn)行復(fù)雜電路的前提。本章通過對(duì)數(shù)字電路中基本邏輯電路的erilog HDL程序設(shè)計(jì)進(jìn)行講述,掌握基本邏輯電路的可綜合性設(shè)計(jì),為具有特定功能的復(fù)雜電路的設(shè)計(jì)打下基礎(chǔ)

2020-12-09 11:24:00 33

33 Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版)免費(fèi)下載。

2021-05-12 14:26:37 0

0 Verilog HDL是一種以文本形式描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的硬件描述語言,也可描述邏輯電路圖、邏輯表達(dá)式等。Verilog HDL和VHDL是目前主流的、最受歡迎的兩種硬件描述語言。

2021-07-23 14:36:55 9909

9909 、韓國、美國等區(qū)域應(yīng)用很普遍。本文簡(jiǎn)要地介紹國內(nèi)數(shù)字電路設(shè)計(jì)普遍使用的Verilog語言。verilog是什么。Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言

2021-11-06 09:05:57 15

15 基于金沙灘51單片機(jī)的電子跑表很久之前學(xué)51單片機(jī)的時(shí)候做的了,現(xiàn)在分享一下。基于金沙灘51單片機(jī),很推薦這款單片機(jī)開發(fā)板,教程很好。零、完成功能本項(xiàng)目完成以下功能:時(shí)鐘模式:在數(shù)碼管上顯示

2021-11-23 16:51:38 10

10 Verilog數(shù)字系統(tǒng)設(shè)計(jì)九任務(wù)和函數(shù)實(shí)驗(yàn)1文章目錄Verilog數(shù)字系統(tǒng)設(shè)計(jì)九前言一、任務(wù)和函數(shù)的區(qū)別?二、編程1.要求:2.設(shè)計(jì)思路:3.采用任務(wù)方法實(shí)現(xiàn):4.采用函數(shù)方法實(shí)現(xiàn):總結(jié)前言

2021-12-05 19:06:09 9

9 HDLBits 是一組小型電路設(shè)計(jì)習(xí)題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習(xí)數(shù)字硬件設(shè)計(jì)~

2022-08-31 09:06:59 1168

1168 第一句話是:還沒學(xué)數(shù)電的先學(xué)數(shù)電。然后你可以選擇verilog或者VHDL,有C語言基礎(chǔ)的,建議選擇VHDL。因?yàn)?b class="flag-6" style="color: red">verilog太像C了,很容易混淆,最后你會(huì)發(fā)現(xiàn),你花了大量時(shí)間去區(qū)分這兩種語言

2022-11-03 09:02:56 2626

2626 Verilog HDL數(shù)字集成電路設(shè)計(jì)原理與應(yīng)用(蔡覺平)西安電子科技大學(xué)出版社

2023-05-26 15:23:15 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論