Broadkey 6416板是一款高端的PCI總線數(shù)據(jù)采集卡,該卡可作軟件無線電數(shù)字中頻接收、數(shù)據(jù)采集、數(shù)據(jù)分析和信號(hào)處理等使用。該卡采用ADC+FPGA+DSP 的通用架構(gòu),都采用高速、高性能

2010-02-05 15:04:28

基于FPGA和DSP的圖像采集監(jiān)測(cè)通信平臺(tái)

2021-06-16 09:38:29 20

20 創(chuàng)龍結(jié)合TI KeyStone系列多核架構(gòu)TMS320C6678及Xilinx Kintex-7系列FPGA設(shè)計(jì)的TL6678F-EasyEVM開發(fā)板是一款DSP+FPGA高速大數(shù)據(jù)采集處理平臺(tái),其

2020-02-12 13:42:30 3447

3447 多通道視頻監(jiān)控系統(tǒng),通過對(duì)不同視頻通道穩(wěn)定、可靠地切換控制,實(shí)現(xiàn)監(jiān)控不同場(chǎng)景。該系統(tǒng)不僅彌補(bǔ)了傳統(tǒng)監(jiān)控視頻范圍有限的不足,而且提高了監(jiān)控資源的利用率,降低了監(jiān)控成本。

2020-01-08 15:16:00 1474

1474

設(shè)計(jì)了一種基于 TI DSP TMS320C6713B 和ALtera Cyclone 系列FPGA 的數(shù)據(jù)采集模塊,使用FPGA 做多路串行AD 器件的信號(hào)采集控制和數(shù)據(jù)緩沖,同時(shí)利用DSP

2019-03-05 16:30:29 16

16 關(guān)鍵詞:dsp , 驅(qū)動(dòng) , 視頻采集 視頻終端的核心是圖像的數(shù)字化處理模塊。基于PC機(jī)的數(shù)字視頻處理,給出了算法研究的途徑,而基于高速DSP的應(yīng)用模塊才提供了實(shí)時(shí)嵌入式視頻處理的可能。然而

2019-02-03 00:09:01 343

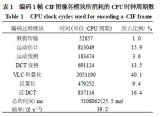

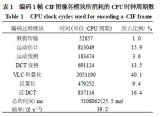

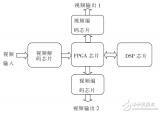

343 采用DSP 和FPGA 協(xié)同技術(shù)設(shè)計(jì)實(shí)現(xiàn)了一個(gè)高性能的MPEG24 視頻編碼器。FPGA 模塊完成視頻采集、YUV 分離、數(shù)據(jù)I/ O 等功能,而使用DSP 專一進(jìn)行視頻壓縮編碼。針對(duì)DSP 片

2018-07-18 07:45:00 557

557

設(shè)計(jì)了一種基于FPGA的實(shí)時(shí)視頻圖像采集處理電路系統(tǒng)。采用FPGA作為整個(gè)系統(tǒng)的控制和圖像數(shù)據(jù)處理中心。DDR2 SDRAM為高速儲(chǔ)存模塊核心器件,CMOS 7670為視頻圖像采集器件。

2018-02-10 02:43:55 19109

19109

本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設(shè)計(jì)。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進(jìn)行實(shí)時(shí)圖像運(yùn)算,通過圖像算法提取車流量信息,最終結(jié)合模糊算法實(shí)現(xiàn)智能控制。

2018-01-09 14:15:41 1710

1710

本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),DSP-BF561作為主處理器,負(fù)責(zé)整個(gè)算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實(shí)現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預(yù)處理中大量的累乘加運(yùn)算。實(shí)驗(yàn)證明系統(tǒng)達(dá)到了實(shí)時(shí)性要求。

2017-12-25 10:39:47 4256

4256

本文主要介紹了一種基于DSP+FPGA的實(shí)時(shí)圖像去霧增強(qiáng)系統(tǒng)設(shè)計(jì),FPGA通常作為一種調(diào)度使用,圖像處理算法實(shí)現(xiàn)主要靠高速處理信號(hào)處理芯片DSP完成,在跟蹤等領(lǐng)域圖像數(shù)據(jù)只需單向進(jìn)入DSP,處理后輸出相應(yīng)參數(shù)即可,在實(shí)時(shí)視頻圖像處理中大量圖像數(shù)據(jù)只需通過EMIF輸入,且輸出數(shù)據(jù)量較小可以實(shí)時(shí)完成。

2017-12-25 10:24:21 3159

3159

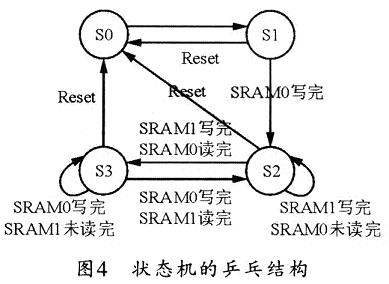

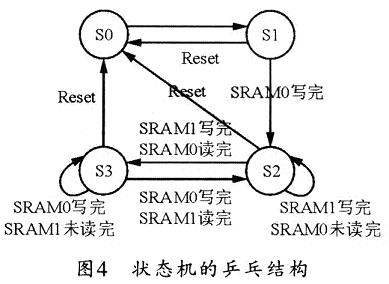

提出了基于 FPGA 的視頻監(jiān)控系統(tǒng)整體實(shí)現(xiàn)方案。首先介紹了在FPGA中設(shè)計(jì)I2C總線配置模塊對(duì)視頻處理芯片進(jìn)行合理的配置,然后簡(jiǎn)單介紹了視頻信號(hào)的處理過程。經(jīng)過處理后的視頻信號(hào)通過 乒乓機(jī)制 存儲(chǔ)

2017-11-24 15:39:58 2467

2467

針對(duì)傳統(tǒng)固定監(jiān)控架設(shè)成本高、監(jiān)控有死角且需要布置的視頻采集端個(gè)數(shù)太多的情況,提出一種基于ARM和FPGA相結(jié)合架構(gòu)的移動(dòng)視頻監(jiān)控系統(tǒng)及其軟硬件實(shí)現(xiàn)方法,在減少視頻采集端節(jié)點(diǎn)的前提下,能夠全方位實(shí)時(shí)

2017-11-17 11:23:01 1869

1869

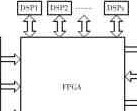

針對(duì)信號(hào)處理數(shù)據(jù)量大、實(shí)時(shí)性要求高的特點(diǎn),從實(shí)際應(yīng)用出發(fā),設(shè)計(jì)了以雙DSP+FPGA為核心的并行信號(hào)處理模塊。為了滿足不同的信號(hào)處理任務(wù)需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號(hào)處理

2017-11-17 06:11:40 2237

2237 隨著視頻處理技術(shù)的不斷發(fā)展,視頻監(jiān)控系統(tǒng)在生活中得到了廣泛的應(yīng)用,同時(shí)用戶對(duì)視頻監(jiān)控技術(shù)的實(shí)時(shí)性、穩(wěn)定性和清晰度也提出了更高的要求。以往基于CPU/DSP的視頻監(jiān)控系統(tǒng),以程序順序執(zhí)行的方式對(duì)視頻

2017-11-09 11:09:56 5

5 視頻終端的核心是圖像的數(shù)字化處理模塊。基于PC機(jī)的數(shù)字視頻處理,給出了算法研究的途徑,而基于高速DSP的應(yīng)用模塊才提供了實(shí)時(shí)嵌入式視頻處理的可能。然而,基于DSP的海量視頻數(shù)據(jù)的實(shí)時(shí)處理的關(guān)鍵則是

2017-11-03 15:44:28 0

0 摘要:采用兩片TI公司的專用視頻處理芯片TMS320DM642設(shè)計(jì)了一種多路視頻監(jiān)控系統(tǒng)。其中,DSP1與視頻采集芯片SAA7113共同完成多路視頻的采集,并拼接成一路視頻圖像輸出;DSP2完成

2017-10-30 17:03:37 2

2 的控制

電路可以大大減少

DSP的開銷,減少軟件實(shí)現(xiàn)的難度;同時(shí)可以作為一個(gè)集成的

視頻采集模塊,用在一般的

DSP芯片上,減少硬件開發(fā)的難度。 本文實(shí)現(xiàn)了一種在

采集A/D

模塊、專用

視頻FIFO以及

DSP微處理使用CPLD作為純硬件控制的方案。使用這種方案的創(chuàng)新點(diǎn)是首先因?yàn)槭褂?/div>

2017-10-20 11:11:48 31

31 基于FPGA和多DSP的多總線并行處理器設(shè)計(jì)

2017-10-19 13:40:31 4

4 的控制電路可以大大減少DSP的開銷,減少軟件實(shí)現(xiàn)的難度;同時(shí)可以作為一個(gè)集成的視頻采集模塊,用在一般的DSP芯片上,減少硬件開發(fā)的難度。

2017-10-13 09:19:05 2

2 基于DSP和FPGA的多頻聲納采集系統(tǒng)設(shè)計(jì)_劉寅

2017-03-19 11:45:23 0

0 基于FPGA的某型雷達(dá)視頻采集預(yù)處理模塊設(shè)計(jì)

2016-08-30 15:10:14 34

34 基于DSP和FPGA技術(shù)的細(xì)胞圖像采集系統(tǒng)設(shè)計(jì)

2016-08-26 12:57:52 13

13 DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計(jì),從而能夠提高算法效率,同時(shí)其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級(jí),適合于實(shí)時(shí)視頻圖像處理。

2015-02-03 15:20:47 1106

1106

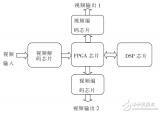

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過程。

2014-10-23 15:35:49 5907

5907

隨著視頻監(jiān)控的不斷發(fā)展和DSP技術(shù)的進(jìn)步,基于DSP的視頻監(jiān)控受到越來越廣泛的關(guān)注和應(yīng)用。基于TI公司的TMS320DM6437設(shè)計(jì)了實(shí)時(shí)的網(wǎng)絡(luò)視頻監(jiān)控平臺(tái)。介紹了整個(gè)系統(tǒng)的框架,并對(duì)基于

2013-09-25 10:39:53 30

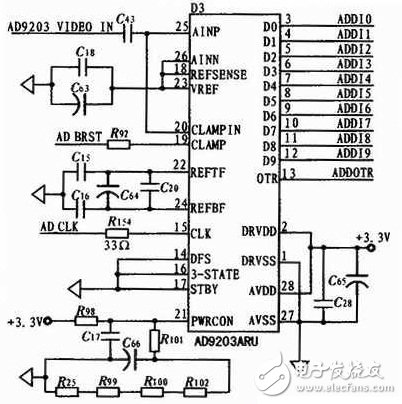

30 在研究基于DSP的視頻監(jiān)控系統(tǒng)時(shí),考慮到高速實(shí)時(shí)處理及實(shí)用化兩方面的具體要求,需要開發(fā)一種具有高速、高集成度等特點(diǎn)的視頻圖象信號(hào)采集系統(tǒng),為此系統(tǒng)采用專用視頻解碼芯片

2012-05-25 09:44:08 1950

1950

本文采用TI公司最新推出的Davinci系列DSP中的一款TMS320DM6437和Xilinx公司的高性能、低成本Spartan-3系列FPGA來構(gòu)建一個(gè)高性能、低成本的嵌入式多路視頻監(jiān)控系統(tǒng)硬件平臺(tái)。

2012-05-25 09:19:19 1009

1009

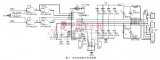

基于嵌入式系統(tǒng)的諸多優(yōu)點(diǎn),這里提出一種基于DSP的視頻監(jiān)控系統(tǒng)解決方案。整個(gè)系統(tǒng)硬件設(shè)計(jì)由電源、視頻信號(hào)處理、FPGA和外圍接口等模塊組成。其中,圖像處理模塊接收CCD圖像傳感

2012-05-21 17:15:43 3118

3118

視頻終端的核心是圖像的數(shù)字化處理模塊。基于PC機(jī)的數(shù)字視頻處理,給出了算法研究的途徑,而基于高速DSP的應(yīng)用模塊才提供了實(shí)時(shí)嵌入式視頻處理的可能。然而,基于DSP的海量視頻數(shù)

2011-09-29 15:14:12 1539

1539

在以DSP為核心的視頻處理系統(tǒng)中,視頻采集的方法通常可以分為兩大類:自動(dòng)的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過FIFO或者雙口RAM向DSP傳送數(shù)據(jù)

2011-09-14 17:05:31 2249

2249

文章介紹了一種基于DSP爭(zhēng)FPGA結(jié)構(gòu)的高精度測(cè)井?dāng)?shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方法,包括信號(hào)調(diào)理、數(shù)據(jù)采集、數(shù)據(jù)處理等。整個(gè)系統(tǒng)使用16位高精度A/D轉(zhuǎn)換芯片AD974。數(shù)字電路部分采用Xilinx公司

2011-09-08 17:46:55 69

69 為了提高系統(tǒng)的監(jiān)控能力降低成本,提出了一種基于CMOS的多通道 視頻監(jiān)控 方案。首先基于同步信號(hào)控制各路視頻同步,保證圖像質(zhì)量。在此基礎(chǔ)上由DSP和FPGA產(chǎn)生控制切換信號(hào),控制多

2011-08-05 15:20:33 74

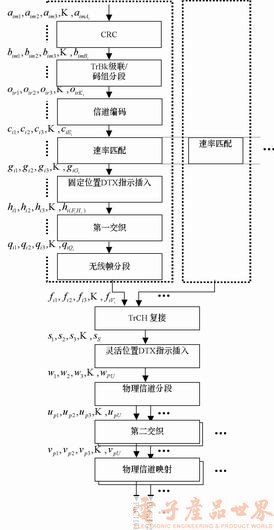

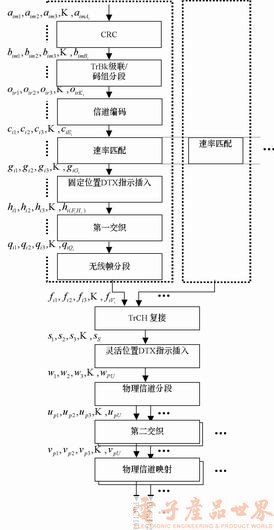

74 摘要:本文在分析TD-SCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,提出了一種在性能、靈活性和性價(jià)比方面都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 關(guān)鍵詞:TD-SCDMA;基帶處理;DSP;FPGA

2011-03-02 01:38:41 60

60 摘要:設(shè)計(jì)了基于PXA270Xscale處理器和多片TMS320DM642DSP處理器的并行智能視頻監(jiān)控系統(tǒng),詳細(xì)介紹了其體系結(jié)構(gòu)的特點(diǎn),關(guān)鍵模塊的硬件組成及工作原理,并通過在該系統(tǒng)上實(shí)現(xiàn)運(yùn)動(dòng)目標(biāo)的實(shí)時(shí)跟蹤算法驗(yàn)證了系統(tǒng)的設(shè)計(jì)性能。驗(yàn)證結(jié)果表明,該監(jiān)控系統(tǒng)具有處理

2011-02-27 13:58:29 32

32 摘要:為了實(shí)現(xiàn)高速HDLC通訊協(xié)議,設(shè)計(jì)了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機(jī);其中DSP用于實(shí)現(xiàn)數(shù)據(jù)控制,FPGA用于實(shí)現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 設(shè)計(jì)一種基于FPGA的多通道同步數(shù)據(jù)采集存儲(chǔ)系統(tǒng),分為多通道同步數(shù)據(jù)采集模塊和數(shù)據(jù)存儲(chǔ)模塊。系統(tǒng)設(shè)計(jì)采用多通道數(shù)據(jù)的同步實(shí)時(shí)采集以及壞塊檢測(cè)技術(shù)。多通道同步數(shù)據(jù)采集

2010-12-27 15:31:33 69

69 目前的衛(wèi)星遙感圖像壓縮系統(tǒng)硬件方案大多基于高性能可編程邏輯器件FPGA[2-4]。但這種方案整系統(tǒng)成本居高不下,且FPGA存在單粒子翻轉(zhuǎn)效應(yīng)。因此,筆者提出一種多DSP+FPGA的

2010-11-27 10:35:05 1271

1271

為了擴(kuò)大監(jiān)控范圍,提高資源利用率,降低系統(tǒng)成本,提出了一種多通道視頻切換的解決方案。首先從視頻信號(hào)分離出行場(chǎng)信號(hào),然后根據(jù)行場(chǎng)信號(hào)由DSP和FPGA產(chǎn)生控制信號(hào),控制多

2010-11-22 16:19:39 14

14 在視頻監(jiān)控系統(tǒng)中使用FPGA進(jìn)行視頻處理:視頻監(jiān)控系統(tǒng)是火車站,機(jī)場(chǎng),銀行,娛樂場(chǎng)所,購(gòu)物中心乃至家庭保安的重要組件。

您可以使用xilinx視頻IP模塊組實(shí)現(xiàn)DVR。

2010-09-22 08:12:16 36

36 為了在梳棉機(jī)上實(shí)現(xiàn)在線檢測(cè)監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測(cè)裝置,取代傳統(tǒng)的PC-Base檢測(cè)模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計(jì)和控制

2010-07-17 17:25:09 10

10 DSP 網(wǎng)絡(luò)視頻監(jiān)控

DSP 網(wǎng)絡(luò)視頻監(jiān)控及OpenCV在DSP平臺(tái)的移植摘要本系統(tǒng)使用DM642 網(wǎng)絡(luò)圖像處理開發(fā)平臺(tái)和OpenCV 來構(gòu)建網(wǎng)絡(luò)視頻監(jiān)控程序。系統(tǒng)采用客戶機(jī)

2010-04-07 14:35:37 31

31 對(duì)于嵌入式折反射全景視頻處理系統(tǒng),由于計(jì)算量大,一般采用多處理器協(xié)同的結(jié)構(gòu),但在該結(jié)構(gòu)下多個(gè)處理器之間需要進(jìn)行高速的數(shù)據(jù)通信。該文提出一種基于DSP+FPGA 架構(gòu)的雙核

2010-03-06 11:03:46 10

10 為了在梳棉機(jī)上實(shí)現(xiàn)在線檢測(cè)監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測(cè)裝置,取代傳統(tǒng)的PC-Base檢測(cè)模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計(jì)和控制

2010-02-24 14:06:05 18

18 基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來

2010-01-11 10:15:46 507

507 一種基于DSP+FPGA的控制系統(tǒng)方案設(shè)計(jì)

一、前言 ?

本文提到的控制系統(tǒng)控制通信設(shè)備的正常工作,是整個(gè)通信設(shè)備的重要組成部分。該控制系統(tǒng)要實(shí)現(xiàn)的功能

2009-12-22 17:44:41 836

836

基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來記錄信息的

2009-12-16 10:20:55 548

548

簡(jiǎn)要分析了DSP+FPGA系統(tǒng)的特點(diǎn)和優(yōu)越性,并且結(jié)合一個(gè)實(shí)時(shí)信號(hào)處理板的開發(fā),提出在此類系統(tǒng)中,FPGA設(shè)計(jì)的幾個(gè)關(guān)鍵問題,并且給出了詳實(shí)的分析和解決方案。

2009-09-02 17:44:44 24

24 本文介紹了DSP 和FPGA 在數(shù)字電子設(shè)計(jì)中的優(yōu)勢(shì),并結(jié)合雷達(dá)模擬系統(tǒng)的硬件設(shè)計(jì)實(shí)例,重點(diǎn)闡述了相應(yīng)的硬件與軟件實(shí)現(xiàn)方法。關(guān)鍵詞:DSP FPGA 數(shù)字電路設(shè)計(jì)雷達(dá)模擬系統(tǒng)

2009-08-25 14:33:01 15

15 為了解決基于DSP 視頻監(jiān)控系統(tǒng)的數(shù)據(jù)采集問題,本系統(tǒng)采用了視頻專用解碼A/D 芯片和復(fù)雜可編程邏輯器件CPLD進(jìn)行控制和接口設(shè)計(jì),有效地實(shí)現(xiàn)視頻信號(hào)的采集與讀取的高速并行性

2009-08-13 10:47:55 21

21 摘? 要: 本文在分析WCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,結(jié)合DSP和FPGA性能的比較,提出了一種在性能、靈活性和性價(jià)比上都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 引言 隨

2006-03-11 13:29:42 634

634

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論