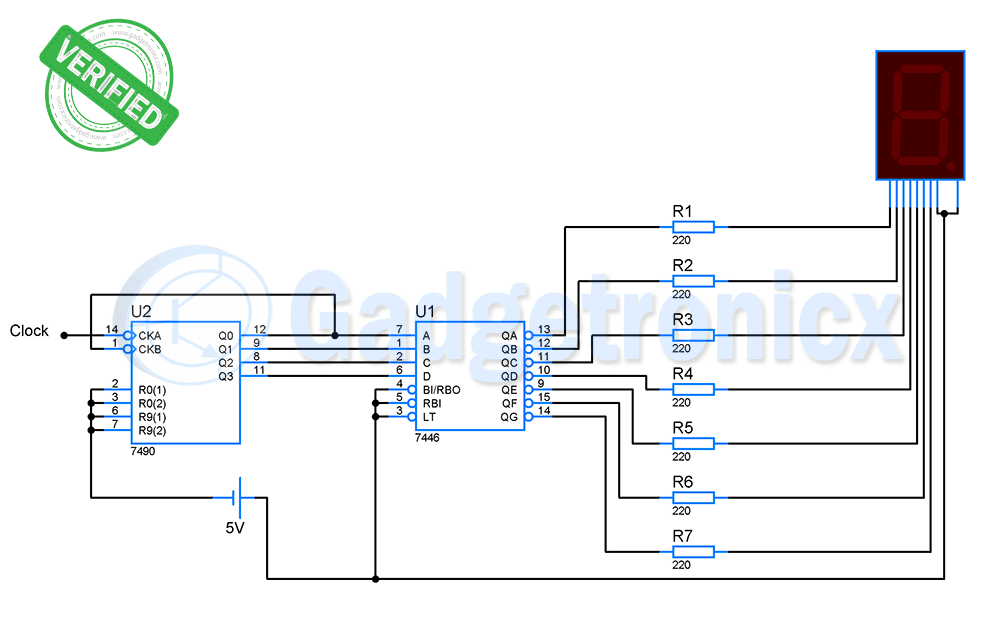

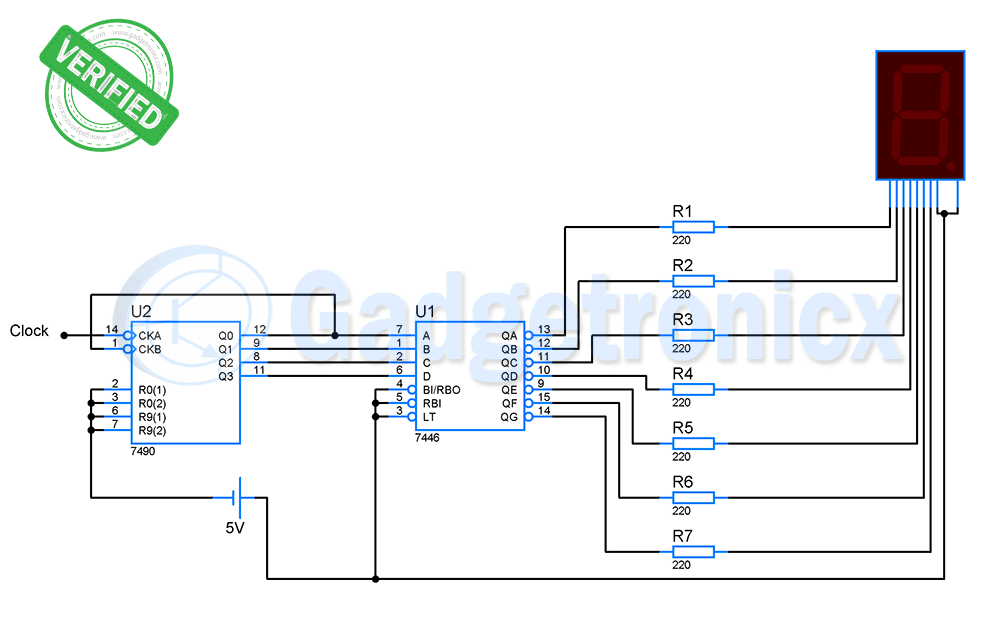

圖所示電路是靜態(tài)的0到9顯示,使用能夠顯示7到0數(shù)字的9段。它在日常生活中有很多應(yīng)用,并使用兩個(gè)簡(jiǎn)單的IC的7490和7446實(shí)現(xiàn)。該電路基于異步十進(jìn)制計(jì)數(shù)器7490(IC2)、7段顯示器(D1

2023-07-05 15:51:15 435

435

可預(yù)置同步BCD十進(jìn)制計(jì)數(shù)器;異步復(fù)位-74HC160

2023-02-20 20:05:50 4

4 帶 10 個(gè)解碼輸出的 Johnson 十進(jìn)制計(jì)數(shù)器-74HC_HCT4017_Q100

2023-02-17 19:59:07 0

0 可預(yù)置同步4位二進(jìn)制計(jì)數(shù)器;異步復(fù)位-74HC161

2023-02-16 21:10:17 1

1 可預(yù)置同步4位二進(jìn)制計(jì)數(shù)器;異步復(fù)位-74HC161_Q100

2023-02-16 21:10:00 1

1 帶 10 個(gè)解碼輸出的 Johnson 十進(jìn)制計(jì)數(shù)器-74HC_HCT4017

2023-02-16 20:29:32 0

0 可預(yù)置同步4位二進(jìn)制計(jì)數(shù)器;異步復(fù)位-74LVC161

2023-02-15 19:23:09 0

0 雙十進(jìn)制紋波計(jì)數(shù)器-74HC_HCT390

2023-02-15 19:06:31 0

0 本方案是一個(gè)基于 FPGA ?的十進(jìn)制計(jì)數(shù)器。共陽極 7 段顯示器上的 0 到 9 十進(jìn)制計(jì)數(shù)器,硬件在 Xilinx Spartan 6 FPGA 板上實(shí)現(xiàn)。

2022-12-20 14:52:25 2

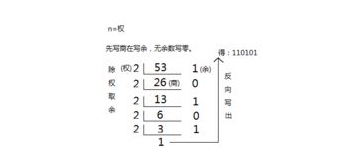

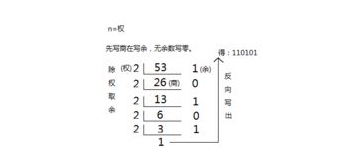

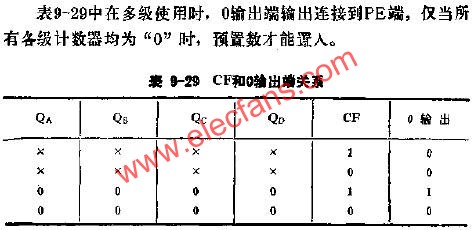

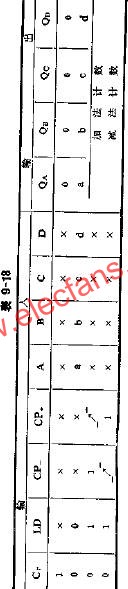

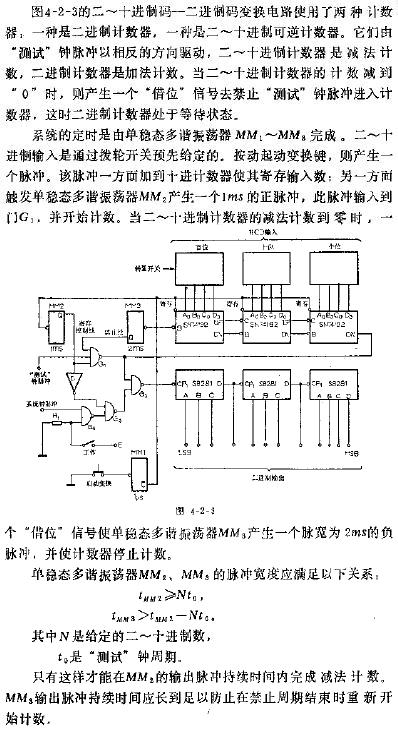

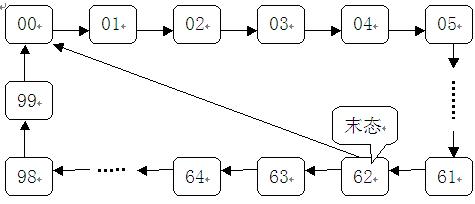

2 、預(yù)置數(shù)法組成任意進(jìn)制加法計(jì)數(shù)器七、預(yù)置數(shù)法組成任意進(jìn)制減法計(jì)數(shù)器八、級(jí)聯(lián)法和復(fù)位法的混合應(yīng)用九、級(jí)聯(lián)法和預(yù)置數(shù)法的混合應(yīng)用十、應(yīng)用總結(jié) 一、用集成計(jì)數(shù)器可以實(shí)現(xiàn)任意進(jìn)制的計(jì)數(shù)器

2008-07-05 13:41:26

二進(jìn)制編碼的十進(jìn)制是一個(gè)串行數(shù)字計(jì)數(shù)器,可計(jì)數(shù)十位數(shù)字,它會(huì)為每個(gè)新的時(shí)鐘輸入重置。由于它可以通過10種獨(dú)特的輸出組合,因此也被稱為“十進(jìn)制(BCD)計(jì)數(shù)器”。十進(jìn)制計(jì)數(shù)器可以計(jì)數(shù)0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 11018

11018

CD4017 十進(jìn)制計(jì)數(shù)器的應(yīng)用實(shí)驗(yàn)

2022-05-11 16:58:25 47

47 計(jì)數(shù)器(Counter)由基本的計(jì)數(shù)單元和控制門所組成,是在數(shù)字系統(tǒng)中對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制功能,且兼有分頻功能的儀器。計(jì)數(shù)器按進(jìn)位制不同,分為二進(jìn)制計(jì)數(shù)器和十進(jìn)制計(jì)數(shù)器;按

2021-11-25 18:06:07 32

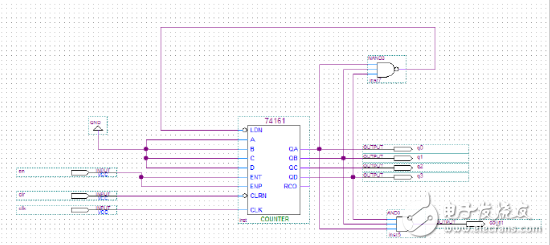

32 74LS161為4位二進(jìn)制同步加法計(jì)數(shù)器。其中 是異步清零端, 是預(yù)置數(shù)控制端,D3 D2 D1 D0是預(yù)置數(shù)輸入端,CTt和CTp是計(jì)數(shù)使能端,CO是進(jìn)位輸出端(CO=Q3 Q0

2021-07-09 16:12:21 73502

73502

芯片74ls160是十進(jìn)制計(jì)數(shù)器,這種同步可預(yù)置十進(jìn)計(jì)數(shù)器是由四個(gè)D型觸發(fā)器和若干個(gè)門電路構(gòu)成。

2021-06-05 14:35:38 12686

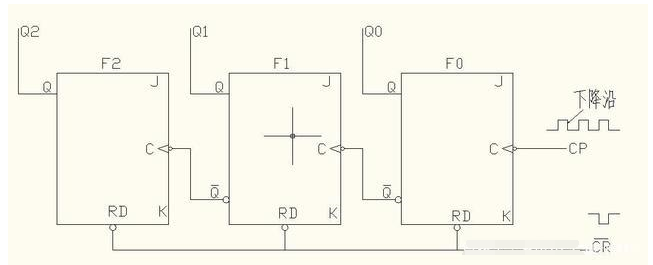

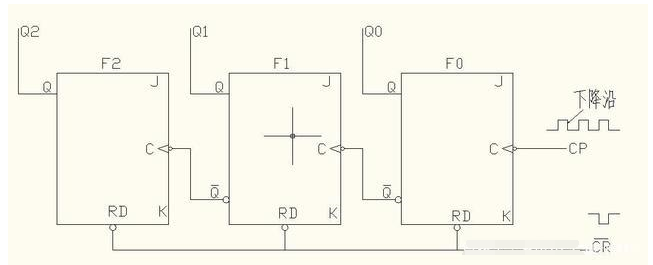

12686 該計(jì)數(shù)器是一個(gè)3位二進(jìn)制異步減法計(jì)數(shù)器,它與前面介紹過的3位二進(jìn)制異步加法計(jì) 數(shù)器一樣,是由3個(gè)JK觸發(fā)器組成,其中J、K端都懸空(相當(dāng)于J=1、K=1),兩者的不同 之處在于,減法計(jì)數(shù)器是將前一個(gè)觸發(fā)器的Q非端與下一個(gè)觸發(fā)器的CP端相連。

2021-04-18 11:19:47 15455

15455

本文檔的主要內(nèi)容詳細(xì)介紹的是十進(jìn)制計(jì)數(shù)器的Multisim仿真實(shí)例電路圖免費(fèi)下載。

2020-09-04 16:55:00 81

81 十進(jìn)制計(jì)數(shù)器是人們最常用的計(jì)數(shù)器,但在某些特殊的計(jì)數(shù)場(chǎng)合下,也需要其他進(jìn)制的計(jì)數(shù)器。

2020-01-14 09:46:48 6705

6705

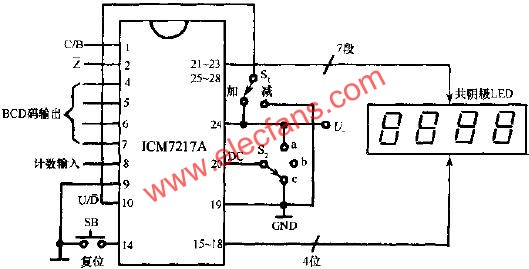

40110 為十進(jìn)制可逆計(jì)數(shù)器/鎖存器/譯碼器/驅(qū)動(dòng)器,具有加減計(jì)數(shù),計(jì)數(shù)器狀態(tài)鎖存,七段顯示譯碼輸出等功能。

2019-04-30 08:00:00 6

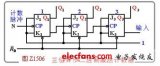

6 關(guān)鍵詞:TTL , 分頻器 , 計(jì)數(shù)器 , 十進(jìn)制 如圖所示為由TTL十進(jìn)制計(jì)數(shù)器構(gòu)成的分頻電路。在許多情況下。需要對(duì)脈沖序列進(jìn)行N(N為整數(shù))分頻。例如,數(shù)字鐘需要進(jìn)行60分頻,得到重復(fù)頻率為

2018-10-03 18:46:02 2650

2650 CD4040組成加法計(jì)數(shù)器,手動(dòng)加1計(jì)數(shù)。

2.二進(jìn)制與十進(jìn)制數(shù)字對(duì)照顯示實(shí)驗(yàn) 本電路可以形象地顯示0~9的二進(jìn)制數(shù)。按動(dòng)加1按鈕AN2,計(jì)數(shù)器的輸入端CP得到一個(gè)負(fù)脈沖信號(hào),計(jì)數(shù)器進(jìn)行加1

2018-09-20 18:26:41 2050

2050 本文主要介紹了74ls163實(shí)現(xiàn)十進(jìn)制計(jì)數(shù)器電路。改變74LS163二進(jìn)制計(jì)數(shù)器為十進(jìn)制計(jì)數(shù)器,即用一FDS4435BZ個(gè)與非門,其兩個(gè)輸人取自QA和QD,輸出接清零端α‘R。當(dāng)?shù)?個(gè)脈沖結(jié)束時(shí),鈑

2018-05-08 11:31:20 44957

44957

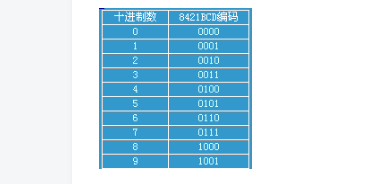

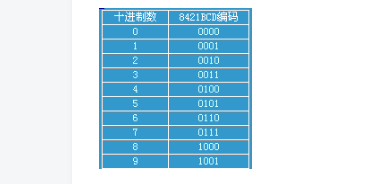

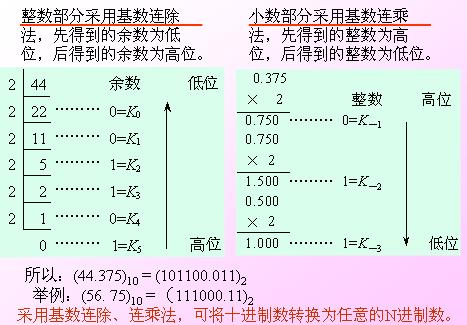

二進(jìn)制編碼的十進(jìn)制數(shù),簡(jiǎn)稱BCD碼。這種方法是用4位二進(jìn)制碼的組合代表十進(jìn)制數(shù)的0,1,2,3,4,5,6 ,7,8,9 十個(gè)數(shù)符。由8421碼加3后形成的余3碼是一種BCD碼,它是由8421碼加3后形成的(即余3碼是在8421碼基礎(chǔ)上每位十進(jìn)制數(shù)BCD碼再加上二進(jìn)制數(shù)0011得到的)。

2018-03-02 09:38:39 179839

179839

8421碼是中國大陸的叫法,8421碼是BCD代碼中最常用的一種。在這種編碼方式中每一位二值代碼的1都是代表一個(gè)固定數(shù)值,把每一位的1代表的十進(jìn)制數(shù)加起來,得到的結(jié)果就是它所代表的十進(jìn)制數(shù)碼。

2018-03-02 09:05:08 30273

30273

74ls290是一個(gè)二,五,十進(jìn)制計(jì)數(shù)器,本文為大家介紹由74ls290構(gòu)成的各種進(jìn)制計(jì)數(shù)器的電路。

2018-01-26 09:26:11 106188

106188

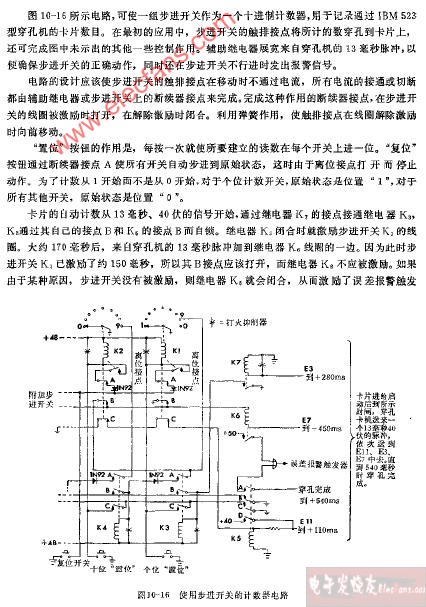

計(jì)數(shù)器在數(shù)字系統(tǒng)中應(yīng)用廣泛,如在電子計(jì)算機(jī)的控制器中對(duì)指令地址進(jìn)行計(jì)數(shù),以便順序取出下一條指令,在運(yùn)算器中作乘法、除法運(yùn)算時(shí)記下加法、減法次數(shù),又如在數(shù)字儀器中對(duì)脈沖的計(jì)數(shù)等等。本文為大家介紹74LS290組成的十進(jìn)制計(jì)數(shù)器。

2018-01-25 14:52:47 25181

25181

74LS290為異步二-五-十進(jìn)制加法計(jì)數(shù)器。本文為大家介紹74ls290構(gòu)成31進(jìn)制計(jì)數(shù)器電路。

2018-01-25 14:36:39 16924

16924

本文主要介紹了74ls160十進(jìn)制計(jì)數(shù)器電路的設(shè)計(jì)與實(shí)現(xiàn)。74LS160是二~十進(jìn)制同步可預(yù)置計(jì)數(shù)器,1腳Cr為清零端,低電平有效.2腳CP為時(shí)鐘脈沖輸人端,上升沿觸發(fā).3~6V腳D1一D4為數(shù)據(jù)

2018-01-18 15:14:45 182091

182091

74ls161為二進(jìn)制同步計(jì)數(shù)器,具有同步預(yù)置數(shù)、異步清零以及保持等功能。兩片74ls161可設(shè)計(jì)一個(gè)24進(jìn)制計(jì)數(shù)器。

2018-01-16 15:30:46 110315

110315

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

435

435

4

4 0

0 1

1 1

1 0

0 0

0 2

2 11018

11018

47

47 32

32 73502

73502

12686

12686 15455

15455

81

81 6705

6705

6

6 2650

2650 2050

2050 44957

44957

179839

179839

30273

30273

106188

106188

25181

25181

16924

16924

182091

182091

110315

110315

111115

111115

148134

148134

60783

60783

81

81 28

28 1

1 118057

118057 19621

19621

6871

6871

963

963

814

814

811

811

1197

1197

5242

5242

8303

8303 23684

23684 6643

6643 5522

5522 8495

8495 1357

1357

4166

4166

867

867

4593

4593

562

562

1940

1940

33045

33045

5412

5412

1405

1405

2733

2733

27668

27668

9254

9254

3143

3143

3559

3559

評(píng)論