數字頻率計課程設計圖

- 頻率(58149)

- 數字頻率計(35394)

相關推薦

[求助]數字頻率計設計

我是一大三測控專業的學生,我們微電子實習需要設計一數字頻率計,個人由于能力限制,許多方面都還不是很明白,希望能得到

2008-12-12 19:01:39

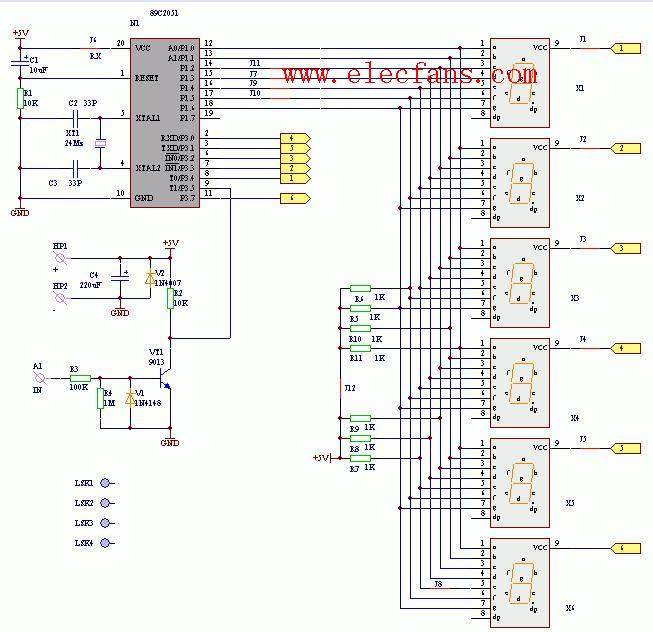

基于單片機的數字頻率計設計

文末下載完整資料1.1數字頻率計概述? ?數字頻率計是計算機、通訊設備、音頻視頻等科研生產領域不可缺少的測量儀器。它是一種用十進制數字顯示被測信號頻率的數字測量儀器。它的基本功能是測量正弦信號

2021-11-04 12:51:04 31

31

31

31基于51單片機的數字頻率計的設計講解

基于51單片機的數字頻率計的設計講解(單片機原理及應用)-該文檔為基于51單片機的數字頻率計的設計講解資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-22 10:54:43 85

85

85

85如何進行簡易數字頻率計的設計分析

文章簡單闡述了數字頻率計在設計之前的理論分析,給出了數字頻率計誤差分析、靈敏度涵義、觸發信號誤差、信號時間間隔的測量等問題的理論分析,為數字頻率計的設計打下了一定的基礎。

2019-05-27 08:00:00 7

7

7

7基于FPGA自適應數字頻率計的設計

為頻率的測量。目前,市場上有各種多功能、高精度、高頻率的數字頻率計,但價格不菲。為適應實際工作的需要,本文在簡述頻率測量的基本原理和方法的基礎上,提供一種基于FPGA的數字頻率計的設計和實現過程,本方案不但切實可行,而且具有成本低廉、小巧輕便、便于攜帶等特點。

2019-01-01 16:00:00 6008

6008

6008

6008

數字頻率計

數字頻率計,數字電路課程的課程設計,

1) 頻率測量范圍:1HZ-10KHZ,10KHZ-100KHZ。

2)測量時間:T≤1.5S。

3)被測信號幅度:0.5V。

4) 具有四位十進制數字顯示功能。

2016-05-13 11:28:05 47

47

47

47大學數字頻率計課程設計報告

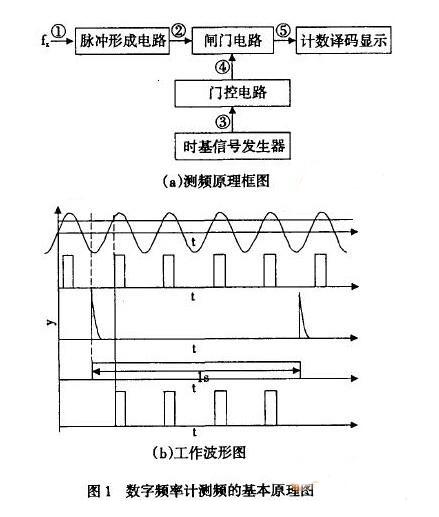

數字頻率計是一種專門對被測信號頻率進行測量的電子測量儀器。其最基本的工作原理為:當被測信號在特定時間段T內的周期個數為N時,則被測信號的頻率f=N/T。

2016-03-01 17:29:08 63

63

63

63基于verilog語言的數字頻率計設計

基于verilog語言的數字頻率計設計基于verilog語言的數字頻率計設計基于verilog語言的數字頻率計設計基于verilog語言的數字頻率計設計

2015-12-08 15:57:23 74

74

74

74數字頻率計的制作

數字頻率計是采用數字電路制做成的能實現對周期性變化信號頻率測量的儀器。頻率計主要用于測量正弦波、矩形波、三角波和尖脈沖等周期信號的頻率值。其擴展功能可以測量信號的周期和脈沖寬度。通常說的,數字頻率計是指電子計數式頻率計。

2015-11-20 14:55:57 142

142

142

142基于DSP2812設計的簡易數字頻率計

我們設計的簡易數字頻率計在未采用任何門控器件控制的情況下,在很寬的范圍內實現了等精度頻率測量,0.5Hz~10MHz的范圍內測量方波的最大相對誤差小于2e-6,測量正弦波的最大相對誤

2011-10-09 11:46:55 4613

4613

4613

4613

基于NiosII的等精度數字頻率計的設計

NiosII 處理器是一個具有很大靈活性的32 軟核處理器,比較容易在片上實現SOPC。本文主要提供了一種基于NiosII 軟核處理器的等精度數字頻率計的設計的實現方法。

2011-09-27 14:51:25 66

66

66

66設計簡易數字頻率計

頻率測量用途非常廣泛,高精度、寬量程的數字頻率計因而成為重要的測量儀器。簡易 數字頻率計 采用多周期測量原理,即用標準頻率信號填充整數個周期的被測信號,從而消除了被

2011-06-28 17:31:42 1194

1194

1194

1194數字頻率計

數字頻率計是一種基礎測量儀器,到目前為止已有30多年的發展史。早期,設計師們追求的目標主要是擴展測量范圍,再加上提高測量精度、穩定度等,這些也是人們衡量數字頻率計的

2011-04-07 13:40:59 922

922

922

92212位十進制等精度數字頻率計

分析了數字式頻率計,利用VHDL設計一種量程可自動轉換的12位十進制等精度數字頻率計,具有自動校驗和測量功能,能用標準時鐘校驗測量精度,并具有超量程報警功能,超出當前

2010-12-16 11:23:34 98

98

98

98超高頻數字頻率計的設計

摘要:介紹了以通用頻率計數器ICM7216D為核心,結合大規模集成電路和簡單的外圍電路,采用分頻法進行測量范圍為10kHz~700MHz的超高頻數字頻率計的設計方法,并給出了該頻率計的

2010-05-25 09:03:31 100

100

100

100八位150MHz數字頻率計的制作

八位150MHz數字頻率計的制作

在制作高頻電路時,會經常碰到頻率測量的問題,實際上頻率計(frequency counter)是一種比較容易自制的電子設備。以下將要制作的頻率計,其

2010-05-14 10:21:20 6257

6257

6257

6257

基于FPGA/CPLD芯片的數字頻率計設計

基于FPGA/CPLD芯片的數字頻率計設計摘要:詳細論述了利用VHDL硬件描述語言設計,并在EDA(電子設計自動化)工具的幫助下,用大規模可編程邏輯器件(FPGA/CPLD)實現

2010-04-30 14:45:13 132

132

132

132基于單片機的數字頻率計的方案

基于單片機的數字頻率計的方案

概述:設計一種以單片機AT89C51為核心的數字頻率計,介紹了單片機、數字譯碼和顯示單元的組成及工作原理。測量

2010-03-24 10:02:01 6181

6181

6181

6181

基于高速串行BCD碼除法的數字頻率計的設計

摘要: 介紹了在PPGA芯片上實現數字頻率計的原理。對各種硬件除法進行了比較,提出了高速串行BCD碼除法的硬件算法,并將其應用在頻率計設計中。

2009-06-20 14:48:14 1147

1147

1147

1147

基于FPGA的數字頻率計的設計與實現

介紹了一種運用FPGA開發軟件Quartus II設計的數字頻率計。該數字頻率計的1 Hz~1 MHz輸入被測脈沖信號具有頻率測量、周期測量、脈寬測量和占空比測量等多種用途,其測試結果由3 只

2009-03-17 10:31:31 184

184

184

184量程自動控制的數字頻率計

量程自動控制的數字頻率計一、 實驗目的:1、數字系統的設計與調試2、TTL 數字集成電路的使用3、量程自動控制的邏輯設計二、實驗要求:設計

2009-03-06 19:56:01 2310

2310

2310

2310

數字頻率計測頻率的基本原理

了解數字頻率計測頻率與測周期的基本原理;熟練掌握數字頻率計的設計與調試方法及減小測量誤差的方法。[重點與難點]重點:數字頻率計的組成框圖和波形圖。難點:

2008-12-01 14:36:48 505

505

505

505基于單片機和CPLD的數字頻率計的設計

基于單片機和CPLD的數字頻率計的設計

在傳統的控制系統中,通常將單片機作為控制核心并輔以相應的元器件構成一個整體。但這種方法硬件連線復

2008-10-15 08:59:51 992

992

992

992 電子發燒友App

電子發燒友App

評論