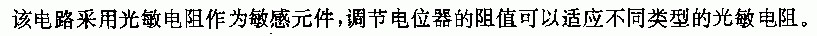

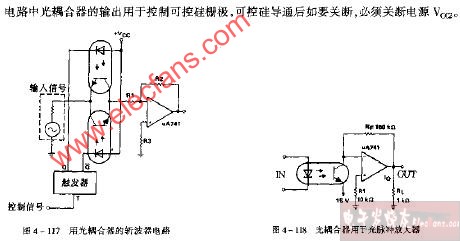

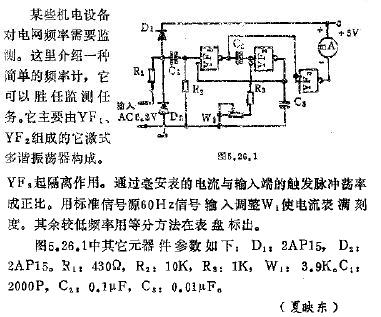

抑制50HZ的光放大器電路原理圖

- 光放大器(11774)

相關推薦

理解高性能Σ-Δ ADC中時鐘公差對50Hz/60Hz噪聲抑制的影響

理解高性能Σ-Δ ADC中時鐘公差對50Hz/60Hz噪聲抑制的影響Understanding the Effects of Clock Tolerances on 50/60Hz Noise

2008-10-06 13:57:19

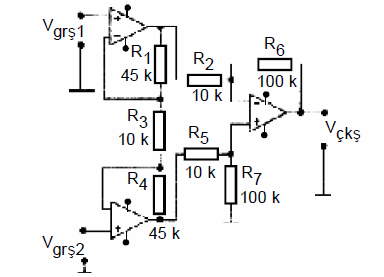

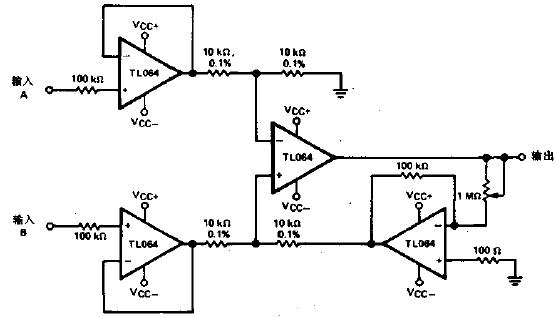

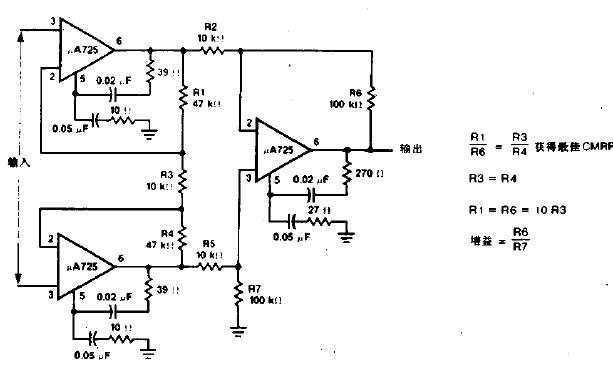

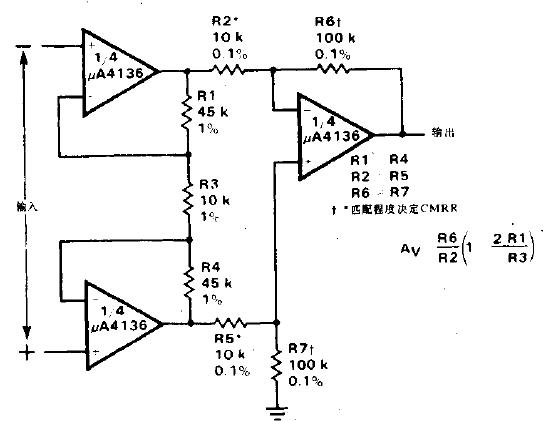

高共模抑制比(CMRR)儀表放大器電路原理圖講解

在儀表放大器中,高共模抑制比 (CMRR) 是一個理想的屬性,因為它允許精確的差分信號放大,同時抑制共模噪聲。我們將在這篇文章中討論高 CMRR 儀表放大器的電路原理圖。

2023-08-09 15:39:10 403

403

403

403

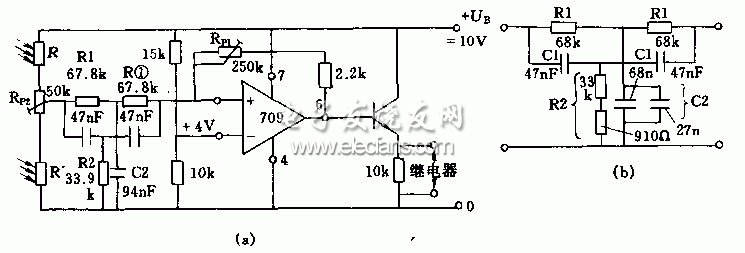

MOSFET功率放大器電路原理圖

這是Mosfet功率放大器5200W RMS的電路設計,原理圖是單通道的。該電路使用 16x IRFP250 在 2 歐姆負載下獲得 5200W RMS 功率輸出。

2023-07-31 16:18:07 423

423

423

423

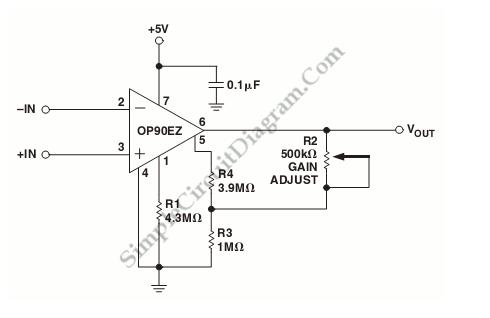

微功耗單電源儀表放大器電路原理圖

微功耗單電源儀表放大器電路原理圖如下所示。該電路僅需15μA電流,可提供超過110dB的公共抑制。單個放大器可以提供差分到單端轉換,并具有出色的共模抑制性能,因為反饋是調整引腳而不是反相引腳。

2023-07-27 16:38:23 265

265

265

265

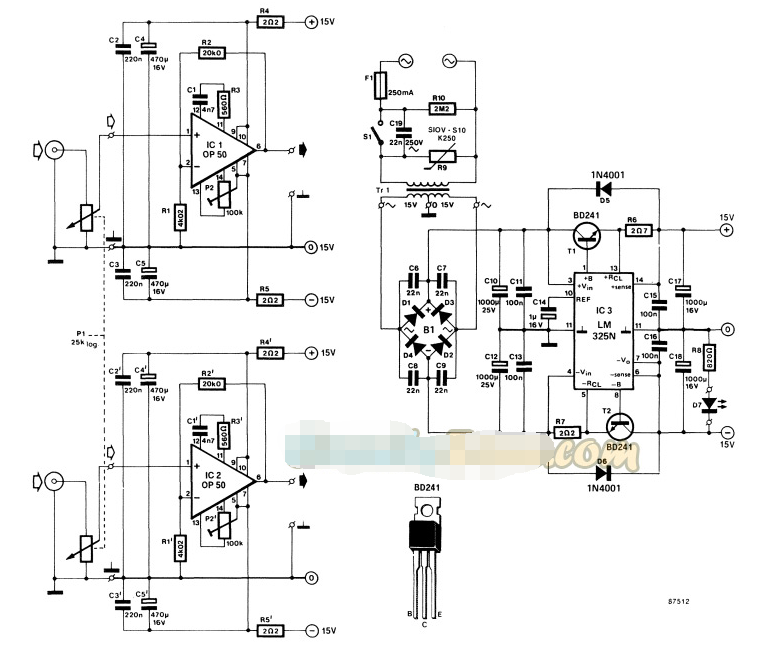

基于OP-50的耳機放大器電路圖

耳機放大電路的電路圖如圖所示。該單元基于OP-50型功率運算放大器,其技術特性總結于表1中。顯然,制造商Precision Monolithics Inc.已經做了一切可行的工作,以確保設備的最佳運行,正是考慮到這一點,放大器的其余部分在設計時就設計了。

2023-05-13 16:12:43 455

455

455

455

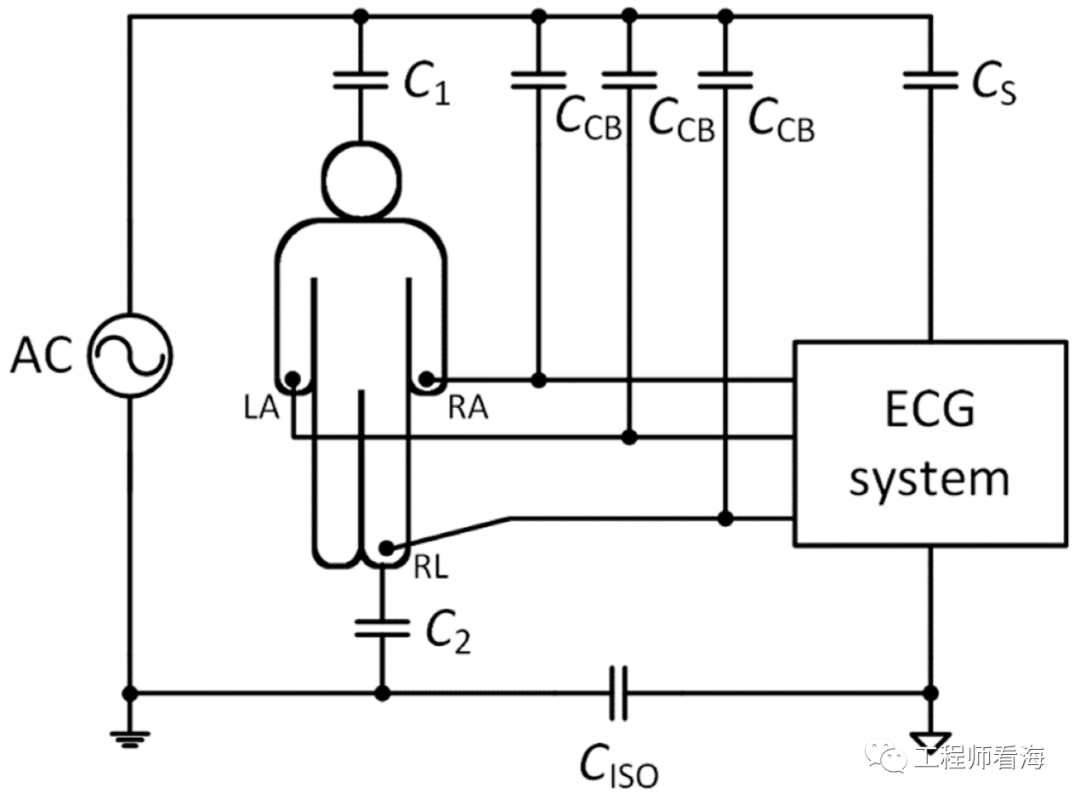

50Hz工頻干擾是怎么來的?怎么抑制?

在一些微弱信號采集應用場景,比如生物電信號,比如肌電信號、心電信號或者更微弱的腦電信號采集過程中難以避免的一重大干擾就是50hz工頻干擾。

2023-04-18 12:11:15 6793

6793

6793

6793

基于UAF42的50Hz陷波器設計與仿真

場合需要用到50Hz陷波器。本節將介紹使用UAF42設計一個高性能的50Hz陷波器。使用UAF42來設計50Hz陷波器,只需要外加6個電阻即可組成一個50Hz陷波器。

2022-11-30 11:00:31 2

2

2

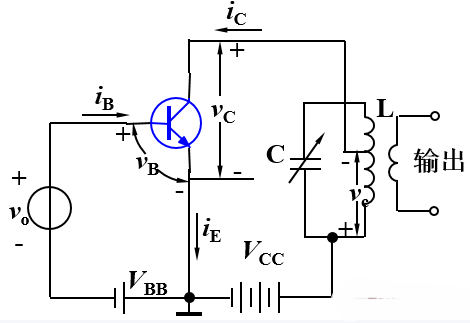

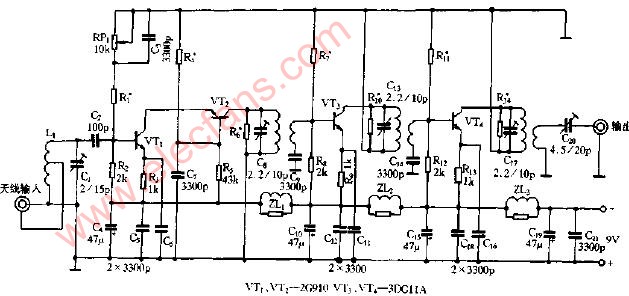

2高頻功率放大器電路圖原理圖解大全

雖然高頻功率放大器的使用場景和應用范圍都十分廣泛,但是很多人對于功率放大器的原理和電路圖都不清楚,下面就讓西安安泰電子的小編來為大家詳細地介紹高頻功率放大器電路圖原理圖解大全的內容。 1、高頻

2022-11-24 18:34:41 1860

1860

1860

1860

儀表放大器的處理抑制問題

計算由電源或共模電壓變化產生的失調偏移時很容易產生困惑。這種困惑的根本原因如下圖所示:

?

?

?

?

?

?

?

?

?

?

圖 1:儀表放大器的典型電源抑制比曲線

在圖

2021-11-23 09:14:17 1028

1028

1028

1028

放大器電源抑制比參數的評估方法

放大器電源抑制比參數對電路的影響與共模抑制比參數的影響近似,因為來自電源線路的噪聲對于放大器而言可視為共模噪聲。本篇介紹放大器電源抑制比參數的評估方法,并通過LTspice仿真參數測量電路。 電源

2020-12-06 10:22:00 3390

3390

3390

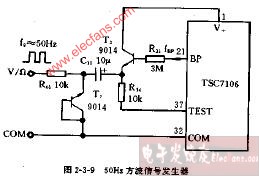

3390精準50Hz信號發生器,Precision 50Hz signal generator

,而(14)腳則輸出50Hz的反相信號.占空比為50%。

??? 50Hz頻率輸出分別經A1和A2運算放大器LM324緩沖,從其①腳和⑦腳可分別輸出兩個相位相反的50Hz方波信號。

2018-09-20 19:17:36 1052

1052

1052

1052話筒放大器電路圖大全(六款話筒放大器電路設計原理圖詳解)

本文主要介紹了話筒放大器電路圖大全(六款話筒放大器電路設計原理圖詳解)。話筒放大器的基本組成結構為壓限器、均衡效果器、撲聲消除器、嘶聲消除器、噪聲門等。設計電路一中采用MC2830形成語音電路。傳統

2018-03-26 11:58:00 204395

204395

204395

204395

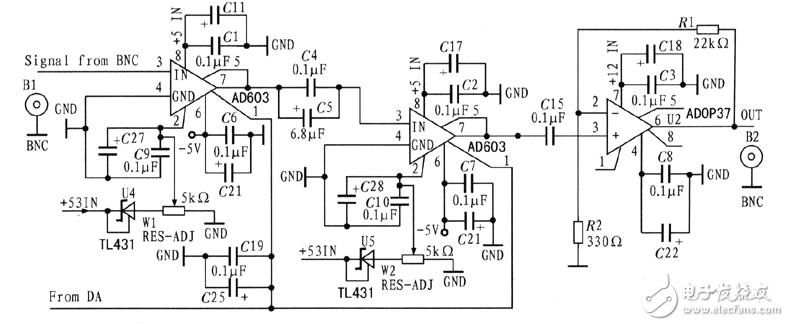

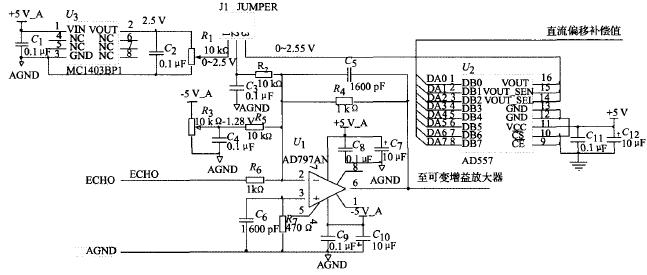

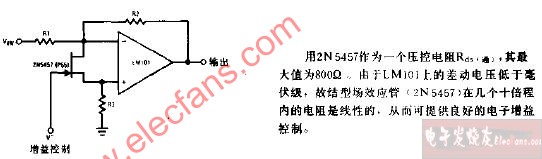

可變增益放大器電路圖(十一款可變增益放大器電路設計原理圖詳解)

本文主要介紹了可變增益放大器電路圖(十一款可變增益放大器電路設計原理圖詳解)。增益控制的核心電路由可變增益運算放大器AD603和精密運算放大器ADOP37組成。其中以AD603為核心,輔以外圍電路

2018-03-26 11:19:00 100931

100931

100931

100931

高精度50Hz時基電路設計

本文介紹的50Hz時基電路是由兩片CMOS數字集成電路和石英晶體組成,該電路產生的50Hz時基信號頻率準確、占空比一致、電路簡單、制作容易。

2017-09-07 15:44:16 10

10

10

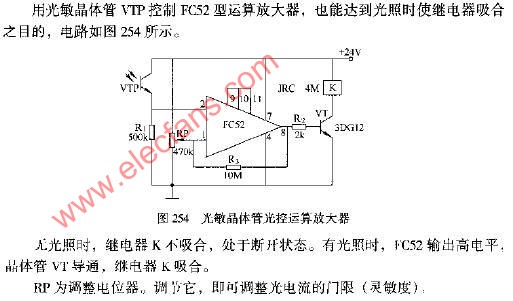

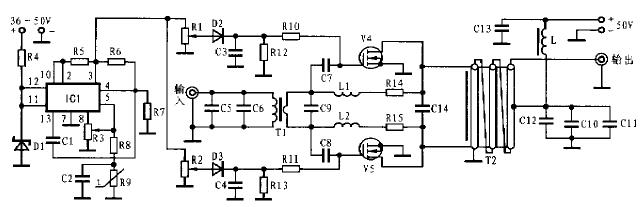

10逆變器誤差放大器原理圖

INVERTER.1端經R24、R25分壓后,與參考波相減作為誤差放大器的輸入,VR1用來調整U3放大器的工作點,逆變器誤差放大器原理圖:

2011-09-02 13:58:42 10009

10009

10009

10009

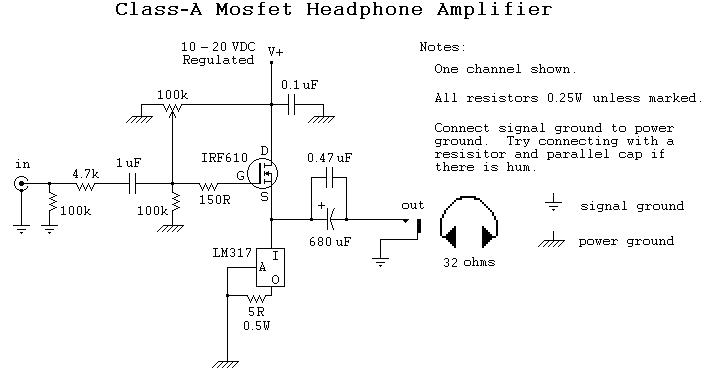

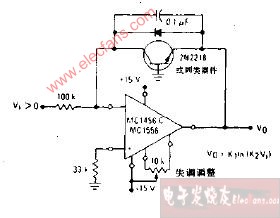

音頻AGC放大電路原理圖

音頻AGC放大電路原理圖

如圖所示為音頻AGC放大電路,這種放大器動態范圍大于50dB,輸出波形的失真非常小,并具有啟動快、緩慢衰減等優

2010-02-27 10:17:41 12794

12794

12794

12794

理解高性能ADC中時鐘公差對50Hz/60Hz噪聲抑制的影響

摘要:本文探討了時鐘公差對Σ-Δ ADC中低通抽樣和數字濾波器的影響,特別是對濾波器陷波頻率的影響。窄帶Σ-Δ應用通常利用數字濾波器提供50Hz、60Hz或50Hz/60Hz的噪聲抑制。在選擇

2009-05-07 11:35:53 723

723

723

723

理解高性能ADC中時鐘公差對50Hz/60Hz噪聲抑制的影響

摘要:本文探討了時鐘公差對Σ-Δ ADC中低通抽樣和數字濾波器的影響,特別是對濾波器陷波頻率的影響。窄帶Σ-Δ應用通常利用數字濾波器提供50Hz、60Hz或50Hz/60Hz的噪聲抑制。在選擇

2009-04-24 14:11:59 755

755

755

755

放大器的共模抑制比的定義

放大器的共模抑制比的定義

共模抑制比(CMRR)是指差分放大器對同時加到兩個輸入端上的共模信號的抑制能力。更確切地說,CMRR是產生特

2009-04-22 20:40:37 2004

2004

2004

2004理解高性能Σ-Δ ADC中時鐘公差對50Hz/60Hz噪聲抑

摘要:本文探討了時鐘公差對Σ-Δ ADC中低通抽樣和數字濾波器的影響,特別是對濾波器陷波頻率的影響。窄帶Σ-Δ應用通常利用數字濾波器提供50Hz、60Hz或50Hz/60Hz的噪聲抑制。在選擇

2009-04-20 15:53:19 586

586

586

586

電子發燒友App

電子發燒友App

評論