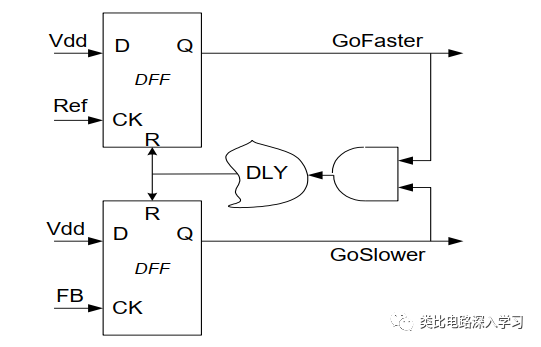

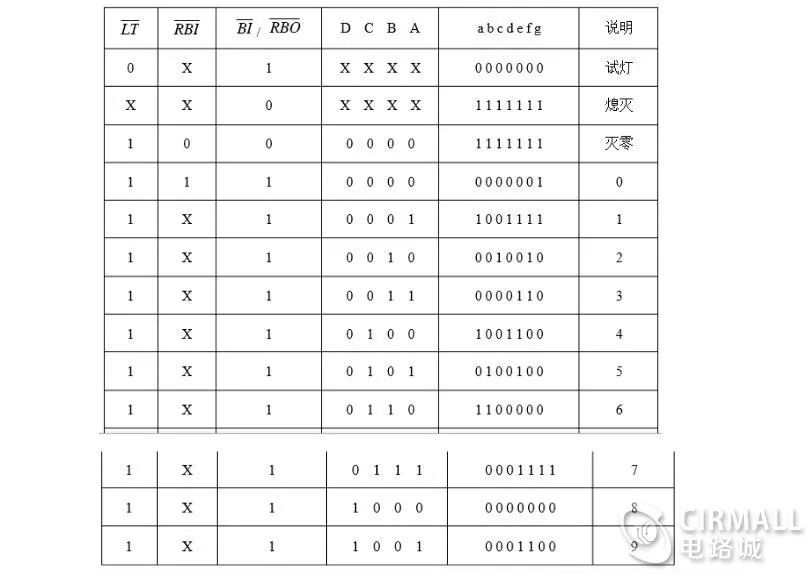

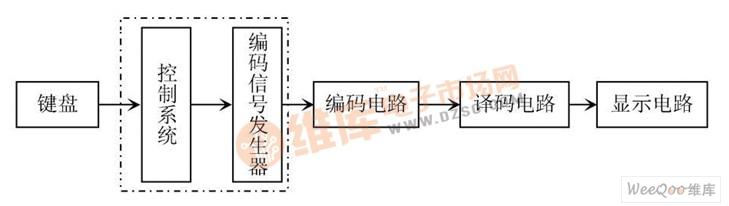

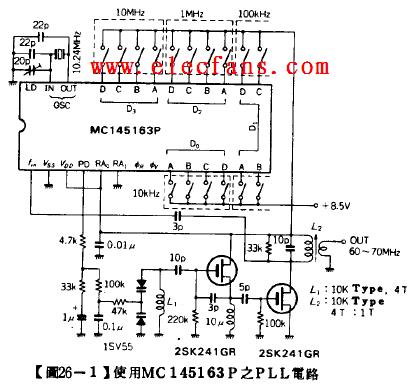

CMOS PLL譯碼電路

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術(shù)應(yīng)用>電子技術(shù)>電路圖>電工基礎(chǔ)電路圖>CMOS PLL譯碼電路

相關(guān)推薦

803

803 226

226 266

266 696

696

425

425

2100

2100

639

639

2201

2201

1311

1311 2

2 8343

8343

35527

35527

9355

9355

37712

37712

1

1 3

3 79

79 817

817 2104

2104 198

198 2291

2291

1293

1293

2613

2613 4173

4173 5062

5062 3505

3505 128

128 11017

11017

28

28 132

132 15826

15826

4367

4367

115

115 36

36 50

50 11977

11977

2011

2011

1930

1930

評(píng)論