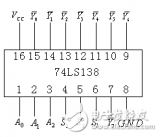

1、利用74LS138實現函數F=ABC+ABC2、利用74LS153構成一個全方位數碼管組成實驗電路,驗證74LS48的邏輯功能3、利用74LS153構成一位全加速,要求列出其真值表,寫出邏輯

2011-05-06 23:58:32

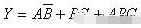

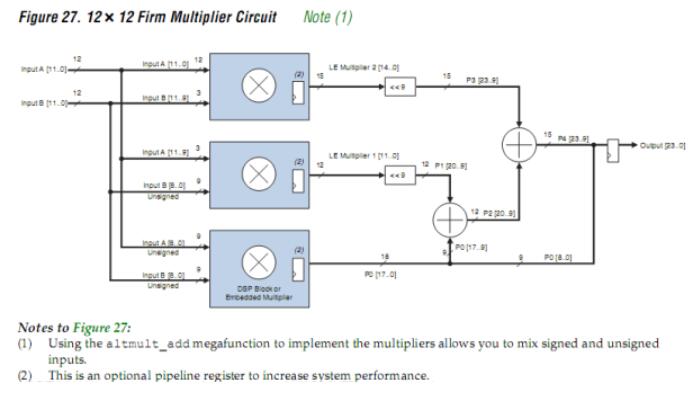

兩個N位二進制數x、y的乘積用簡單的方法計算就是利用移位操作來實現。

2023-06-21 09:01:57 259

259

例題:利用74LS138實現邏輯函數式Y的邏輯功能。

2023-03-23 14:38:04 8270

8270

8位同步二進制遞減計數器-74HC40103

2023-03-03 19:49:59 0

0 可預置同步4位二進制計數器;同步復位-74HC_HCT163

2023-02-21 18:35:57 0

0 7級二進制紋波計數器-74HC4024_Q100

2023-02-21 18:29:31 0

0 雙4位同步二進制計數器-74HC_HCT4520

2023-02-17 19:22:25 1

1 雙4位同步二進制計數器-74HC_HCT4520_Q100

2023-02-17 19:22:15 0

0 可預置同步4位二進制計數器;異步復位-74HC161

2023-02-16 21:10:17 1

1 可預置同步4位二進制計數器;異步復位-74HC161_Q100

2023-02-16 21:10:00 1

1 雙 4 位二進制紋波計數器-74LV393

2023-02-16 21:08:21 0

0 雙 4 位二進制紋波計數器-74LV393_Q100

2023-02-16 21:08:11 0

0 可預置同步4位二進制計數器;同步復位-74LVC163

2023-02-16 20:48:19 0

0 可預置同步 4 位二進制向上/向下計數器-74HC_HCT193

2023-02-15 19:40:01 0

0 可預置同步 4 位二進制向上/向下計數器-74HC191

2023-02-15 19:39:04 0

0 可預置同步4位二進制計數器;異步復位-74LVC161

2023-02-15 19:23:09 0

0 雙 4 位二進制紋波計數器-74HC_HCT393_Q100

2023-02-15 19:05:13 0

0 雙 4 位二進制紋波計數器-74HC_HCT393

2023-02-15 18:58:50 0

0 74LS138譯碼器實現流水燈的控制。

2022-10-12 09:30:57 3614

3614 將二進制數視為元胞自動機可能有助于數字二進制計數器的設計和實現嗎?

2022-07-28 11:47:10 840

840

基于8051的Proteus仿真-74LS138譯碼器應用

2022-05-11 17:30:25 42

42 位,52位尾數位。尾數:M是一個二進制小數,因為是二進制,所以科學計數法中這個值范圍是:1≤M尾數:M是一個二進制小數,因為是二進制,所以科學計數法中這個值范圍是:1≤MIEEE754對有效數字M和指數E,還有一些特別規定。1≤M<2,也就是說,M可以寫成1.xxxxxx的形式,其

2021-11-26 11:21:06 50

50 P1.2、P1.1、P1.0。)把譯碼輸出端口Y7Y0連接到L7L0八位LED電平指示輸入端口,驗證74LS138的邏輯譯碼功能。二、仿真圖三、代碼C語言實現:在這里插入代碼片```#include

2021-11-12 14:21:00 26

26 時序邏輯方式設計的16位乘法器,乘法通過逐向移位加原理來實現,從被乘數的最低位開始,若為1,則乘數左移與上一次和相加;若為0,左移后以全零相加,直至被乘數的最高位。從而實現乘法的移位運算。

2021-06-01 09:43:56 26

26 硬件乘法器的實現本質是“移位相加”。對于二進制,乘數和被乘數的每一位非0即1,相當于乘數中的每一位分別和被乘數的每一個體位進行與運算,并產生其相應的乘積位。這些局部乘積左移一位與上次的和相加。即從

2021-02-18 16:34:45 8901

8901

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數技術來實現。乘法器不僅作為

2021-02-18 15:08:01 22932

22932

本文檔的主要內容詳細介紹的是4位二進制并行加法器的程序和工程文件免費下載。

2020-09-30 16:41:00 26

26 乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數技術來實現。

2019-11-28 07:06:00 2848

2848 二進制加法器是半加器和全加法器形式的運算電路,用于將兩個二進制數字加在一起.

2019-06-22 10:56:38 23032

23032

VerilogHDL語言實現的兩位陣列乘法器和傳統的 Booth編碼乘法器進行了性能比較,得出用這種混合壓縮的器乘法器要比傳統的4-2壓縮器構成的乘法器速度提高了10%,硬件資源占用減少了1%。

2018-12-19 13:30:25 10152

10152

本文主要介紹了74ls160和74ls161區別。74ls161為四位二進制,74ls160 為2-10進制;且都為同步可預置計數器。74ls161 是4位二進制同步計數器(直接清除),74ls160 是4位十進制同步計數器(直接清除)。

2018-05-08 10:23:35 113147

113147

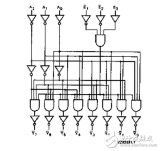

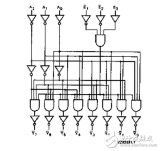

本文主要介紹了五款74ls138的應用電路圖。其中包括了74ls138全加器電路、74ls138搶答器電路、74ls138實現邏輯函數、74ls138全減器電路以及與74LS20組合的三人表決器電路。

2018-05-04 10:31:55 87718

87718

二進制數據壓縮算法二進制是計算技術中廣泛采用的一種數制。二進制數據是用0和1兩個數碼來表示的數。它的基數為2,進位規則是“逢二進一”,借位規則是“借一當二”,由18世紀德國數理哲學大師萊布尼茲發現。當前的計算機系統使用的基本上是二進制系統

2018-02-28 09:31:06 18768

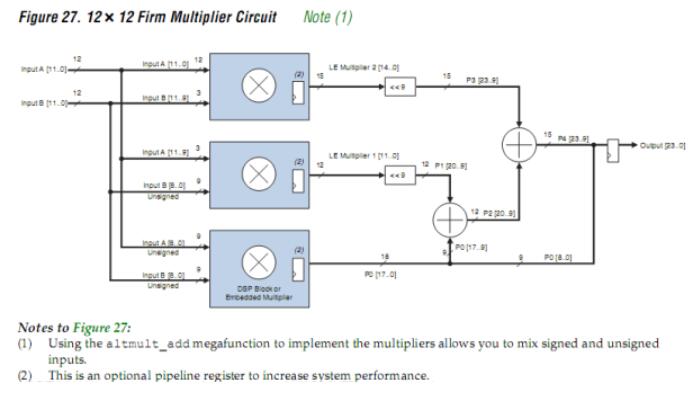

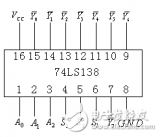

18768 74LS138 為3 線-8 線譯碼器,共有 54/74S138和 54/74LS138兩種線路結構型式,其工作原理如下:當一個選通端(E1)為高電平,另兩個選通端((/E2))和(/E3))為

2017-12-04 15:48:10 761680

761680

74LS138的單片機I/O口擴展 將2片74LS138芯片采用如上圖所示的連接方式,來實現對AT89C51芯片I/O口的擴展。其中,使能端G1選擇高電平,G2b選擇低電

2017-11-29 19:21:48 6001

6001

基于VHDL的EDA實驗---3位二進制計數器

2017-11-08 17:45:53 1

1 乘法器,求模運算部分利用Barrett約減運算,用硬件描述語言進行FPGA設計與實現,避免了除法運算。對于192位的操作數,完成Barrett模乘需要約186個時鐘周期,計算速率可以達到269.17 Mb/s。

2017-11-08 15:18:19 32

32 74LS138 為3 線-8線譯碼器,共有 54LS138和 74LS138 兩種線路結構型式。54LS138為軍用,74LS138為民用。他的工作原理是一下四點。這里還給大家分享74LS138中文資料pdf完整版免費下載。

2017-11-03 15:14:08 58542

58542

用3線—8線譯碼器74LS138和門電路設計1位二進制全減器,輸入為被減數、減數和來自低位的借位;輸出為兩數之差和向高位的借位信號。

2017-10-31 17:15:35 218929

218929

用兩片74LS138設計一個全加器。在考慮到74LS138譯碼器為3 線-8 線譯碼器,共有 54/74S138和 54/74LS138 兩種線路結構型式,其74LS138工作原理為:當一個選通端

2017-10-31 15:53:34 137363

137363

74hc138的邏輯功能和74ls138是一樣的。74hc138是高速CMOS芯片,工作電源電壓為2V - 6V,輸出端驅動電流為正負25mA。74ls138是TTL芯片,工作電源電壓為5V,輸出驅動電流高電平-400微安,低電平8mA。從電源電壓和驅動電流選的74hc138。

2017-10-31 11:19:57 40311

40311

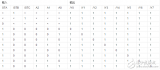

74LS138為3線-8線譯碼器,共有54/74S138和54/74LS138兩種線路結構型式,其74LS138工作原理如下:

當一個選通端(G1)為高電平,另兩個選通端(/(G2A)和/(G2B))為低電平時,可將地址端(A、B、C)的二進制編碼在一個對應的輸出端以低電平譯出。

2017-10-31 11:12:02 46

46 一個自己寫的八位數的乘法器

2016-12-01 15:45:23 15

15 74LS138英文手冊,感興趣的小伙伴們可以瞧一瞧。

2016-11-22 14:35:13 14

14 74LS138 datashee—英版數據手冊,感興趣的可以看看哦。

2016-08-29 18:14:35 7

7 74LS138介紹,關于138譯碼器的引腳,內部結構以及其工作時的情況

2016-04-29 17:14:45 28

28 二進制加法程序【匯編版】二進制加法程序【匯編版】二進制加法程序【匯編版】二進制加法程序【匯編版】

2015-12-29 11:02:06 3

3 實驗目的 1、熟悉Xilinx的ISE 軟件的使用和設計流程; 2、掌握Modelsim仿真軟件的使用方法; 3、用乘法運算符實現一個16*16 乘法器模塊; 4、用IP核實現一個16*16 乘法器模塊; 5、用例化語

2011-05-20 17:00:14 66

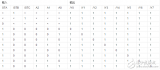

66 本資料有74ls138真值表_74ls138功能表。

2011-03-20 14:25:55 69

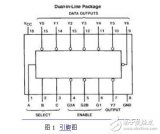

69 74LS138的邏輯功能

三個譯碼輸入端(又稱地址輸入端)A2、A1、A0,八個譯碼輸出端 ,以及三個控制端(又稱使能端) 、 、 。

、 , 是譯碼器的控制輸入端,當

2010-08-26 16:18:52 173

173 變跨導乘法器

這種乘法器現在已經成為一種工業上的標準方法,是應用極為廣泛的優質乘法器。

2010-05-18 16:00:55 999

999

1/4平方乘法器

這種乘法器是根據數學關系設計而成的,因此稱為1/4平方乘法電路,或稱1/4平方乘法器。其

2010-05-18 14:08:10 1652

1652

乘法器的基本概念

乘法器是一種完成兩個互不相關的模擬信號相乘作用的電子器件。理想乘法器的輸出特性方程可由下式表示:

UO

2010-05-18 14:03:59 12929

12929

本的二進制加法/減法器,本的二進制加法/減法器原理

兩個二進制數字Ai,Bi和一個進位輸入Ci相加,產生一個和輸出Si,以及一個進位輸

2010-04-13 11:11:55 5077

5077 二進制電平,什么是二進制電平

在二進制數字通信系統中,每個碼元或每個符號只能是“1”和“0”兩個狀態之一。若將每個碼元可能取的狀態增

2010-03-17 16:51:58 2144

2144 什么是二進制計數器,二進制計數器原理是什么?

計數器是數字系統中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數,還可以實現

2010-03-08 13:16:34 29984

29984 二進制數的運算規則 二進制數之間可以執行算術運算和邏輯運算,其規則簡單,容易實現。 (1) 加法運算規則 0 + 0 = 0 例如:

2009-10-13 16:24:15 21600

21600 二進制編碼和二進制數據

二進制編碼是計算機內使用最多的碼制,它只使用兩個基本符號"0"和"1",并且通過由這兩個符號組成的

2009-10-13 16:22:51 4179

4179 本文在設計實現乘法器時,采用了4-2 和5-2 混合壓縮器對部分積進行壓縮,減少了乘法器的延時和資源占用率;經Xilinx ISE 和Quartus II 兩種集成開發環境下的綜合仿真測試,與用Verilog

2009-09-17 11:13:21 27

27 12位二進制計數器

2009-09-16 15:56:08 5906

5906

74ls138譯碼器內部電路邏輯圖功能表簡單應用

74HC138:74LS138 為3 線-8 線譯碼器,共有 54/74S138和 54/74LS138 兩種線路結構型式,其74LS138工作原理如下:

2009-07-13 12:02:52 47612

47612

二進制

二進制與十進制的區別在于數碼的個數和進位規律有很大的區別,顧名思義,二進制的計數規律為逢二進一,是以2為基數的計數體制。10這個數在二進

2009-04-06 23:48:01 6966

6966

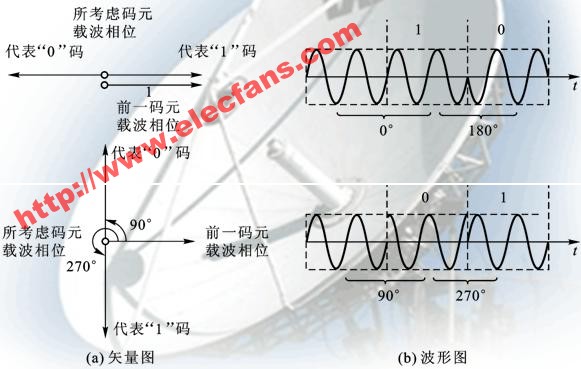

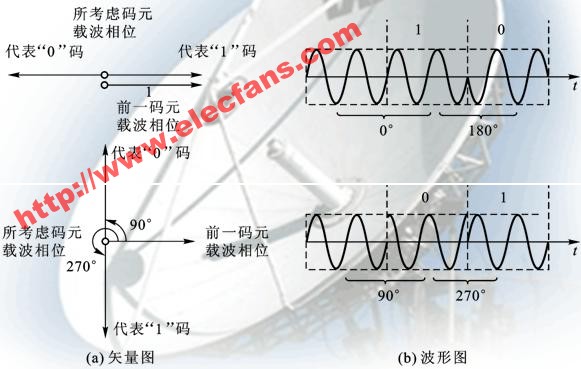

二進制相對調相(二進制差分調相2DPSK)的工作原理

2008-10-21 13:01:35 2932

2932

二進制絕對調相工作原理:二進制絕對調相(二相絕對調相)利用載波不同 位的絕對值來傳遞數字信息。(2BPSK)

2008-10-21 13:00:43 4898

4898

54/742854 位 x4 位并行二進制乘法器(OC,產生低位積)簡要說明:54/74285 為集電極開路的 4 位 x4 位并行二進制乘法器,其主要電特性的典型值如下(具體廠家有可能不是完

2008-03-15 13:07:39 52

52 54/742844 位 x4 位并行二進制乘法器(OC,產生高位積)簡要說明:54/74284 為集電極開路的 4 位 x4 位并行二進制乘法器,其主要電特性的典型值如下(具體廠家有可能不是完

2008-03-15 13:07:07 43

43 74LS274中文資料:

54/742744 位 x4 位并行二進制乘法器(3S)簡要說明:54/74S274 為 4 位 x4 位并行二進制乘法器,其主要電特性的典型值如下(具體廠家有可能不是完

2008-03-15 09:17:25 48

48 74LS261中文資料:54/742612 位 x4 位并行二進制乘法器(鎖存器輸出)簡要說明:54/74LS261 為 2 位 x4 位并行二進制乘法器,其主要電特性的典型值如下(具體廠家有可能

2008-03-15 09:14:51 40

40 74LS138中文資料

2007-12-17 22:36:13 2369

2369 74ls138引腳圖

2007-12-17 22:33:25 171927

171927

4位二進制同步計數器74LS161引腳圖及功能表

4位二進制同步計數器74LS161

2007-11-22 12:51:59 50388

50388

電子發燒友App

電子發燒友App

評論