with reference to axis-X和Flip with reference toaxis-Y,原來在AD19中這兩個(gè)命令沒有設(shè)置快捷鍵,后來設(shè)置完后仍然無法使用X和Y。3.另外在AD13

2019-05-07 20:40:21

一般情況下,通過快捷鍵shift+E進(jìn)行中心的抓取,就能很愉快的解決這一問題;但AD19確行不通。中國(guó)IC交易網(wǎng)中國(guó)ICPDF網(wǎng)經(jīng)過一方小嘗試,可以試試以下的方法:1. 快捷鍵TP進(jìn)入?yún)?shù)設(shè)置的界面,在“System”欄的“General”設(shè)置中,選擇“高級(jí)設(shè)置”。

2019-08-19 11:10:24

請(qǐng)教各位大神,AD19如何放置結(jié)點(diǎn)?

2019-08-06 10:01:40

剛從ad13轉(zhuǎn)到ad19就蒙了,這個(gè)器件上無法敷銅,百度過后未能解決,有沒有遇見相同情況的人?但是其他器件情況正常,如圖3。莫非我封裝畫的有問題?

2020-02-13 22:28:02

),可以導(dǎo)入到PCB中18.多板設(shè)計(jì)里面添加支持FPC(軟板)的功能。18.多板設(shè)計(jì)里面添加支持FPC(軟板)的功能。關(guān)于AD19 ,大家有哪些試用體驗(yàn)? 歡迎跟帖交流和分享!

2018-12-11 19:24:21

ad19畫好板形及板孔后,關(guān)掉文件,然后打開板回的孔消失了,請(qǐng)各位指點(diǎn)。開孔是用快捷鍵T-V-B

2020-11-03 17:39:52

我的封裝定義是頂層,可是畫的焊盤的絲印那些是底層,這樣怎么解決?

2019-05-07 07:35:14

請(qǐng)問有人知道不同封裝的電阻對(duì)應(yīng)的焊盤尺寸大小嗎?

2020-07-29 11:16:47

→1.我在制作奇異焊盤時(shí),依照網(wǎng)上方法繪制不規(guī)則的top/top paste/top solder三層,再放置一個(gè)top layer層的焊盤,在Save. sch中增加此封裝,但是在導(dǎo)入pcb中時(shí)候

2018-08-28 18:12:38

如題,在修改焊盤后xx.pad文件后 再調(diào)用原來用該焊盤做的xx.dra,xx.psm封裝文件 里面的所用的焊盤會(huì)自動(dòng)更新么?或者怎么做能完成更新?望各位大神指點(diǎn)一二。。

2013-12-03 18:08:24

Allegro焊盤和封裝制作.pdf ... Allegro焊盤和封裝制作.pdf ...

2013-05-13 23:13:53

新手小白 這種情況應(yīng)該怎么辦鴨 百度說什么GND換個(gè)port 沒看懂版本AD19 加載了simulate插件

2020-11-11 15:01:04

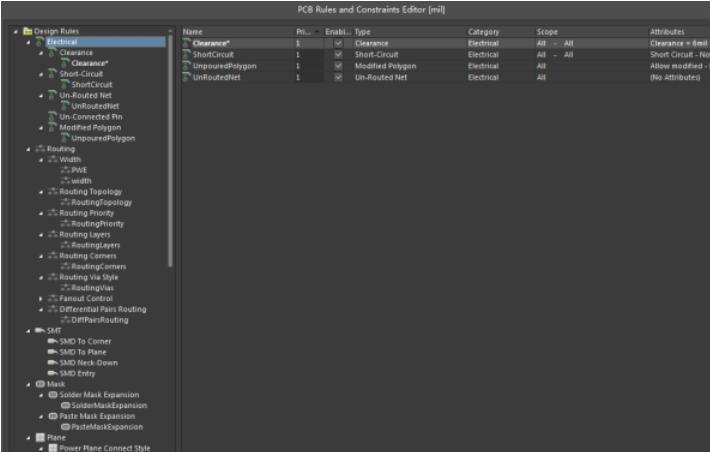

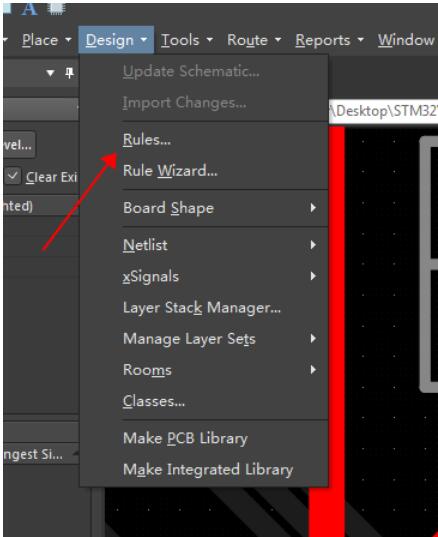

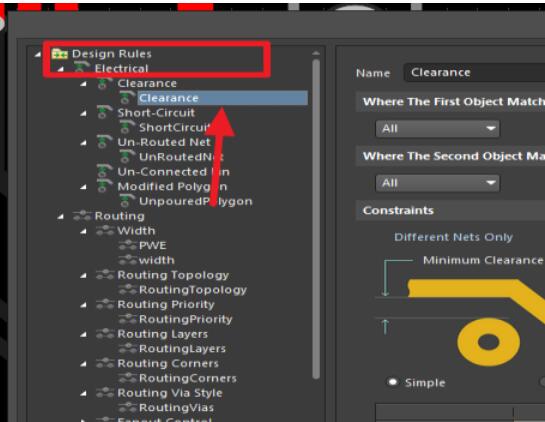

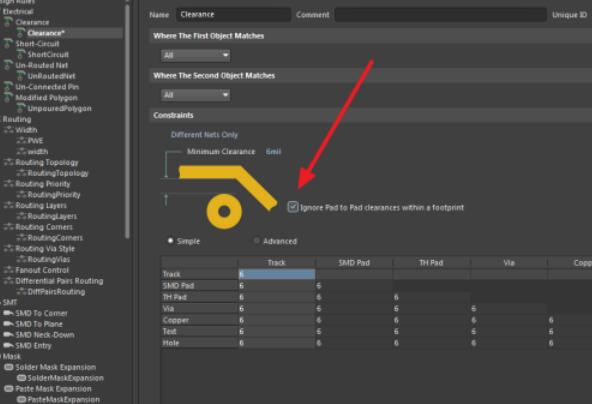

在我們PCB設(shè)計(jì)的時(shí)候,有時(shí)候總會(huì)碰到絲印會(huì)重疊在焊盤上面,那么我們?cè)O(shè)置一個(gè)絲印焊盤的距離的報(bào)錯(cuò)就行了。如果我們絲印一附在焊盤上便會(huì)自動(dòng)的報(bào)錯(cuò),就是提高我們的PCB設(shè)計(jì)效率,我們就以AD19為例,進(jìn)行講解。1. 在設(shè)計(jì)——規(guī)則,或者快捷鍵DR打開我們的規(guī)則約束器:(圖文詳解見附件)

2019-11-18 11:31:01

我們?cè)赑CB設(shè)計(jì)中,不管是高壓板卡爬間距,還是板型結(jié)構(gòu)的要求。我們都需要進(jìn)行挖槽,挖槽就是在設(shè)計(jì)PCB的時(shí)候進(jìn)行挖空處理。那么挖槽就有長(zhǎng)方形,正方形,圓形和異形挖槽。就以AD19為例對(duì)兩種類型的挖槽

2019-11-18 11:24:57

AD19繪制PCB板時(shí),遇到比較尷尬的情況,在布線的過程中發(fā)現(xiàn):出線不能從焊盤的中心出來,都會(huì)強(qiáng)制的從焊盤的旁邊出線,如下圖: 一般情況下,通過快捷鍵shift+E進(jìn)行中心的抓取,就能很愉快

2019-11-01 17:59:31

通常在PADS封裝庫(kù)的編輯中,通過設(shè)定坐標(biāo)+復(fù)制+偏移的方法,可以快速生產(chǎn)新異種封裝,但往往可能涉及焊盤編號(hào)的重排,快速實(shí)現(xiàn)焊盤重編號(hào),特別是40PIN以上的異形焊盤,可以避免對(duì)焊盤逐個(gè)修改所產(chǎn)生額外時(shí)間成本

2019-07-18 07:43:51

剛?cè)腴T,一些基本的知識(shí)都不了解,請(qǐng)問有經(jīng)驗(yàn)的設(shè)計(jì)師。在做常用的PCB元件封裝的時(shí)候,比如管腳是0.6mm,那焊盤中間通孔取0.8mm的樣子(比管腳大0.2mm),那焊盤直徑是不是取1.3mm左右,焊盤的尺寸如何確定,有沒有什么經(jīng)驗(yàn)標(biāo)準(zhǔn)啊?求指導(dǎo)

2014-10-11 12:51:24

在進(jìn)行PCB板設(shè)計(jì)中設(shè)計(jì)PCB焊盤時(shí),就需要嚴(yán)格按照相關(guān)要求標(biāo)準(zhǔn)去設(shè)計(jì)。因?yàn)樵赟MT貼片加工中,PCB焊盤的設(shè)計(jì)十分重要,焊盤設(shè)計(jì)的會(huì)直接影響著元器件的焊接性、穩(wěn)定性和熱能傳遞,關(guān)系著貼片加工

2018-09-25 11:19:47

PCB設(shè)計(jì)中焊盤孔徑與焊盤寬度設(shè)置多少?

2023-04-12 11:34:11

為什么Ubuntu18.04下運(yùn)行run_demo會(huì)報(bào)錯(cuò)呢?Ubuntu18.04下運(yùn)行run_demo報(bào)錯(cuò)怎么辦?

2022-02-16 06:37:47

自己做了個(gè)異形焊盤,三部分組成,1、3是用FILL做的,2是真焊盤。導(dǎo)入PCB后報(bào)規(guī)則錯(cuò)誤,分別是FILL和焊盤短路與距離太近。怎么才能在不修改規(guī)則的情況下,讓這個(gè)異形焊盤不報(bào)錯(cuò)呢

2018-06-12 14:16:06

cadence的原理圖中不畫支架但畫封裝時(shí)要做出來!導(dǎo)網(wǎng)表時(shí)報(bào)錯(cuò)怎么辦啊

2013-09-06 11:13:18

使用cadence自帶的XILINX的fpga的PCB封裝,其焊盤不是表貼焊盤而是通孔焊盤,這是為什么?所用FPGA型號(hào)為spartan6系列xc6slx150csg484,圖一是封裝的top層

2020-08-05 16:08:22

TSOP48封裝的芯片,其Datasheet中,芯片左列管腳外端到右列管腳外端之間的距離是787密耳,我做了個(gè)PCB封裝,管腳焊盤尺寸是65X10密耳,左列管腳焊盤中心到右列管腳焊盤中心之間的距離是不是應(yīng)該也是787密耳?

2009-10-13 13:29:36

`如下圖,為 48-PIN-LQFP 的PCB封裝 ;請(qǐng)教:1. pads中,想給 這個(gè)封裝加個(gè) 熱焊盤,怎么加 ?2. 添加過程是在 PCB decal editor環(huán)境下操作,還是 在PCB環(huán)境

2017-08-23 00:08:19

qfpn封裝的散熱焊盤的soldmask層為什么要按照下圖的來做

2014-11-15 14:51:23

sx1278驅(qū)動(dòng)移植時(shí)報(bào)錯(cuò)怎么辦?如何解決?為什么會(huì)同時(shí)調(diào)用stm32f10x.h和stm32f103xe.h這兩個(gè)頭文件呢?

2022-02-21 07:23:45

`很多人安裝AD19時(shí)候遇到這種問題,點(diǎn)擊不了下一步。今天錄制了一個(gè)安裝AD19的教程,從安裝包,AD19使用,到破解,希望對(duì)大家有所幫助。`

2019-04-08 09:51:40

→Defaults→Pad”在“Proprieties→Designator”中設(shè)置為“1”,即每個(gè)新建的封裝放置的焊盤編號(hào)都會(huì)是“1”了。 圖4-13焊盤編號(hào)默認(rèn)設(shè)置位置示意圖

2021-09-08 16:07:23

電鍍填平當(dāng)BGA封裝的焊盤間距小而無法出線時(shí),需設(shè)計(jì)盤中孔,將孔打在焊盤上面,從內(nèi)層走線或底層走線,這時(shí)的盤中孔需要 樹脂塞孔電鍍填平 ,如果盤中孔不采取樹脂塞孔工藝,焊接時(shí)會(huì)導(dǎo)致焊接不良,因?yàn)?b class="flag-6" style="color: red">焊盤

2023-03-24 11:51:19

請(qǐng)問各位大俠在畫板的時(shí)候,有沒有遇到這樣的問題。自己做的元件封裝,全部焊盤是長(zhǎng)條狀的。在AD10中保存為PcbDoc后,打開是正常的長(zhǎng)條狀焊盤。但保存為.pcb(99se格式)時(shí),打開就變成圓形焊盤

2019-09-30 04:38:33

在使用allegro繪制蛇形天線封裝的時(shí)候,天線本體是焊盤1,饋點(diǎn)是焊盤2疊加在焊盤1上,導(dǎo)致報(bào)錯(cuò)無法生成PSM文件,請(qǐng)問怎么解決呢?

2019-09-25 05:35:28

這是一個(gè)裝鍋?zhàn)衅?b class="flag-6" style="color: red">焊盤, 我自已畫的時(shí)候變成綠色報(bào)錯(cuò),但別人也一樣放置卻不會(huì),檢查設(shè)置也是沒有問題,,這個(gè)應(yīng)該怎樣畫?

2019-08-28 18:24:38

,印制板里面的導(dǎo)線把焊盤連接起來,實(shí)現(xiàn)元器件在電路中的電氣連接。BOM 錯(cuò)料的原因1BOM型號(hào)錯(cuò)誤BOM文件是從EDA軟件里面生成輸出的,在整個(gè)設(shè)計(jì)過程中導(dǎo)致BOM文件里面的數(shù)據(jù)錯(cuò)誤有很多種情況。例如:修改

2023-02-17 10:22:05

尚不能正常使用,我相信很多讀者都會(huì)在這里遇到問題,因?yàn)榘凑漳J(rèn)設(shè)置,Allegro會(huì)去檢查封裝所使用的焊盤即pad文件是否存在于環(huán)境變量所指定的目錄中。例如,在本人所用的電腦上,pad路徑設(shè)置為D

2014-11-12 17:51:40

大家好! 使用LP Wizard制作Allegro插件封裝,在批處理生成焊盤時(shí)報(bào)錯(cuò),并停止封裝建立。Pad_Allegro報(bào)錯(cuò)如下:PADS TACK ERRORS and WARNINGS

2014-07-17 11:29:28

請(qǐng)教一下各位大神,AD19的設(shè)計(jì)規(guī)則中什么地方可以設(shè)置不同層的網(wǎng)格錯(cuò)開,如雙層的網(wǎng)格鋪銅,可以自動(dòng)頂層和底層錯(cuò)開設(shè)計(jì),非常感謝!

2021-06-21 09:24:12

如圖,綠色即為報(bào)錯(cuò),原本這四個(gè)焊盤周圍的敷銅應(yīng)該同周圍的小過孔一樣,與敷銅區(qū)域有間距,我敷銅設(shè)置也是同一網(wǎng)絡(luò)連接的,但看上去似乎沒有避開,該如何設(shè)置?

2022-01-19 15:39:37

按鍵封裝外面這個(gè)焊盤怎么能畫出來呢?

2019-09-30 04:47:01

電阻的封裝給的是電阻的整體大小,并沒有對(duì)焊盤大小有要求。焊盤該如何設(shè)置?

2019-09-27 05:35:58

相同網(wǎng)絡(luò)標(biāo)號(hào)焊盤顯示同色怎么設(shè)置

2019-09-11 02:21:22

運(yùn)用AD19導(dǎo)入PCB之后,進(jìn)行元件布局,之前的版本是在Tool/Component Placement 中有Auto place,但在AD19中沒有找到元件自動(dòng)布局的指令,請(qǐng)問有人知道嘛?

2019-10-02 17:53:18

村田電感 1008(2520)的封裝尺寸,AD畫封裝找不到標(biāo)準(zhǔn)尺寸。請(qǐng)大佬給我兩個(gè)焊盤的尺寸

2019-01-12 12:26:03

求0201排阻封裝庫(kù) 和 圓形焊盤貼片封裝庫(kù)

2014-11-05 16:53:32

變壓器的原理圖有四個(gè)引腳,但是我們老師讓我們畫的封裝只有兩個(gè)焊盤多余兩個(gè)引腳導(dǎo)致pcb載入net時(shí)出錯(cuò),不知道怎么辦,我問了老師,他讓我刪掉多余的引腳的編號(hào),但是我仍然出錯(cuò),我室友刪掉編號(hào)之后就可以了,不知道為什么,弄了幾個(gè)小時(shí)還是這樣,有大神能教教我嗎

2022-04-20 02:17:01

求畫PCB焊盤封裝公式,例如QFN,QFP的IC封裝

2016-08-14 23:30:29

用AD怎么畫環(huán)形焊盤的封裝?

2018-07-27 10:23:55

` 誰來闡述一下電路板焊盤焊掉了怎么辦?`

2020-01-15 15:27:10

請(qǐng)問pcb editor 在畫bga封裝時(shí),在放置焊盤時(shí),當(dāng)放到第12行時(shí),會(huì)莫名其妙的出現(xiàn)多余的線條!在放置下一個(gè)焊盤時(shí),會(huì)出現(xiàn)如下多余的線條請(qǐng)問各位大神,為什么會(huì)出現(xiàn)這種情況?

2017-02-21 21:23:22

常見的模擬麥克風(fēng)的封裝有一個(gè)圓環(huán)焊盤,但實(shí)際上圓環(huán)不是焊盤,網(wǎng)上給出的一般是環(huán)形的line或則環(huán)形的敷銅,然后在其里面放置一個(gè)小的焊盤,但在實(shí)際pcb走線時(shí),這個(gè)圓環(huán)就會(huì)報(bào)錯(cuò),如何解決,或則怎么樣畫這種封裝才對(duì)

2022-01-19 16:20:36

我是Allegro的新手,也學(xué)習(xí)了Allegro的教程,在教程里,我看到每次做封裝時(shí)都要先做焊盤,那我能不能不做焊盤而直接用Allegro中自帶的焊盤來元件的封裝嗎?有請(qǐng)高人請(qǐng)教。

2013-01-16 08:43:48

借用別人的問題描述:AD19的panels面板中沒有l(wèi)ibrarys選項(xiàng)怎么添加刪除可用庫(kù)?在AD19屏幕右下角的panels面板-----彈出的面板類型中只有components元件面板,沒有以前

2019-12-01 23:17:21

請(qǐng)教大神固件編譯報(bào)錯(cuò)了該怎么辦呢?

2021-12-28 06:27:56

請(qǐng)教大神固件編譯報(bào)錯(cuò)了該怎么辦呢?

2022-03-29 19:15:23

AD19的panels面板中沒有l(wèi)ibrarys選項(xiàng)怎么添加刪除可用庫(kù)?在AD19屏幕右下角的panels面板-----彈出的面板類型中只有components元件面板,沒有以前版本的librarys庫(kù)面板。如果添加/刪除可用庫(kù)?

2019-03-06 05:14:01

焊盤間距比差分規(guī)則的間距大,差分線走不出來,怎么辦?

2019-09-10 23:04:40

求大佬幫助,Allgreo 布置焊盤時(shí)無法預(yù)覽。按照網(wǎng)上教程在setup=〉user preference=>Paths=>library=〉padpath/devpath

2018-07-27 17:07:58

D19很難從焊盤中間出線是怎么回事?

2019-03-20 07:35:04

PCB線寬,焊盤大小報(bào)錯(cuò),怎么設(shè)置啊?還有,即使元器件重疊,也不報(bào)錯(cuò),誒,大神,指點(diǎn)迷津吧 PCB報(bào)錯(cuò).docx (137.02 KB )

2019-02-25 00:56:17

我看TF卡座封裝有4個(gè)焊盤是固定TF卡座的,請(qǐng)問這幾個(gè)焊盤需要接地嗎?如果需要,能否與TF卡的VSS共地?謝謝~

2019-01-21 06:15:18

在allegro制作插件通孔封裝時(shí),只設(shè)置正焊盤,不設(shè)置熱風(fēng)焊盤和隔離焊盤,對(duì)多層pcb板有影響嗎?

2019-09-16 10:27:51

請(qǐng)問不規(guī)則焊盤如何做PCB封裝啊是不是鋪銅.還是添置啊如

2010-05-21 23:08:58

做BGA封裝焊盤要做阻焊嗎?要選那個(gè)?

2019-07-22 01:44:50

這個(gè)焊盤報(bào)錯(cuò)怎么取消

2019-07-11 05:35:22

本文檔的主要內(nèi)容詳細(xì)介紹的是Altium Designer教程之AD19軟件安裝免費(fèi)下載。

2018-12-19 08:00:00 0

0 在將原理圖通過網(wǎng)表導(dǎo)入或者直接導(dǎo)入的方式導(dǎo)入到PCB中,我們有時(shí)候可以看到同封裝的焊盤在進(jìn)行綠色報(bào)錯(cuò),一般情況下是多管腳的IC元器件報(bào)錯(cuò),例如可以看到如圖5-15所示的報(bào)錯(cuò)情況。遇到這樣的情況我們應(yīng)該如何處理?

2020-09-21 15:22:46 18961

18961

AD19中多選操作修改器件所在層教程

2021-08-05 16:44:45 0

0 AD19 PCB中,添加3D封裝模型,模型必須時(shí) Step 格式

2021-08-16 11:19:56 0

0 AD19制作stm32最小系統(tǒng)板本人小白,如有制作步驟有所不妥還請(qǐng)大佬指出。首先明確制作目標(biāo):運(yùn)用AD19的軟件設(shè)計(jì)出一塊STM32F103C8T6的最小系統(tǒng)板。一.建立工程。1.我們先建立

2021-11-17 18:21:01 27

27 AD19設(shè)計(jì)規(guī)則設(shè)置

2022-08-08 15:31:31 7

7

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論