技術前沿:先進封裝之硅通孔TSV和玻璃通孔TGV

隨著晶圓代工制程不斷縮小,摩爾定律逼近極限,先進封裝是后摩爾時代的必然選擇。其中,利用高端封裝融合最新和成熟節點,采用系統封裝(SiP)和基于小芯片的方法,設計和制造最新的SoC產品已經成為主要的技術路徑。2.5D/3D封裝正在加速3D互連密度的技術突破,TSV及TGV的技術作為2.5D/3D封裝的核心技術,越來越受到重視。

一、先進封裝技術越來越重要

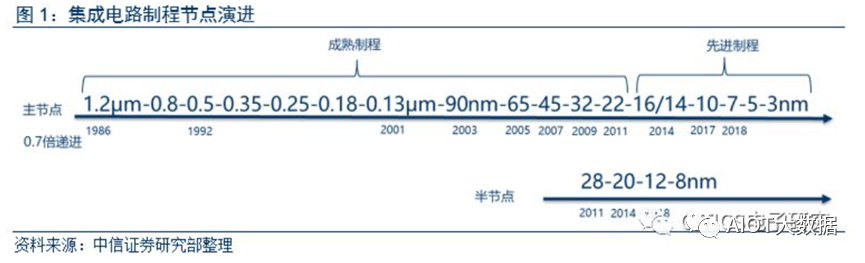

摩爾定律指引集成電路不斷發展。摩爾定律指出:“集成電路芯片上所集成的電路的數目,每隔18-24個月就翻一倍;微處理器的性能提高一倍,或價格下降一半。”根據摩爾定律,制程節點以0.7倍(實際為根號2的倒數)遞減逼近物理極限,從1μm、0.8μm、0.5μm、0.35μm、0.25μm、0.18μm、0.13μm、90nm、65nm、45nm、32nm、22nm、16nm、10nm、7nm,一直發展到未來的5nm、3nm,事實上90nm節點以前特征尺寸完全對應柵極長度,自65nm開始各廠商節點名稱的定義越來越模糊,已不能完全對應器件的物理尺寸。目前14nm、10nm的節點名稱大致對應柵極長度的一半。

遵循摩爾定律,縮小晶體管尺寸,依舊可以提升產品性能。但是高昂的開發費用和資本支出導致單個晶體管成本不像之前隨著性能的提升而下降,開發更先進的制程已經不再經濟。另一方面摩爾定律已經接近極限。2017年10nm制程已經發展到量產的階段,非常接近FinFET工藝物理極限5nm。

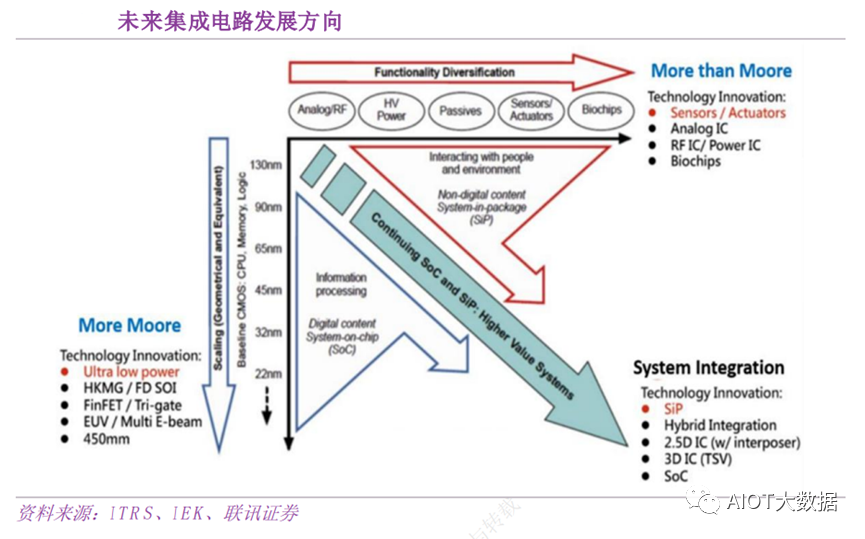

在這種情況下,集成電路產業將走向何方,產業界和學術界給出了比摩爾定律更為多元化的答案:MoreMoore(深度摩爾)、MorethanMoore(超越摩爾)、BeyondCMOS將是未來的發展方向。

深度摩爾是在現有硅基CMOS基礎上,在器件結構、溝道材料、連接導線、高介質金屬柵、架構系統、制造工藝等方面進行創新研發,沿著摩爾定律進行升級,延續摩爾定律(18個月左右晶體管數量翻番)的生命。同時更加注重功耗的降低。FinFET技術、EUV光刻是典型代表。業界認為5nm將會是硅基CMOS技術的物理極限。

超越摩爾側重于根據應用場景來實現芯片功能的多樣化。這可以通過三條路徑來實現:優化算法和電路設計;多個功能模塊封裝于一個芯片中;開發新功能芯片。因此封裝將會發揮越來越重要的作用。

BeyondCMOS是指打破硅基晶體管結構和材料限制,研發全新的晶體管來取代硅基CMOS。新的器件要具有高性能、低功耗、可接受的制造成本、足夠穩定以及適合于大規模制造等特性。潛在的技術主要有:隧穿FET(TunnelingFET,TFET)、Nano-electromechanicalSwitch(NEMS)、單電子晶體管(SingleElectronTransistor,SET)、量子元胞自動機(QuantumCellularAutomata,QCA)、AtomicSwitch、自旋FET(SpinFET)、石墨烯FET(GrapheneFET)、碳納米管FET(CarbonNanotubeFET)、納米線FET(NanowireFET)等。

此外,半導體產業也將逐漸從技術驅動轉變為應用驅動。目前移動產品仍是半導體產業主要的推動力,其朝小尺寸、多功能、高速化發展,帶動先進封裝技術導入。未來物聯網、5G、人工智能、汽車電子、AR/VR、云計算等將會興起,市場驅動力將多元化,對產品多樣化也提出了需求。先進封裝是滿足不同應用需求的重要手段。隨著晶圓代工制程不斷縮小,摩爾定律逼近極限,先進封裝是后摩爾時代的必然選擇,包括倒裝、晶圓級封裝、扇出型封裝、3D封裝、系統級封裝等。

二、封測技術及發展方向

半導體的生產過程可分為晶圓制造工序(WaferFabrication)、封裝工序(Packaging)、測試工序(Test)等幾個步驟。其中晶圓制造工序為前道(FrontEnd)工序,而封裝工序、測試工序為后道(BackEnd)工序。封裝是指將生產加工后的晶圓進行切割、焊線塑封,使電路與外部器件實現連接,并為半導體產品提供機械保護,使其免受物理、化學等環境因素損失的工藝。測試是指利用專業設備,對產品進行功能和性能測試,測試主要分為中測和終測兩種。

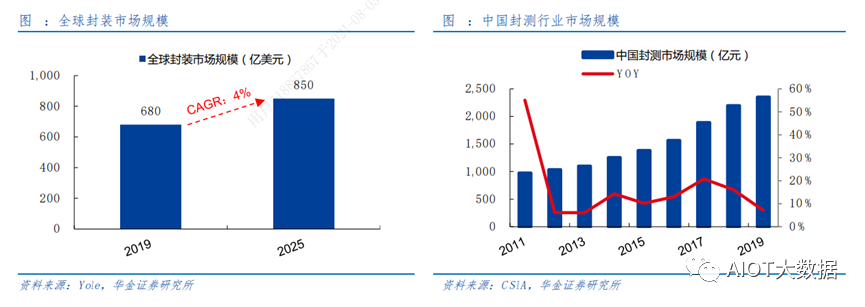

根據Yole的數據,全球封測行業市場規模保持平穩增長,預計從2019年的680億美元增長到2025年的850億美元,年均復合增速約4%。根據中國半導體行業協會的數據,中國封測行業市場規模從2011年的976億元增長到了2019年的2350億元,年均復合增速約11.6%,顯著高于全球增速。

1、封測生產流程

晶圓代工廠制造完成的晶圓在出廠前會經過一道電性測試,稱為晶圓可接受度測試(WaferAcceptanceTest,WAT),WAT測試通過的晶圓被送去封測廠。封測廠首先對晶圓進行中測(ChipProbe,CP)。由于工藝原因會引入各種制造缺陷,導致晶圓上的裸Die中會有一定量的殘次品,CP測試的目的就是在封裝前將這些殘次品找出來,縮減后續封測的成本。在完成晶圓制造后,通過探針與芯片上的焊盤接觸,進行芯片功能的測試,同時標記不合格芯片并在切割后進行篩選。CP測試完成后進入封裝環節,封裝工藝流程一般可以分為兩個部分,用塑料封裝之前的工藝步驟稱為前段操作,在成型之后的工藝步驟稱為后段操作。基本工藝流程包括晶圓減薄、晶圓切割、芯片貼裝、固化、芯片互連、注塑成型、去飛邊毛刺、上焊錫、切筋成型、打碼等。因封裝技術不同,工藝流程會有所差異,且封裝過程中也會進行檢測。封裝完成后的產品還需要進行終測(FinalTest,FT),通過FT測試的產品才能對外出貨。

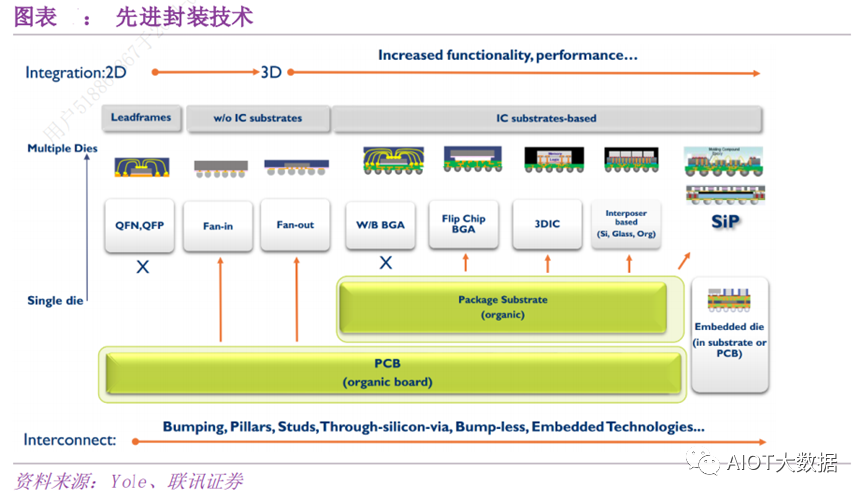

2、封裝技術不斷演進

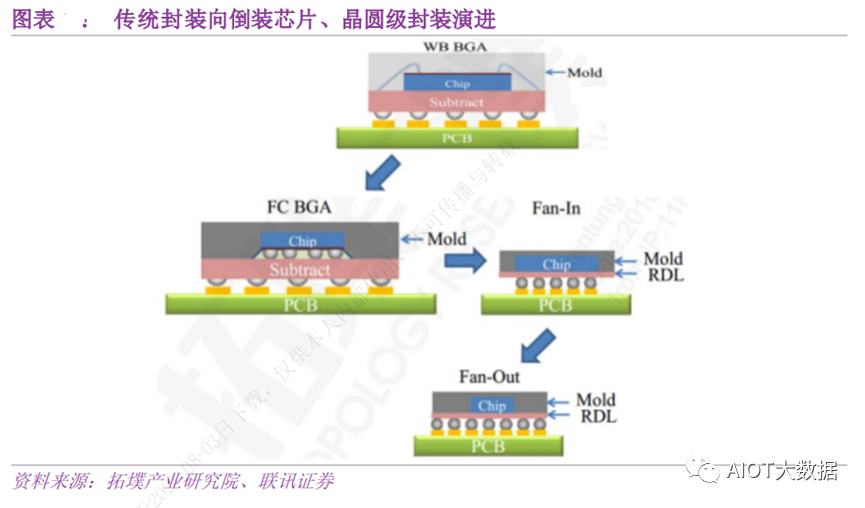

封裝技術正逐漸從傳統的引線框架、引線鍵合向倒裝芯片、硅通孔、嵌入式封裝(ED,EmbeddedDiePackage)、扇入/扇出型晶圓級封裝、SiP封裝、系統級封裝(SoP,SystemonPackage)等先進封裝技術演進。芯片的尺寸繼續縮小,引腳數量不斷增加,集成度持續提升。

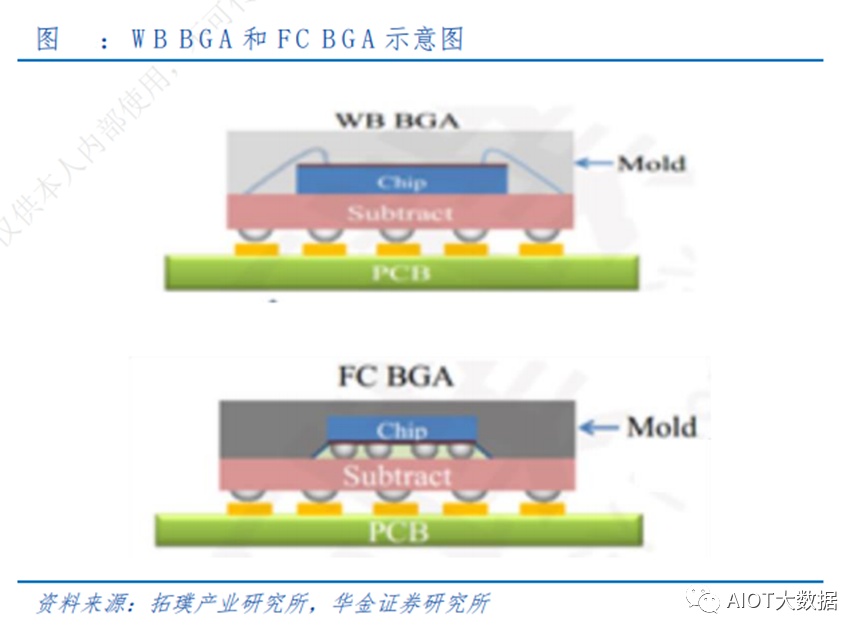

倒裝芯片與傳統的引線鍵合技術的區別在于前者將芯片面朝下,與基板直接通過焊球連接,不再需要引線,芯片與外部電路的距離縮短。芯片I/O密度提高、尺寸縮小、電氣性能改善。

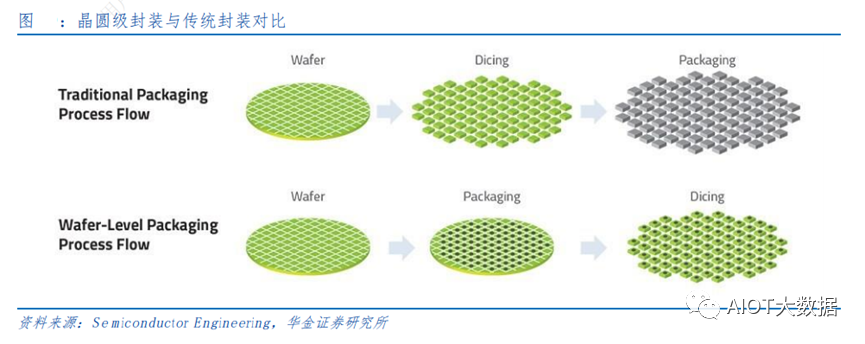

晶圓級封裝通常直接在晶圓上進行大部分或全部封測工藝,再切割成單顆芯片。再分布層(RDL,RedistributionLayer)與凸塊(Bump)技術為其I/O布線的一般選擇,由此無需使用IC載板,從而降低了厚度和成本。

晶圓級封裝可以實現較小尺寸封裝,如:芯片尺寸封裝(CSP,ChipScalePackage)。由于引腳全部位于芯片下方,I/O數受到限制,該類型一般又稱為晶圓級芯片尺寸封裝(WLCSP,WaferLevelChipScalePackage)或扇入型晶圓級封裝(Fan-InWLP)。目前多用于低引腳數消費類芯片。

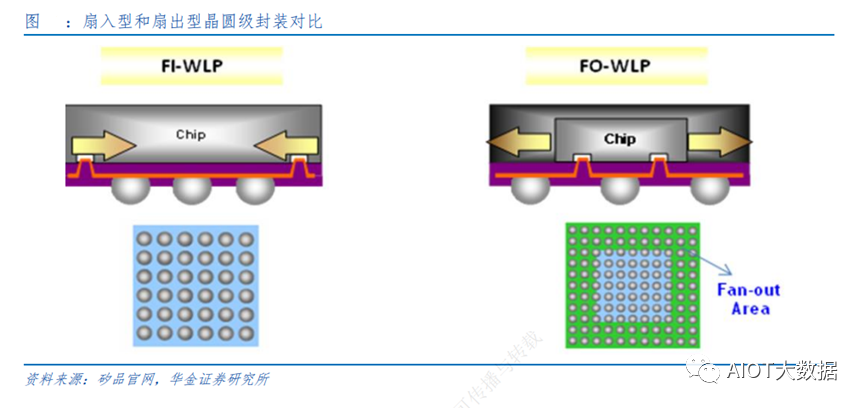

WLP可分為扇入型晶圓級封裝(Fan-InWLP)和扇出型晶圓級封裝(Fan-OutWLP)兩大類。扇入型直接在晶圓上進行封裝,封裝完成后進行切割,布線均在芯片尺寸內完成,封裝大小和芯片尺寸相同;扇出型則基于晶圓重構技術,將切割后的各芯片重新布置到人工載板上,芯片間距離視需求而定,之后再進行晶圓級封裝,最后再切割,布線可在芯片內和芯片外,得到的封裝面積一般大于芯片面積,但可提供的I/O數量增加。

隨著I/O數目增加,焊球間距不斷減小。持續降低焊球間距將會導致下游PCB制造成本增加。扇出型晶圓級封裝(Fan-OutWLP)應運而生。

扇出(FanOut,FO)是相對扇入而言,“扇入”只能向內走線,而在扇出型封裝中,既可以向內走線,也可以向外走線,從而可以實現更多的I/O,以及更薄的封裝。目前量產最多的是晶圓級扇出型產品。

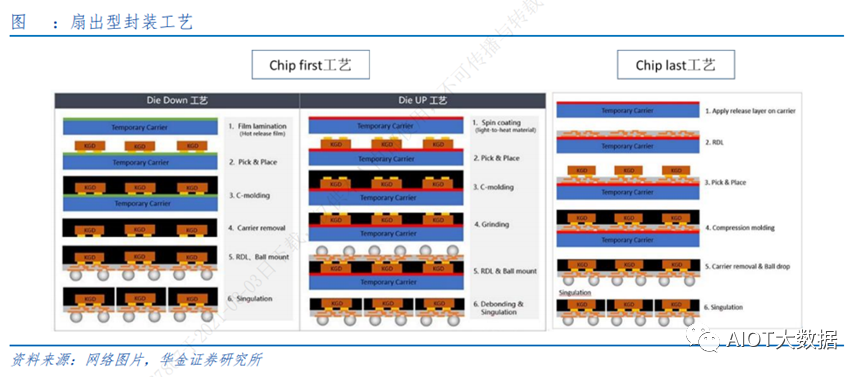

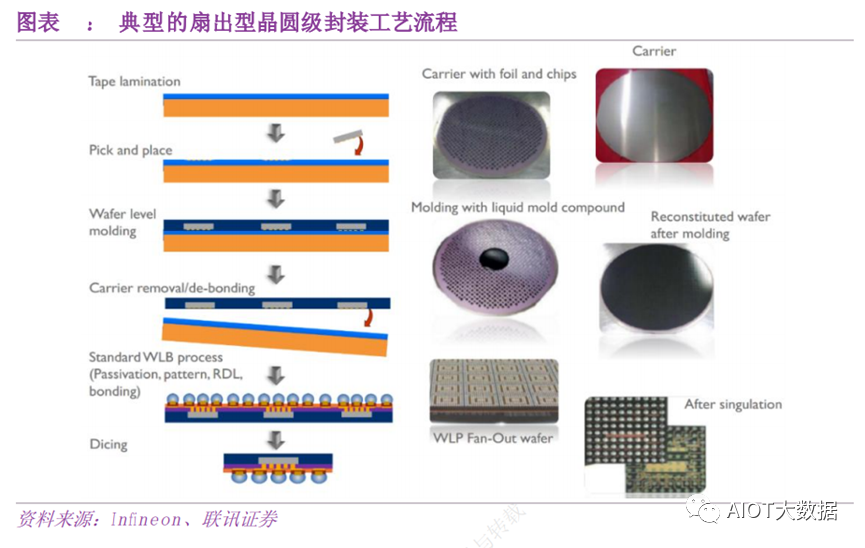

扇出型封裝工藝主要分為Chipfirst和Chiplast兩大類,其中Chipfirst又分Diedown和Dieup兩種。

扇出型封裝生產工藝的關鍵步驟包括芯片放置、包封和布線。芯片放置對速度和精度的要求很高,放置速度直接決定生產效率,從而影響制造成本;放置精度也是決定后續布線精度的關鍵性因素。包封需要對包封材料進行填充和加熱,這一過程不僅可能導致已放置好的芯片發生移位,還有可能因包封材料與芯片的膨脹系數的不同而造成翹曲,這兩者都會影響后續的布線環節。布線成功率是決定最終封裝成品率的關鍵因素,另一方面,布線設備是整個生產設備中最昂貴的,對制造成本的影響很大。

Fan-Out是指通過再分布層將I/O凸塊擴展至芯片周邊,在滿足I/O數增大的前提下又不至于使焊球間距過小而影響PCB工藝。Fan-Out封裝是近期先進封裝技術中的熱門話題。臺積電的InFO(IntegratedFanOut)封裝技術用于iPhone處理器。

扇出型晶圓級封裝的優勢在于縮小芯片尺寸,降低成本(無需載板),散熱、能耗及性能方面較倒裝也有改善。工藝上也面臨著加工過程中翹曲、裸晶在載板上的位置精度、裸晶與載板界面處的平整性、多芯片封裝等問題。

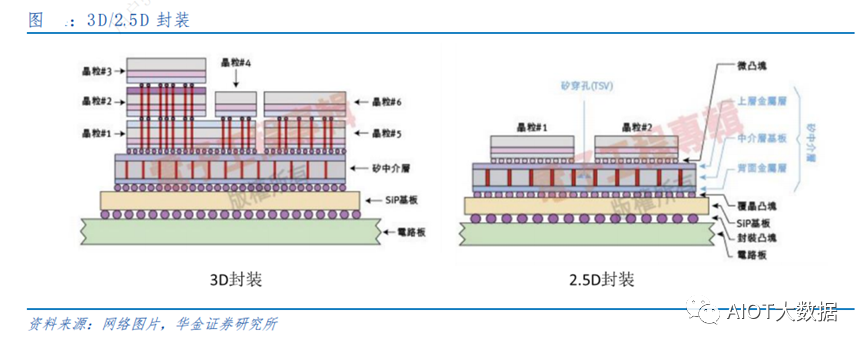

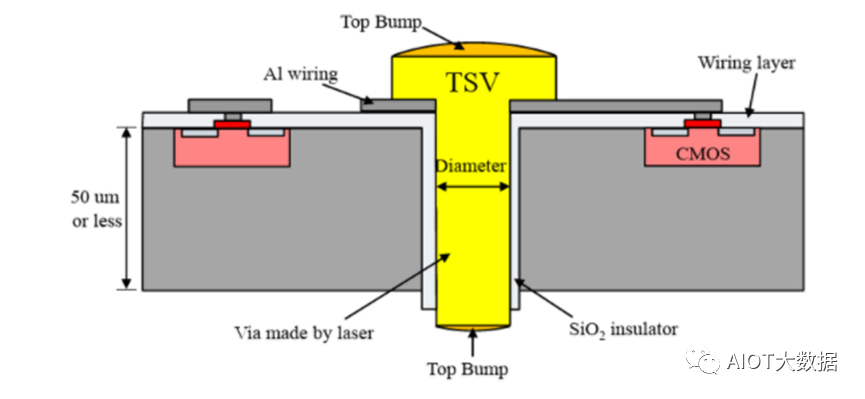

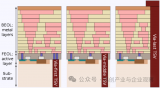

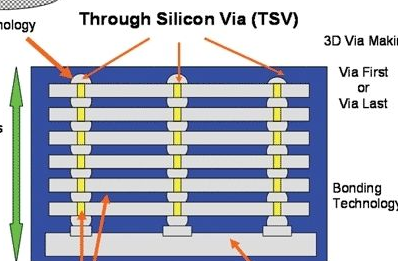

硅通孔技術(TSV)是指在晶圓片上打孔,在孔中填充導電材料實現芯片之間、芯片與外部之間互聯的技術,被認為是目前半導體行業最先進的技術之一。硅通孔技術具有互連距離短、集成度高的優點,能夠使芯片在三維空間堆疊密度最大,并提升芯片性能、降低功耗、縮小尺寸。該技術是實現異質集成的重要手段,未來將廣泛的用于2.5D/3DIC。

3D封裝又稱為疊層芯片封裝技術,是指在不改變封裝體尺寸的前提下,在同一個封裝體內于垂直方向疊放兩個以上芯片的封裝技術,它起源于快閃存儲器(NOR/NAND)及SDRAM的疊層封裝,可以實現不同類型芯片的異質集成,目前在存儲芯片上已有較多應用。

3D封裝可采用凸塊或硅通孔技術(ThroughSiliconVia,TSV),TSV是利用垂直硅通孔完成芯片間互連的方法,由于連接距離更短、強度更高,能實現更小更薄而性能更好、密度更高、尺寸和重量明顯減小的封裝,而且還能用于異種芯片之間的互連。

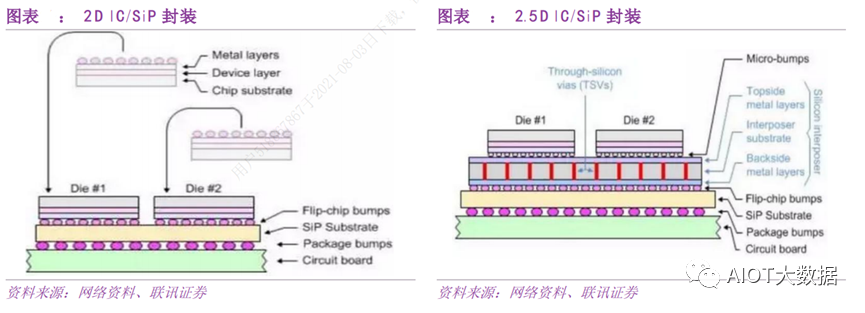

2.5D封裝是在基板和芯片之間放一個硅中間層,這個中間層通過TSV連接上下部分。

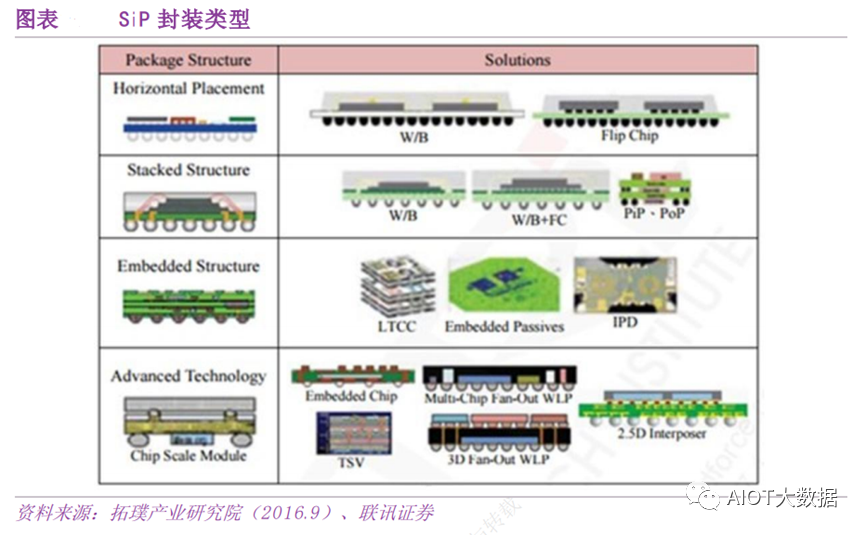

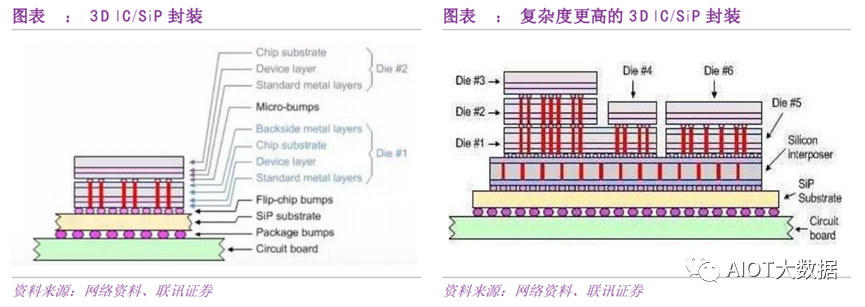

根據國際半導體路線組織(ITRS,International Technology Roadmapfor Semiconductors)的定義,SiP是對不同芯片進行并排或疊加的封裝方式。疊加的芯片可以是多個具有不同功能的有源電子元件與/或無源器件,也可以是MEMS或者光學器件。封裝在一起之后成為可以實現一定功能的系統。

相對簡單的SidebySide的多芯片模組(MCM,Multi-chipModule)技術(2DPackage)、更復雜的多芯片封裝(MCP,Multi-chipPackage)技術、芯片堆疊(StackDie)技術等均可以用來構建集成多種功能的SiP系統(2.5D/3DIC)。SiP可以有效突破SoC在整合芯片過程中的限制,大幅降低設計端和制造端成本,同時具備客制化的靈活性。SiP在超越摩爾的發展路徑中具有十分重要的地位。

臺積電推出的InFO和CoWoS(Chip-on-Wafer-on-Substrate)屬于2.5DIC封裝。該技術是把不同的芯片集成在一塊硅載板(siliconinterposer)上,并在載板上布線實現互連。CoWoS針對高端市場,連線數量和封裝尺寸都比較大。InFO針對性價比市場,封裝尺寸較小,連線數量也比較少。2.5D比3DIC封裝成本更低,但是堆疊芯片的3D封裝比同樣的SiP系統的2.5D封裝尺寸更小。此外堆疊芯片還可以帶來功耗降低、傳輸速率提升等性能方面的改善。

SoC(系統級芯片,System-on-a-Chip)與SiP的區別在于SoC的集成是從晶圓片上制作出來,而SiP的集成是將不同的芯片或裸晶(Die)封裝在一起。目前高端數字工藝(例如16nmFinFET)用于模擬和射頻模塊并不適合。首先高端工藝的額定電源電壓很低,導致模擬/射頻模塊設計非常困難。其次高端工藝的掩模制造成本非常高,而模擬/射頻模塊的晶體管密度遠低于數字模塊,使用高端工藝制造模擬/射頻模塊并不劃算。采用SoC方式集成研制難度大、開發時間長、制造成本高。因此采用先進封裝技術將高端工藝制造的數字模塊,比較成熟的工藝來實現模擬/射頻模塊,用硅通孔等技術實現模塊間互連,封裝在一起形成SiP系統,可以加快開發速度,制造低成本和高集成的芯片。

3、先進封裝市場規模

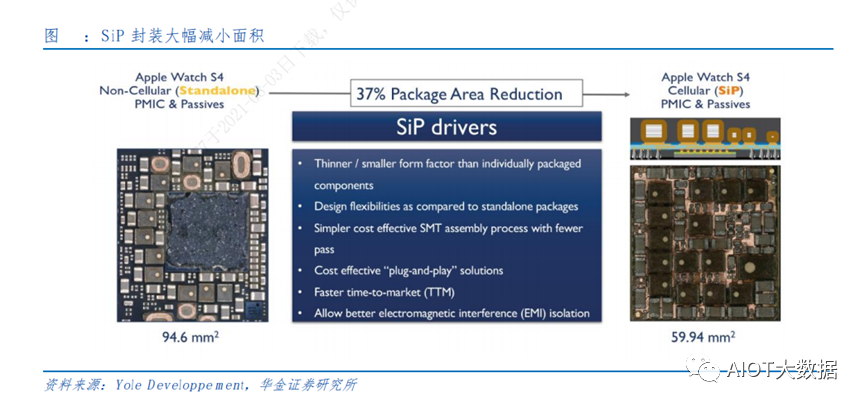

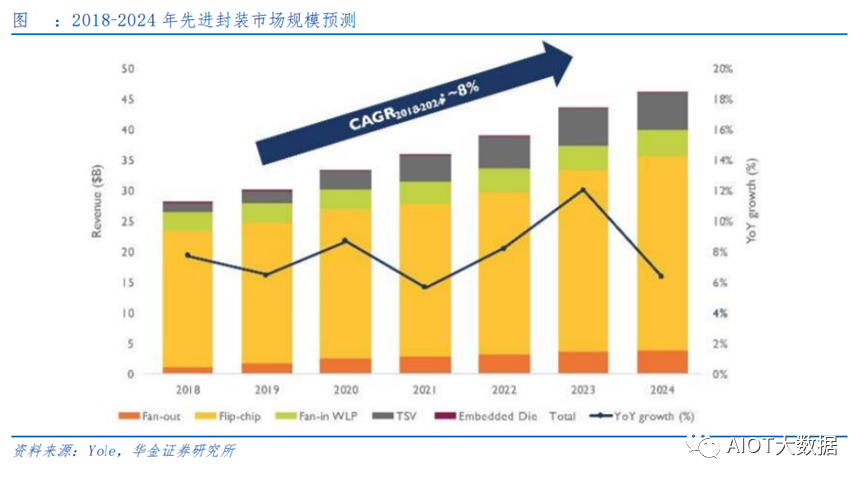

摩爾定律的放緩、異質集成和各種大趨勢(包括5G、AI、HPC、物聯網等)推動著先進封裝市場強勢發展。根據Yole的數據,2019年全球先進封裝市場規模約290億美元,預計2025年增長到420億美元,年均復合增速約6.6%,高于整體封裝市場4%的增速和傳統封裝市場1.9%的增速。

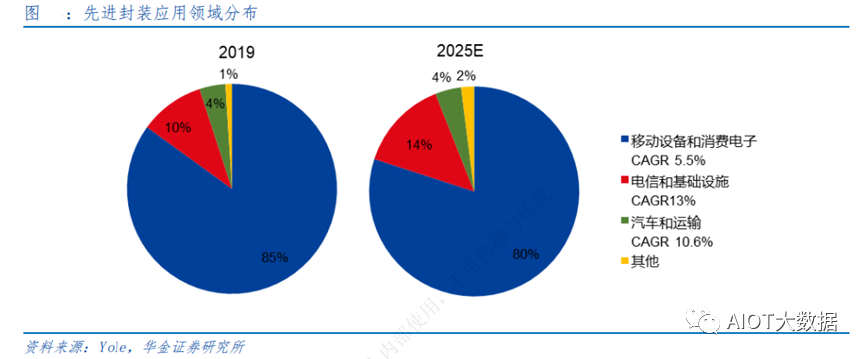

從下游應用市場來看,移動設備和消費電子對集成度要求高,是先進封裝最大的細分市場,2019年占比達85%,2019-2025的CAGR為5.5%,略低于整體增速,2025年將占先進封裝市場的80%。電信和基礎設施是先進封裝市場中增長最快的細分市場,CAGR約為13%,市場份額將從2019年的10%增至2025年的14%。汽車與運輸細分市場在2019年至2025年期間將以10.6%的CAGR增長,到2025年達到約19億美元,但其在先進封裝市場中所占的份額仍將持平,約4%。

從技術分類來看,3D堆疊封裝、嵌入式芯片封裝、扇出型封裝在2019年到2025年的增速更高,CAGR分別為21%、18%、16%。扇出型技術進入移動設備、網絡和汽車領域;3D堆疊技術進入AI/ML、HPC、數據中心、CIS、MEMS/傳感器領域;嵌入式芯片封裝進入移動設備、汽車和基站領域。

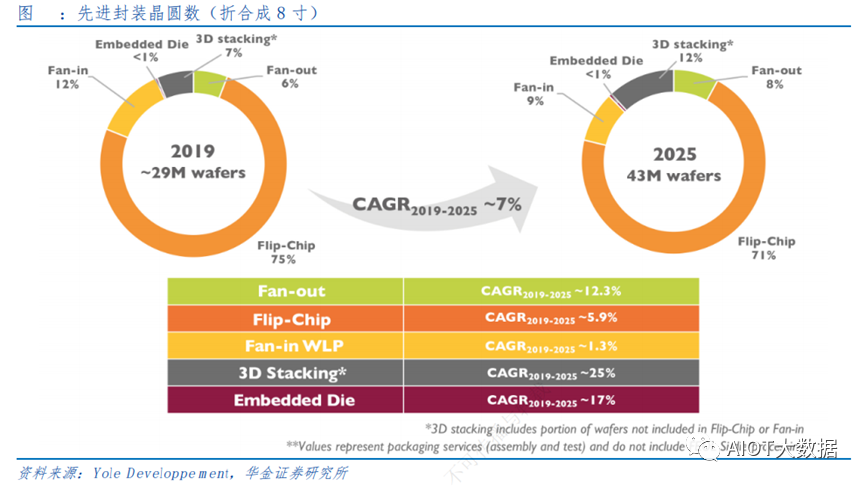

從晶圓數來看,2019年約2900萬片晶圓采用先進封裝,到2025年增長為4300萬片,年均復合增速為7%。其中倒裝技術占比最高,3D封裝增速最快。

三、硅通孔技術(TSV)

TSV互連具有縮短路徑和更薄的封裝尺寸等優點,被認為是三維集成的核心技術。

TSV結構如下圖所示,在硅板上面有加工完成的通孔;在通孔內由內到外依次為電鍍銅柱、絕緣層和阻擋層。絕緣層的作用是將硅板和填充的導電材料之間進行隔離絕緣,材料通常選用二氧化硅。由于銅原子在TSV制造工藝流程中可能會穿透二氧化硅絕緣層,導致封裝器件產品性能的下降甚至失效,一般用化學穩定性較高的金屬材料在電鍍銅和絕緣層之間加工阻擋層。最后是用于信號導通的電鍍銅。

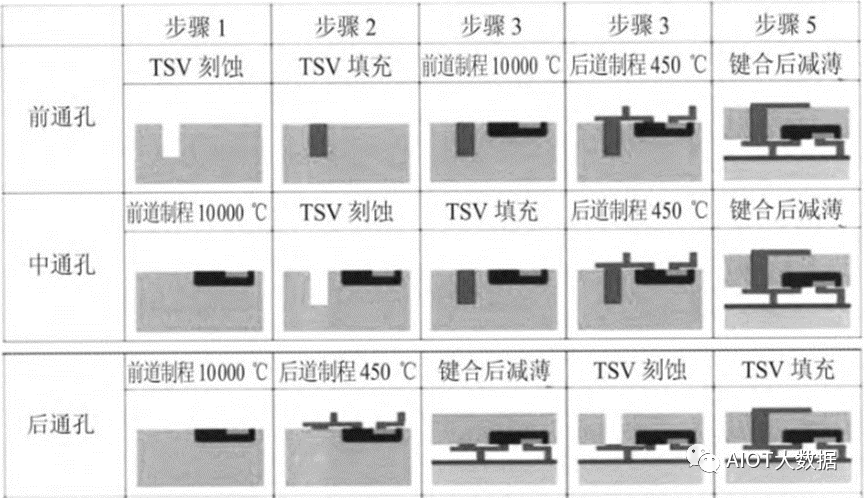

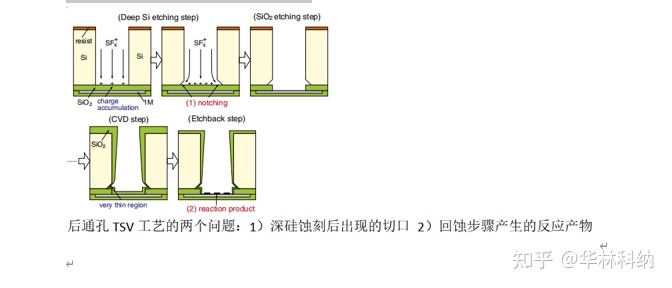

在三維集成中TSV技術可分為三種類型:在CMOS工藝過程之前在硅片上完成通孔制作和導電材料填充的是先通孔技術;而中通孔,在CMOS制程之后和后端制程(BEOL)之前制作通孔。最后一種后通孔技術是在CMOS工藝完成后但未進行減薄處理時制作通孔。最終技術方案的選擇要根據不同的生產需求。

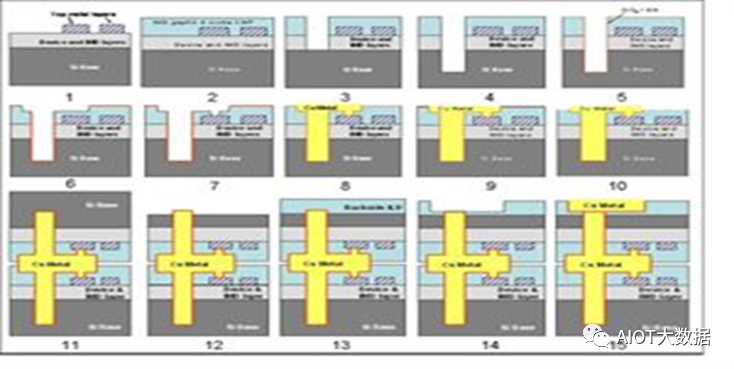

1、TSV制造的工藝流程

TSV制造的工藝流程舉例如下:

步驟1:首先在晶圓上制作IC組件(Devices)。

步驟2:使用化學機械研磨(CMP)制程,將氧化物(Oxide)進行平坦化。

步驟3:蝕刻介電堆積層(DielectricStack)。

步驟4:將硅蝕刻達深度4~9μm。

步驟5:沉積氧化物(Oxide)和氮化物(SiN)層,以作為阻障層(BarrierLayer)及鈍化層(PassivationLayer)。

步驟6及7:制作溝渠(Trench)和導孔(Via),以作為晶圓間之接合(Bonding)使用。

步驟8及9:沉積Ta或TaN阻障層(BarrierLayer),銅晶種層(CopperSeedLayer),接著進行電鍍銅以填充導孔(ViaFilling),使用化學機械研磨(CMP)制程,去除多余之Ta層及銅,此時以完成晶圓后段導線制程(BackendoftheLine;BEOL),包括結合鋁與銅導線層。

步驟10:在銅墊上沉積無電鍍金屬層(ElectrolessMetalDeposition),或去除介電層(DielectricLayer),以形成晶圓對晶圓(WafertoWafer)之接合墊。

步驟11:制作銅對銅(CoppertoCopper)之熱擴散接合(ThermalDiffusionBonding)。

步驟12:使用化學機械研磨(CMP)及研磨(Grinding)方式,將上層晶圓進行薄化(Thinning),并以化學蝕刻法(ChemicalEtching)去除12μm厚度的硅。

步驟13:使用PE-CVD沉積氧化物于薄化晶圓之背面,如此可防止上層晶圓因進行整合堆棧另一片晶圓時,所造成硅之污染。

步驟14:進行氧化層蝕刻,以形成溝渠(Trench),接著沉積銅,以作為導線連接之使用。步驟15:形成銅墊(CopperPad),以作為上層晶圓進行晶圓堆棧之接合點。

2、TSV制作流程中關鍵技術

2.1TSV刻蝕

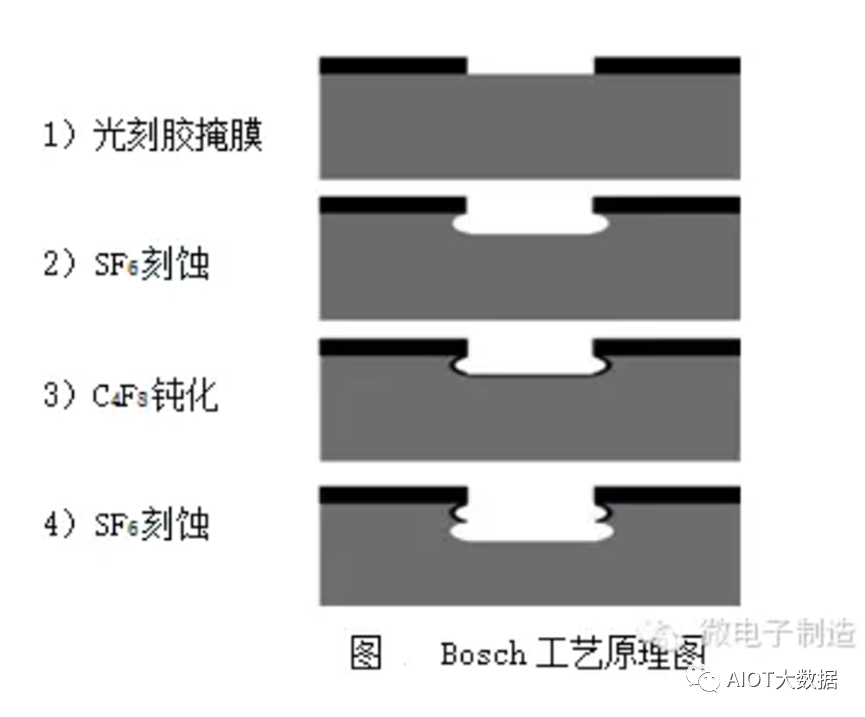

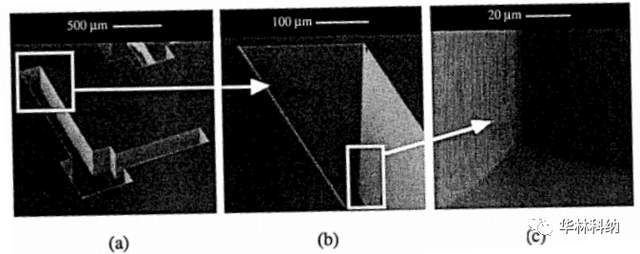

TSV刻蝕是三維集成的關鍵技術,并且目前深硅刻蝕首選技術為干法刻蝕或稱博世刻蝕。博世刻蝕工藝的刻蝕速率高達5~10μm/min,對光刻膠的選擇性為50~100,對氧化物掩膜的刻蝕率高達200。博世工藝包括以下流程:(1)利用六氟化硫(SF6)作為蝕刻劑進行硅刻蝕;(2)填充八氟環丁烷(C4F8)氣體,以產生良好的鈍化膜來保護刻蝕出的側壁;(3)用定向離子進一步刻蝕六氟化硫(SF6)等離子體中的鈍化層和硅層。然后,使用O2和Ar等離子體清洗鈍化層。然而,這種工藝造成側壁缺口粗糙,可能會造成接下來的步驟出現差錯,引發漏電和可靠性問題。在深硅刻蝕中,側壁粗糙度受刻蝕和鈍化到兩個流程的影響。側壁粗糙會增大TSV的空隙,進而影響到絕緣層、阻擋層和銅種子層的覆蓋范圍。因此,隨著TSV尺寸的減小,側壁糙度需要控制在最小。

2.2TSV絕緣層

TSV的金屬填充需要用到絕緣層來對硅襯底進行充分的電氣隔離。絕緣層的工藝要求包括良好的階梯覆蓋率,無漏電流,低應力,高擊穿電壓,以及不同的TSV集成引起的加工溫度的限制。二氧化硅(SiO2)或氮化硅(Si3N4)是常用于等離子體增強化學氣相沉積(PECVD)或減壓化學氣相沉積(SACVD)的絕緣層。然而,當TSV直徑小于3μm時,絕緣層更適用于原子層沉積(ALD)。ALD有幾個優勢,如較低的熱預算,比現有流程更好的階梯覆蓋率,無需再進行表面處理,并且由于較薄的絕緣層,降低了TSV的CMP加工時間。

2.3TSV阻擋層和種子層

接下來的過程是阻擋層沉積,目的是防止銅原子在溫度400℃下的退火過程的TSV中擴散。另外,阻擋層也作為絕緣層和銅層之間的粘合層。常見的作為阻擋層的的材料是Ti、Ta、TaN、TiN;根據TSV的尺寸來選擇物理氣相沉積(PVD)、化學氣相沉積(CVD)或原子層沉積(ALD)法來實現。

金屬阻擋層使用PVD沉積,如鉭和鈦。溫度要求低是這種方法最大的特點,但是其階梯覆蓋率也低,很容易產生較高縱橫比(>10:1)的TSV[6]。沉積較厚的金屬阻擋層可以克服階梯覆蓋低的缺點,但會使生產成本變高。TiN或TiN阻擋層可以用化學氣相沉積法沉積,具有均勻性好的優點、但需要較高的加工溫度。

在下面的過程中,銅種子通常采用物理氣相沉積法沉積在TSV中。在IMEC研究中,采用ALD法TiN作為阻擋層,制造了均勻性約80%,尺寸2×30μm的TSV(縱橫比=15)。成本和減少阻擋層和種子層過程的熱預算是TSV應用中的關鍵挑戰。

在后端工序互聯之后用于設備可靠性檢測的溫度是一個值得關注的問題。采用低溫下進行的全濕法對高縱橫比的TSV的阻擋層和銅種子層實現無電鍍沉積,用金納米粒子(AuNPs)或鈀納米粒子(PdNPs)作為催化劑實現鈷-鎢和銅的阻擋層/種子層的無電鍍沉積。一個TSV不同位置的吸附鈀納米粒子在室溫下3小時后的形態,如圖3所示。PdNPs沉積均勻地分布在整個尺寸為2×24μm的TSV中,沒有觀察到鈀結塊。盡管全濕法阻擋層和種子層在較低溫度下有較好的階梯覆蓋率,但它的可靠性還需要更多的實驗來證明。

2.4TSV填充

TSV填充電鍍銅有三種方法:共形電鍍,自下而上的密封凸點電鍍,和超共形電鍍。電鍍方法是以各種三維集成應用為基礎的。總的來說,TSV的結構是深度在10到200μm之前的典型的圓柱形孔。TSV的深度取決于芯片或晶圓鍵合時的所需厚度,而TSV縱橫比的大小則由介電膜、阻擋層和種子層和填充過程決定的。

2.4.1共形電鍍

共形度銅與晶圓級芯片規模封裝中線路鍍銅相似。以CIS應用作為一個例子,它的主要過程包括硅的深反應離子刻蝕到CMOS金屬層,通孔的氧化物隔離,阻擋層和種子層PVD沉積,最后對RDL共形鍍銅。在抗蝕劑掩模中銅厚5~10μm。然而,由于銅種子層的不連續性,僅有縱橫比為3的TSV得以應用。

2.4.2自下而上密封凸點電鍍

TSV自下而上密封凸點電鍍法的一個優點是能夠有效避免通孔填充過程中產生空隙。此外,自下而上填充法適合后通孔工藝。它通常需要在底部的銅種子層的臨時鍵合或粘貼技術來完成填充過程。載體晶圓的去除會帶來額外的花費和可靠性問題,因此有一種新型的TSV自下而上密封凸點電鍍銅填充法。該工藝流程為:

(1)TSV刻蝕,(2)減薄,(3)氧化隔離,(4)種子層沉積,(5)光刻膠標記,(6)制造密封凸點,(7)TSV凸點電鍍,(8)最終刻蝕。掃描電鏡、光學顯微鏡和X射線分析都能觀察到,自下而上填充法不會產生缺陷。

2.4.3超共形電鍍

超共形電鍍銅填充的適用尺寸有較大的范圍,從鑲嵌尺寸到用于應用設備的較大尺寸。通過X射線觀測到銅覆蓋層和阻擋層用CMP去除后,TSV中沒有縫隙。

此外,三步PPR電流波形法減少了銅填充時間和TSV填充的缺陷。然而,由于使用可以減少通孔側壁銅離子的脈沖反向電流,填充高縱橫比的TSV需要很長的時間。因此,三維集成中縮短TSV填充時間是很有必要的。提高充填效率的優化方法有多種,包括陽極位置優化,多級TSV填充,電鍍電流密度優化。

最后,使用CMP來去除晶片表面的銅覆蓋層和阻擋層。總的來說,這項技術需要兩個步驟。第一步是去除通孔填充后的厚的銅凹坑或凹槽,到阻擋層停止。第二步是去除阻擋層,到絕緣層停止。選擇不同的漿料來實現隔離,避免凹陷和侵蝕。

2.5TSV銅暴露

另一個關鍵步驟是由于銅材料和硅襯底之間熱膨脹系數不匹配帶來的TSV擠壓或TSV凸點問題。銅的熱膨脹系數為17.6ppm/℃,高于硅的2.6ppm/℃,引起電介質層開裂和分層等可靠性問題。通過對一系列不同條件下退火工藝的實驗,得出了退火工藝的影響。Cu從退火溫度在350℃開始凸起,一直到450℃。銅的突出現象,有兩種可能的機制。第一個機制是在退火過程中垂直擴展的銅材料塑性變形。第二種機制是由于當TSV中應力分布不均勻引起的擴散蠕變。通過對電鍍工藝之后的TSV進行適當的預退火處理來減少硅應力是很有必要的,然后,用CMP去除多余銅。

3、TSV制程關鍵工藝設備

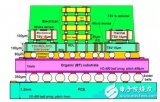

TSV制作工藝包括以下幾步:通孔制作;絕緣層、阻擋層和種子層的沉積;銅填充;通過化學機械拋光去除多余的金屬;晶圓減薄;晶圓鍵合等。

每一步工藝都有相當的技術難度,在通孔制作步驟,保持孔的形狀和控制角度非常重要,通過Bosch工藝來實現深孔刻蝕;在沉積絕緣層、阻擋層和種子層時,需要考慮各層的均勻性和粘附性;銅填充時必須避免空洞等缺陷,這樣填充的銅可以在疊層器件較高的溫度下保持正常的電性能;一旦完成了銅填充,則需要對晶圓進行減薄;最后是進行晶圓鍵合。

TSV制作流程會涉及到深刻蝕、PVD、CVD、銅填充、微凸點及RDL電鍍、清洗、減薄、鍵合等二十余種設備,其中通孔制作、絕緣層/阻擋層/種子層的沉積、銅填充、晶圓減薄、晶圓鍵合等工序涉及的設備最為關鍵,在某種程度上直接決定了TSV的性能指標。

3.1深硅刻蝕設備

通常情況下,制造硅通孔(經常穿透多層金屬和絕緣材料)采用深反應離子刻蝕技術(DRIE),常用的深硅刻蝕技術又稱為“Bosch(博氏)”工藝,有最初發明該項技術的公司命名。

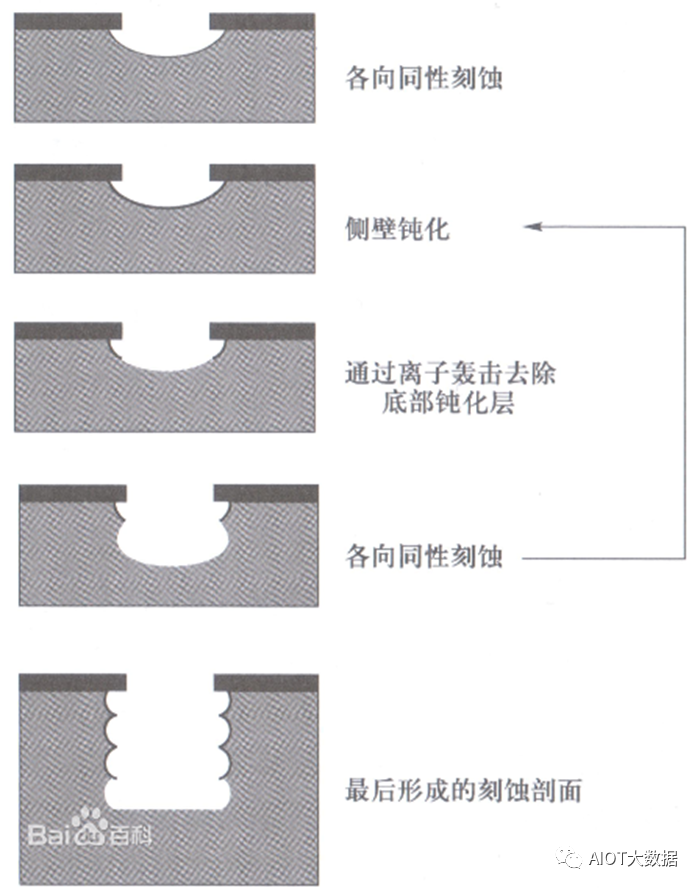

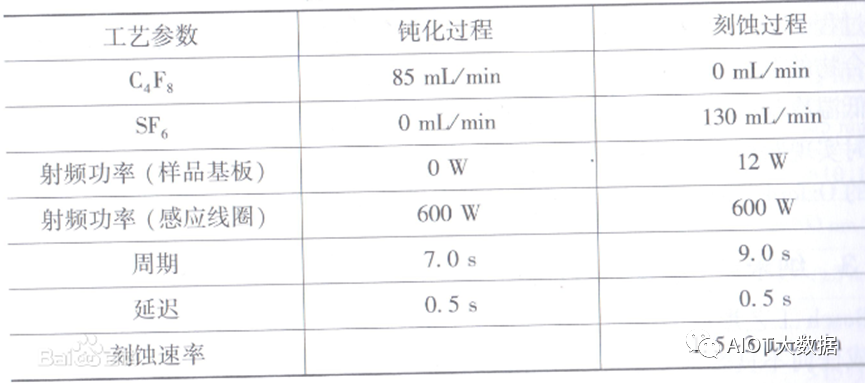

如下圖所示,一個標準Bosch工藝循環包括選擇性刻蝕和鈍化兩個步驟,其中選擇性刻蝕過程采用的是SF6和O2兩種氣體,鈍化過程采用的是C4F8氣體。在Bosch工藝過程中,首先利用SF6等離子體刻蝕硅襯底,接著利用C4F8等離子體作為鈍化物沉積在硅襯底上,在這些氣體中加入O2等離子體,能夠有效控制刻蝕速率與選擇性。因此,在Bosch刻蝕過程中很自然地形成了貝殼狀的刻蝕側壁。

目前深硅刻蝕設備主要由美國應用材料、泛林半導體等設備廠商控制。從國內看,近年來在國家科技重大專項支持下,中微半導體、北方微電子等廠家研制的深硅等離子刻蝕機可以投入硅通孔刻蝕的研發及量產中。尤其DSE200系列刻蝕機是北方微電子公司于2012年推出的首款深硅等離子刻蝕機,該刻蝕機能實現高達50:1的硅高深寬比刻蝕,并同時實現優良的側壁形貌控制、穩定的均勻性、極高的刻蝕選擇比。

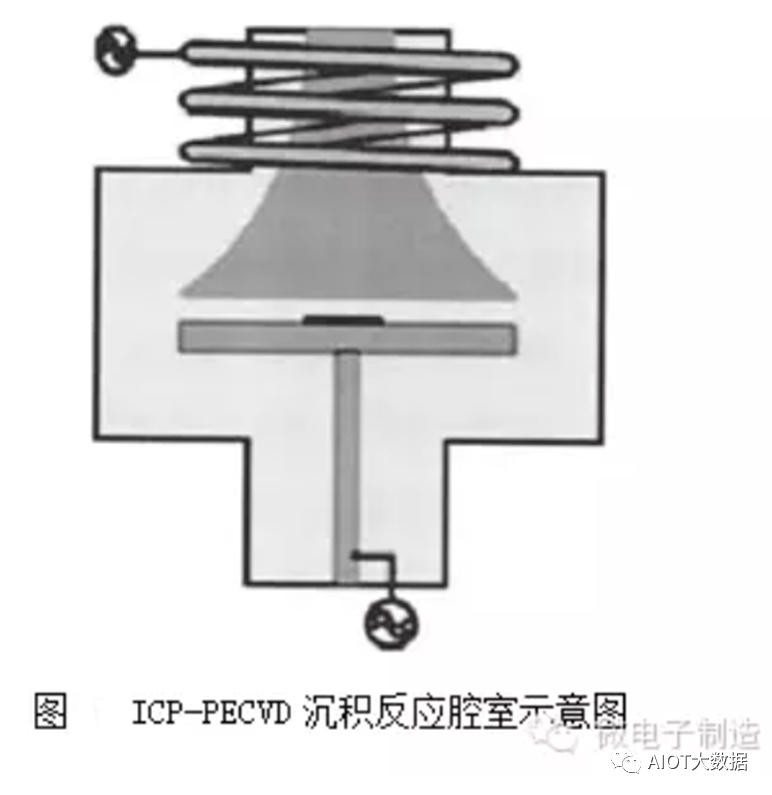

3.2PVD/CVD沉積設備

硅通孔形成后,通過等離子體增強化學氣相沉積法(PECVD)在硅孔內表面沉積一層絕緣材料SiO2,工藝溫度低,在100~400℃進行沉積,是TSV孔絕緣的主流技術之一。今年來ICP-PECVD新型等離子氣相增強化學沉積設備被引入進行TSV孔絕緣層的填充,與常規PECVD不同之處在于,其射頻功率通過電感耦合至工藝腔室,配合耦合至反應室襯底的射頻源可以提高反應離子的方向性,典型的ICP-PECVD工藝腔設計下圖所示。ICP-PECVD沉積SiO2的工藝溫度低至20~100℃,反應離子濃度高,有助于提高對TSV孔的填充效率。

絕緣層做好后,通過物理氣相沉積法(PVD)沉積金屬擴散阻擋層和種子層,為后續的銅填充做好準備。如果填充材料為多晶硅或者鎢,則不需要種子層。

后續的電鍍銅填充要求TSV側壁和底部具有連續的阻擋層和種子層。種子層的連續性和均勻性被認為是TSV銅填充最重要的影響因素。根據硅通孔的形狀、深寬比及沉積方法不同,種子層的特點也各有不同,種子層沉積的厚度、均勻性和粘合強度是很重要的指標。

3.3電鍍銅填充設備

很多成本模型顯示,TSV填充工藝是整個工藝流程中最昂貴的步驟之一。TSV的主要成品率損耗之一是未填滿的空洞。電鍍銅工藝作為最合適的硅通孔填充技術受到業內的普遍關注,其關鍵技術在于TSV高深寬比(通常大于10:1)通孔的全填充電鍍技術。

?

國外有諸多公司已經成功研發該項目技術并已形成成熟產品,包括NEXX、TECHNIC、Semitool等公司。尤其是美國NEXX公司是先進封裝領域的專用設備供應商,其中StratusS200(4~8英寸)、S300(8~12英寸)全自動電鍍設備已應用于全球各大封裝廠家的12英寸及以下規格的晶圓量產生產中,可用于TSV、凸點、UBM、RDL、銅互連等制程。見圖。

NEXX公司系列電鍍設備銷往全球,其中亞洲封測廠家占75%。據了解國內封裝龍頭企業長電、富士通等的產線上都在使用Stratus系列設備。該系列設備采用剪切電鍍方式,具有鍍層均勻、結構緊湊、易于擴展等優點,為封測廠家提供了質量穩定、生產效率高、占地小的一款自動設備。

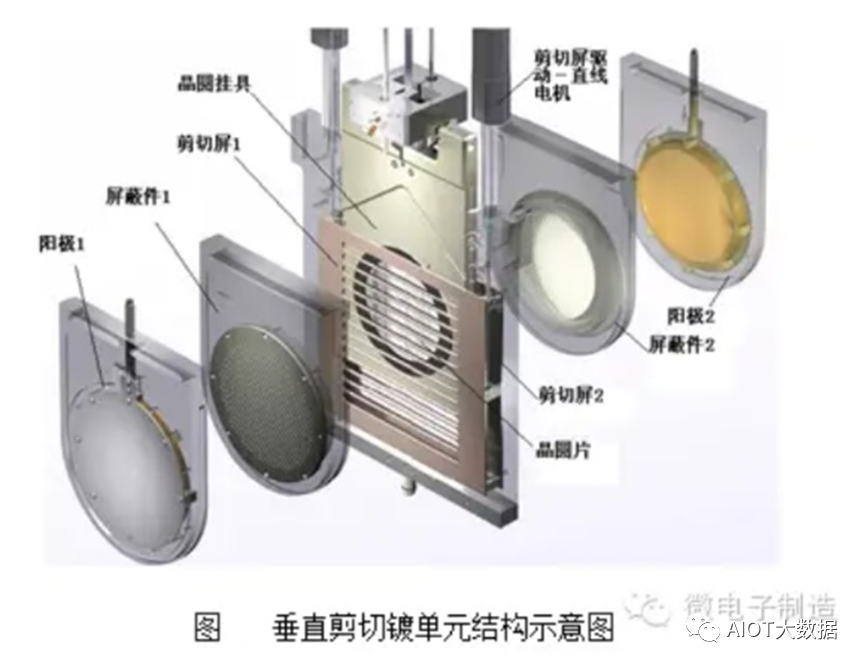

垂直剪切鍍單元作為該設備的核心部分(見圖),主要包括陽極、屏蔽件、晶圓夾具、剪切屏及驅動電機等。整體單元框架上分別布置以上各件的安裝導槽、提高鍍層均勻性的剪切屏、直流導電夾緊機構。各個部件主體均采用氟塑料材質板,單元整體為用螺栓、密封件將各個部件連接組合。

目前國內研究機構在TSV單項技術上取得一些研究結果,但是對于電鍍相關工藝設備幾乎并無廠家涉及,只有中國電子科技集團公司第二研究所在進行TSV銅填充工藝技術的研究,并有相關實驗設備交付客戶使用。

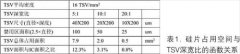

3.4晶圓減薄設備

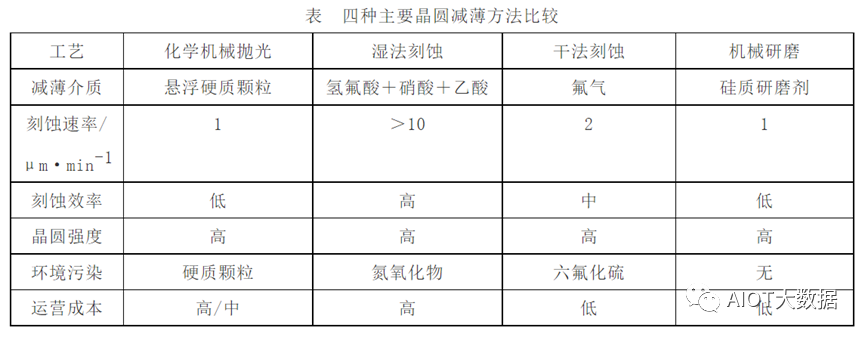

TSV要求晶圓減薄至50μm甚至更薄,要使硅孔底部的銅暴露出來,為下一步的互連做準備。目前晶圓減薄可以通過機械研磨、化學機械拋光、濕法及干法化學處理等不同的加工工序來實現,通過它們之間有機的結合,并優化這幾道工序的比例關系,保證晶圓既能減薄到要求的厚度,又要有足夠的強度。目前四種主要晶圓減薄方法對比見下表。

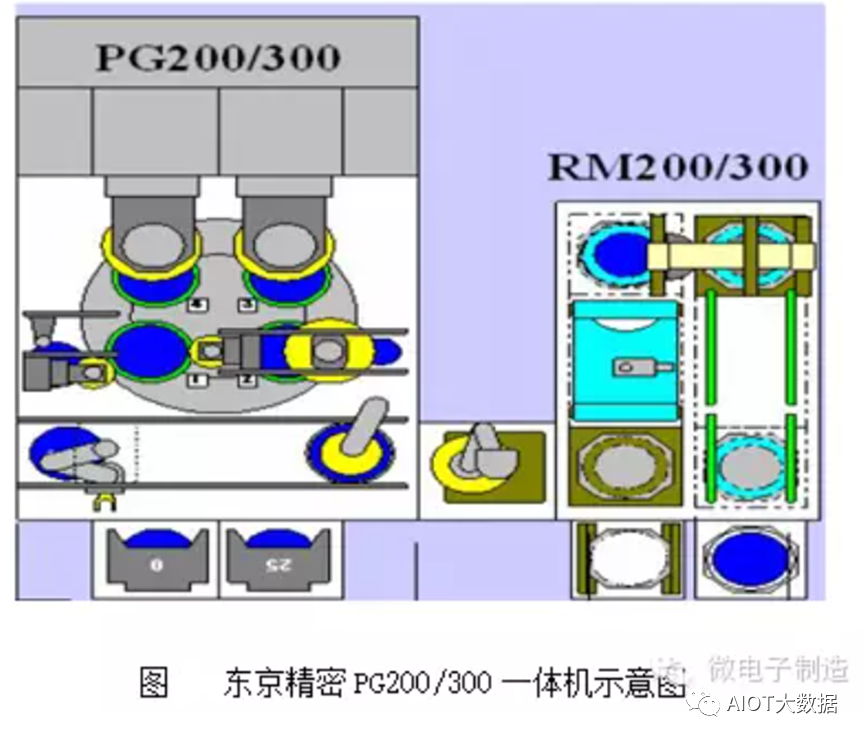

在要求<50μm這個厚度上,晶圓很難容忍減薄過程中的磨削對晶圓的損傷及內在應力,其剛性也難以使晶圓保持原有的平整狀態,同時后續工藝的晶圓傳遞、搬送也遇到了很大的問題。目前業界的主流解決方案是采用一體機的思路,將晶圓的磨削、拋光、保護膜去除、劃片膜粘貼等工序集合在一臺設備內,晶圓從磨片一直到粘貼劃片膜為止始終被吸在真空吸盤上,始終保持平整狀態,從而解決了搬送的難題。

右圖是東京精密公司的一體機PG200/300的基本配置示意圖。圖中PG部分是磨片和拋光的集成體。通過一個帶有4個真空吸盤的大圓盤回轉臺360°順時針旋轉,使晶圓在不用離開真空吸盤的情況下就可以依次送到粗磨、精磨、拋光等不同的加工工位,完成整個減薄過程。

減薄好的晶圓從PG處轉移到RM處,它是通過一個多孔陶瓷吸盤來完成。RM部分主要是完成保護膜的去除和劃片膜的粘貼。由于保護膜的剝離需要在晶圓的正面動作,所以必須將晶圓進行反轉。由于晶圓厚度很薄,翻轉難度很大。東京精密公司把傳統剝膜工藝的后續工藝——貼膜工藝前移,利用劃片膜粘貼到框架上所具有的平整性和張力來給晶圓提供支撐,從而解決這一問題。

?

3.5晶圓鍵合設備

晶圓鍵合最初是為MEMS制造工藝而開發,主要作為晶圓級覆蓋技術。現在晶圓鍵合不僅用于覆蓋MEMS晶圓,而且也用于堆疊具有不同功能的晶圓,通過TSV實現晶圓的3D堆疊。

目前晶圓鍵合主要有直接氧化物鍵合、陽極鍵合、粘接鍵合、基于焊料的鍵合、金屬—金屬直接鍵合、超聲鍵合、玻璃介質鍵合等等。但是,因為CMOS器件熱預算的緣故,與TSV互連的CMOS晶圓兼容的鍵合工藝僅僅局限于直接氧化物鍵合、金屬鍵合(Cu-Cu或Cu-Sn-Cu)、粘接鍵合和這幾種方法的組合。其中Cu-Cu直接鍵合與其它鍵合方法對比有種種優點:電阻率較低、抗EM較好、互連RC延遲減少,可以同時實現機械和電學的接觸界面。

不過,可靠地Cu-Cu鍵合對于大多數應用僅從高溫、高壓和長工藝時間產生,主要是因為它有形成自然氧化物的傾向,對器件可靠性有不利影響。現在,工藝溫度高是Cu-Cu直接鍵合的主要瓶頸之一,因為它給器件可靠性及制造良率產生負面影響。另外,高溫下對晶圓之間的對準精度也產生了不利影響。

基于此,領先地晶圓鍵合設備供應商奧地利EVG公司開發了光學對準、低溫Cu-Cu熱壓鍵合工藝,對準精度達到了亞微米。

四、玻璃穿孔技術(TGV)

硅基轉接板2.5D集成技術作為先進的系統集成技術,近年來得到迅猛的發展。但硅基轉接板存在兩個的主要問題:

1)成本高,硅通孔(TSV)制作采用硅刻蝕工藝,隨后硅通孔需要氧化絕緣層、薄晶圓的拿持等技術;

2)電學性能差,硅材料屬于半導體材料,傳輸線在傳輸信號時,信號與襯底材料有較強的電磁耦合效應,襯底中產生渦流現象,造成信號完整度較差(插損、串擾等)。作為另一種可能的替代硅基轉接板材料,玻璃通孔(TGV)轉接板正在成為半導體企業和科研院所的研究熱點。

和TSV相對應的是,作為一種可能替代硅基轉接板的材料,玻璃通孔(TGV)三維互連技術因眾多優勢正在成為當前的研究熱點,與硅基板相比,TGV的優勢主要體現在:

1)優良的高頻電學特性。玻璃材料是一種絕緣體材料,介電常數只有硅材料的1/3左右,損耗因子比硅材料低2-3個數量級,使得襯底損耗和寄生效應大大減小,保證了傳輸信號的完整性;

2)大尺寸超薄玻璃襯底易于獲取。Corning、Asahi以及SCHOTT等玻璃廠商可以提供超大尺寸(>2m×2m)和超薄(<50μm)的面板玻璃以及超薄柔性玻璃材料。

3)低成本。受益于大尺寸超薄面板玻璃易于獲取,以及不需要沉積絕緣層,玻璃轉接板的制作成本大約只有硅基轉接板的1/8;

4)工藝流程簡單。不需要在襯底表面及TGV內壁沉積絕緣層,且超薄轉接板中不需要減薄;

5)機械穩定性強。即便當轉接板厚度小于100μm時,翹曲依然較小;

6)應用領域廣泛。除了在高頻領域有良好應用前景,作為一種透明材料,還可應用于光電系統集成領域,氣密性和耐腐蝕性優勢使得玻璃襯底在MEMS封裝領域有巨大的潛力。

近年來,國內外許多研究者致力于研發低成本、小尺寸、細間距、無損快速玻璃成孔技術的開發,如噴砂法、光敏玻璃、等離子體刻蝕、聚焦放電、激光燒蝕等。但是由于玻璃材料的易碎性和化學惰性,當前已有的方法都還存在許多問題,距離實際應用和大規模的量產,還有很長的路要走。截止目前,玻璃通孔三維互連技術發展的主要困難包括:

1)現有的方法雖然可以實現TGV,但有些方法會損傷玻璃,造成表面不光滑;有些方法的加工效率低,沒法大規模量產;

2)TGV的高質量填充技術,與TSV不同,TGV孔徑相對比較大且多為通孔,電鍍時間和成本將增加;

3)與硅材料相比,由于玻璃表面平滑,與常用金屬(如Cu)的黏附性較差,容易造成玻璃襯底與金屬層之間的分層現象,導致金屬層卷曲,甚至脫落等現象。

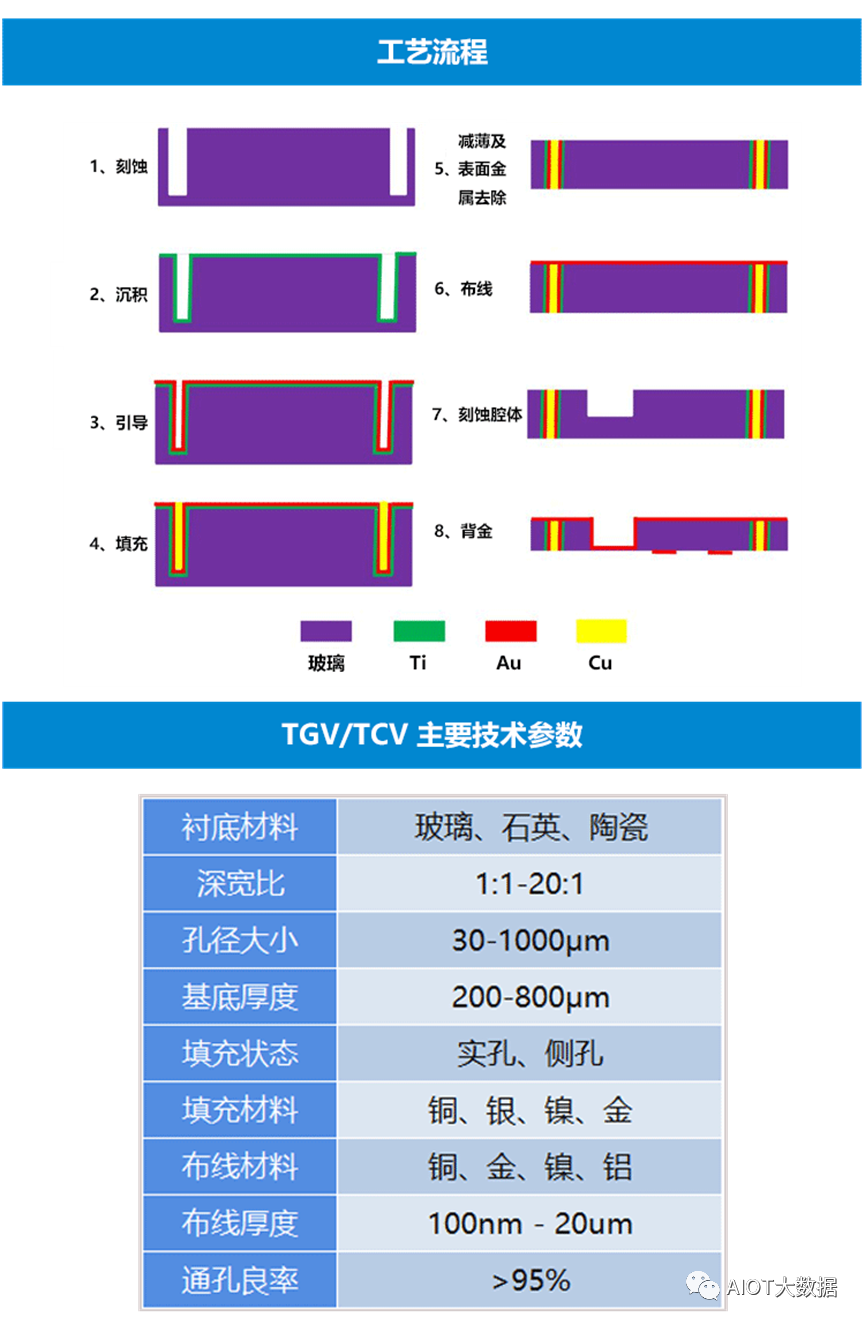

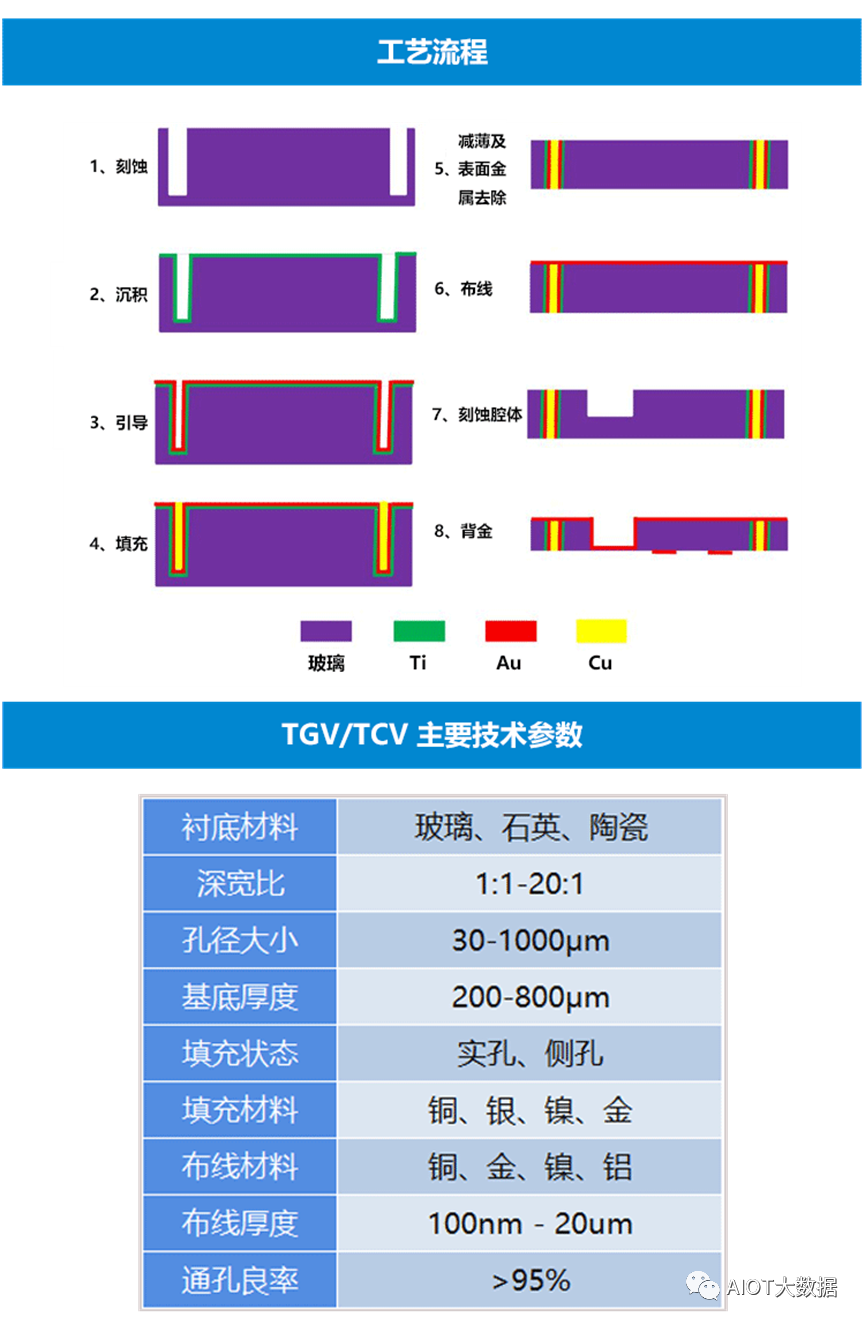

1、玻璃穿孔主要技術

1.1玻璃穿孔成孔技術

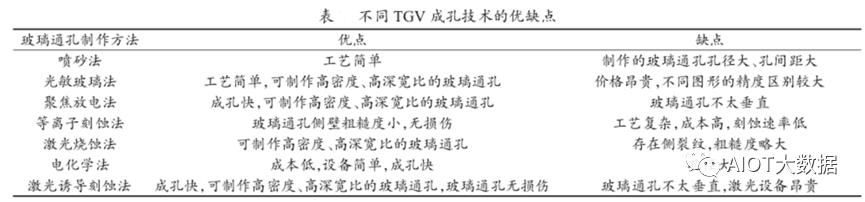

制約玻璃通孔技術發展的主要困難之一就是玻璃通孔成孔技術,需要滿足高速、高精度、窄節距、側壁光滑、垂直度好以及低成本等一系列要求。玻璃通孔成孔技術可以分為噴砂法、光敏玻璃法、聚焦發電法、等離子體刻蝕法、激光燒蝕法、電化學放電加工法、激光誘導刻蝕法。

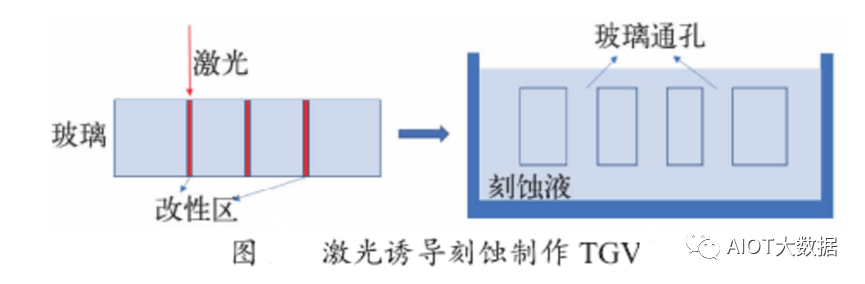

其中,玻璃誘導刻蝕法如下:

1)使用皮秒激光在玻璃上產生變性區域;2)將激光處理過的玻璃放在氫氟酸溶液中進行刻蝕。

?

1.2玻璃穿孔填孔技術

類似硅通孔的金屬填充方案也可以應用在TGV上。

另外一個將TGV填實的方案是將金屬導電膠進行TGV填實。利用金屬導電膠的優點是固化后導電通孔的熱膨脹系數可以調節,使其接近基材,避免了因CTE不匹配造成的失效。

除了TGV電鍍填實外,TGV也可以采用通孔內電鍍薄層方案實現電學連接。

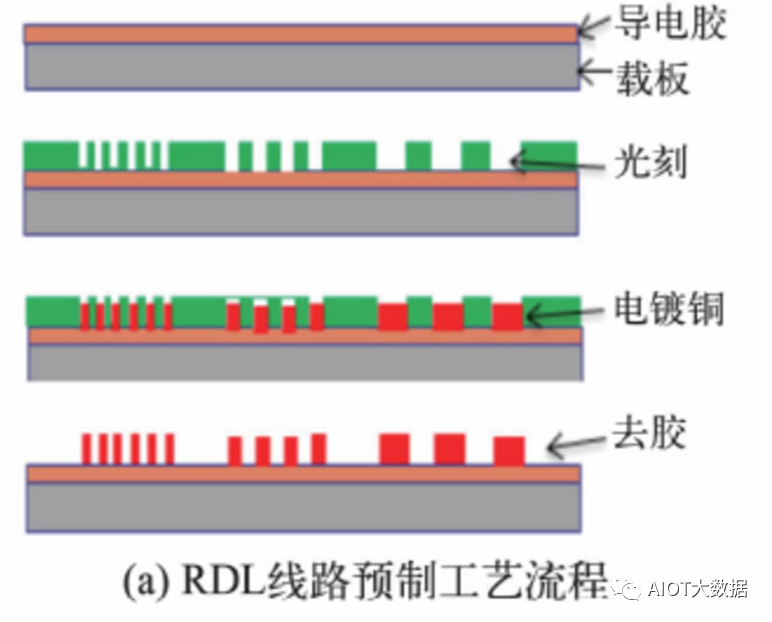

1.3玻璃通孔高密度布線

線路轉移(CTT)和光敏介質嵌入法,是比較常用的方式。CTT主要包括兩個過程。一是精細RDL線預制,每一RDL層可以在可移動載體上單獨制造一層薄導電層,并在轉移到基板上之前測試或檢查細線成品率。精細線路的形成采用細線光刻和電解鍍銅的方法,并且以薄銅箔作為鍍層的種子層。工藝流程如下:

?

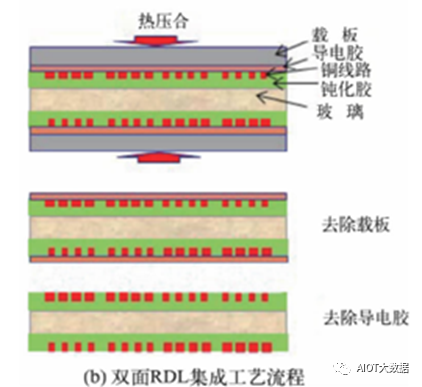

第二步就是將RDL層集成到基板上。RDL層被制造出來后,他們再使用熱壓合的同時被轉移到核心層的兩邊。步驟如下:

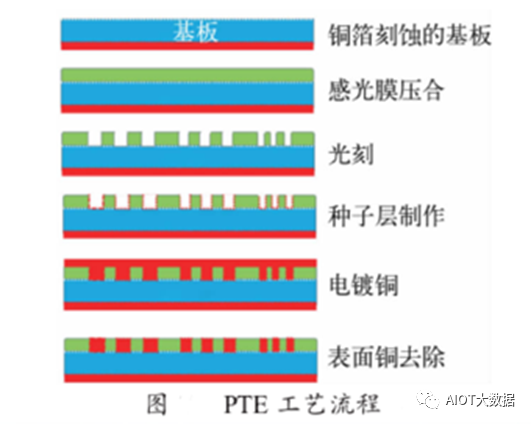

PTE工藝可分為兩個不同的步驟,一是在光敏介質層總形成精細的溝槽;二是金屬化,包括種子層沉積、電鍍和表面除銅。工藝流程如下:

2、國內外研究現狀

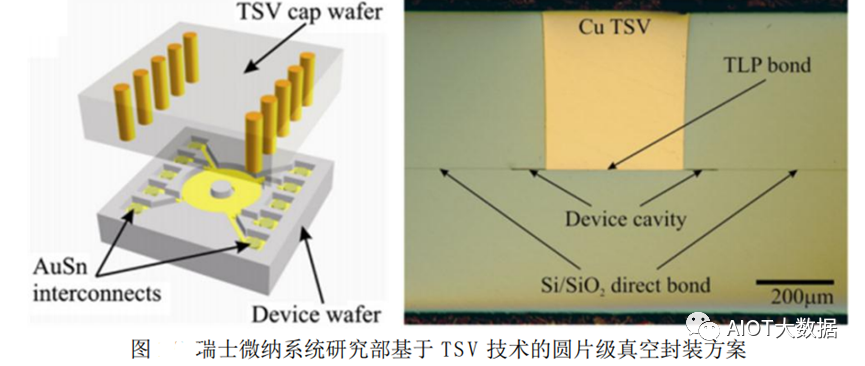

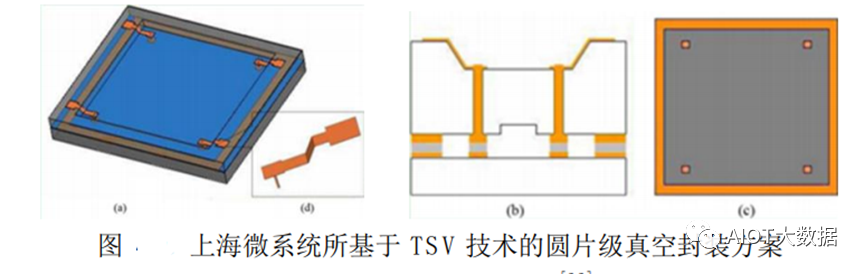

2011年,瑞士的微納系統研究部提出了如下圖所示的基于TSV技術圓片級真空封裝方案。該方案由TSV封帽與器件層兩部分構成,TSV封帽垂直導通柱是填充在硅通孔中的銅柱。器件層上制作有金錫電極與銅柱相連,從而把電信號從空腔內部的引到空腔外部,最后通過硅-硅直接鍵合實現密封。該方案氣密性很好,但是TSV封帽制作工藝復雜,熱應力大(銅柱與硅熱失配大),且硅硅鍵合對鍵合表面要求質量很高,一般加工過的硅片很難達到此要求。

2013年,新加坡微電子學院提出如下圖所示基于TSV技術的圓片級真空封裝方案。該方案由TSV封帽、硅器件層組成,TSV封帽也是由硅通孔里的銅柱做垂直導通柱,硅器件層上制作有射頻結構及金屬電極,最后使用AuSn焊料鍵合實現氣密封裝。此方案雖然也存在TSV封帽制作工藝復雜,熱應力大的問題,但采用焊料鍵合方式封裝,盡管犧牲一定的密封性,但大大降低對TSV鍵合表面質量的要求,其工業應用范圍更廣。

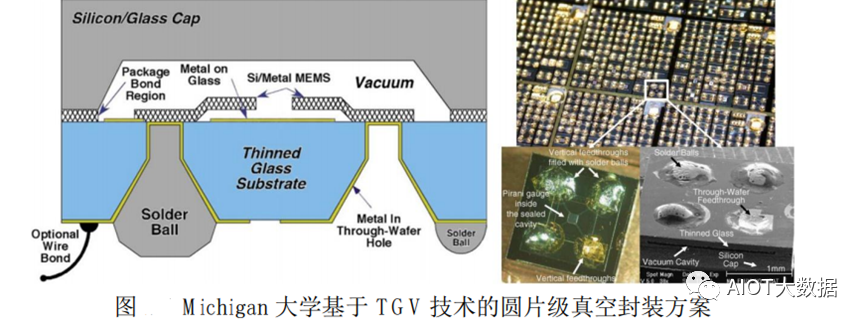

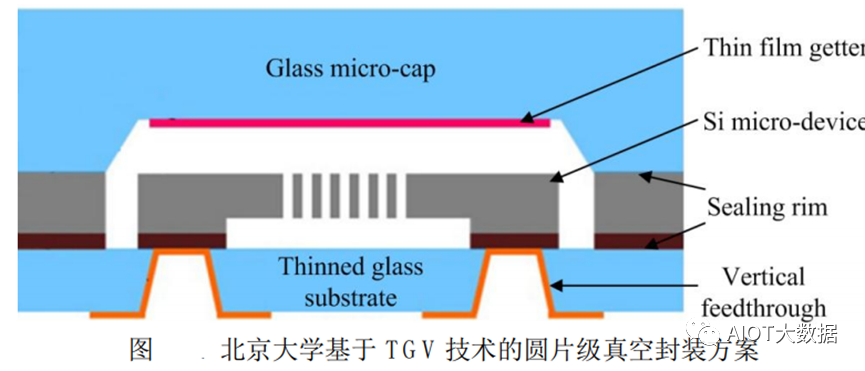

從以上兩個TSV例子可以看出,TSV存在工藝復雜,熱應力過大的缺點。為解決這些問題,更好實現真空封裝,又提出了TGV技術。2008年,美國Michigan大學提出了的一種基于常規工藝TGV技術的圓片級真空封裝方案,如下圖所示。該方案由封帽,器件層以及基于常規工藝TGV技術襯底三部分構成。封帽可以為硅或玻璃,制作有空腔;器件層是硅結構層。基于常規工藝TGV技術襯底是在玻璃片上制作電極和通孔,通孔表面沉積有金屬層,有的通孔填充焊錫球,用以形成垂直導通柱,把電信號由密封腔中引出。最后通過陽極鍵合把器件層與TGV襯底鍵合在一起,形成密封。該方案優點是通過陽極鍵合形成密封,陽極鍵合密封性好、熱失配小、污染小且一般硅片能達到陽極鍵合對表面質量的要求。

2010年,挪威的SensonorTechnologiesAS提出了結構如下圖所示的一種基于玻璃回流TGV技術圓片級真空封裝方案封裝蝶翼式硅微陀螺。為減少結構應力,提高陀螺儀靈敏度,采用三層對稱結構設計,上下兩層均為TGV襯底,中間夾硅結構層。基于玻璃回流TGV襯底,是通過高溫玻璃回流,然后雙面CMP加工制成的。TGV襯底垂直導通柱即為由回流玻璃隔離出來的硅柱,襯底上不制作金屬電極,直接用硅做電極。硅結構層采用Silicon-on-Insulator(SOI)材料和干法刻蝕制作而成,空腔制作在硅可動結構層上,通過硅-玻璃將三者陽極鍵合在一起,分別有兩次,形成密封環境。該封裝方案優勢凸出,不僅封裝應力低,而且TGV襯底工藝簡單,密封性好,熱適配小,寄生電容小。

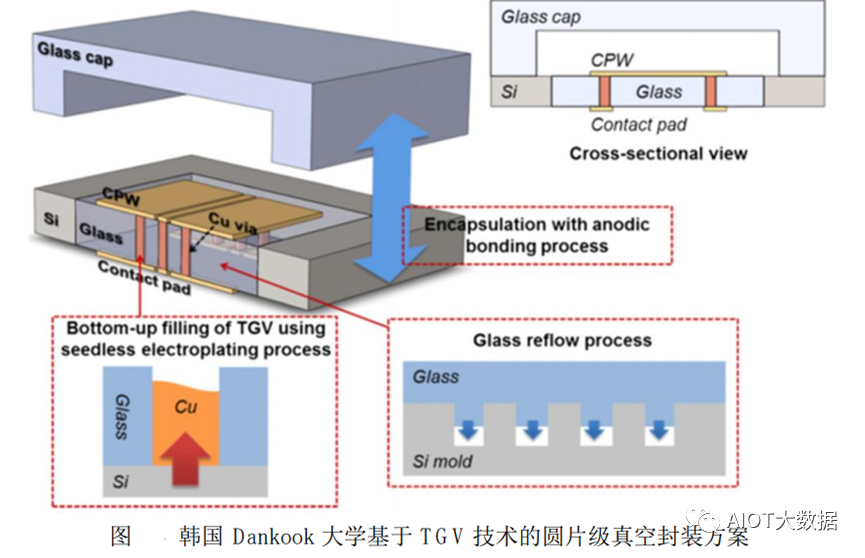

2013年,韓國Dankook大學開發出結構如圖所示的TGV技術圓片級真空封裝方案。該方案包括玻璃封帽、CPW器件層以及TGV襯底,腔體制作在玻璃封帽上。其TGV襯底與眾不同,先后采用玻璃回流工藝與電鍍銅工藝制作。簡而言之,為先利用玻璃回流工藝制作硅導通柱,然后去除硅導通柱,用電鍍銅作導通柱。CPW器件層制作在襯底密封環范圍內,最后封帽與襯底通過硅-玻璃陽極鍵合形成密封腔,并制作外部的金屬焊盤完成引線及封裝。該方案電學性能優良,但工藝復雜。

?

2009年,上海微系統所提出了一種結構如圖所示基于TSV技術的圓片級真空封裝方案。該方案由TSV封帽與硅襯底兩部分組成:TSV封帽采用濕法和干法刻蝕出通孔,通孔中填充銅作為導通柱,導通柱與硅通過隔離層隔離,腔體制作在TSV封帽上。硅襯底上制作有結構,通過Cu-Sn焊料鍵合與TSV封帽實現密封封裝。該方案簡單易行,但焊料鍵合用在圓片級真空封裝上會顯得鍵合密封性不夠,污染過大。

2012年,北京大學提出了結構如圖所示一種基于常規工藝TGV技術的圓片級真空封裝方案。該方案是典型的三明治式架構,由玻璃封帽、硅可動結構層、TGV襯底三層組成。硅可動結構采用干法刻蝕出可動結構;基于常規工藝TGV襯底采用濕法腐蝕出通孔與金屬沉積導通柱等工藝制作而成;空腔制作在封帽上,空腔頂部沉積有吸氣劑,保持腔體真空度。最后玻璃封帽、硅可動結構層、TGV襯底通過兩次硅-玻璃陽極鍵合封裝在一起。

3、TGV技術的應用

3.1玻璃基板的三維集成無源元件

玻璃基板具有優異的高頻電學性能,因此被廣泛的應用于集成無源器件(IPD)之中。2010年,喬治亞理工的封裝中心率先完成了基于TGV的濾波器設計與制造,并與相同的硅基電感對比,展現了更好的電學特性。2017年,日月光集團在玻璃基板上實現了面板級的IPD制作工藝。該方案板材翹曲可控制在1mm以內,并且無明顯結構剝落分層現象。

3.2嵌入式玻璃扇出與集成天線封裝

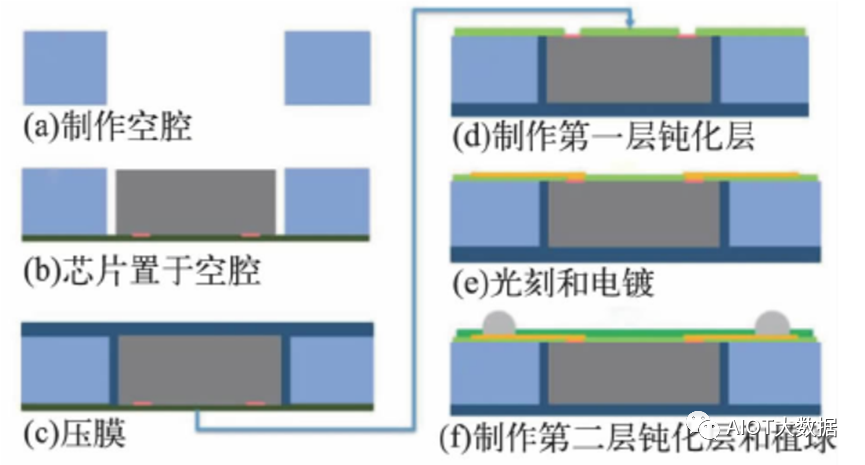

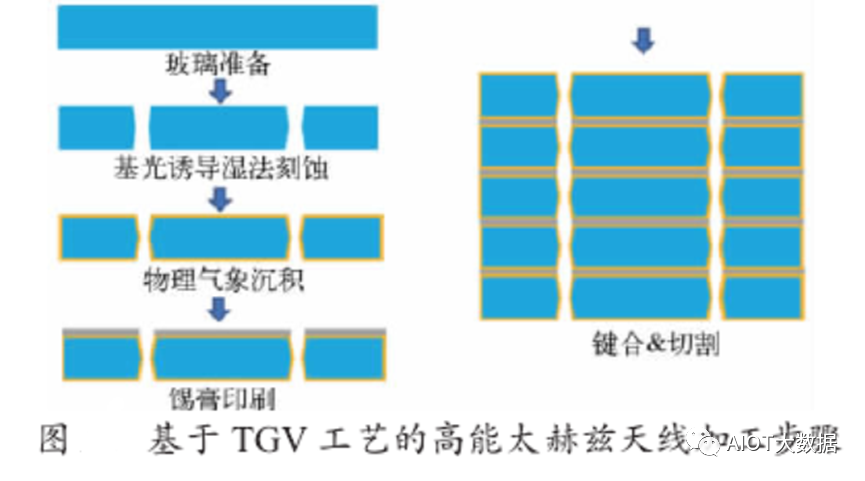

玻璃通孔還可以在玻璃上制作空腔,進而為芯片的封裝提供一種嵌入式玻璃扇出(eGFO)的新方案。2017年喬治亞理工率先實現了用于高I/O密度和高頻多芯片集成的玻璃面板扇出封裝。該技術在70um厚、大小為300mm*300mm的玻璃面板上完成了26個芯片的扇出封裝,并有效的控制芯片的偏移和翹曲。2020年云天半導體采用嵌入式玻璃扇出技術開了77GHz汽車雷達芯片的封裝,并在此基礎上提出了一種高性能的天線封裝(AiP)方案。工藝流程如圖所示:

在厚度為180um的玻璃晶片中,先采用激光誘導玻璃變性和化學腐蝕工藝形成玻璃空腔,然后將175um高的芯片放入玻璃空腔總。通過復合材料將芯片和玻璃之間的縫隙填壓而不產生空隙,同時保護芯片的背面。對晶圓的頂面進行剝離,形成銅RDL,最后進行后續線路制作、球柵陣列(BGA)制作以及晶圓切片。

3.3基于玻璃通孔的MEMS封裝

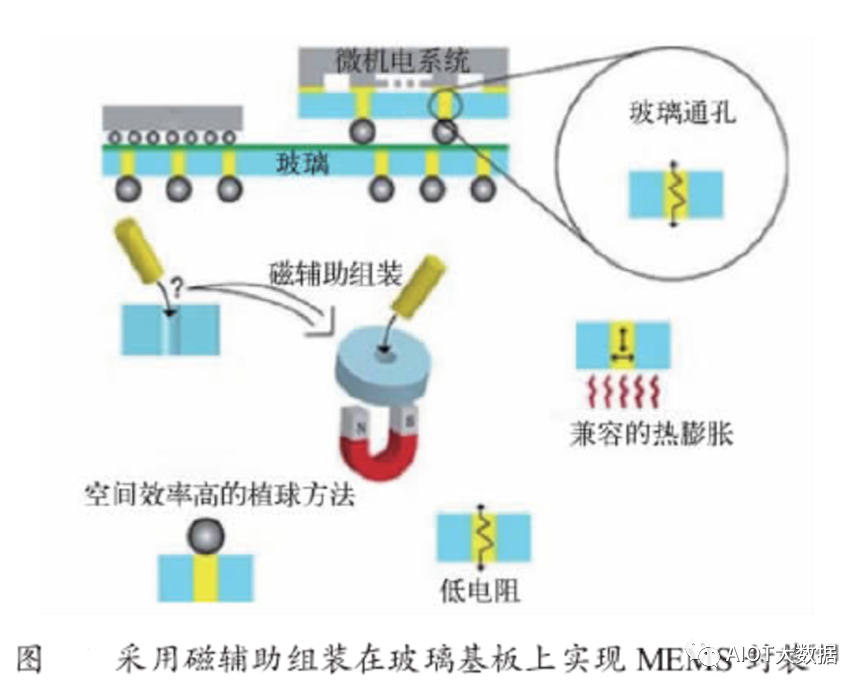

2013年,LEE等利用玻璃穿孔技術實現射頻MEMS器件的晶圓級封裝,采用電鍍方案實現通孔的完全填充,通過該方案制作的射頻MEMS器件在20GHz時具有0.197dB的低插入損耗和20.032dB的高返回損耗。2018年,LAAKSO等創造性地使用磁輔助組裝的方式來填充玻璃通孔,并用于MEMS器件的封裝中。

3.4基于TGV的集成天線

?

廈門大學的張淼創造性的引入TGV加工波導縫隙天線。首先采用激光誘導刻蝕制備波導縫隙陣列天線玻璃襯底,通過激光在玻璃上誘導產生連續性的變性區,后將變性后的玻璃在稀釋氫氟酸總進行刻蝕,由于激光作用處的玻璃氫氟酸中刻蝕速率較快,所以玻璃會成塊脫落從而形成目標通孔結構。最終刻蝕后的玻璃穿孔精度為±5μm,遠遠高于傳統機加工的精度。其次,采用物理氣相沉積對每層波導縫隙陣列天線玻璃襯底濺射銅層,經過氧等離子體清洗以徹底清除焊盤表面的有機物等顆粒,并使晶圓表面產生一定的粗糙度,為種子層的良好附著創造條件。清洗后的晶圓在烤箱150℃下烘烤60min徹底去除水汽。然后在磁控濺射設備中,晶圓表面濺射一層厚度約為5μm的銅層。最后,采用技術焊料鍵合技術將5片晶圓鍵合。用刮刀以及絲網將10μm厚度的錫焊料印刷到晶圓表面,然后在鍵合機的真空腔室中以240℃的溫度加熱,以40N的壓力壓合5min使焊料融化或相互擴散以達到鍵合的目的。工藝流程度如圖:

3.5多層玻璃基板

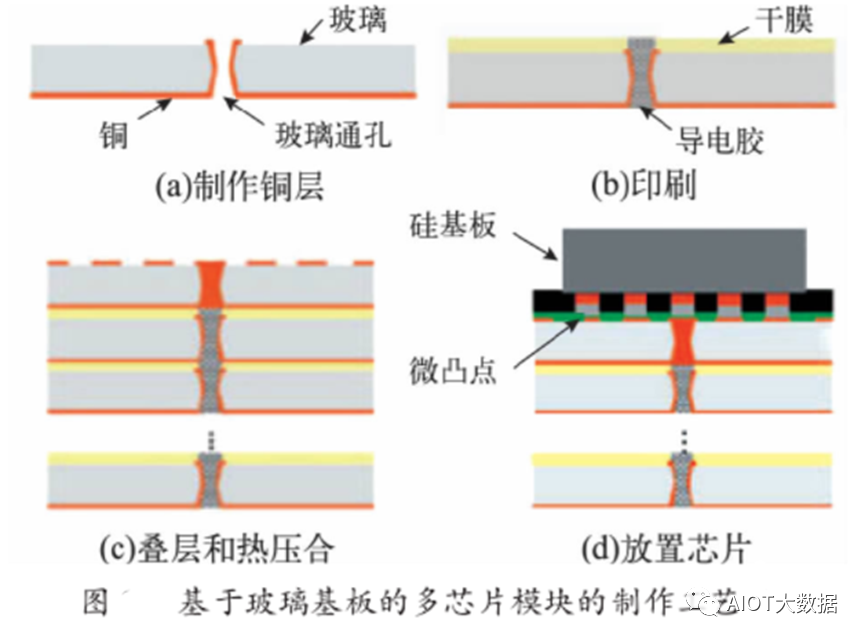

2018年IWAI等使用導電膠填充玻璃通孔,從而實現多層玻璃基板堆疊,在回流過程中,通過該方案制作的多層玻璃基板的翹曲比傳統有機基板要小,通過該技術可以實現高密度布線,同時具有較高的可靠性。2019年,IWAI等在多層玻璃基板的技術基礎上,完成了一個多芯片封裝的結構。其工藝流程如圖:

五、目前主要廠商的先進封裝進展

目前,國內外主要的代工廠和封測廠都有布局相應的先進封裝產能,國外的代工廠和封測廠在技術實力上處于領先地位,在2.5D/3D先進封裝的細分領域,在TSV工藝上,臺積電和英特爾處于領先地位,在TGV工藝上,領先的是康寧和德國LPTK。國內的封測廠商如長電、華天、通富微都有相關技術的研究儲備。半導體各細分子行業中,國內企業在封測領域與國際巨頭的差距相對較小,同時,國內新建的晶圓廠逐漸進入量產階段,產能較大幅度地提升將成為國內封測企業步入快速發展通道的有效驅動力,從國內幾家領先封測企業的擴產來看,預計國內先進封測企業的高端先進封裝將進一步擴大量產規模。同時,經過多年的技術和經驗積累,封測行業進入門檻逐漸提升,領先企業迎發展黃金期。

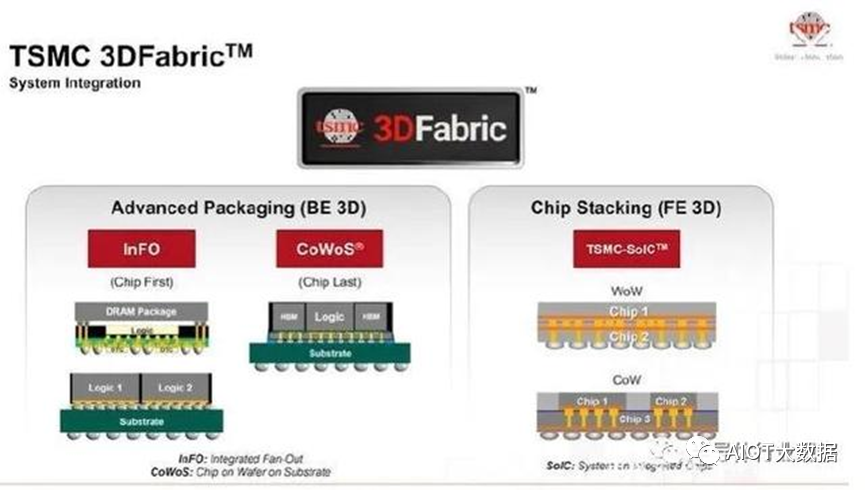

1、臺積電

2012年,TSMC與Xilinx一起推出了當時最大的FPGA,它由四個相同的28nmFPGA芯片并排安裝在中間層上。他們還開發了硅通孔(TSV),微凸點和再分布層(re-distribution-layer:RDL),以將這些組件連接在一起。臺電基于其構造,封裝這種封裝解決方案,稱為CooS(Chip-on-Wafer-Substrate)。支持的封裝技術已成為高和高功率設計的實際行業標準。

臺積電于2017年推出了InFO(IntegratedFanOuttechnology)技術。它使用聚酰胺薄膜代替了CoWoS中的中間層,從而降低了單體成本和高度,這也是臺積電成功應用的重要標準。貨了海量用于智能手機的InFO設計。

臺積電于2019年又推出了集成芯片系統(SoIC)技術。借助前端(國外工廠)設備,臺積電可以非常合理的壓地,然后使用大量的吸塑的銅吸附進行焊(壓焊)設計,以更小的形狀因數,裝扮和能力。這兩種技術就逐漸演成了今天的3DFabric。

臺積電將他們的2.5D和3D封裝產品合并為一個單一的、全面的品牌3DFabric。

其中,2.5D封裝技術CoWoS可分為CoWoS和InFO系列。首先看CoWoS技術,可以分為以下幾種:

1)、CoWoS-S

用于die到die再分布層(redistributionlayer:RDL)連接的帶有硅中介層的“傳統”基板上晶圓上芯片(chip-on-wafer-on-substratewithsiliconinterposer)正在慶祝其大批量制造的第10年。

2)、CoWoS-R

CoWoS-R選項用有機基板中介層取代了跨越2.5Ddie放置區域范圍的(昂貴的)硅中介層。CoWoS-R的折衷是RDL互連的線間距較小——例如,與CoWoS-S的亞微米間距相比,有機上的間距為4微米。

3)、CoWoS-L

在硅–S和有機–R中介層選項之間,TSMCCoWoS系列包括一個更新的產品,具有用于相鄰die邊緣之間(超短距離)互連的“本地”硅橋。這些硅片嵌入有機基板中,提供高密度USR連接(具有緊密的L/S間距)以及有機基板上(厚)導線和平面的互連和功率分配功能。

再看2.5D封裝技術InFO。

據介紹,InFO在載體上使用(單個或多個)裸片,隨后將這些裸片嵌入moldingcompound的重構晶圓中。隨后在晶圓上制造RDL互連和介電層,這是“chipfirst”的工藝流程。單dieInFO提供了高凸點數選項,RDL線從芯片區域向外延伸——即“扇出”拓撲。如下圖所示,多dieInFO技術選項包括:

InFO-PoP:“package-on-package”

InFO-oS:“InFOassembly-on-substrate”

臺積電的3D封裝技術則是SoIC。據臺積電介紹,公司的3D封裝與SoIC平臺相關聯,該平臺使用堆疊芯片和直接焊盤鍵合,面對面或面對背方向-表示為SoIC晶圓上芯片(chiponwafer)。硅通孔(TSV)通過3D堆棧中的die提供連接。SoIC開發路線圖如下所示——例如,N7-on-N7芯片配置將在21年第四季度獲得認證。

?

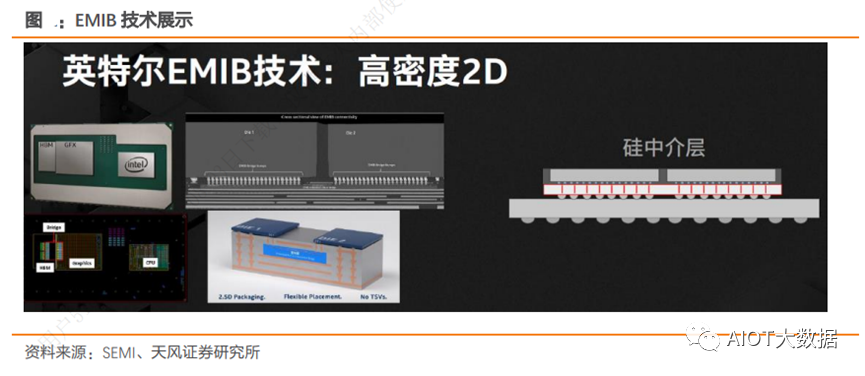

2、英特爾

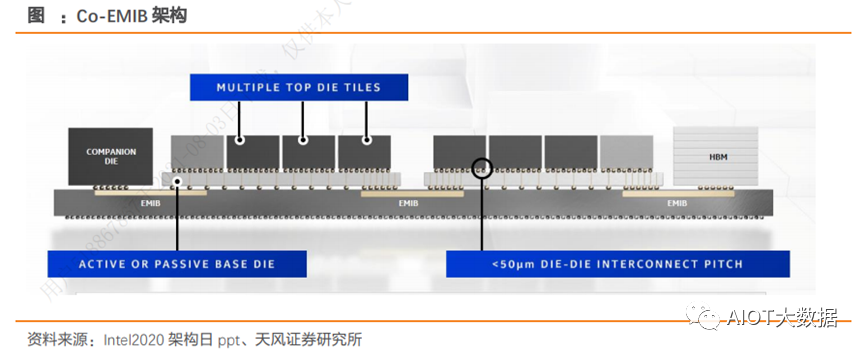

在2D的平面多芯片封裝,英特爾獨有的競爭優勢是嵌入式多芯片互連橋接(EMIB)技術,可以實現更好的導線密度。在硅中介層硅通孔上放不同的裸片連接到整個基板,只需在局部進行高密度布線,而不必在全部的芯片上進行高密度布線,使成本大幅降低同時性能也得到優化。

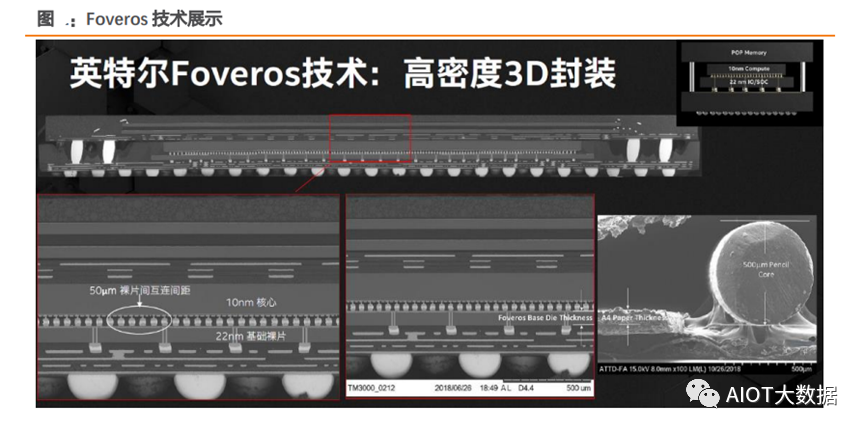

而在3D高密度微縮方面,英特爾的Foveros技術將多個單片連接到基礎裸片,然后進行底層填充實現中間互連并進行注塑來保護整個芯片,使用焊接的技術已經可以做到20-30微米,而通過無焊料銅與銅的接口互連可突破20微米的瓶頸。

而在未來,封測技術相比較于現有的Foveros技術會更進一步。相比較于現有的技術,未來的凸塊間距將會由50um縮小至10um,電路將更小更簡潔,能耗也會更低。

Foveros技術與EMIB集成產生了Co-EMIB(通過EMIB和Foveros兩個技術之間的集成把2D和3D芯片進行融合)。Co-EMIB可以把超過兩個不同的裸片進行水平和垂直方向疊加,以實現更好的靈活度。

全方位互連(ODI)改變了常規疊加方式下基礎裸片尺寸必須大于上面疊加所有小芯片總和的限制。ODI的架構通過傳統的硅通孔技術,使頂層小芯片可以與下方的芯片互連,這樣就可以通過底層封裝直接對上方小芯片進行供電,并保持上、下方裸片間直接互連。AdelElsherbini介紹,通過這種并排互連形式延遲可下降2.5倍,功耗可以降低15%,帶寬可以提高3倍。根據英特爾對先進封裝的路線預測,在未來凸塊間距將縮小至10um級別,密度將達到10000每平方毫米,能耗也會降低至0.05pj/bit。而ODI和CO-EMIB技術的應用,也會使先進封測進一步擴展應用范圍。

先進封裝的制程演進同先進制造工藝的制程呈現出同步趨勢。在臺積電等半導體制造廠制程逐漸進入5nm以下之際,先進封裝的凸塊間距也會逐漸進入10-20um區間。

3、康寧

康寧公司是全球頂尖材料科學創新公司之一,在逾160年間提出多項玻璃解決方案,包括用于電子應用方面的液晶顯示器(LCD)基板,以及用于電視機、智慧型手機和平板電腦等消費性電子裝置,極為耐用的保護玻璃。

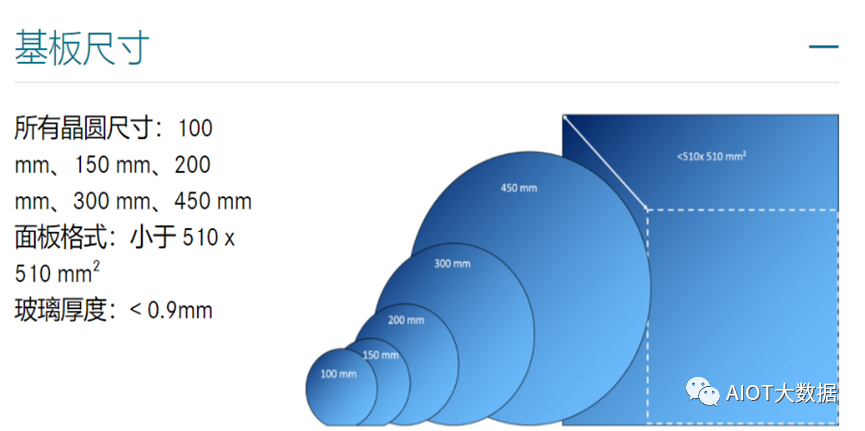

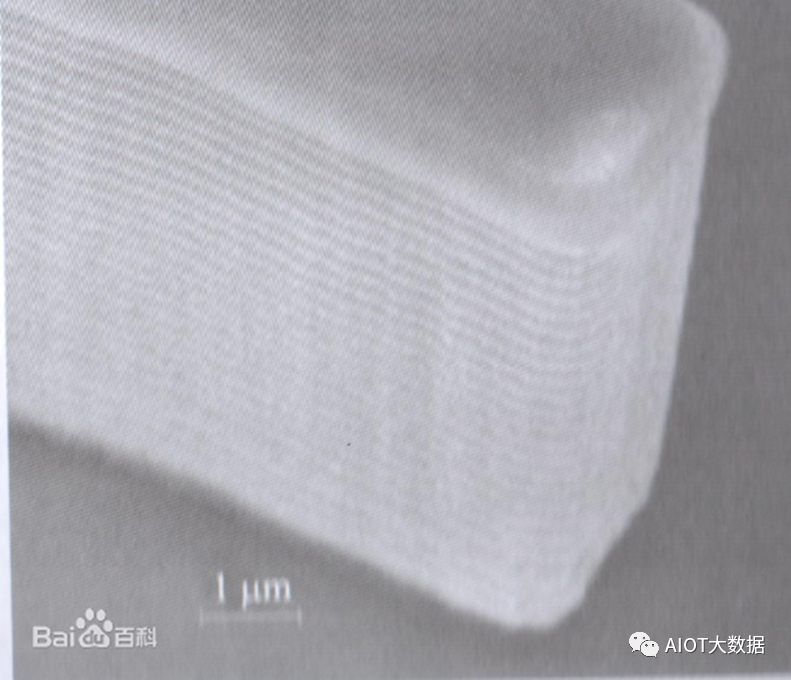

熔融制程為康寧的專利創新技術核心。這項高度精準且自動化的熔融下拉制程,生產出表面極為純凈光滑又平坦,且尺寸穩定的玻璃基板——這剛好是3DIC基板所要求的特性。

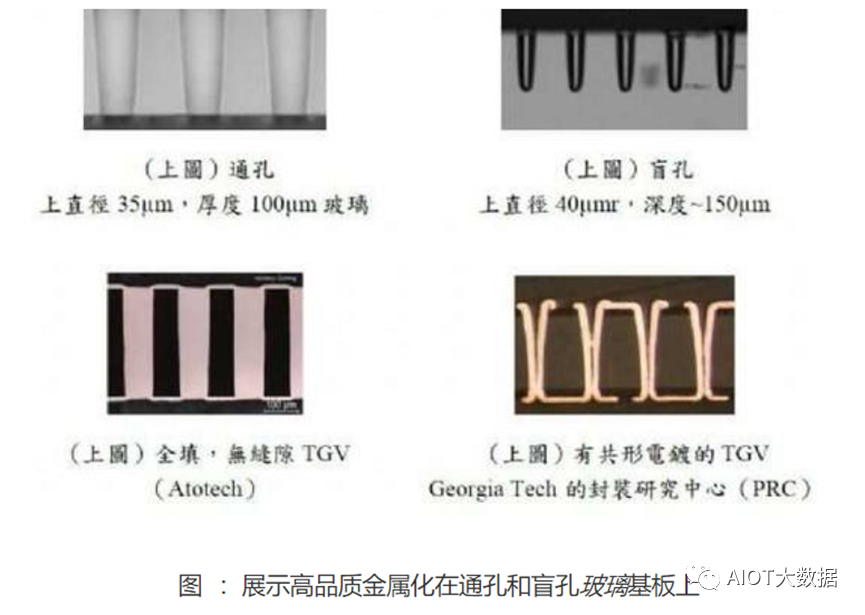

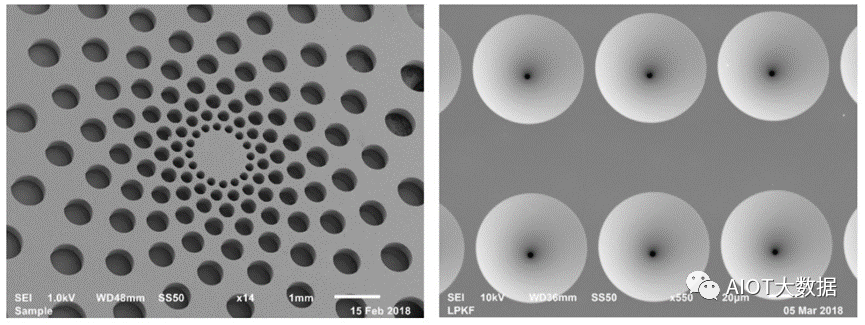

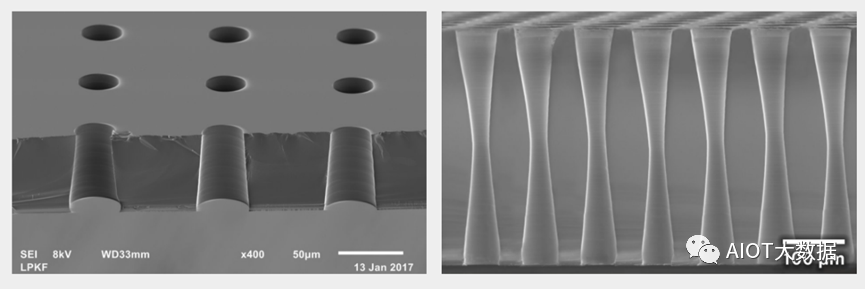

能夠利用現有晶圓和面板設備制程是非常重要的一件事,盲孔填滿金屬化是最適用于現行以晶圓為基礎的設備,而通孔金屬化則最適合用于許多以面板為基礎的制程。康寧已開發出制作高品質孔洞的先進制程,能在薄型(像是100μm)和厚型(例如700μm)玻璃上制作通孔和盲孔(請上圖)。

再者,康寧已與產業領導廠商進行密切合作,運用以晶圓與面板為基礎的金屬化方式來填充玻璃孔洞。TGV基板的填充方式與終端應用息息相關,成本、生產能力、導電性、密閉度等要求會影響到金屬化的方式。因此康寧與產業多個單位合作,像是RTI、Atotech、i3Electronics、工研院(ITRI)、GeorgiaTech的封裝研究中心等,證明出完整的金屬化技術的適用性和可用性。此用來驗證的玻璃基板晶片測試結果顯示出,相對于矽基板,使用玻璃孔洞能達到更好的電性、熱和可靠性表現(請見上圖)。

利用面板相關制程來達到經濟規模制造的能力,是另一項落實成本效益的重要因素。目前業界已有許多設備能被應用來制造面板形式的穿孔玻璃載板和其對應的電子元件,包括填孔步驟和微影制程。

日前康寧已與RudolphTechnologies、i3Electronics與Atotech完成合作,證明出運用現有機臺設備來制造面板形式的穿孔玻璃載板和其電子元件,包括填孔步驟和微影制程。RDL(RedistributionLayers)的結果顯示出,能準確將金屬鍍在玻璃上(請見上圖)。

據麥姆斯咨詢報道,CorningIncorporated(康寧)和MenloMicro(以下簡稱Menlo)近日聯合宣布,Menlo革命性數字微開關(DMS)技術平臺的開發實現了重要的里程碑,Menlo將重塑電子系統最基本的構建模塊——電子開關。兩家公司共同發布展示了成功整合的玻璃通孔(TGV)封裝技術,使Menlo的高性能RF和功率產品擴展至超小型晶圓級封裝。

TGV相比傳統的鍵合封裝技術,使Menlo的產品尺寸縮小了60%以上,使其更理想地適用于那些信道密度增長,同時尺寸、重量、功率和成本降低的非常重要應用。Menlo將在本周于美國費城舉辦的IEEEMTT國際微波會議上展示這項技術。

此外,除了顯著的尺寸減小,TGV還為Menlo的DMS產品帶來的重要的性能優勢。通過更短且良好控制的金屬化通孔替代鍵合,現在Menlo得以降低75%以上的封裝寄生效應。這將幫助Menlo的產品支持更高的頻率,這對于先進的無線通訊系統、測試儀器以及眾多的航空和國防應用,正變得越來越重要。與此同時,玻璃相比硅等傳統的基板材料具有獨特的性能,可實現更低的RF損耗和更高的線性度,意味著系統將獲得更低的功耗和更高的整體效率。

通過利用TGV封裝技術,Menlo正在開發覆蓋DC~18GHz帶寬的RF產品,并有能力逐步擴展至50GHz以上。其DMS平臺可為RF和AC/DC產品實現數十種高價值應用,包括電池管理、家居自動化、電氣化汽車、軍事和專業無線電、無線基站以及物聯網等廣泛市場。

?

4、德國LPKF

LPKF深耕激光領域多年,對于如何將激光作為工具集成為功能強大的設備有著豐富的技術經驗。LPKF激光系統立足于助力高科技領域的進步。無論是移動系統、通信系統、電力以及數字娛樂等,最終目標都是加工產品的速度更快、尺寸更小、更節能。德國LPKF始終保持著在激光技術領域的領先地位。我們的激光系統在印刷電路板、微芯片、汽車零部件、太陽能電池板以及許多其他零部件的工藝制造中都起著至關重要的作用。

憑借幾十年的激光加工經驗,LPKF提供了前沿的技術解決方案,具有更高的精度、成品率和成本效率等系統優勢,引領不斷走向小型化的趨勢。該產品包含許多優勢:一種新型玻璃通孔(TGV)加工工藝全面開啟了薄片玻璃作為封裝基板的潛力。厚度介于50微米至500微米之間的薄片玻璃是一種非常適用于高密度高頻應用的封裝基板材料。LPKF運用激光這種非接觸精密加工工具開發的創新LIDE工藝能夠以無以倫比的效率和質量微加工玻璃通孔。

LPKF的最小通孔直徑為10μm。通常,一個基板上的所有微孔都顯示相同的直徑。通過應用多次蝕刻運行,不同的直徑是可能的。縱橫比在1:10的范圍內,但根據玻璃類型,它也可以高達1:50。LIDE生成的微孔側壁光滑、無裂紋、無碎屑和無應力,可實現可靠的金屬化。錐角在0.1°-30°之間。LIDE制造的微孔通常呈沙漏形狀。通過將蝕刻限制為僅從先前修改過的玻璃的一側進行,V形微孔是可能的。加工的尺寸選擇如圖:

5、中芯長電

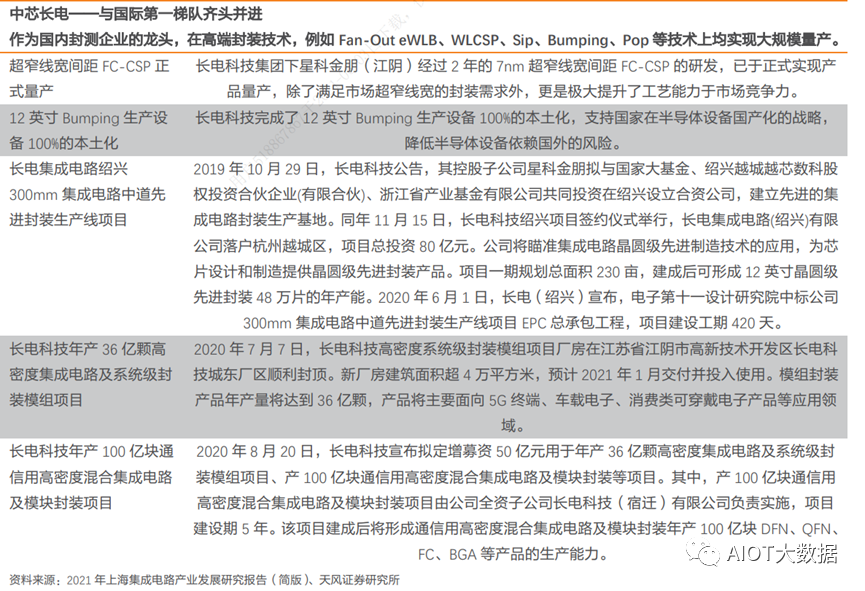

長電科技是全球領先的封測廠商,聚焦關鍵應用領域,在5G通信類、高性能計算、消費類、汽車和工業等重要領域,業務覆蓋高/中/低端全品類,已成為中國第一大和全球第三大封測企業。公司封測產能多地布局,互為補充,各具技術特色和競爭優勢;公司在主要封裝領域內掌握多項核心技術,在先進封裝技術覆蓋度上與全球第一的日月光集團旗鼓相當,具備行業領先的SiP、WL-CSP、FC、eWLB、PiP、PoP及2.5/3D等高端封裝技術,并定增50億元加碼SiP、QFN、BGA等高端封裝產能。公司與中芯國際戰略互通,可實現代工+封測一體化協同發展。

6、華天科技

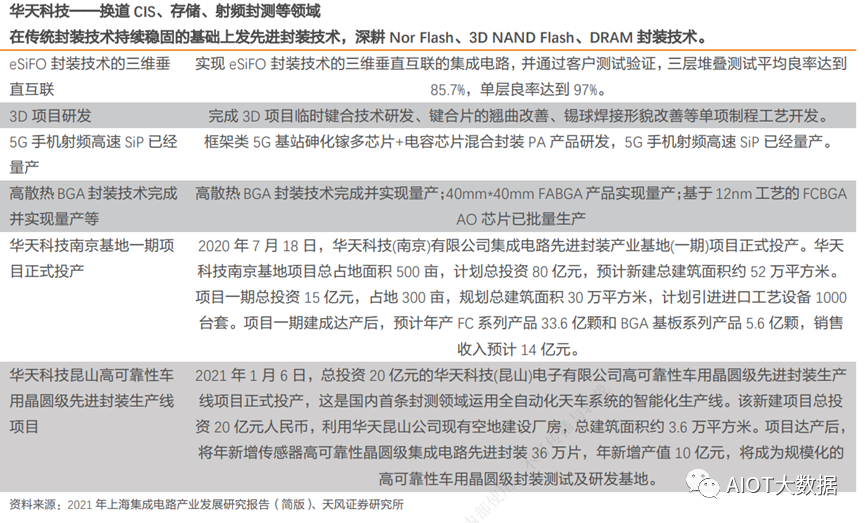

公司在產業布局方面,積極推進先進封裝基地建設,近年來先后投資擴建了昆山、寶雞、南京等基地,打通了CIS芯片、存儲器、射頻等多種高端產品的生產線。2020年7月18日華天科技南京基地舉行了一期項目投產儀式,一期項目已竣工面積16.3萬平方米,實現FC和BGA系列產品年封測量可達40億只,今年可實現產值2億元以上。

研發方面公司重視新產品、新技術、新工藝的研發,研發支出金額逐年增加,已自主研發出了SiP、FC、TSV、MEMS、Bumping、Fan-Out、WLP等高端封裝技術和產品。自2019下半年來,國內半導體封測行業逐步回暖,未來有望隨著新型應用領域和先進封測技術的發展進入新一輪增長。華天科技作為國內領先的集成電路封測企業,產品線布局豐富,技術水平行業領先,有望持續受益行業景氣度及國產替代加速影響,未來發展前景廣闊。

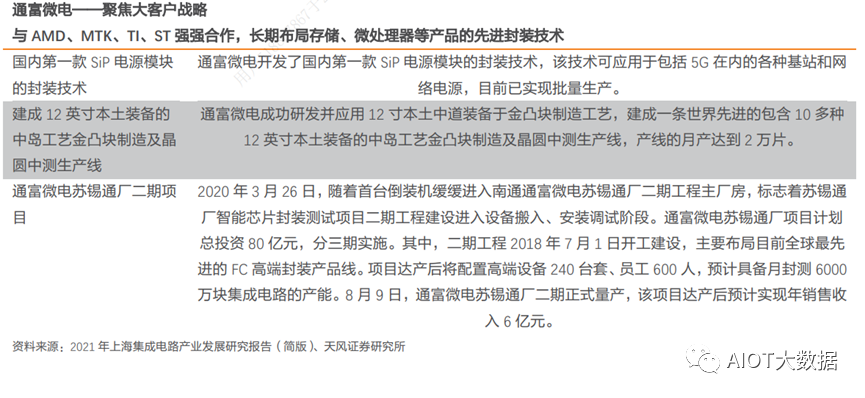

7、通富微電

通富微電為半導體封測龍頭,與AMD、MTK等大客戶共同成長。公司為全球第五大、國內第二大封測廠商,在封測技術上布局全面。早期公司以傳統封裝技術為主,2016年收購AMD蘇州、檳城兩大封測廠,得以深度綁定AMD供應鏈并占據AMD封測訂單的大部分份額。同時公司憑借在高端封裝領域的實力,成為MTK在中國大陸的重要封測合作方。展望未來,公司有望伴隨大客戶份額的提升和市場整體規模的擴大而迎來加速成長。

先進封裝因5G、AI的應用迎來快速成長,公司技術領先有望充分受益。傳統封測市場近年增速較為平穩,2011-2018年市場年復合增速在3%,至2018年空間達560億美元。然而,隨著摩爾定律的放緩,半導體性能的提升越來越多依賴于封裝技術的進步,從而對封裝技術提出更高要求。具體來看,隨著5G、AI芯片的大規模應用,以及終端設備小型化趨勢的演繹,全球先進封裝市場有望快速成長:據Yole預計,先進封裝市場至2024年有望達440億美元,2018-2024年CAGR達8%。公司通過對AMD蘇州、檳城廠的收購,增強了先進封裝的技術實力,未來有望充分受益于先進封裝市場的快速增長。

MiniLED玻璃背板TGV工藝現狀

隨著集成電路技術的發展,摩爾定律逐步放緩,半導體產業朝著延續摩爾定律和拓展摩爾定律的兩個方向發展。其中,拓展摩爾定律重要的技術手段是先進封裝;2.5D/3D集成技術將平面集成電路擴展到了第三維度,顯著提升了空間的利用率。與傳統的2D平面集成技術相比,三維集成技術通過垂直互連結構傳輸信號,具有集成度高、功耗低、設計靈活、易實現異質集成等優勢。

在三維集成電路中,硅通孔(TSV)和玻璃通孔(TGV)是常用的兩種通孔互聯加工方式,具有縮短路徑和更薄的封裝尺?等優點。其中,TGV技術由TSV技術演化而來,是制造三維集成電路的關鍵技術。所謂TGV技術,指的是通過在玻璃晶圓上加工微納尺寸的通孔或盲孔,并向其中填充導體材料(例如Cu),從而實現芯片與芯片之間、晶圓與晶圓之間的垂直導通。硅用作垂直互聯的中介層(Interposer)時,需要沉積額外的絕緣層(例如氧化硅)用于電隔離,這種絕緣層厚度通常為亞微米級,在高頻信號傳輸中難以在TSV之間提供良好的電隔離,易引入寄生電容。玻璃材料沒有?由移動的電荷,介電性能優良,熱膨脹系數(CTE)與硅接近,以玻璃替代硅材料的TGV技術可以避免TSV的問題。此外,TGV技術?需制作絕緣層,降低了?藝復雜度和加?成本。TGV技術在光通信、射頻、微波、微機電系統、微流體器件和三維集成領域有?泛的應?前景。

TGV和TSV

玻璃通孔(TGV)技術被認為是下一代三維集成的關鍵技術,該技術的核心為深孔形成工藝。感應耦合等離子體(ICP)刻蝕技術是半導體領域中深孔形成的重要手段之一。本文通過正交實驗設計方法,研究ICP石英玻璃刻蝕工藝中工作壓強、C4F8流量、Ar流量三個工藝參數對深孔刻蝕的影響,探索提高刻蝕速率的優化組合。實驗結果表明,C4F8流量對玻璃刻蝕速率有顯著影響,并且隨著C4F8/Ar流量比減小,側壁角度垂直性越好。實驗為TGV技術開發和應用提供了實驗依據。

隨著半導體制造工藝向深亞微米及納米級發展,傳統的光刻技術逐漸接近極限,集成電路晶體管數目的增加和特征尺寸的縮小越發緩慢和困難,“摩爾定律”的延續面臨巨大挑戰。同時,傳統封裝中信號傳輸距離長帶來的互連延遲問題日益嚴重,難以滿足芯片高速和低功耗的要求。為克服集成電路和傳統封裝面臨的難題,三維集成技術應運而生。其中硅通孔(ThroughSiliconVia,TSV)技術被認為是實現三維集成最有前景的技術。

TSV技術通過在芯片與芯片、晶圓與晶圓之間制作垂直通孔,實現芯片之間的直接互連。它能夠使芯片在三維方向堆疊的密度最大、芯片間的互連線最短、外形尺寸最小,顯著提高芯片速度,降低芯片功耗,因此成為目前電子封裝技術中最引人注目的一種技術。然而,硅是一種半導體材料,TSV周圍的載流子在電場或磁場作用下可以自由移動,對鄰近的電路或信號產生影響,影響芯片性能。玻璃材料沒有自由移動的電荷,介電性能優良,熱膨脹系數(CTE)與硅接近,以玻璃替代硅材料的玻璃通孔(ThroughGlassVia,TGV)技術可以避免TSV的問題,是理想的三維集成解決方案。此外,TGV技術無需制作絕緣層,降低了工藝復雜度和加工成本。TGV及相關技術在光通信、射頻、微波、微機電系統、微流體器件和三維集成領域有廣泛的應用前景。

TGV在半導體先進封裝領域的應用。玻璃通孔(TGV)和硅通孔(TSV)工藝相比TGV的優勢主要體現在:

1)優良的高頻電學特性。玻璃材料是一種絕緣體材料,介電常數只有硅材料的1/3左右,損耗因子比硅材料低2-3個數量級,使得襯底損耗和寄生效應大大減小,保證了傳輸信號的完整性;

2)大尺寸超薄玻璃襯底易于獲取。Corning、Asahi以及SCHOTT等玻璃廠商可以提供超大尺寸(>2m×2m)和超薄(<50μm)的面板玻璃以及超薄柔性玻璃材料。

3)低成本。受益于大尺寸超薄面板玻璃易于獲取,以及不需要沉積絕緣層,玻璃轉接板的制作成本大約只有硅基轉接板的1/8;

4)工藝流程簡單。不需要在襯底表面及TGV內壁沉積絕緣層,且超薄轉接板中不需要減薄;

5)機械穩定性強。即便當轉接板厚度小于100μm時,翹曲依然較小;

6)應用領域廣泛,是一種應用于晶圓級封裝領域的新興縱向互連技術,為實現芯片-芯片之間距離最短、間距最小的互聯提供了一種新型技術途徑,具有優良的電學、熱學、力學性能,在射頻芯片、高端MEMS傳感器、高密度系統集成等領域具有獨特優勢,是下一代5G、6G高頻芯片3D封裝的首選之一。

TGV的成形工藝主要包括噴砂、超聲波鉆孔、濕法刻蝕、深反應離子刻蝕、光敏刻蝕、激光刻蝕、激光誘導深度刻蝕以及聚焦放電成孔等。

TGV技術面臨的關鍵問題是沒有類似硅的“Bosch”深刻蝕工藝,難以快速制作高深寬比的玻璃深孔或溝槽。傳統的噴砂法、濕法刻蝕法和激光鉆孔法等均存在一定的局限性。感應耦合等離子體(ICP)干法刻蝕技術控制精度高,刻蝕表面平整光滑,垂直度好,常用于刻蝕高深寬比結構。近年來,國內外的研究單位在等離子體玻璃刻蝕方面進行了大量的實驗研究。氣體成分主要采用碳氟氣體、SF6與Ar、He等不同惰性氣體的組合。文獻報道的最高刻蝕速率可以達到1.7μm/min,但各向同性刻蝕嚴重。由于玻璃襯底上掩膜沉積工藝的限制,在深孔刻蝕時,需要一定的刻蝕選擇比。在保證側壁垂直性與刻蝕選擇比的同時提高玻璃刻蝕速率成為目前研究的難點。

ICP玻璃刻蝕基本原理

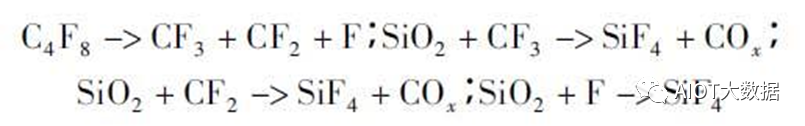

實驗采用北方微電子公司的GSE200C刻蝕機臺。系統有兩路頻率均為13.56MHz的射頻功率源。射頻源功率連接真空反應腔室上方的線圈來激發腔室內的刻蝕氣體,射頻偏壓功率連接真空反應腔室內的靜電卡盤來控制離子能量和方向。石英玻璃的主要成分為SiO2,Si-O鍵的鍵強為200kcal/mol(約8eV),大于Si-Si鍵80kcal/mol(約3.4eV)鍵強的2倍,這是SiO2的ER慢于Si的主要原因。因此,SiO2刻蝕以物理刻蝕為主,化學刻蝕為輔,通常采用碳氟氣體,如CF4、CHF3、C4F8等,并加入一定量的惰性氣體。一般來說,碳原子數與氟原子數的比越高,就能形成越多的聚合物和越高的刻蝕選擇比,有利于深孔刻蝕,故本實驗碳氟氣體選用C4F8。惰性氣體中He、Ar為半導體工藝常用氣體,且成本較其他惰性氣體有優勢。而相比于He,Ar具有用于物理刻蝕的相對大的質量,有利于提高SiO2的ER,故本實驗惰性氣體選用Ar。C4F8在等離子體放電過程中主要離解為C2F4,C2F4進一步離解為更小的CFx自由基。在CFx(CF,CF2,CF3)自由基中,CF2含量最多。

工藝過程中主要反應為:

其中硅通孔(TSV)的Bosch工藝是指在集成電路制造中為了阻止或減弱側向刻蝕,設法在刻蝕的側向邊壁沉積一層刻蝕薄膜的工藝。因最早由RobertBosch提出,亦被稱為Bosch工藝。

1993年,RobertBosch提出了一種ICP刻蝕工藝技術,被稱作“Bosch工藝”。

這種工藝首先采用氟基活性基團進行硅的刻蝕,然后進行側壁鈍化,刻蝕和保護兩步工藝交替進行。圖1說明了其工藝過程。它是通過交替轉換刻蝕氣體與鈍化氣體實現刻蝕與邊壁鈍化。其中刻蝕氣體為SF6,鈍化氣體為C4F8。C4F8在等離子體中能夠形成氟化碳類高分子聚合物。它沉積在硅表面能夠阻止氟離子與硅的反應。刻蝕與鈍化每5~10s轉換一個周期。在短時間的各向同性刻蝕之后即將剛剛刻蝕過的硅表面鈍化。在深度方向由于有離子的物理濺射轟擊,鈍化膜可以保留下來,這樣下一個周期的刻蝕就不會發生側向刻蝕。通過這種周期性“刻蝕-鈍化-刻蝕”,刻蝕只沿著深度方向進行。

反應離子深度刻蝕硅的水平可以達到在表面1%暴露刻蝕面積的情況下,刻蝕速率可以達到50μm/min,在表面20%暴露刻蝕面積的情況下,刻蝕速率可以達到30μm/min,硅與光刻膠的抗刻蝕比大于300:1,刻蝕的深寬比大于100:1[2]。

在Bosch工藝中由于刻蝕與鈍化的互相轉換,而每一步刻蝕都是各向同性的,因此造成刻蝕邊壁表面的波紋效應(scalping)。圖2是典型的由于Bosch工藝形成的邊壁波紋。邊壁波紋可形成高達100nm以上的表面粗糙度。通過縮短刻蝕與鈍化的周期可以減弱這種波紋效應。通過優化Bosch刻蝕工藝可以實現70μm深的邊壁表面波紋起伏小于20nm。這種深刻蝕的邊壁足以作為光反射鏡面進行光纖通信開關轉換。另一種減少邊壁波紋粗糙度的方法是在刻蝕后進行化學濕法拋光腐蝕,例如將刻蝕樣品放入KOH+IPA混合腐蝕液中短暫時間,將表面的波紋起伏腐蝕平滑。

前面提到的低溫刻蝕不會形成所謂“波紋”效應,因為低溫刻蝕不需要氣體轉換過程。而且由于系統中不引入鈍化氣體,在刻蝕腔體內壁不會形成氟化碳類聚合物的沉淀。在刻蝕系統方面,低溫刻蝕與Bosch刻蝕的區別僅在于一個需要低溫冷卻樣品基板,一個需要氣體轉換,所以可以在同一臺ICP刻蝕系統上同時實現兩種刻蝕方式。

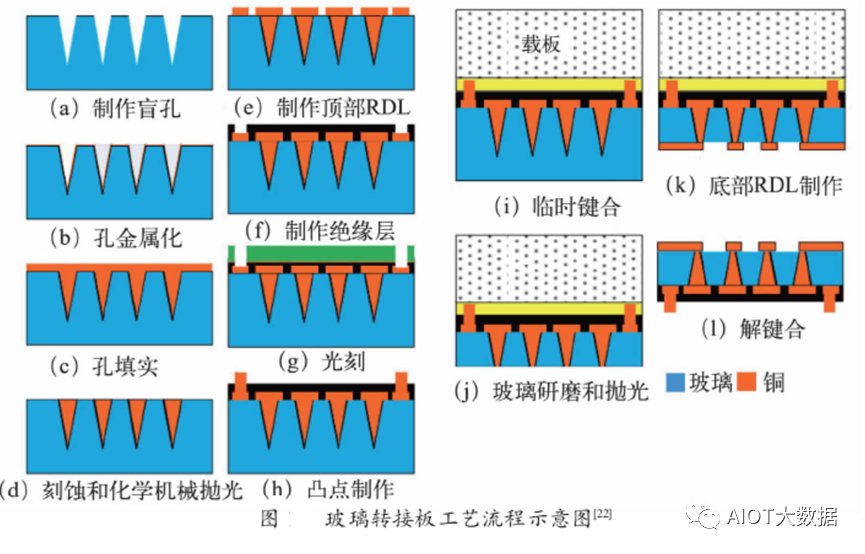

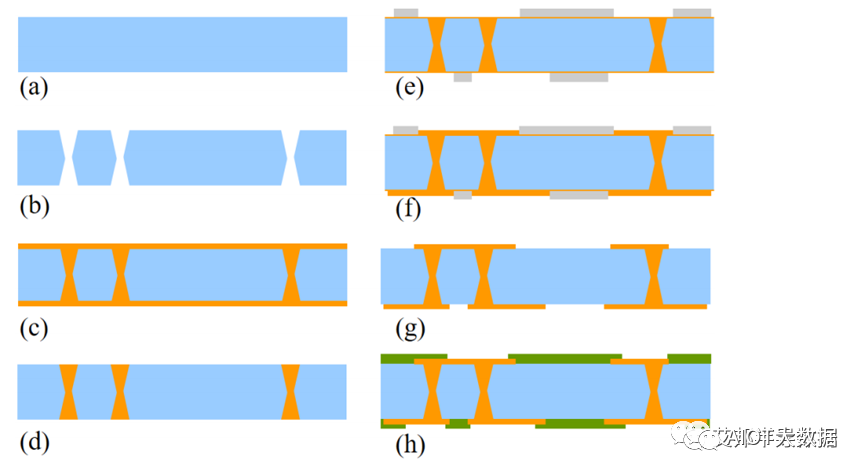

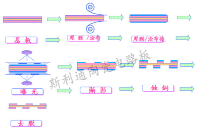

而TGVinterposer的加工流程如圖2,整體方案為先玻璃基板上進行打孔,然后在側壁及表面沉積阻擋層和種子層。阻擋層防止Cu向玻璃襯底擴散,同時增加兩者的粘附性,當然在一些研究中也發現阻擋層不是必須的。然后采用電鍍的方法將Cu沉積,接著退火,并采用CMP的方法將表面Cu層去掉。最后采用PVD鍍膜光刻方法制備RDL重布線層,去膠后最終再形成鈍化層。

圖2,(a)準備晶圓,(b)形成TGV,(c)雙面電鍍-沉積銅,(d)退火及CMP化學機械拋光,去表面銅層,(e)PVD鍍膜及光刻,(f)布置RDL重布線層,(g)去膠及Cu/Ti刻蝕,(h)形成鈍化層

或者采用精密機械加工和半導體技術進行玻璃材質的微納孔及微納米通道制備。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論