在計算機芯片領域,數字越大越好。更多的內核、更高的GHz和更高的FLOPs,都是工程師和用戶所期望的。然而,半導體中有一個指標不斷獲得關注和相關性:越小越好。歡迎來到半導體制造和技術節點(也稱為工藝節點)的世界。

但它到底是什么?為什么它具有如此重要的意義?為什么它以納米為單位來測量,為什么數字10、7和5在本文中占據顯著位置?讓我們進入流程節點的世界吧......

與芯片制造相關的最大營銷術語之一是特征尺寸。

在芯片行業,術語“特征尺寸”與工藝節點相關。正如“CPU 的設計方式,第 3 部分”中所討論的,該術語有些靈活。不同的制造商使用它來描述芯片的不同方面。不久前,它專門表示晶體管兩部分之間的最小間隙。

如今,它更多地是一個營銷術語,對于比較生產方法并不是很有用。盡管如此,晶體管是任何處理器的關鍵特征,因為晶體管組執行芯片內部完成的所有數字處理和數據存儲,并且來自同一制造商的較小工藝節點非常令人垂涎。為什么,你可能會問?

處理器世界中沒有任何活動是瞬時發生的,并且每個操作都需要電能。較大的組件需要更多時間來改變狀態。信號需要更多的時間來傳輸,并且需要更多的能量來在處理器內循環電力。簡而言之,更大的組件占據更多的物理空間,使芯片本身變得更笨重。

我們觀察到三個老式英特爾 CPU。從左到右:2006 年的 Celeron、2004 年的 Pentium M 和 1995 年的較舊 Pentium。它們的工藝節點分別為 65nm、90nm 和 350nm。換句話說,28 年設計中的關鍵部件比 17 年型號的關鍵部件大五倍以上。另一個值得注意的區別是:較新的芯片擁有大約 2.9 億個晶體管,而最初的奔騰芯片擁有超過 300 萬個晶體管,數量減少了近一百倍。

雖然工藝節點的減少有助于最近的設計實現更小的物理尺寸和更高的晶體管數量,但不可否認的是,它在英特爾的進步中發揮了關鍵作用。

但真正的問題是:賽揚產生大約 30W 的熱量,而奔騰僅發出 12W。這種熱量主要來自芯片電路中的電流運動。當電流流動時,能量由于各種過程而耗散,其中絕大多數以熱量的形式釋放。雖然 30 肯定高于 12,但重要的是要記住 Celeron 擁有近 100 倍的晶體管。

鑒于較小的工藝節點提供了更緊湊的芯片的優勢,芯片上裝有更多晶體管,可以更快地切換(這意味著每秒的計算次數更高),并且以熱量形式釋放的能量更少,這自然會提出一個問題:為什么不呢?世界上的每一個芯片都是使用盡可能最小的工藝節點制造的嗎?

要有光!

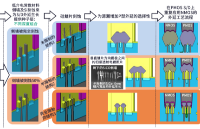

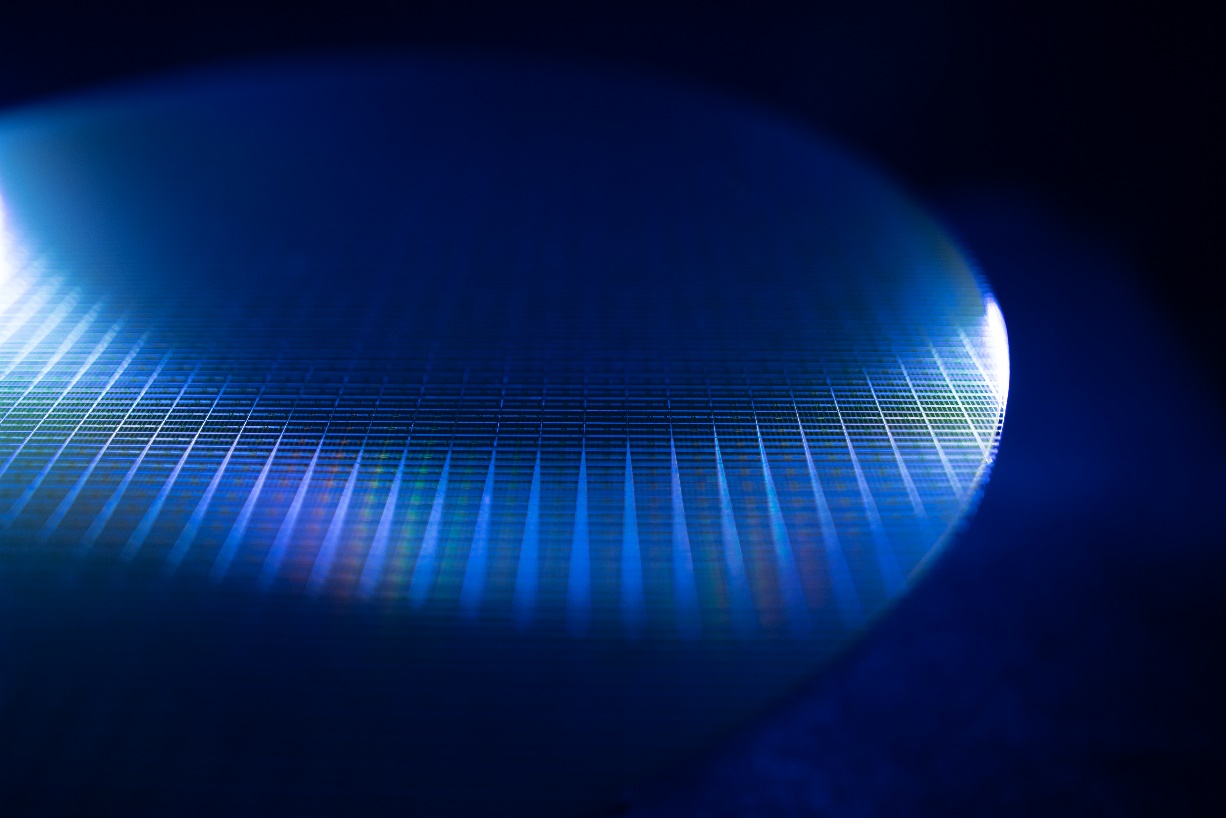

此時,有必要了解一種稱為光刻的工藝。在這里,光線穿過一個稱為光掩模的裝置,該裝置會阻擋某些區域的光線,并允許光線穿透其他區域。光線經過的地方,會集中到一個小區域。然后,這種光與芯片制造中使用的特殊層相互作用,描繪出芯片各個組件的位置。

將其視為類似于手的 X 射線:骨骼阻擋射線,就像光掩模一樣,而肉則允許射線通過,從而產生展示手的內部結構的圖像。

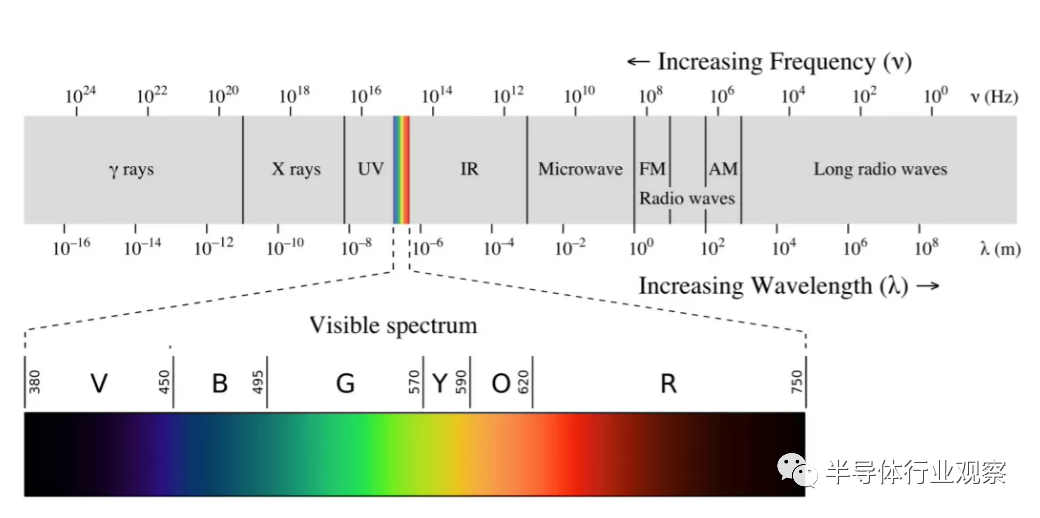

有趣的是,這個過程中并沒有使用實際的光。即使對于像奔騰這樣的舊芯片,光的“尺寸”或波長也太大。現在,您可能想知道地球上的光如何可以具有任意大小,但這是相對于波長的。光是一種電磁波,是電場和磁場的永久振蕩融合。

雖然我們經常用經典的正弦波來表示它以形象化其形式,但電磁波并不真正具有獨特的形狀。相反,它們在相互作用時產生的效果遵循這種正弦波模式。這種振蕩模式的波長表示波上兩個全等點之間的物理距離。

想象一下海浪拍打著海岸;波長是連續波峰之間的距離。電磁波表現出大量可能的波長,因此我們將它們歸入總稱“頻譜”。

小,更小,最小

在下圖中,我們所識別的光只是整個光譜的一小部分。該頻譜包括其他熟悉的實體,例如無線電波、微波、X 射線等。

在此光譜內,光的波長大約為10-7米或大約0.000004 英寸!

對于這種微小的測量,科學家和工程師喜歡使用納米,簡稱“nm”。如果我們深入研究光譜的一部分,我們會觀察到可見光實際上跨越380nm到750nm。

回想一下本文前面提到的芯片 - 它是使用 65 nm 工藝節點制造的。您可能想知道,如何創建比可見光更小的組件?很簡單:光刻過程不使用光,而是使用紫外線(又名 UV)。

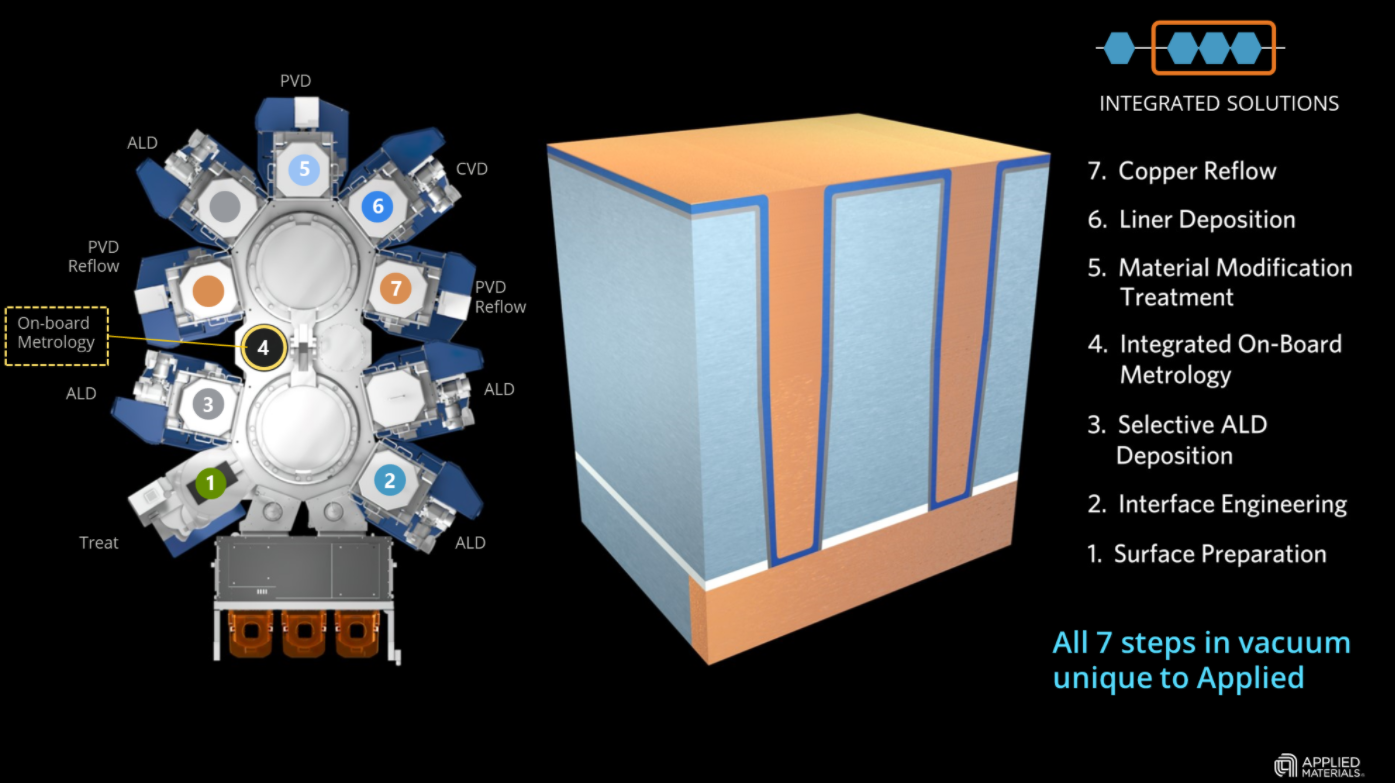

根據光譜圖,紫外線從大約 380 nm(可見光達到峰值)開始,并縮小到大約 10 nm。英特爾、臺積電和 GlobalFoundries 等制造商使用稱為 EUV(極端紫外線)的電磁波,其波長約為 190 nm。這些較短的波長不僅可以生產更小的元件,而且還可能提高其整體質量。這使得各個部件可以更緊密地封裝在一起,有助于縮小芯片的整體尺寸。

不同的制造商為其采用的工藝節點的規模分配不同的名稱。英特爾為其 10 納米節點之一使用了一個朗朗上口的名稱:P1274,但他們經常將其表示為“10 納米”以供外行觀眾使用。相比之下,臺積電只是將他們的產品標記為“10FF”。

AMD 等處理器設計公司創建適合這些較小工藝節點的布局和結構,然后依靠臺積電等制造巨頭進行生產。

臺積電一直在努力推進更小的節點(7nm、5nm、3nm),為蘋果、聯發科、高通、Nvidia 和 AMD 等主要客戶制造芯片。在這個制造領域,一些最微小的特征的寬度僅為 6 納米(盡管許多特征要大得多)。

為了理解 6 nm 的微小程度,請考慮以下情況:構成處理器主要部分的硅原子間隔約 0.5 nm,每個原子的直徑約為 0.1 nm。因此,粗略估計,臺積電的設施可處理寬度小于 10 個硅原子的晶體管元件。

瞄準原子的挑戰

拋開芯片制造商正在努力實現僅跨越幾個原子的功能這一令人難以置信的現實,EUV光刻技術提出了一系列嚴峻的工程和制造挑戰。

英特爾在將其10納米生產與其14納米工藝的效率相匹配方面面臨著相當大的挑戰,而 GlobalFoundries在縮小到7納米甚至更小的工藝方面也遇到了一系列問題。雖然英特爾和 GlobalFoundries 面臨的復雜情況可能不僅僅源于 EUV 光刻的復雜性,但兩者不太可能完全無關。

電磁波的波長越短,它所蘊含的能量就越多。這種較高的能量水平存在在芯片制造過程中造成損壞的風險。超精密制造極易受到所用材料的污染和缺陷的影響。此外,衍射極限和統計噪聲等因素(EUV 波的能量沉積到芯片層上的位置的固有差異)阻礙了生產完美芯片的愿望。

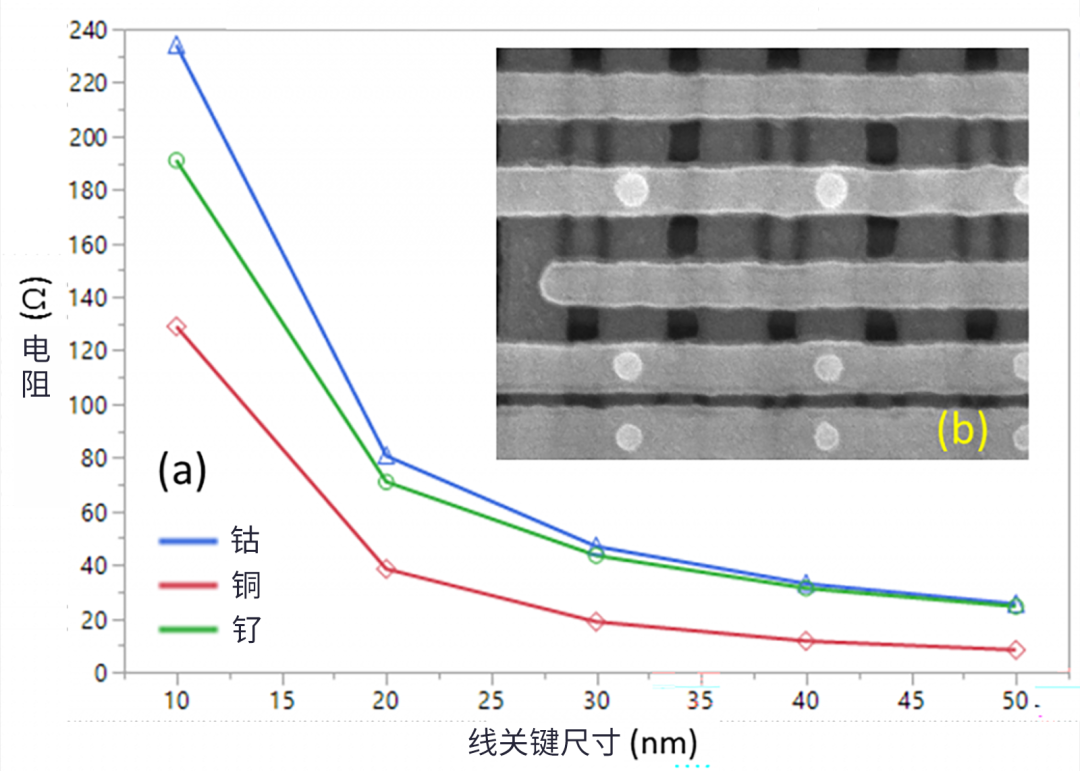

在原子層面,對電力和能量傳輸的傳統理解不再牢固。確保電流(以移動電子(三種亞原子粒子之一)的形式)通過緊密放置的導體在熟悉的尺度上相當簡單;人們可以簡單地將導體包裹在堅固的絕緣層中。

然而,在英特爾和臺積電的運營規模下,這項任務變得令人畏懼,主要是因為絕緣層不夠厚。然而,就目前而言,大多數生產挑戰可歸因于 EUV 光刻技術固有的復雜性。因此,我們可能還得再等幾年,然后才能在論壇上就 Nvidia 在處理量子行為方面相對 AMD 的優勢展開毫無意義的爭論,反之亦然。

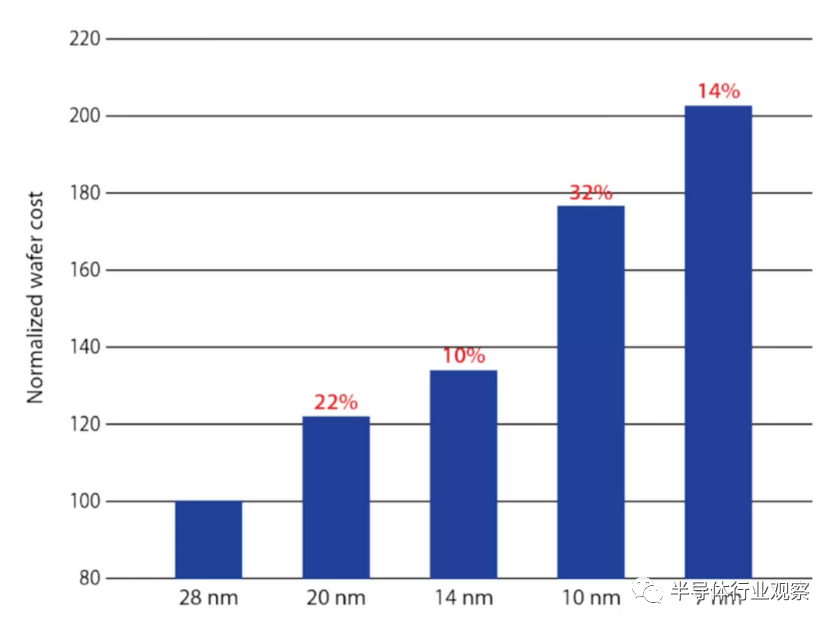

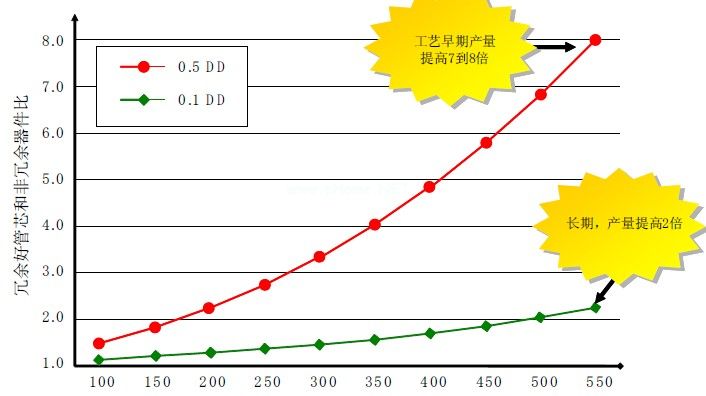

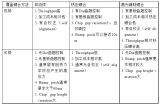

這是因為真正的問題,生產困難背后的最終原因,是英特爾、臺積電和他們所有的制造伙伴都是企業,他們瞄準原子的唯一目的是創造未來的收入。在 Mentor 的一篇研究論文中,對于較小工藝節點的晶圓成本增加了多少,提供了以下概述......

我們假設 Intel 的 28 nm 工藝節點用于其 Haswell CPU 系列(例如 Core i7-4790K)。如果是這樣,他們的 10 nm 方法每片晶圓的成本幾乎翻倍。雖然晶圓可以生產的芯片數量很大程度上取決于芯片尺寸,但較小的工藝節點可能允許每晶圓更高的芯片產量,從而在一定程度上抵消成本的上升。最終,制造商將嘗試通過提價將盡可能多的成本轉移給消費者。然而,他們必須考慮市場需求取得平衡。

過去十年中智能手機(以及為其提供動力的 SoC)銷量的激增,以及家庭和汽車智能技術近乎指數級的增長,意味著芯片制造商被迫承受因采用更小型工藝節點而帶來的財務損失直到整個系統足夠成熟,可以生產出高產量的晶圓。

這種情況將持續下去,直到他們的系統足夠成熟,能夠持續批量生產高產量晶圓(缺陷最少)。

鑒于賭注高達數十億美元,這是一項不穩定的努力。這種財務賭博是 GlobalFoundries 退出工藝節點競賽的部分原因。

前景

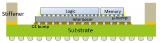

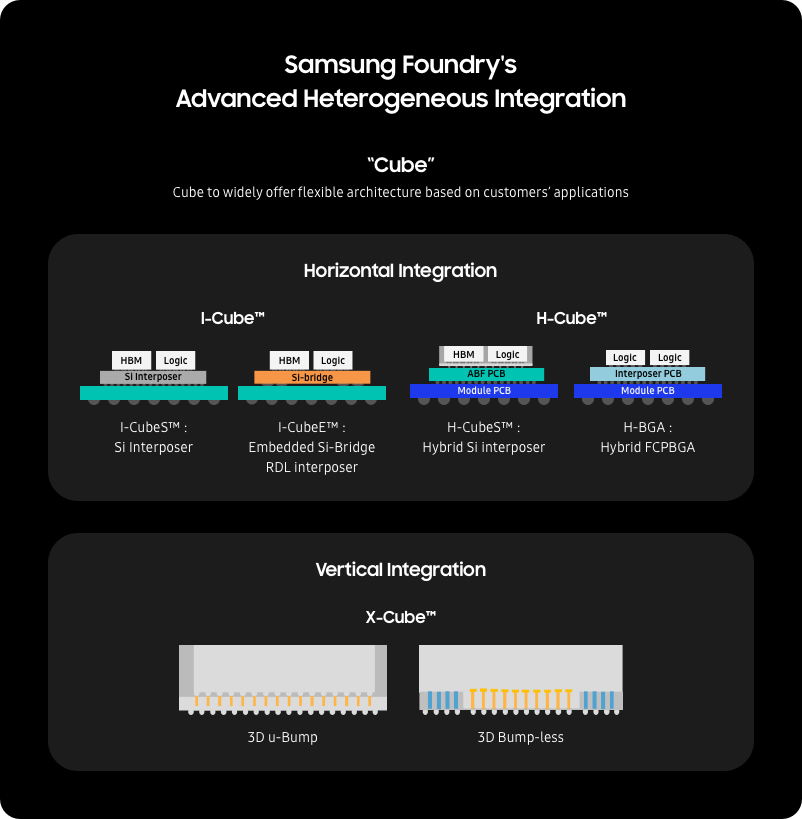

如果這一切聽起來有些悲觀,那么重要的是要記住,不久的將來是充滿希望的。三星和臺積電的 7 納米生產線已成功運營一段時間,產量和收入令人印象深刻。此外,芯片設計人員通過在產品中利用多個節點來保證他們的設計面向未來。

AMD 針對 Ryzen CPU 的小芯片設計策略為其他芯片制造商樹立了先例。例如,他們于 2019 年首次推出的第三代 Ryzen CPU,采用了兩顆臺積電 7 納米節點制造的芯片和一顆由 GlobalFoundries 制造的 14 納米芯片。前者是實際的處理器部件,而后者則管理連接到 CPU 的 DDR4 內存和 PCI Express 設備。

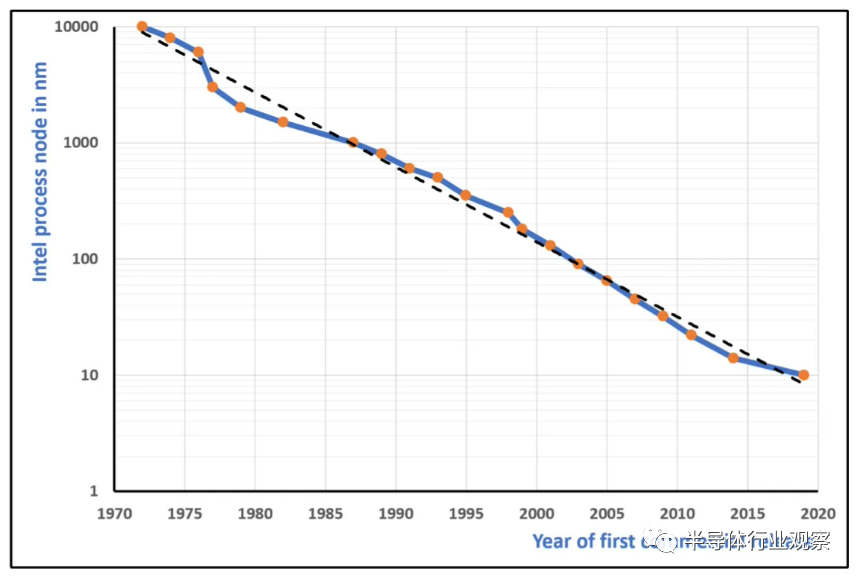

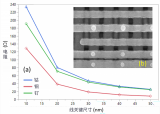

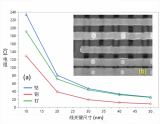

上圖展示了英特爾過去 50 年的工藝節點演變。在垂直軸上,節點尺寸以 10 為單位顯示,從 10000 nm 開始一直向上。這家芯片巨頭的發展軌跡表明,節點半衰期(每次將節點大小減少一半所需的時間)為 4.5 年。

這個軌跡是否表明英特爾將在2025年發布3nm-5nm 工藝?可能性很大。盡管之前出現了一些問題,英特爾的復蘇工作仍在全面展開。與此同時,三星和臺積電已經在3納米生產和進一步創新方面取得進展。對于整個領域的處理器來說,前景確實是樂觀的。

這些未來的處理器有望更加緊湊和高效,消耗更少的功率,同時提供卓越的性能。它們為全自動汽車、可與當代手機的功率和電池壽命相媲美的智能手表以及超越十年前大片視覺奇跡的游戲圖形(或者我們應該說人工智能芯片?)等進步鋪平了道路。

未來確實是光明的,因為未來很小。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論