采集數(shù)據(jù)中的量化噪聲,在進(jìn)行數(shù)據(jù)壓縮前采用濾波的預(yù)處理技術(shù)。介紹LZW算法和滑動濾波算法的基本理論,詳細(xì)闡述用單片FPGA實(shí)現(xiàn)兩種算法的方法。最終測試結(jié)果表明,該設(shè)計(jì)方案能夠有效濾除數(shù)據(jù)中的高頻噪聲

2010-04-24 09:05:21

本帖最后由 發(fā)燒友LV 于 2014-12-29 20:13 編輯

在FPGA中實(shí)現(xiàn)PID算法,面臨著小數(shù)的計(jì)算,請問大家一般是怎么處理的?

2014-12-03 21:59:29

與視頻處理培訓(xùn)發(fā)布時(shí)間:2009-1-6,來自 未名芯銳課程目標(biāo):1、深入了解JPEG標(biāo)準(zhǔn)和H.264標(biāo)準(zhǔn)協(xié)議;2、掌握FPGA在圖像與視頻方向設(shè)計(jì)的設(shè)計(jì)流程、方法及技巧。3、能夠實(shí)現(xiàn)視頻處理中的重要模塊

2009-07-16 14:05:25

FPGA設(shè)計(jì)之浮點(diǎn)DSP算法實(shí)現(xiàn),DSP算法是很多工程師在設(shè)計(jì)過程中都會遇到的問題,本文將從FPGA設(shè)計(jì)的角度來講解浮點(diǎn)DSP算法的實(shí)現(xiàn)。FPGA設(shè)計(jì)之浮點(diǎn)DSP算法實(shí)現(xiàn)是賽靈思工程師最新力作,資料不可多得,大家珍惜啊1FPGA設(shè)計(jì)之浮點(diǎn)DSP算法實(shí)現(xiàn)[hide][/hide]

2012-03-01 15:23:56

在FPGA上實(shí)現(xiàn)H 264 AVC視頻編碼標(biāo)準(zhǔn)盡管H.264/AVC承諾將比已有視頻編碼標(biāo)準(zhǔn)具有更高的編碼效率,它仍為系統(tǒng)架構(gòu)師、DSP 工程師和硬件設(shè)計(jì)人員帶來了巨大的工程設(shè)計(jì)挑戰(zhàn)。H.264

2008-06-25 11:33:26

因使用HDL仿真器耗大量時(shí) 間。系統(tǒng)級設(shè)計(jì)和驗(yàn)證工具(如MATLAB和Simulink)通過在FPGA上快速建立算法原型,可以幫助工程師實(shí)現(xiàn)這些優(yōu)勢。本文將介紹使用MATLAB和Simulink創(chuàng)建

2020-05-04 07:00:00

的提升。運(yùn)算速度或者數(shù)據(jù)路徑寬度都可以進(jìn)一步提高,另外,時(shí)序操作可以在結(jié)構(gòu)上增加一些并行度。這些措施中,每一種都可以提高一定的性能。在利用了目標(biāo)FPGA器件靈活性的結(jié)構(gòu)中實(shí)現(xiàn)算法,會獲得比較大的好處

2021-12-15 06:30:00

設(shè)計(jì)人員降低了成本,提高了集成度,大大降低了功耗。結(jié)論LCD 以前只是用于穩(wěn)定地顯示計(jì)算機(jī)數(shù)據(jù)文本和圖像,現(xiàn)在可以在大屏幕上顯示快速移動的視頻內(nèi)容。這需要采用專門的圖像處理算法,而FPGA 能夠實(shí)現(xiàn)

2008-10-16 15:44:08

本設(shè)計(jì)充分利用DM6446的強(qiáng)大運(yùn)算能力,在DSP內(nèi)核上實(shí)時(shí)運(yùn)行目標(biāo)跟蹤算法。 設(shè)計(jì)還在ARM處理器上執(zhí)行多線程應(yīng)用程序,負(fù)責(zé)視頻采集,顯示,網(wǎng)絡(luò)通信,外圍器件控制等工作。

2021-06-07 06:25:31

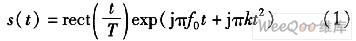

雷達(dá)主要是指用無線電方法發(fā)現(xiàn)目標(biāo)并測定它們在空間的準(zhǔn)確位置,因此雷達(dá)也稱為“無線電定位"。隨著雷達(dá)技術(shù)的不斷發(fā)展,雷達(dá)所要實(shí)現(xiàn)的任務(wù)不僅是準(zhǔn)確測量目標(biāo)的距離、方位和俯仰角,而且還包括準(zhǔn)確

2016-07-01 11:47:58

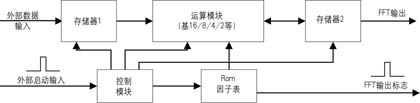

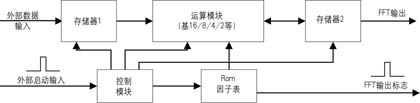

FPGA實(shí)現(xiàn)的 FFT 處理器的硬件結(jié)構(gòu)。接收單元采用乒乓RAM 結(jié)構(gòu), 擴(kuò)大了數(shù)據(jù)吞吐量。中間數(shù)據(jù)緩存單元采用雙口RAM , 減少了訪問RAM 的時(shí)鐘消耗。計(jì)算單元采用基 2 算法, 流水線結(jié)構(gòu), 可在

2017-11-21 15:55:13

在信號處理中,FFT占有很重要的位置,其運(yùn)算時(shí)間影響整個(gè)系統(tǒng)的性能。傳統(tǒng)的實(shí)現(xiàn)方法速度很慢,難以滿足信號處理的實(shí)時(shí)性要求。針對這個(gè)問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實(shí)時(shí)性

2010-05-28 13:38:38

,使用HDL編碼器自動生成HDL代碼具有眾多明顯優(yōu)勢。工程師可以快速地評估能否在硬件中實(shí)施當(dāng)前算法;迅速評估不同的算法實(shí)現(xiàn),選擇最佳方案;并在FPGA上更快地建立算法原型。 對于DDC案例研究而言

2018-09-04 09:26:53

申請理由:本人已經(jīng)成功完成閾值自適應(yīng)視頻邊緣檢測算法的FPGA快速實(shí)現(xiàn),但FPGA也有很多局限性,所以想將硬件平臺從FPGA換成香蕉派。相信會有全新的體驗(yàn),和更加快捷的開發(fā)途徑。項(xiàng)目描述:在香蕉派上

2016-06-20 15:55:06

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過程。實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于用

2019-07-01 07:38:06

仿真,由ISE綜合并下載,在Xilinx公司的Virtex-5xc5vfx70t器件上以200 MHz的時(shí)鐘實(shí)現(xiàn)驗(yàn)證,運(yùn)算結(jié)果與其他設(shè)計(jì)的運(yùn)算效率對比有一定優(yōu)勢。在現(xiàn)代聲納、雷達(dá)、通信、圖像處理等領(lǐng)域

2019-07-03 07:56:53

針對視頻的輸出顯示要求,重點(diǎn)介紹了基于雙線性插值算法的實(shí)現(xiàn)。ModelSim的仿真結(jié)果表明,該算法符合多屏幕顯示系統(tǒng)的要求。關(guān)鍵詞 視頻監(jiān)控;視頻圖像處理;雙線性插值;FPGA;多屏幕

2019-06-28 07:06:54

中每幀的數(shù)據(jù)傳輸與計(jì)算的協(xié)調(diào)工作使用圖3所示的代碼完成。

該代碼運(yùn)行在主機(jī)處理器上,負(fù)責(zé)發(fā)送視頻幀到FPGA加速器卡,啟動加速器,然后從FPGA加速器卡取回處理后的幀。

FPGA水印算法的首個(gè)實(shí)現(xiàn)

2019-06-19 07:27:40

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-28 08:10:26

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-19 06:12:05

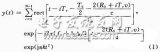

實(shí)時(shí)計(jì)算所需要的回波,從而實(shí)現(xiàn)對雷達(dá)目標(biāo)回波的模擬,這樣可以在沒有陣面數(shù)據(jù)的情況下,使信號處理分系統(tǒng)調(diào)試能夠正常進(jìn)行,從而不影響科研進(jìn)度,做到有問題早發(fā)現(xiàn)。 1 系統(tǒng)原理 由于要調(diào)試的是PD體制雷達(dá)

2011-07-13 09:09:26

模數(shù)轉(zhuǎn)換、FFT快速、準(zhǔn)確的要求,并且具有高度集成、高可靠性和可編程等特點(diǎn),減少了系統(tǒng)硬件開發(fā)周期,所以選用基于FPGA來實(shí)現(xiàn)雷達(dá)信號處理系統(tǒng)的設(shè)計(jì)。回映電子是一家基于Edge-AI技術(shù)的個(gè)護(hù)健康

2021-12-27 17:08:50

本帖最后由 gk320830 于 2015-3-8 21:23 編輯

開始科創(chuàng),老師給了我們一個(gè)題基于FPGA的FFT算法硬件實(shí)現(xiàn)。但是什么都不會,想找些論文看看,求相關(guān)的論文

2012-05-24 22:14:40

亮度分布特性有力的工具,根據(jù)它的結(jié)果可以進(jìn)行諸如灰度拉伸、自動對比度、動態(tài)伽馬調(diào)整等操作。圖1 Lena 圖像的灰度直方圖統(tǒng)計(jì)FPGA算法統(tǒng)計(jì)在計(jì)算機(jī)或者DSP 上實(shí)現(xiàn)直方圖統(tǒng)計(jì)時(shí),我們通常會使用數(shù)組

2012-05-14 12:37:37

VGA顯示屏上,前面我們把硬件平臺已經(jīng)搭建完成了,后面我們將利用這個(gè)硬件基礎(chǔ)平臺上來實(shí)現(xiàn)基于FPGA的一系列圖像處理基礎(chǔ)算法。椒鹽噪聲(salt &pepper noise)是數(shù)字圖像的一

2017-08-28 11:34:10

:《科技資訊》 (科技資訊)年 卷 期:2017年 第24期摘 要:文章概述了一種廣泛應(yīng)用于VOIP(VoiceOverIP)技術(shù)的回聲消除算法,并基于該算法在大規(guī)模邏輯器件FPGA上實(shí)現(xiàn)應(yīng)用。通過仿真

2018-05-08 10:23:36

隨機(jī),使接收信號具有相參性。仿真結(jié)果表明了本文所述基于FPGA的DSU實(shí)現(xiàn)方法有效,另外該算法已經(jīng)實(shí)際用于某非相參雷達(dá)改造上,并進(jìn)行了外場實(shí)驗(yàn),取得了良好的實(shí)測效果。

2015-02-05 15:34:43

`大家好,給大家介紹一下,這是基于FPGA的膚色識別算法實(shí)現(xiàn)。我們今天這篇文章有兩個(gè)內(nèi)容一是實(shí)現(xiàn)基于FPGA的彩色圖片轉(zhuǎn)灰度實(shí)現(xiàn),然后在這個(gè)基礎(chǔ)上實(shí)現(xiàn)基于FPGA的膚色檢測算法實(shí)現(xiàn)。將彩色圖像轉(zhuǎn)化

2017-10-28 08:48:57

本篇文章我要寫的是基于的腐蝕膨脹算法實(shí)現(xiàn),腐蝕膨脹是形態(tài)學(xué)圖像處理的基礎(chǔ),,腐蝕在二值圖像的基礎(chǔ)上做“收縮”或“細(xì)化”操作,膨脹在二值圖像的基礎(chǔ)上做“加長”或“變粗”的操作。那么什么是二值圖像呢?把

2017-09-22 13:20:55

在實(shí)際的外場試飛過程中是不可能實(shí)現(xiàn)的,這也是雷達(dá)信號模擬器對場外試飛的一大優(yōu)勢。FPGA作為高性能數(shù)字信號處理系統(tǒng)中的關(guān)鍵部件,在雷達(dá)信號模擬和雷達(dá)信號采集等方面有著巨大的開發(fā)潛能,采用這些技術(shù)對雷達(dá)

2019-07-15 06:48:33

Proeessors,DSP)、高速現(xiàn)場可編程邏輯器件(Field ProgrammableGate Array,FPGA)的出現(xiàn),可以在不增加現(xiàn)有雷達(dá)發(fā)射功率和接收靈敏度的條件下,在信噪比降為3

2018-08-15 09:43:14

視覺、交通監(jiān)測、可視預(yù)警、機(jī)器導(dǎo)航等民用領(lǐng)域有著廣泛的應(yīng)用,同時(shí)在火力攔截、導(dǎo)彈電視和紅外視頻制導(dǎo)等軍用方面也發(fā)揮著重要作用。基于二維轉(zhuǎn)臺以DSP和FPGA為核心器件構(gòu)成的視頻識別和跟蹤裝置,可工作于

2019-06-26 06:09:46

本文介紹了如何在FPGA中利用Block RAM的特殊結(jié)構(gòu)實(shí)現(xiàn)HDTV視頻增強(qiáng)算法中灰度直方圖統(tǒng)計(jì)。

2021-04-30 07:34:58

使用SoC FPGA,實(shí)現(xiàn)汽車雷達(dá)的數(shù)字化處理本白皮書介紹使用Altera? 低成本Cyclone? V SoC FPGA,實(shí)現(xiàn)典型雷達(dá)系統(tǒng)數(shù)字化處理的可行性。與定制ASIC 相比,這一方法的優(yōu)勢

2013-11-13 15:56:28

的檢測性能,在檢測前進(jìn)行一次視頻積累是非常必要的。雖然視頻積累的效果不如相參積累,但是視頻積累的工程實(shí)現(xiàn)比較簡單,對雷達(dá)的收發(fā)系統(tǒng)沒有嚴(yán)格的相參性要求,且對大多數(shù)運(yùn)動目標(biāo)來講其回波的起伏將明顯破壞相鄰回波信號的相位相參性,因此在許多實(shí)際工程應(yīng)用場合還是采用視頻積累。

2019-08-12 06:00:57

FFT算法的實(shí)現(xiàn)為了提高FFT工作頻率和節(jié)省FPGA資源,采用3級流水線結(jié)構(gòu)實(shí)現(xiàn)64點(diǎn)的FFT運(yùn)算。流水線處理器的結(jié)構(gòu)如圖2所示。每級均由延時(shí)單元、轉(zhuǎn)接器(SW)、蝶形運(yùn)算和旋轉(zhuǎn)因子乘法4個(gè)模塊組成

2019-06-17 09:01:35

我打算在FPGA上實(shí)現(xiàn)許多計(jì)算機(jī)視覺算法。 Digilent Atlys是這類應(yīng)用的良好平臺嗎?我是初學(xué)者,不能自己解決這個(gè)問題。Digilent Atlys:http

2019-10-28 07:10:38

芯片設(shè)計(jì)和驗(yàn)證工程師通常要為在硅片上實(shí)現(xiàn)的每一行RTL代碼寫出多達(dá)10行測試平臺代碼。驗(yàn)證任務(wù)在設(shè)計(jì)周期內(nèi)可能會占用50%或更多的時(shí)間。盡管如此辛苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以發(fā)現(xiàn)系統(tǒng)級錯(cuò)誤,芯片設(shè)計(jì)人員正利用FPGA來加速算法創(chuàng)建和原型設(shè)計(jì)。

2019-09-18 07:50:02

請問一下如何用FPGA實(shí)現(xiàn)FFT算法?

2021-04-08 06:06:26

主要內(nèi)容包括:1. 為什么很多人覺得學(xué)習(xí)FPGA很困難,以及HDL學(xué)習(xí)的一些誤區(qū);2. 軟件和硬件在算法實(shí)現(xiàn)上的區(qū)別;3. 通過具體例子詳細(xì)講解了從算法的行為級建模向RTL級建模的轉(zhuǎn)換思想和底層電路

2015-09-18 15:44:39

在IPSec協(xié)議中認(rèn)證使用SHA-1和MD5單向散列函數(shù)算法實(shí)現(xiàn),通過使用FPGA高速實(shí)現(xiàn)SHA-1消息認(rèn)證算法。

2021-04-13 06:02:01

如何采用FPGA實(shí)現(xiàn)視頻監(jiān)視?

2021-04-29 06:24:06

,采用AGC算法,可提高音頻信號系統(tǒng)和音頻信號輸出的穩(wěn)定性,解決了AGC調(diào)試后的信號失真問題。本文針對基于實(shí)用AGC算法的音頻信號處理方法與FPGA實(shí)現(xiàn),及其相關(guān)內(nèi)容進(jìn)行了分析研究。1、 實(shí)用AGC算法在

2020-10-21 16:42:15

我正在做我的遺傳算法項(xiàng)目,有沒有辦法在斯巴達(dá)3AN fpga中實(shí)現(xiàn)遺傳算法,如果沒有建議我一些方法來克服這種沖突。謝謝以上來自于谷歌翻譯以下為原文I am doing my project

2019-04-03 13:16:55

本文利用CORDIC算法在FPGA上實(shí)現(xiàn)了高速自然對數(shù)變換器。

2021-04-30 06:05:22

ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)將視頻信號(NTSC:720*480 PAL:720*576)放大成1024*768。3、放大后的視頻信號輸入到FPGA或ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)在放大的視頻上疊加直線的功能。4

2011-06-09 22:29:18

ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)將視頻信號(NTSC:720*480 PAL:720*576)放大成1024*768。3、放大后的視頻信號輸入到FPGA或ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)在放大的視頻上疊加直線的功能。4

2011-06-09 22:30:33

ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)將視頻信號(NTSC:720*480 PAL:720*576)放大成1024*768。3、放大后的視頻信號輸入到FPGA或ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)在放大的視頻上疊加直線的功能。4

2011-06-09 22:32:19

ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)將視頻信號(NTSC:720*480 PAL:720*576)放大成1024*768。3、放大后的視頻信號輸入到FPGA或ARM或?qū)S眯酒?b class="flag-6" style="color: red">實(shí)現(xiàn)在放大的視頻上疊加直線的功能。4

2011-06-09 22:34:42

進(jìn)行驗(yàn)證。能夠實(shí)現(xiàn)LFMCW雷達(dá)多目標(biāo)檢測方法的硬件電路設(shè)計(jì)。弄清LFMCW雷達(dá)的工作原理,系統(tǒng)中傳輸?shù)男盘柼攸c(diǎn);研究檢測算法的特點(diǎn),用verilog語言實(shí)現(xiàn)檢測算法,在獲得滿意仿真結(jié)果的基礎(chǔ)上,完成電路的FGPA驗(yàn)證分析。QQ2784829569

2018-04-08 23:48:36

介紹一種在FPGA上實(shí)現(xiàn)的單精度浮點(diǎn)加法運(yùn)算器,運(yùn)算器算法的實(shí)現(xiàn)考慮了FPGA器件本身的特點(diǎn),算法處理流程的拆分和模塊的拆分,便于流水設(shè)計(jì)的實(shí)現(xiàn)。

2021-04-29 06:27:09

求助大神,在FPGA上實(shí)現(xiàn)retinex算法 。。。

2013-05-08 23:29:41

用FPGA硬件實(shí)現(xiàn)。 現(xiàn)在我沒有FPGA硬件實(shí)現(xiàn)的經(jīng)驗(yàn),不知道如何用FPGA硬件實(shí)現(xiàn)小波算法。 懇請賜教!謝謝!

2012-11-20 21:35:16

數(shù)據(jù)格式為LVDS/CSI,需要專用的FPGA開發(fā)板才能將如此高速的數(shù)據(jù)上傳到上位機(jī)做算法驗(yàn)證。NXP的dolphin通過外接帶千兆網(wǎng)的S32處理器開發(fā)板,可以實(shí)現(xiàn)數(shù)據(jù)到上位機(jī)的傳輸。但千兆網(wǎng)傳輸效率

2018-09-29 17:01:53

謝謝各位。。各位大神。。用fpga實(shí)現(xiàn)FFT算法,最好是verilog hdl的。。或者推薦一些好書。。

2013-05-06 00:24:19

本文推導(dǎo)出一種適合在FPGA上實(shí)現(xiàn)從RGB到Y(jié)CbCr。顏色空間變換的新算法,采用單片FPGA完成電路設(shè)計(jì),利用FPGA內(nèi)嵌DSP核實(shí)現(xiàn)乘法運(yùn)算,提高了轉(zhuǎn)換算法的運(yùn)行速度。

2021-04-29 06:57:57

想實(shí)現(xiàn)一些視頻算法的測試,需要讀入視頻(avi,MP4)。在CCS上可以讀入視頻文件嗎?怎樣實(shí)現(xiàn)?

2018-08-02 08:21:31

就已經(jīng)出現(xiàn),隨著FPGA芯片價(jià)格的不斷降低,其在工業(yè)領(lǐng)域的應(yīng)用正在飛速發(fā)展,采用FPGA來實(shí)現(xiàn)SVPWM調(diào)制算法也將層出不窮2. 系統(tǒng)任務(wù)分析及實(shí)現(xiàn)SVPWM調(diào)制算法相對比較復(fù)雜,在完成系統(tǒng)控制任務(wù)

2022-01-20 09:34:26

一般的雷達(dá)信號源實(shí)現(xiàn)主要有三種方式:第一種方式是采用DDS和MCU控制器件結(jié)合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結(jié)合的方式:第三種是由FPGA等可編程器件實(shí)現(xiàn)DDS的方式

2020-11-24 06:39:52

小波盲源分離算法的仿真及FPGA實(shí)現(xiàn):提出了一種基于小波變換的盲源分離方法,在理論分析和仿真結(jié)果的基礎(chǔ)上,給出了FPGA 的實(shí)現(xiàn)方案。針對傳統(tǒng)盲分離算法對源信號統(tǒng)計(jì)特征敏

2009-06-21 22:44:09 21

21 提出一種基于DCT域的數(shù)字水印算法,并用FPGA硬件實(shí)現(xiàn)其中關(guān)鍵部分DCT變換。采用VHDL語言有效設(shè)計(jì)和實(shí)現(xiàn)DCT變換,分析與仿真結(jié)果表明:與軟件實(shí)現(xiàn)相比,用FPGA實(shí)現(xiàn)水印算法具有高

2010-12-28 10:22:14 20

20 用FPGA實(shí)現(xiàn)FFT算法

引言 DFT(Discrete Fourier Transformation)是數(shù)字信號分析與處理如圖形、語音及圖像等領(lǐng)域的重

2008-10-30 13:39:20 1427

1427

本系統(tǒng)基于自主產(chǎn)生的原理,選用DSP和FPGA為核心處理器,通過合理的算法設(shè)計(jì),實(shí)現(xiàn)了可兼容多種雷達(dá)波形的中頻雷達(dá)回波模擬器的設(shè)計(jì),采用改進(jìn)的基于存儲轉(zhuǎn)發(fā)的數(shù)字脈沖延時(shí)方法

2011-08-28 17:24:10 930

930

MIDI合成算法及其FPGA實(shí)現(xiàn).

2012-04-16 13:57:38 44

44 基于FPGA的SM3算法優(yōu)化設(shè)計(jì)與實(shí)現(xiàn)的論文

2015-10-29 17:16:51 4

4 ECT圖像重建算法的FPGA實(shí)現(xiàn)

ECT圖像重建算法的FPGA實(shí)現(xiàn)

2015-11-19 14:59:41 1

1 基于FPGA的三相SVPWM調(diào)制算法的實(shí)現(xiàn)。

2016-04-18 09:47:49 23

23 基于FPGA的視頻字符疊加的設(shè)計(jì)與實(shí)現(xiàn)。

2016-05-10 17:46:07 30

30 利用FPGA的IP核設(shè)計(jì)和實(shí)現(xiàn)FFT算法

2016-05-24 14:14:47 36

36 Xilinx FPGA工程例子源碼:在FPGA上實(shí)現(xiàn)CRC算法的程序

2016-06-07 15:07:45 28

28 基于FPGA的JPEG解碼算法的研究與實(shí)現(xiàn)

2016-08-29 16:05:01 11

11 基于FPGA的某型雷達(dá)視頻采集預(yù)處理模塊設(shè)計(jì)

2016-08-30 15:10:14 34

34 新的自調(diào)整多叉樹RFID防碰撞算法的FPGA實(shí)現(xiàn)_任少杰

2017-01-08 15:15:59 2

2 LMS自適應(yīng)算法的FPGA設(shè)計(jì)與實(shí)現(xiàn)_陳亮

2017-03-19 11:27:34 5

5 傳統(tǒng)的插值算法在視頻圖像縮放尤其是輸出高分辨率的視頻圖像時(shí),對細(xì)節(jié)方面的處理性能較差。采用多相位插值算法實(shí)現(xiàn)視頻圖像縮放,主要闡述算法的原理及算法實(shí)現(xiàn)的硬件結(jié)構(gòu)。其中硬件電路控制部分使用Xilinx

2017-11-16 11:48:09 4559

4559

隨著視頻設(shè)備的高速發(fā)展,數(shù)字視頻相關(guān)應(yīng)用同樣發(fā)展迅速,如監(jiān)控設(shè)備、行車記錄儀以及手機(jī)等電子產(chǎn)品。而如今數(shù)字視頻圖像增強(qiáng)的算法層出不窮,由于算法的復(fù)雜程度比較高,很難滿足實(shí)時(shí)性這一基本的要求。討論

2017-11-16 14:30:14 2094

2094 本文是基于FPGA實(shí)現(xiàn)Cordic算法的設(shè)計(jì)與驗(yàn)證,使用Verilog HDL設(shè)計(jì),初步可實(shí)現(xiàn)正弦、余弦、反正切函數(shù)的實(shí)現(xiàn)。將復(fù)雜的運(yùn)算轉(zhuǎn)化成FPGA擅長的加減法和乘法,而乘法運(yùn)算可以用移位運(yùn)算代替

2018-07-03 10:18:00 2349

2349

、功耗與實(shí)時(shí)性要求都很高的實(shí)時(shí)SAR成像系統(tǒng),其應(yīng)用十分廣泛。在整個(gè)有距離-多普勒(R-D)算法中方位脈沖壓縮系統(tǒng)是設(shè)計(jì)的關(guān)鍵。隨著FPGA芯片突飛猛進(jìn)的發(fā)展,實(shí)時(shí)雷達(dá)成像方位脈沖壓縮系統(tǒng)在FPGA上實(shí)現(xiàn)變成了可能。

2018-12-30 11:10:00 3331

3331

本文介紹了如何在FPGA 中利用Block RAM 的特殊結(jié)構(gòu)實(shí)現(xiàn)HDTV視頻增強(qiáng)算法中灰度直方圖統(tǒng)計(jì)。

2019-07-10 08:10:00 2578

2578 為有效提高視頻監(jiān)控應(yīng)用領(lǐng)域中多屏幕畫面顯示的清晰度、分辨度等問題,提出了一種基于FPGA的實(shí)時(shí)視頻圖像處理算法。

2019-09-13 14:53:00 3490

3490 針對多屏幕拼接顯示系統(tǒng)中高分辨率.高清晰、低失真的顯示需求,提出了一種基于FPGA實(shí)現(xiàn)的實(shí)時(shí)視頻處理算法。在介紹了DVI接口屏幕拼接顯示的系統(tǒng)結(jié)構(gòu)及FPGA算法的主要功能后,針對算法處理對象具有視頻

2021-03-31 15:23:09 10

10 基于FPGA的定點(diǎn)LMS算法的實(shí)現(xiàn)講解。

2021-04-28 11:17:25 10

10 FPGA算法是指在FPGA(現(xiàn)場可編程門陣列)上實(shí)現(xiàn)的算法。FPGA是一種可重構(gòu)的硬件設(shè)備,可以通過配置和編程實(shí)現(xiàn)各種不同的功能和算法,而不需要進(jìn)行硬件電路的修改。

FPGA算法可以包括

2023-08-16 14:31:23 1604

1604

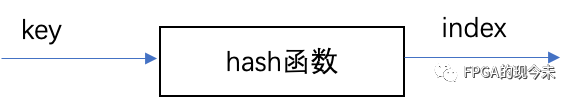

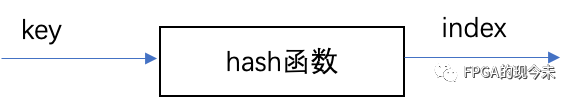

在FPGA的設(shè)計(jì)中,尤其是在通信領(lǐng)域,經(jīng)常會遇到hash算法的實(shí)現(xiàn)。hash算法在FPGA的設(shè)計(jì)中,它主要包括2個(gè)部分,第一個(gè)就是如何選擇一個(gè)好的hash函數(shù),減少碰撞;第二個(gè)就是如何管理hash表。本文不討論hash算法本身,僅說明hash表的管理。

2023-09-07 17:01:32 471

471

電子發(fā)燒友App

電子發(fā)燒友App

評論