0 引 言

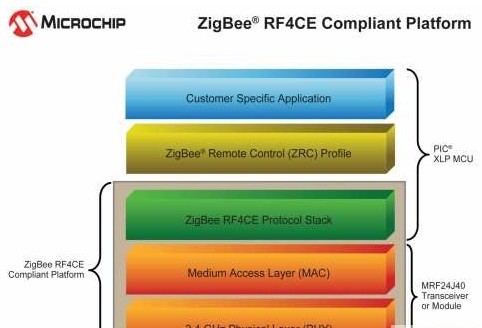

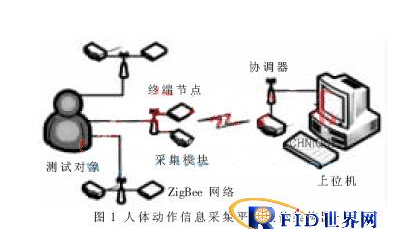

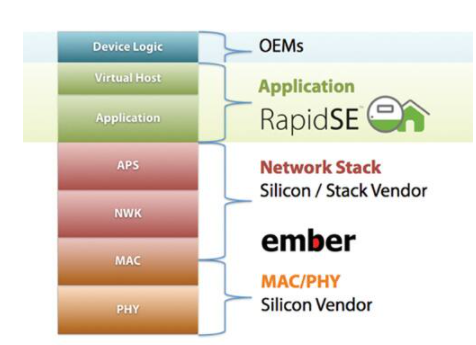

??? ZigBee技術是一種具有統一技術標準的短距離、低速率的無線通信技術,其物理層和媒體訪問控制層協議為IEEE 802.15.4協議標準,網絡層由ZigBee技術聯盟制定,應用層的開發根據用戶的實際應用需求,對其進行開發設計。

??? 在設計開發ZigBee協議之前必須要有相應硬件平臺的支撐,這里為ZigBee協議棧的實現提供了相應的硬件平臺設計。在此主要介紹了MT-ZigBee硬件平臺的設計與各硬件模塊的測試。硬件平臺的設計主要包括硬件平臺的選型、ZigBee控制電路的硬件設計和ZigBee射頻電路部分的硬件設計;硬件平臺的測試主要包括各個硬件模塊的測試。

1 ZigBee硬件方案

??? 在ZigBee技術聯盟中,Freescale,TI,Chipeon,Philips等公司都是ZigBee標準制訂的先驅。在射頻收發芯片方面,主要有Freeseale公司的MC13192,MC13193和Chipeon公司的CC2420,CC2430所提供的兩大解決方案。下面簡單比對這兩種可選的硬件開發方案。

??? Freescale公司面向ZigBee技術推出了完整的硬件解決方案,其中主要包括MC13192,MC13193射頻(Radio Frequenee,RF)收發芯片;與RF端相配套的低功耗HCS08核MCU;相關的傳感器等。MC13192,MC13193是符合IEEE 802.15.4標準的射頻數據調制解調器,它工作在2.4 GHz頻段下,與MCU通過標準的4線SPI接口通信,采用16個射頻通道,數據速率為250 Kb/s。與HCS08核MCU配套使用,可提供低成本、低功耗、經濟高效的ZigBee硬件平臺方案。挪威半導體公司Chipcon推出的CC2430射頻芯片是全球首顆符合ZigBee技術標準的2.4 GHz射頻芯片,它沿用了CC2420的架構。CC2430兼容IEEE802.15.4標準,具有8051核的無線單片機。其在單芯片上集成了ZigBee RF前端、存儲器和微控制器。另外,CC2430內部還包含了模/數轉換器(ADC)、定時器、AES-128協處理器、看門狗、32 kHz晶振時鐘、上電復位電路、掉電檢測電路以及21個可編程I/O接口。由于Freescale公司提供了詳細的芯片手冊、參考設計、布線設計等文檔說明,為硬件平臺的搭建提供了良好的開發環境。這里在現有的ZigBee硬件方案中選擇了Freescale公司提供的解決方案:MC9S08GB60和MC13192;并以此方案為背景設計開發了MT-ZigBee硬件平臺。

2 MT-ZigBee硬件平臺設計

??? MT-ZigBee硬件平臺的設計,主要包括硬件平臺的選型,ZigBee控制電路的硬件設計和ZigBee射頻電路部分的硬件設計。

2.1 硬件選型

??? (1)主控MCU的選取。從芯片內部集成功能模塊、RAM和FLASH的存儲容量、芯片和開發環境的熟悉程度等方面考慮,本文選擇了Freescale公司生產的S08系列的8位MC9S08GB60(以下簡稱GB60)作為平臺的主控芯片。HCS08核,最高總線頻率可達40 MHz;它內部具有64 KB的FLASH和4 KB的RAM存儲空間;內部集成了1個SPI模塊,適合與MC13192的通信;2個SCI模塊,方便與PC通信;具有背景調試模塊.能利用單線對HCS08核的系列MCU進行方便地寫入和調試,加快開發的速度并大大降低了調試的難度。

??? (2)物理層芯片的選取。為了設計出低成本、低功耗、經濟高效的ZigBee硬件平臺.這里選擇了與HCS08核MCU配套使用的MC13192芯片作為Zig-Bee物理層芯片。MC13192是Freescale公司于2005年推出的工作在2.4 GHz頻率下短距離,低功率,工業、科學和醫療(ISM)的無線數據收發器。MC13192與MCU的接口簡單,只需四線的SPI,1個IRQ中斷請求線和3個控制線。

2.2 MT-ZigBee硬件平臺設計

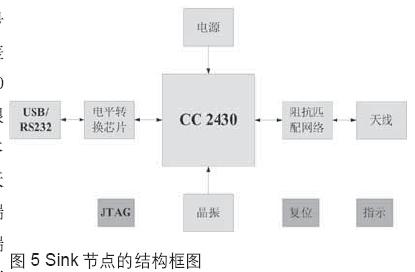

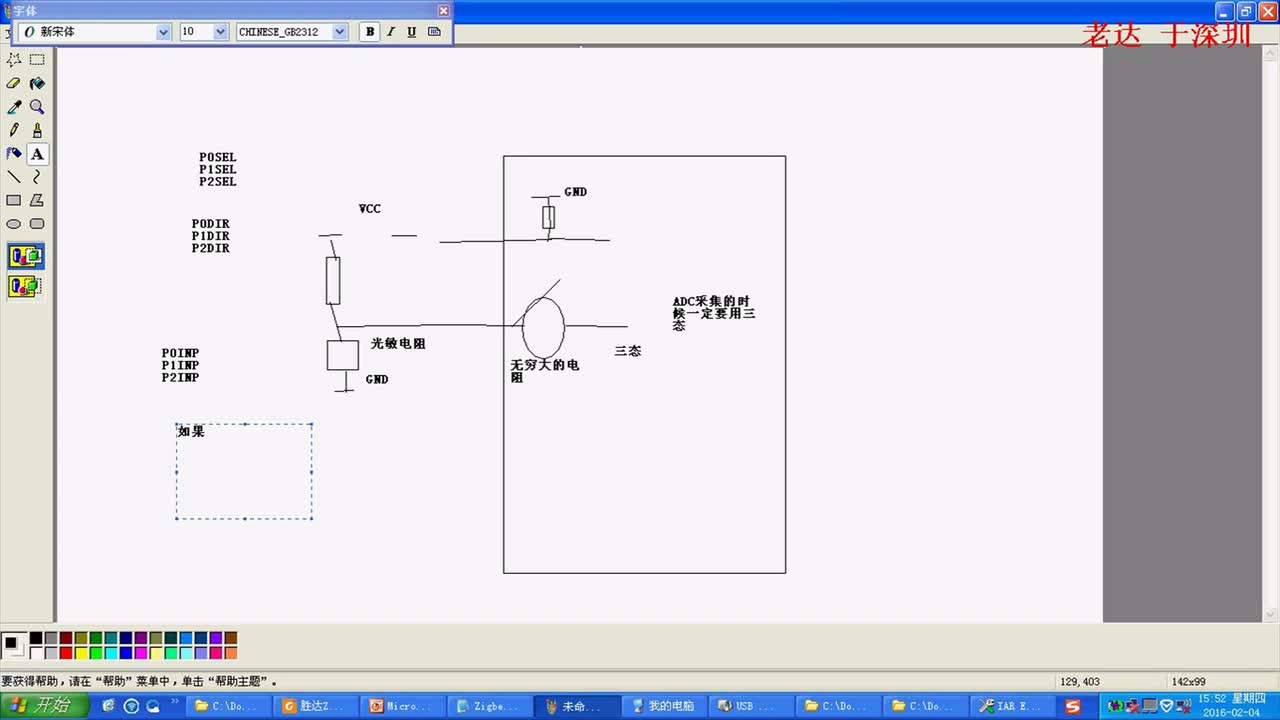

??? MT-ZigBee硬件平臺主要包括主控MCU支撐模塊;外部輸入部分有電源輸入模塊和按鍵輸入;MC13192無線射頻通信模塊;SCI串行通信模塊;運行狀態顯示模塊和現場數據采集模塊,整體的硬件框圖如圖1所示。其中按鍵輸入、SCI串行通信模塊、液晶及運行指示燈模塊設計比較簡單,由于篇幅問題,不再敘述。下面重點介紹電源輸入模塊、MCU支撐模塊、GB60與MC13192接口電路和MC13192無線射頻通信模塊的硬件設計。

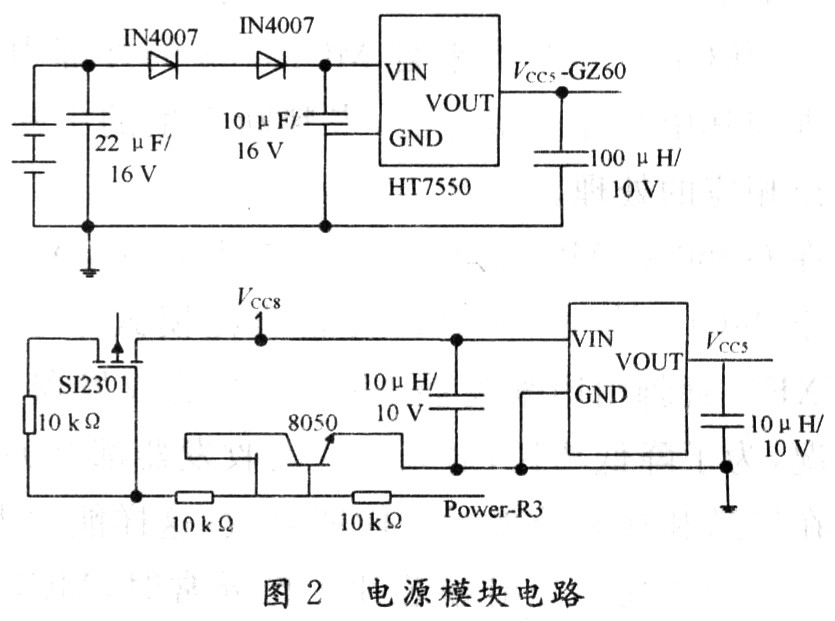

2.2.1 電源輸入模塊

??? 無線傳感器網絡主要用于采集現場數據,再進行相應控制。設備均安放在采集現場,考慮到便于攜帶、安裝,供電電源采用1節9 V的干電池。在硬件電路上電源分為兩路:一路是單獨供給主控芯片GB60的電源;另一路是供給LCD、MC13192、SCI、按鍵和測試小燈等所有外圍模塊的電源。具體電源電路如圖2所示。

??? 在電源電路中,主控芯片電源在任何情況下都是存在的.這樣保證任何情況下GB60都是工作的;外圍模塊電源受到主控芯片控制,GB60通過MOS管來控制外圍模塊電源:當系統正常工作時,GB60允許外圍模塊電源上電;當系統進入低功耗狀態時,GB60切斷外圍模塊電源.這樣整個系統只有主控芯片有供電,主控芯片再進入低功耗模式(Stop Mode),這樣就更好地實現了整個系統的低功耗。注意,在切斷外圍模塊電源時,不能直接使用一般的三極管,這樣進入低功耗狀態后外圍模塊仍然有較大的電流消耗,應該使用電流截止性能好的MOS管(如:SI2301)來實現。

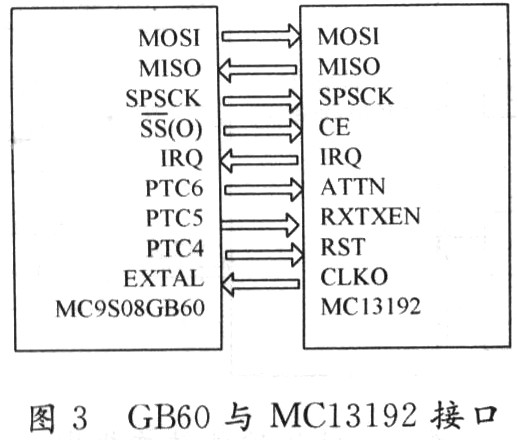

2.2.2 GB60與MC13192接口電路設計

??? GB60與MC13192的接口電路如圖3所示。GB60與MC13192主要有9個連接接口:4根SPI通信接口、IRQ中斷接口、3根MC13192的控制口和MC13192時鐘輸出引腳。其中對于4線SPI,根據參考手冊指出,當作為SPI主機方式,同時SPI狀態與控制寄存器的模式錯誤標志(MODF)有效并置為1時,引腳可單獨作為I/O口使用。在該設計中GB60為SPI主機方,直接作為輸出口使用,用以控制MC13192的CE使能信號。

G1360對MC13192上的寄存器、片上RAM讀取和寫入時都是通過標準的4線SPI接口來實現的。通信時,MC13192只能作為從機,因此對于MCU而言,MOSI線是發送數據線,而MISO線是接收數據線,SPI的同步時鐘由GB60在SPSCK管腳上給出,連接到MC13192的SPICLK上。

??? MC13192的IRQ管腳連接到GB60的IRQ管腳上,MC13192上產生的所有中斷事件直接反映給GB60。當GB60接收到來自MC13192的外部中斷時,還要查詢其中斷標志寄存器,來判斷產生的中斷事件,并作出相應的處理。

??? 在GB60對MC13192的3個控制口中,ATTN管腳用于MCU、將MC13192從低功耗模式下喚醒,而RXTXEN管腳則用來使能MC13192的收發器。在通常情況,為了降低功耗,射頻芯片的收發器都是關閉的,只有在發送和接收數據時才使能有效,這樣能大大降低射頻芯片的功耗。當射頻芯片工作異常時,MCU也可以通過RST管腳來硬件復位MC13192。

??? MC13192的時鐘輸出引腳CLKO直接與GB60的EXTAL引腳相連接,從而GB60不再需要外部晶振電路的支持,直接采用來自MC13192的時鐘源即可。該時鐘源是可編程的,能夠提供8種不同的時鐘頻率:16 MHz,8 MHz,4 MHz,2 MHz,1 MHz,62.5kHz,32.768 kHz和16.393 kHz。

2.2.3 MC13192無線射頻通信模塊設計

??? 射頻電路的設計是硬件設計中最為復雜的部分。這一部分對PCB的材質、電阻電容的精度、電路的走線等都有很高的要求,其參數選擇的好壞直接影響到射頻電路的質量。

??? 射頻電路的設計是參考Freescale,Microchip等公司給出的參考樣例進行設計開發的。

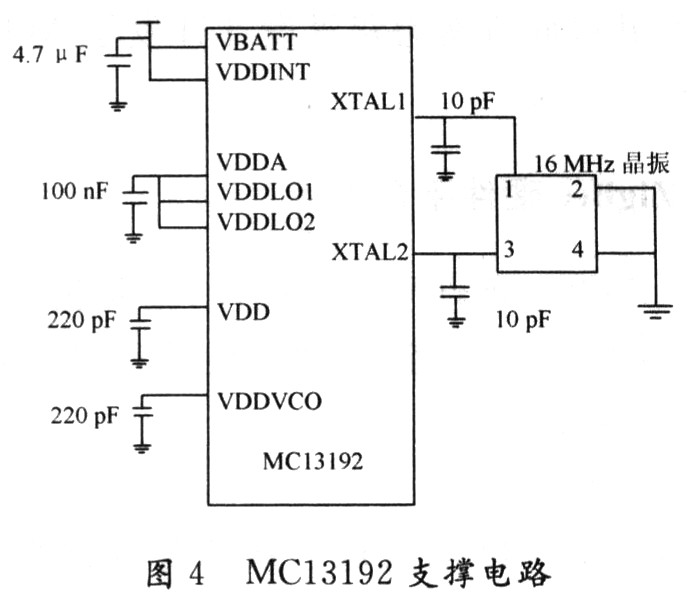

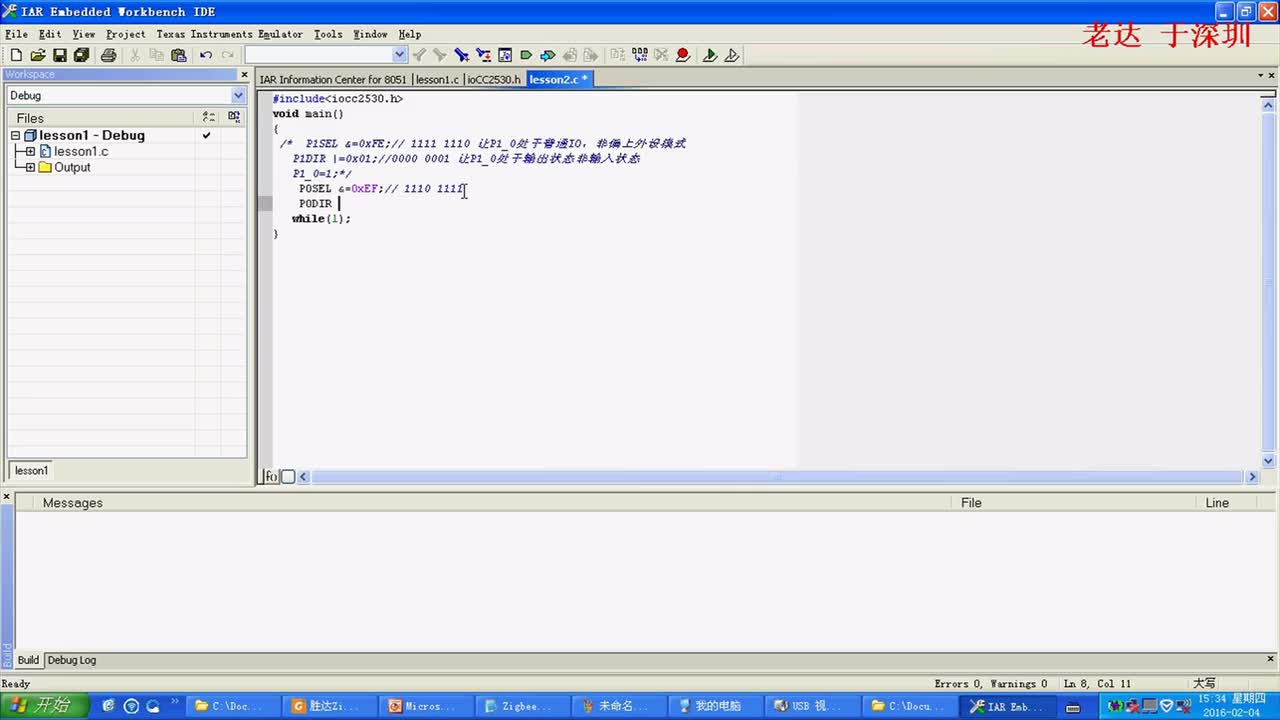

??? (1)MC13192支撐電路的設計。MC13192的支撐電路包括電源電路,濾波電路和晶振電路,其邏輯連接如圖4所示。VBATT和VDDINT是電源輸入引腳,MC13192的正常工作電壓為2.0~3.6 V,必須接一個4.7μF的穩壓電容。VDDA,VDDL01和VDDL02為經過整流的模擬電壓,必須旁接一個100 nF的濾波電容。VDD為經過內部整流的數字電壓,旁接一個220 pF的濾波電容。VDDVCO為VCO電路供電,同樣必須旁接一個220 pF的電容。XTAL1和XTAL2外接16 MHz的專用于2.4 GHz射頻電路的晶振,其旁路電容為1O pF。

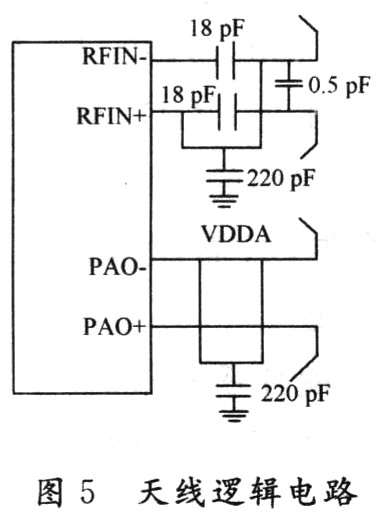

??? (2)天線電路的設計。用于2.4 GHz射頻電路的天線有3種類型:外接直立天線、PCB天線和片式天線。外接直立天線的性能最好,但體積過大,只能用于對體積無要求的場合;片式天線采用集成電路來實現,性能一般,而且很難根據實際調整性能;PCB天線具有體積優勢,但是對設計和PCB布線要求高,在無線傳感器網絡的硬件平臺上應用最多。

??? 圖5為天線電路的原理圖。RFIN-和RFIN+為接收通道,2個18 pF的電容過濾掉高頻干擾信號,而0.5 pF的電容能防止共扼干擾。PAO-和PAO+為發送通道,這兩個管腳和VDDA連在一起,給發送通道提供必要的能量。

3 MIT-ZigBee硬件平臺的模塊測試

??? 在完成硬件電路設計后,必須對各模塊的硬件電路進行測試,以保證硬件電路的可靠性。對于整塊的硬件電路,應該按模塊分別焊接、調試,并逐模塊調試通過后再聯合起來一起調試。在硬件PCB設計時需要預留出一定的測試節點,以便以后測量使用。

??? MT-ZigBee主要模塊的基本測試流程如下:

??? (1)電源模塊測試。在空的PCB電路板上首先將電源模塊的相關元器件焊接好,上電后直接利用萬用表測量電源的輸出點,看是否得到要求的電壓值,以保證其他模塊能正常工作。

??? (2)微控制器部分測試。當電源模塊工作正常后,就需要測試GB60是否正常工作。對于MCU的測試主要就是通過BDM燒寫器與GB60通信,看是否能進行正常的擦除與寫入操作。若無法正常工作,則首先就應該仔細核對MCU支撐電路及電阻、電容的值是否正確,特別是晶振電路部分。GB60含有4 MHz的內部時鐘源,且外圍電路很少,所以比較容易調試通過。

??? (3)MC13192模塊測試。對于MC13192射頻模塊的測試,主要是通過讀寫其內部的寄存器和緩沖區來進行測試的。

??? (4)其他外圍模塊測試。串行通信(SCI)是通過PC實現基本的收發;測試小燈模塊,主要通過MCU將相應的I/O口置不同的值,看是否能點亮對應的小燈;測試液晶LCD模塊,看是否在液晶上顯示指定的字符。

4 結 語

??? 這里主要為ZigBee協議棧的實現提供了相應的硬件平臺設計。在MT-ZigBee平臺硬件芯片選型的基礎上,給出硬件平臺的整體框架,闡述了硬件平臺電源電路、GB60與MC13192接口電路和MC13192射頻模塊的詳細設計。最后,還對MT-ZigBee硬件平臺進行了各個模塊的測試。由于篇幅有限,實現ZigBee技術相關的底層協議棧設計和具體驗證協議棧可用性的應用實例在此中沒有介紹。

電子發燒友App

電子發燒友App

評論