基于AD9640的無(wú)線接收機(jī)設(shè)計(jì)

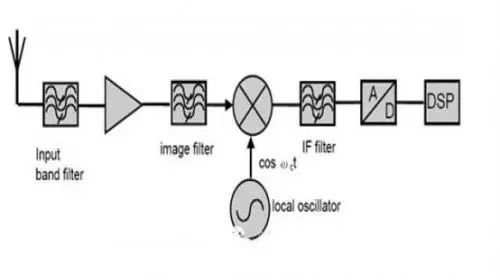

在無(wú)線接收機(jī)射頻前端硬件的實(shí)際制作中,中頻頻率的選擇、帶通濾波器的中心頻率與3dB帶寬、外部無(wú)源器件的使用等設(shè)計(jì)考慮,都需要隨著不同的系統(tǒng)應(yīng)用而仔細(xì)的規(guī)劃與調(diào)整,以便在適當(dāng)?shù)某杀鞠逻_(dá)到規(guī)定的性能。本文以認(rèn)知抗干擾為設(shè)計(jì)目標(biāo),主要討論了接收機(jī)鏈路的核心器件之一—高性能的ADC,敘述它們?nèi)绾螡M足對(duì)高性能的需求。此外,接收機(jī)系統(tǒng)的設(shè)計(jì)還包括器件的選擇和設(shè)計(jì),整體排版布線以及調(diào)試過(guò)程等步驟。

ADC設(shè)計(jì)

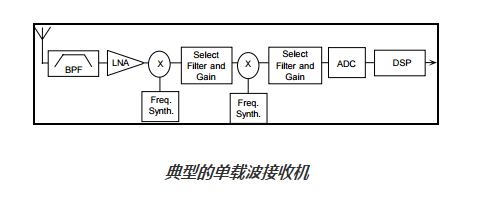

天線接收到的射頻信號(hào)必須經(jīng)過(guò)A/D數(shù)字化,以便后面的數(shù)字處理芯片進(jìn)行數(shù)字信號(hào)處理[1]。ADC影響接收機(jī)體系的功耗、工作頻率動(dòng)態(tài)范圍、接收帶寬和總體成本,其性能更是能夠影響接收機(jī)結(jié)構(gòu)的設(shè)計(jì)。理想情況下,在接收機(jī)的鏈路天線后直接進(jìn)行數(shù)據(jù)轉(zhuǎn)換,ADC對(duì)射頻信號(hào)直接進(jìn)行抽樣,這樣很大程度上繞過(guò)了模擬器件。而本文接收機(jī)體系結(jié)構(gòu)的一個(gè)重要特點(diǎn)是將ADC盡量靠近射頻前端,在較高的中頻直接進(jìn)行數(shù)字化,因此A/D設(shè)計(jì)是接收機(jī)設(shè)計(jì)的核心之一。

選定最優(yōu)采樣頻率

如果對(duì)采樣輸出信號(hào)進(jìn)行濾波的低通濾波器可以做到矩形系數(shù)為1,在無(wú)混疊的采樣率范圍內(nèi)選定任何一個(gè)頻率都是可以的(不考慮采樣時(shí)鐘的抖動(dòng))。但是實(shí)際上,這樣的濾波器是做不出來(lái)的,即使是矩形系數(shù)接近于1的低通濾波器也很難實(shí)現(xiàn)。如果后續(xù)的低通濾波器在過(guò)渡帶里面沒(méi)有頻譜的平移轉(zhuǎn)換,那么,即使矩形系數(shù)大一些也不會(huì)改變?cè)盘?hào)的頻譜結(jié)構(gòu),這也就意味著平移頻譜之間的間隔應(yīng)該越大越好。對(duì)于無(wú)混疊的采樣率來(lái)說(shuō),并不是頻率越高間隔越大,頻譜間隔最大的無(wú)混疊采樣率在降低后續(xù)低通濾波器的設(shè)計(jì)難度上是最優(yōu)的。

本文首先討論無(wú)混疊采樣率與平移的頻譜間隔的關(guān)系,然后結(jié)合方案選擇一個(gè)最優(yōu)的采樣頻率。

對(duì)圖1中虛線所示的頻譜塊,其左間距表示為:

-fH+(m-1)fs-[fH-(m-1)fs]=2(m-1)fs-2fH (m=1, 2, 3…)

右間距表示為:

fL-(-fL+mfs)=-mfs+2fL

使頻譜間隔最大條件是頻譜塊的左間距等于右間距:

2mfs-2fH=-mfs+2fL

即

![]()

比如天線接收的信號(hào)是75MHz中頻,帶寬1MHz的信號(hào),所以使頻譜間隔最大的采樣頻率為:fs=133.3333、66.6667、33.3333、26.6667MHz…(m=1, 2, 3, 4…)。注意,上面所指的頻譜間隔最大是對(duì)于相應(yīng)的m而言的,對(duì)于不同的m來(lái)說(shuō),間隔的絕對(duì)值隨m的增大而減小。

由于超過(guò)100MHz的高精度A/D器件價(jià)格昂貴,我們選擇m=2,這時(shí)的無(wú)失真采樣頻率fs的范圍是50.3333MHz≤fs≤75.5100MHz。同時(shí)考慮到ADC采樣頻率與中頻濾波器的帶寬之間必須滿足一定的關(guān)系:

fs≥B+B×w

其中w是該中頻帶通濾波器的矩形系數(shù),本文設(shè)為:w=3。此時(shí),ADC采樣通帶不會(huì)發(fā)生混疊,但過(guò)渡帶將會(huì)混疊,直到ADC采樣頻率增大到上式右邊的兩倍后,過(guò)渡帶才不會(huì)混疊。從本質(zhì)上看,還是會(huì)“混疊”的,但此時(shí)“混疊”的信號(hào)已被衰減得很微弱,比如衰減到比通帶信號(hào)小70dB以上。

最后考慮到后續(xù)DDC器件進(jìn)行速率轉(zhuǎn)換后輸出速率為8MHz(由于ADC和后續(xù)算法處理要求),采樣得到的信號(hào)速率最好是2的整數(shù)倍,同時(shí)又考慮到采樣時(shí)對(duì)信號(hào)頻段確定和控制的方便,最優(yōu)的采樣頻率選定為64MHz。這個(gè)采樣頻率產(chǎn)生的頻譜間隔對(duì)后續(xù)濾波器的設(shè)計(jì)也是足夠的。

器件選擇

綜合采樣精度和速率的要求對(duì)ADC進(jìn)行選擇:16位的ADC可以達(dá)到大約96dB的信噪比,但是精度達(dá)到16位同時(shí)速度超過(guò)60 MHz 的ADC價(jià)格非常昂貴且不易購(gòu)買到;14位的ADC可以達(dá)到大約84dB的信噪比,也可以滿足要求,還可以買到速度更快的產(chǎn)品。本設(shè)計(jì)選擇14位雙通道A/D器件AD9640[2]進(jìn)行采樣。其主要性能為:可選最大采樣速率80、105、125、150MSPS;采樣精度14位;無(wú)雜散動(dòng)態(tài)范圍85dB@125MSPS;信噪比71.8dB@ 125MSPS;低功耗750mW@125MSPS。

其中采樣速率的改變可通過(guò)改變輸入時(shí)鐘來(lái)實(shí)現(xiàn),從而可實(shí)現(xiàn)在不改變硬件的情況下通過(guò)軟件來(lái)擴(kuò)展。

設(shè)計(jì)高性能ADC之前的“前端”或輸入配置,是獲取所需系統(tǒng)性能的關(guān)鍵所在。整個(gè)設(shè)計(jì)的優(yōu)化[3]取決于許多因素,其中包括應(yīng)用的特點(diǎn)、系統(tǒng)劃分,以及ADC 的構(gòu)架等。許多放大器都十分適合用于高速ADC 的前端電路。ADA4937 能被用于150MHz以下的頻率;由于它能處理很大的輸出共模電壓范圍,因此它的主要優(yōu)勢(shì)是應(yīng)用于ADC 的直流耦合應(yīng)用中。對(duì)于窄帶或諧振應(yīng)用,使濾波器與放大器的輸出阻抗匹配,來(lái)消除ADC 的輸入電容。通常使用一個(gè)多極點(diǎn)濾波器來(lái)消除感興趣頻率范圍外的寬帶噪聲。

接收機(jī)PCB設(shè)計(jì)

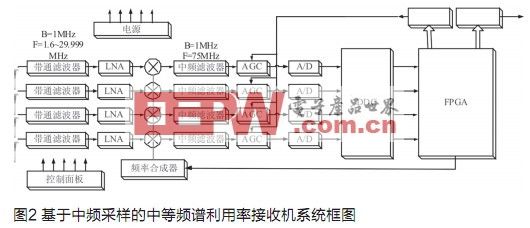

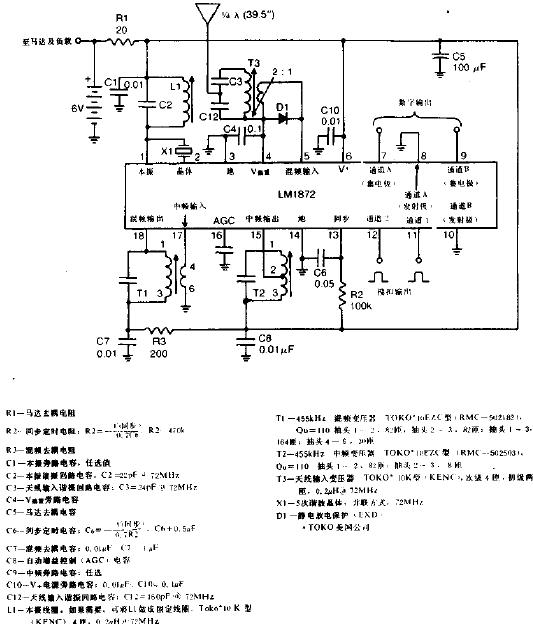

基于圖2的接收機(jī)框圖(圖中DDC使用四通道數(shù)字下變頻器AD6635)和PCB設(shè)計(jì)的基本要求,可以提出本文接收機(jī)PCB排版布線的總體要求如下:

● 所有電源在PCB板頂層或/和底層應(yīng)留出散熱區(qū)[4];

● 所有盒子輸入輸出接口位于PCB板的底層;

● PCB板頂層和底層大面積敷銅并接地;

● 電源及其附屬元件靠近,獨(dú)立驅(qū)動(dòng)電源平面,電源平面為電源分配網(wǎng)絡(luò)。元器件供電從電源平面獲取,根據(jù)需要在靠近管腳處濾波;

● 所有電源線進(jìn)入盒子安裝“穿心電容”;

● 放大器直接接地,同時(shí)應(yīng)該屏蔽所有高增益放大器以防止它們產(chǎn)生振蕩。

ADC布線

在PCB原理圖中,模擬地的網(wǎng)絡(luò)標(biāo)號(hào)為AGND,數(shù)字地的網(wǎng)絡(luò)標(biāo)號(hào)為GND。在將A/D轉(zhuǎn)換器的模擬地和數(shù)字地引腳連接在一起時(shí),大多數(shù)的A/D轉(zhuǎn)換器是將AGND和DGND引腳通過(guò)最短的引線連接到同一個(gè)低阻抗的地上,任何與DGND連接的外部阻抗都會(huì)通過(guò)寄生電容將更多的數(shù)字噪聲耦合到芯片內(nèi)部的模擬電路上。從而需要把A/D轉(zhuǎn)換器的AGND和DGND引腳都連接到模擬地上,但這種方法會(huì)產(chǎn)生諸如數(shù)字信號(hào)去耦電容的接地端應(yīng)該接到模擬地還是數(shù)字地的問(wèn)題。

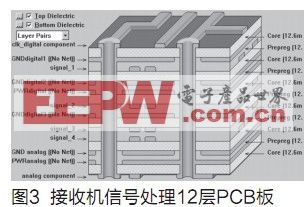

本設(shè)計(jì)的多通道接收機(jī)中A/D轉(zhuǎn)換器較多,如果在每一個(gè)A/D轉(zhuǎn)換器的下面都將模擬地和數(shù)字地連接在一起,則產(chǎn)生多點(diǎn)相連,模擬地和數(shù)字地之間的隔離就毫無(wú)意義。而如果不這樣連接,就又違反了廠商的要求。因此,最好的辦法是開始時(shí)就用統(tǒng)一地,將統(tǒng)一的地分為模擬部分和數(shù)字部分。這樣的布局布線既滿足了ADC器件廠商對(duì)模擬地和數(shù)字地引腳低阻抗連接的要求,同時(shí)又不會(huì)形成環(huán)路天線或偶極天線而產(chǎn)生電磁兼容(EMC)問(wèn)題。本文中AD9640的PCB制版安排見(jiàn)圖3。

接收機(jī)排版布線

本設(shè)計(jì)中,接收機(jī)布線堅(jiān)持2W原則:布線寬度為W,線間距不小于2W。PCB電路板分為模擬層和數(shù)字層兩個(gè)部分,共12層,制版安排見(jiàn)圖2,布線安排設(shè)計(jì)如下。

(1)模/數(shù)布線和元件排版分離。高速信號(hào)位于優(yōu)質(zhì)布線層clk-digital component和signal_1,高速信號(hào)線同低速信號(hào)線盡量遠(yuǎn)離,重要的低速信號(hào)線位于低速信號(hào)層signal_2 和signal_3。首先,保證關(guān)鍵高速時(shí)鐘和信號(hào)線布放于層clk-digital component和signal_1;然后保證關(guān)鍵低速信號(hào)線位于層signal_2 和signal_3;其次,低速信號(hào)線進(jìn)入高速布線層clk-digital component時(shí)應(yīng)該遠(yuǎn)離高速信號(hào)線(尤其是時(shí)鐘),高速信號(hào)線進(jìn)入低速布線層signal_2 和signal_3應(yīng)該遠(yuǎn)離低速信號(hào)線;最后,上述原則無(wú)法實(shí)施時(shí)應(yīng)該增加布線層。

(2)PCB板下三層為模擬電路,上七層為數(shù)字電路;層clk-digital component布線64MHz時(shí)鐘;層signal_1布線64MHz數(shù)字信號(hào),包括AD9640采樣64MHz高速數(shù)字信號(hào);層signal_2 和signal_3布線小于64MHz的所有其它數(shù)字信號(hào);將數(shù)字地GNDdigital2用多個(gè)過(guò)孔連接到GNDdigital1上,GNDdigital2僅僅為隔離模數(shù)兩個(gè)系統(tǒng),保護(hù)模擬信號(hào)免受數(shù)字干擾。GNDdigital1作為電源+5V的數(shù)字地;GNDdigital2作為+1.8V、+2.5V、+3.3V的數(shù)字地。

(3)FPGA、穩(wěn)壓片等所有核心元件位于頂層clk-digital component。

(4)各層敷銅接地方法:

● 層clk-digital component、signal_1、signal_2 、signal_3的大面積敷銅,并通過(guò)多個(gè)過(guò)孔連接到GNDdigital1;

● 層analog component的大面積敷銅,并通過(guò)多個(gè)過(guò)孔連接到GND analog。

(5)電源布線:電源線根據(jù)使用區(qū)域大面積填充,形成分割的電源平面。模擬電源平面PWRanalog分割為3.3V和5V兩個(gè)部分,數(shù)字電源平面PWRdigital分割為1.8V、2.5V、3.3V、5V四個(gè)部分。

實(shí)物制造及測(cè)試

圖4示出所設(shè)計(jì)的接收機(jī)實(shí)物圖,將其放置在一定的溫度、濕度和振動(dòng)壓力之下測(cè)試以檢查任何設(shè)計(jì)或工作的缺陷。

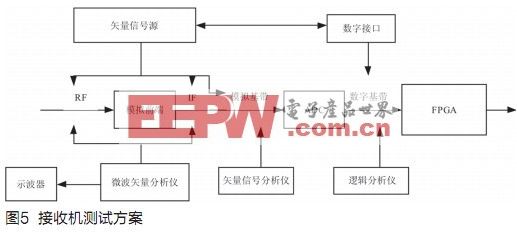

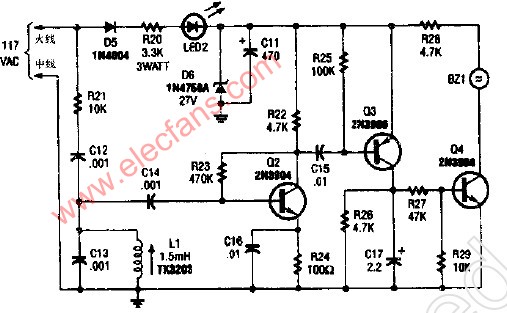

在本文設(shè)計(jì)接收機(jī)的調(diào)試過(guò)程中,用到儀器為:數(shù)字接口(Agilent N5102A),矢量信號(hào)源(Agilent E8267D),微波矢量分析儀(Agilent 89650A),示波器(Tektronix TDS 3032B),矢量信號(hào)分析儀(Agilent 89611A),邏輯分析儀(Agilent 16900A)。上述儀器,對(duì)接收機(jī)測(cè)試的連接圖如圖5所示。

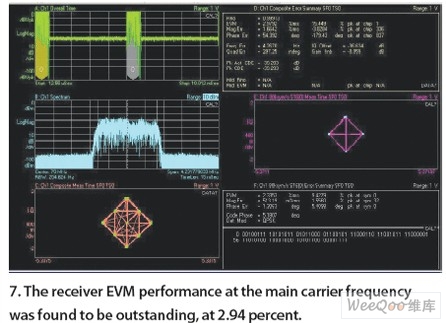

矢量信號(hào)源產(chǎn)生接收機(jī)需要的各種調(diào)制信號(hào)輸入到射頻前端,經(jīng)過(guò)測(cè)試可得,接收機(jī)體積小,性能穩(wěn)定,且便于調(diào)試,實(shí)際ADC采樣速率為63.488MHz;進(jìn)入FPGA數(shù)據(jù)速率為7.936MHz;FPGA處理主時(shí)鐘速率為63.488MHz; 2~30MHz帶寬、-113dBm~-36dBm的通信信號(hào)被接收的平均誤碼率為:Pe<10-5。因此,本接收機(jī)射頻前端抗干擾性強(qiáng),電磁兼容性好,滿足設(shè)計(jì)要求。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論