在verilog中狀態(tài)機(jī)的一種很常用的邏輯結(jié)構(gòu),學(xué)習(xí)和理解狀態(tài)機(jī)的運(yùn)行規(guī)律能夠幫助我們更好地書寫代碼,同時作為一種思想方法,在別的代碼設(shè)計(jì)中也會有所幫助。 一、簡介 在使用過程中我們常說

2024-02-12 19:07:39 1818

1818

本帖最后由 mr.pengyongche 于 2013-4-30 02:22 編輯

FSM 設(shè)計(jì)指導(dǎo)FSM分兩大類:米里型和摩爾型

2012-08-14 16:28:33

語句在執(zhí)行順序不同時導(dǎo)致不同的結(jié)果,則存在競爭.Nonblocking不 是一個類型;Blocking賦 值是一個單步過程,計(jì)算RHS,并更形LHS是不可中斷的.七條準(zhǔn)則:1.時序邏輯和鎖存器,使 用

2019-03-26 08:00:00

三個always段完成。三段式建模描述FSM的狀態(tài)機(jī)輸出時,只需指定case敏感表為次態(tài)寄存器, 然后直接在每個次態(tài)的case分支中描述該狀態(tài)的輸出即可,不用考慮狀態(tài)轉(zhuǎn)移條件。三段式描述方法雖然代碼結(jié)構(gòu)

2018-07-03 10:13:31

三個always段完成。三段式建模描述FSM的狀態(tài)機(jī)輸出時,只需指定case敏感表為次態(tài)寄存器, 然后直接在每個次態(tài)的case分支中描述該狀態(tài)的輸出即可,不用考慮狀態(tài)轉(zhuǎn)移條件。三段式描述方法雖然代碼結(jié)構(gòu)

2018-07-09 01:55:18

在verilog程序仿真時,發(fā)現(xiàn)雙向端口引腳ad_data沒有信號輸出,但是該信號跑到最后所有信號的下面,并且出現(xiàn)一列ad_data~result信號波形。這是什么原因?

2013-04-13 22:43:27

波形仿真時verilog 寫的狀態(tài)機(jī)被綜合掉,編譯沒有錯誤,狀態(tài)轉(zhuǎn)移也沒錯,什么原因可能導(dǎo)致這種問題呢。

2017-10-05 11:31:26

verilog實(shí)現(xiàn)I2C透傳,作為主從機(jī)設(shè)備之間的傳輸通道,但是SDA信號在cpld的端口進(jìn)行輸入、輸出狀態(tài)切換的邏輯始終處理不好,有沒有大佬能幫忙分析一下!

2022-08-17 11:22:27

verilog語法學(xué)習(xí)心得1.數(shù)字電路基礎(chǔ)知識: 布爾代數(shù)、門級電路的內(nèi)部晶體管結(jié)構(gòu)、組合邏輯電路分析與設(shè)計(jì)、觸發(fā)器、時序邏輯電路分析與設(shè)計(jì)2.數(shù)字系統(tǒng)的構(gòu)成: 傳感器AD數(shù)字處理器DA執(zhí)行部件3.

2012-01-12 15:15:21

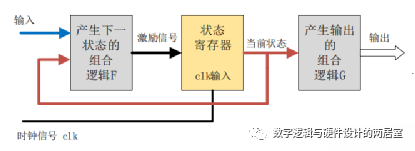

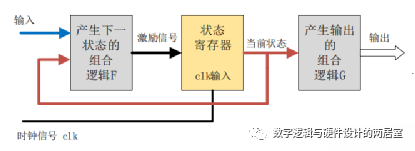

數(shù)字系統(tǒng)有兩大類有限狀態(tài)機(jī)(Finite State Machine,FSM):Moore狀態(tài)機(jī)和Mealy狀態(tài)機(jī)。Moore狀態(tài)機(jī) 其最大特點(diǎn)是輸出只由當(dāng)前狀態(tài)確定,與輸入無關(guān)。Moore狀態(tài)

2012-03-09 10:04:18

、掌握組合邏輯和時序邏輯電路的設(shè)計(jì)方法;5、掌握verilog代碼編寫規(guī)范;6、掌握Verilog HDL設(shè)計(jì)的精華有限狀態(tài)機(jī)FSM設(shè)計(jì)方法,掌握RTL設(shè)計(jì)方法;7、掌握基本IP核(pll/dcm

2012-09-07 14:19:38

、掌握組合邏輯和時序邏輯電路的設(shè)計(jì)方法;5、掌握verilog代碼編寫規(guī)范;6、掌握Verilog HDL設(shè)計(jì)的精華有限狀態(tài)機(jī)FSM設(shè)計(jì)方法,掌握RTL設(shè)計(jì)方法;7、掌握基本IP核(pll/dcm

2012-10-12 09:29:00

進(jìn)行仔細(xì)的分析計(jì)算才行。FPGA設(shè)計(jì)要點(diǎn)之二:FSMFSM:有限狀態(tài)機(jī)。這個可以說時邏輯設(shè)計(jì)的基礎(chǔ)。幾乎稍微大一點(diǎn)的邏輯設(shè)計(jì),幾乎都能看得到FSM.FSM分為moore型和merly型,moore型

2019-07-03 10:04:02

Unico為ST可編程傳感器提供了一個UI界面,方便用戶設(shè)計(jì)/調(diào)試ST FSM功能? 在Unico選擇了帶FSM的器件后,在GUI中會導(dǎo)入FSM的配置和調(diào)試窗口? FSM配置、調(diào)試窗口可通過點(diǎn)擊左邊圖標(biāo)進(jìn)入:

2023-09-06 06:43:02

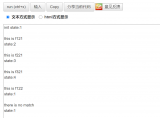

modelsim仿真verilog代碼 發(fā)現(xiàn)結(jié)果不符合邏輯代碼里面兩個信號相與結(jié)果出來的信號竟然是不定態(tài)這是什么原因?試了好幾次都沒找到原因代碼和仿真結(jié)果如下:

2014-05-01 15:07:40

modelsim仿真verilog代碼 發(fā)現(xiàn)結(jié)果不符合邏輯代碼里面兩個信號相與結(jié)果出來的信號竟然是不定態(tài)這是什么原因?試了好幾次都沒找到原因代碼和仿真結(jié)果如下:

2014-05-01 15:19:21

經(jīng)過網(wǎng)上的搜索及自己的實(shí)驗(yàn),總結(jié)在Modelsim仿真中顯示狀態(tài)機(jī)名稱的三種方法。下面以一個具體的實(shí)例進(jìn)行講解。實(shí)例功能:引入狀態(tài)機(jī)實(shí)現(xiàn)2分頻,這里使用狀態(tài)機(jī)完全只是為了說明如何在仿真中顯示狀態(tài)

2020-02-21 16:48:08

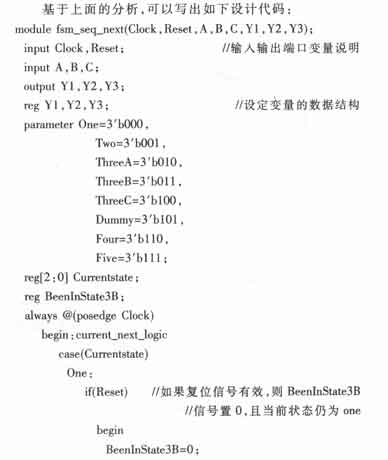

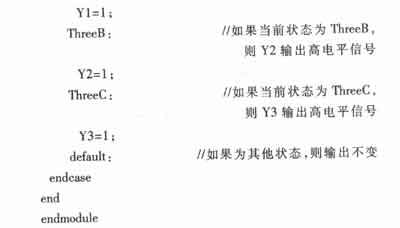

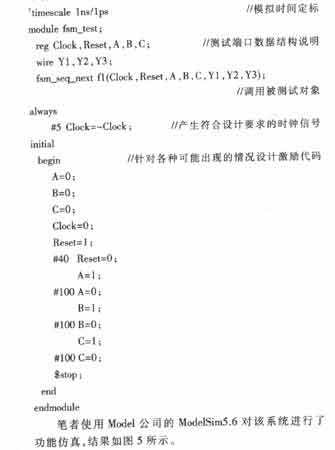

筆試時也很常見。[例1] 一個簡單的狀態(tài)機(jī)設(shè)計(jì)--序列檢測器序列檢測器是時序數(shù)字電路設(shè)計(jì)中經(jīng)典的教學(xué)范例,下面我們將用Verilog HDL語言來描述、仿真、并實(shí)現(xiàn)它。序列檢測器的邏輯功能...

2022-02-16 07:29:49

為什么在verilog中添加與邏輯的其他部分無關(guān)的進(jìn)程(帶有always語句)會影響輸出?我將該過程添加到verilog代碼中,即該過程中的一個寄存器將根據(jù)狀態(tài)機(jī)中的某些信號變高或變低,并且此過程中

2019-03-27 07:37:35

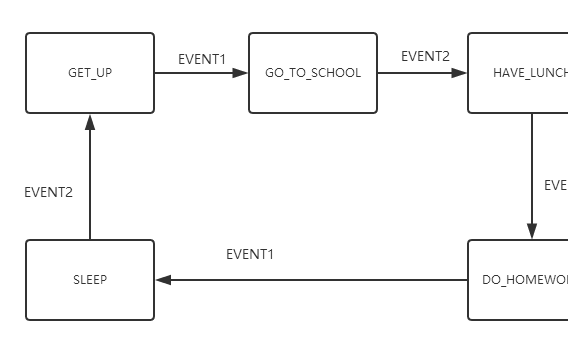

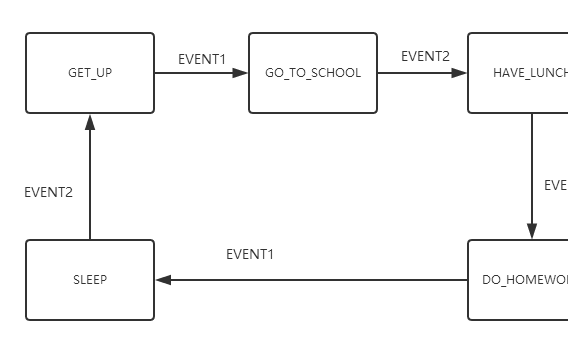

什么是有限狀態(tài)機(jī)FSM簡述 有限狀態(tài)機(jī)(以下用FSM指代)是一種算法思想,簡單而言,有限狀態(tài)機(jī)由一組狀態(tài)、一個初始狀態(tài)、輸入和根據(jù)輸入及現(xiàn)有狀態(tài)轉(zhuǎn)換為下一個狀態(tài)的轉(zhuǎn)換函數(shù)組成。在Gof的23種

2008-06-04 10:35:23

Spinal狀態(tài)機(jī)在使用SpinalHDL的狀態(tài)機(jī)時,生成的Verilog代碼里狀態(tài)機(jī)中狀態(tài)的定義全都是由宏定義來實(shí)現(xiàn)的。在真實(shí)的工程里,我們很少會講所有的Verilog代碼放在一個文件里。往往是一

2022-07-08 16:13:01

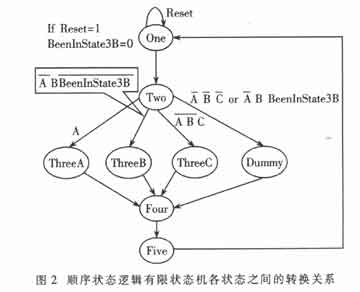

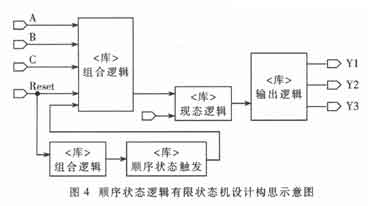

與當(dāng)時根據(jù)輸入的實(shí)際信號改變狀態(tài)的組合邏輯電路不同,順序邏輯電路具有某種形式的內(nèi)置“存儲器”。這意味著順序邏輯電路能夠考慮其先前的輸入狀態(tài)以及實(shí)際存在的輸入狀態(tài),因此順序電路會涉及某種“之前

2021-01-29 09:19:07

用戶界面(GUI)調(diào)試–延時的計(jì)算及反標(biāo)注(annotation)–性能仿真描述–如何使用NC Verilog仿真器進(jìn)行編譯及仿真–如何將設(shè)計(jì)環(huán)境傳送給NC Verilog–周期(cycle)仿真邏輯

2012-08-03 00:23:48

匿名飛控源碼整體的邏輯順序是怎樣的?

2022-01-20 07:50:36

基于Verilog HDL的DDS設(shè)計(jì)與仿真

2012-08-19 23:15:05

本文檔中的腕部動作識別是基于布局0實(shí)現(xiàn)的。腕部動作識別類型? FSM #1 – (左手)靜止/坐著/走路等場景下的抬腕亮屏動作? FSM #2 – (右手)靜止/坐著/走路等場景下的抬腕亮屏動作? FSM #3 – 跑步場景下的抬腕亮屏動作? FSM #4 – 水平向內(nèi)移動手腕亮屏動作

2023-09-06 08:03:51

的硬件和邏輯工程師面試中,狀態(tài)機(jī)設(shè)計(jì)幾乎是必選題目。本章在引入狀態(tài)機(jī)設(shè)計(jì)思 想的基礎(chǔ)上,重點(diǎn)討論如何寫好狀態(tài)機(jī)。 本文主要內(nèi)容如下: 狀態(tài)機(jī)的基本概念; 如何寫好狀態(tài)機(jī); 使用 Synplify Pro 分析 FSM。[hide] [/hide]

2011-10-24 11:43:11

什么是有限狀態(tài)機(jī)FSM呢?如何去實(shí)現(xiàn)有限狀態(tài)機(jī)FSM的程序設(shè)計(jì)呢?

2022-01-21 07:04:39

嗨,當(dāng)我們設(shè)計(jì)FSM時,如何選擇FSM是否使用粉狀或摩爾。謝謝娜文G K.

2020-05-20 11:05:26

實(shí)例:FSM實(shí)現(xiàn)10010串的檢測狀態(tài)轉(zhuǎn)移圖:初始狀態(tài)S0,a = 0,z = 0.如果檢測到1,跳轉(zhuǎn)到S1。下一狀態(tài)S1,a = 1,z = 0.如果檢測到0,跳轉(zhuǎn)到S2。下一狀態(tài)S2,a = 0

2016-06-27 22:13:36

假設(shè)我的Spartan-6設(shè)計(jì)包含由DCM或PLL生成的時鐘提供時鐘的有限狀態(tài)機(jī),在DCM / PLL實(shí)現(xiàn)鎖定后,我是否必須重置FSM?我擔(dān)心的是,在獲取鎖定時,DCM / PLL輸出可能以比FSM

2019-05-21 12:19:49

嗨,我想在我的VHDL代碼中使用fsm_style屬性來在SpartanXC3S200AN設(shè)備中的BRAM中實(shí)現(xiàn)我的狀態(tài)機(jī)。我在綜合后得到的代碼和警告如下:HDL代碼arcihtecture bla

2019-04-01 12:36:46

我想知道我是否可以使用邏輯單元(Spartan 6)的verilog代碼,這樣我就不必花時間為邏輯單元編寫verilog代碼。這可以節(jié)省我的時間,讓我專注于其他部分內(nèi)容,因?yàn)槲矣幸粋€很短的時間來完成

2020-03-10 09:45:39

進(jìn)行仔細(xì)的分析計(jì)算才行。FPGA設(shè)計(jì)要點(diǎn)之二:FSMFSM:有限狀態(tài)機(jī)。這個可以說時邏輯設(shè)計(jì)的基礎(chǔ)。幾乎稍微大一點(diǎn)的邏輯設(shè)計(jì),幾乎都能看得到FSM.FSM分為moore型和merly型,moore型

2019-08-30 07:30:00

這個FSM的要求是,時鐘為50Mhz,如果input持續(xù)為1長達(dá)30ms,那么output為1。如果input持續(xù)為0長達(dá)30ms,那么output為0。別的情況下,就不改變output。

2017-05-02 14:33:50

什么是狀態(tài)機(jī)?簡單來說,就是通過不同的狀態(tài)遷移來完成一些特定的順序邏輯。硬件的并行性決定了用Verilog描述的硬件實(shí)現(xiàn)(譬如不同的always語句)都是并行執(zhí)行的,那么如果希望分多個時間完成一個

2014-09-25 09:35:29

問題:基于Cadence這類硬件仿真的電路,有其他較為簡單的方法去實(shí)現(xiàn)Verilog(或VHDL、或C/C++等)與硬件電路的聯(lián)合仿真嗎?當(dāng)然也有比較強(qiáng)力的辦法:自己已經(jīng)知道觸發(fā)邏輯的功能,按照IBIS、Pspice的規(guī)范,自己編寫相關(guān)的模型,這個辦法肯定是可以的,不過難度挺高。求大神指導(dǎo)指導(dǎo),謝謝。

2018-06-02 09:44:22

嗨,大家好正如我在標(biāo)題中所說,我有兩個有限狀態(tài)機(jī),其中一個將多次運(yùn)行另一個(現(xiàn)在是兩個)。計(jì)劃具有從1到第2 FSM的信號,直到它到達(dá)初始狀態(tài)為止。然后初始狀態(tài)將驅(qū)動“標(biāo)志”信號0.然后第一個FSM

2018-11-01 16:15:47

用戶可使用UML從不同角度對系統(tǒng)進(jìn)行建模,但不同視圖間存在信息冗余,可能導(dǎo)致視圖不一致問題。該文針對具有多種邏輯語義的順序圖提出分析方法,為復(fù)雜層次結(jié)構(gòu)的狀態(tài)圖引

2009-04-16 08:43:39 27

27 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 FSM設(shè)計(jì)指導(dǎo):做了一段時間邏輯,遇到復(fù)雜的時序邏輯設(shè)計(jì)時,遇到了瓶頸。于是想到了用“狀態(tài)機(jī)”進(jìn)行設(shè)計(jì)。總結(jié)了一些很基礎(chǔ)的知識,與大家共享!以 Verilog 語言為例。

2009-11-01 14:48:42 32

32 分析了模擬硬件描述語言 Verilog-A 的特點(diǎn)及模型結(jié)構(gòu),根據(jù)仿真速度和仿真精度的折衷考慮,設(shè)計(jì)實(shí)現(xiàn)了模擬開關(guān)、帶隙基準(zhǔn)電壓源及運(yùn)放的Verilog-A 行為模型。根據(jù)數(shù)模轉(zhuǎn)換器

2009-11-21 15:37:55 30

30 復(fù)雜數(shù)字邏輯系統(tǒng)的Verilog

2010-11-01 17:03:59 0

0 FSM 分兩大類:米里型和摩爾型。

組成要素有輸入(包括復(fù)位),狀態(tài)(包括當(dāng)前狀態(tài)的操作),狀態(tài)轉(zhuǎn)移條件,狀態(tài)的輸出條件。

設(shè)計(jì)FSM 的方法和技巧多種

2010-11-19 16:07:26 148

148

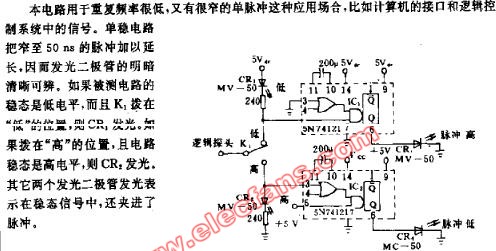

邏輯狀態(tài)探頭電路圖

2008-12-24 14:55:10 757

757

基于SPW-FSM Editor的CPM調(diào)制器的建模

CPM調(diào)制是一種非線性有記憶調(diào)制方式,其信號內(nèi)在的狀態(tài)轉(zhuǎn)移特性更適合于用有限狀態(tài)機(jī)(FSM)來描述。SPW的FSM Editor是一個簡單易用的FSM建模

2009-03-28 16:29:45 901

901 Verilog HDL語言實(shí)現(xiàn)時序邏輯電路

在Verilog HDL語言中,時序邏輯電路使用always語句塊來實(shí)現(xiàn)。例如,實(shí)現(xiàn)一個帶有異步復(fù)位信號的D觸發(fā)器

2010-02-08 11:46:43 4468

4468 順序控制,順序控制是什么意思

順序控制就是按照生產(chǎn)工藝預(yù)先規(guī)定的順序,在各個輸入信號的作用下,根據(jù)內(nèi)部狀態(tài)和時間的順序,在生產(chǎn)過程

2010-03-18 14:24:39 6635

6635 FSM 分兩大類:米里型和摩爾型。 組成要素有輸入(包括復(fù)位),狀態(tài)(包括當(dāng)前狀態(tài)的操作),狀態(tài)轉(zhuǎn)移條件,狀態(tài)的輸出條件。 設(shè)計(jì)FSM 的方法和技巧多種多樣,但是總結(jié)起來有兩大

2011-10-09 16:31:25 0

0 This paper will discuss a variety of issues regarding FSM design using Synopsys Design Compiler1. Verilog and VHDL coding styles will be prese

2011-12-21 14:21:51 47

47 設(shè)計(jì)FSM的方法和技巧多種樣,但是總結(jié)起來有兩大類:第一將狀態(tài)轉(zhuǎn)移態(tài)的操作和判斷等寫到一個模塊。另一種是將狀態(tài)轉(zhuǎn)移單獨(dú)寫成個模塊,將狀態(tài)的操作和判斷等寫到另一個中代碼

2011-12-24 00:48:00 66

66 有許多可綜合狀態(tài)機(jī)的Verilog代碼描述風(fēng)格,不同代碼描述風(fēng)格經(jīng)綜合后得到電路的物理實(shí)現(xiàn)在速度和面積上有很大差別。優(yōu)秀的代碼描述應(yīng)當(dāng)易于修改、易于編寫和理解,有助于仿真和調(diào)

2011-12-24 00:52:00 30

30 電子發(fā)燒友網(wǎng)核心提示: 本例程是Verilog HDL源代碼:關(guān)于基本組合邏輯功能中雙向管腳的功能實(shí)現(xiàn)源代碼。 Verilog HDL: Bidirectional Pin This example implements a clocked bidirectional pin in Verilog HDL.

2012-10-15 11:28:26 1525

1525 Verilog HDL 數(shù)字設(shè)計(jì)教程【作者:賀敬凱;出版社:西安電子科技大學(xué)出版社】(本資料為ppt) 內(nèi)容簡介:介紹了Verilog HDL語言,狀態(tài)機(jī)設(shè)計(jì),仿真,還有好幾個可綜合設(shè)計(jì)的舉例,除了

2012-11-28 13:43:11 489

489 電子發(fā)燒友網(wǎng)站提供《數(shù)字邏輯基礎(chǔ)與Verilog設(shè)計(jì)(原書第2版).txt》資料免費(fèi)下載

2014-10-22 15:30:31 0

0 八選一多路選擇器 Verilog代碼 附仿真結(jié)果(modelsim仿真)

2016-03-28 15:27:42 32

32 =OTHERmessage... ),使得我們在設(shè)計(jì)FSM時需要手動編寫HDL代碼。那如何快速把HDL代碼轉(zhuǎn)換為圖形化的FSM狀態(tài)轉(zhuǎn)移圖呢?利用ISE和ModelSim配合就行了。

2019-10-06 15:47:00 3426

3426

建模描述FSM的狀態(tài)機(jī)輸出時,只需指定case敏感表為次態(tài)寄存器, 然后直接在每個次態(tài)的case分支中描述該狀態(tài)的輸出即可,不用考慮狀態(tài)轉(zhuǎn)移條件。 三段式描述方法雖然代碼結(jié)構(gòu)復(fù)雜了一些,但是換來的優(yōu)勢是:使FSM做到了同步寄存器輸出,消除了組合邏輯輸

2017-02-09 09:42:49 939

939 HDL代碼設(shè)計(jì)中重要的內(nèi)容之一就是設(shè)計(jì)程序的狀態(tài)機(jī)FSM,狀態(tài)轉(zhuǎn)換控制著整個程序的流程,為了理解程序,我們經(jīng)常需要把狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換圖畫出來,這樣看起來很直觀,但是,有沒有辦法自動生成狀態(tài)轉(zhuǎn)換圖呢?

2017-02-10 15:39:49 14477

14477

有限狀態(tài)機(jī)(FSM)是一種常見的電路,由時序電路和組合電路組成。設(shè)計(jì)有限狀態(tài)機(jī)的第一步是確定采用Moore狀態(tài)機(jī)還是采用Mealy狀態(tài)機(jī)。

2017-02-11 13:51:40 3881

3881

在FPGA對Flash控制操作中,有限狀態(tài)機(jī)(Finite State Machine,FSM)與多進(jìn)程描述方式相比有著層次分明、結(jié)構(gòu)清晰、易于修改和移植的明顯優(yōu)勢而被廣泛應(yīng)用。傳統(tǒng)狀態(tài)機(jī)在描述實(shí)現(xiàn)

2017-11-17 02:30:07 3184

3184

本文首先介紹了verilog的概念和發(fā)展歷史,其次介紹了verilog的特征與Verilog的邏輯門級描述,最后介紹了Verilog晶體管級描述與verilog的用途。

2018-05-14 14:22:44 43434

43434

有限狀態(tài)機(jī)(Finite State Machine, FSM),根據(jù)狀態(tài)機(jī)的輸出是否與輸入有關(guān),可分為Moore型狀態(tài)機(jī)和Mealy型狀態(tài)機(jī)。Moore型狀態(tài)機(jī)輸出僅僅與現(xiàn)態(tài)有關(guān)和Mealy

2018-06-25 08:42:00 3638

3638 同時大家要明白verilog不是不能實(shí)現(xiàn)順序執(zhí)行,而是實(shí)現(xiàn)順序執(zhí)行并不像語法那么直觀,最簡單的順序執(zhí)行方法就是用狀態(tài)機(jī)去控制每一個寄存器的跳變,C/C++編程也可以認(rèn)為本質(zhì)上就是大型的一個狀態(tài)機(jī),verilog要做到那樣也只是做成狀態(tài)機(jī)去模擬他的工作。只要是數(shù)字電路能夠?qū)崿F(xiàn)的,F(xiàn)PGA都可以做到。

2018-08-31 16:45:52 20818

20818 設(shè)計(jì)同步有限狀態(tài)機(jī)(FSM)是數(shù)字邏輯工程師的共同任務(wù)。本文將討論SimopySesign CPLILRIL1關(guān)于FSM設(shè)計(jì)的各種問題。Verilog和VHDL編碼風(fēng)格將被呈現(xiàn)。將使用真實(shí)世界的例子來比較不同的方法。

2018-09-25 08:00:00 6

6 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Verilog-HDL做CPLD設(shè)計(jì)的時序邏輯電路的實(shí)現(xiàn)。

2018-12-12 16:25:46 8

8 有限狀態(tài)機(jī)(finite state machine)簡稱FSM,表示有限個狀態(tài)及在這些狀態(tài)之間的轉(zhuǎn)移和動作等行為的數(shù)學(xué)模型,在計(jì)算機(jī)領(lǐng)域有著廣泛的應(yīng)用。FSM是一種邏輯單元內(nèi)部的一種高效編程方法,在服務(wù)器編程中,服務(wù)器可以根據(jù)不同狀態(tài)或者消息類型進(jìn)行相應(yīng)的處理邏輯,使得程序邏輯清晰易懂。

2019-05-15 16:53:39 1813

1813

Verilog HDL是一種硬件描述語言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2019-11-28 07:02:00 2638

2638 的數(shù)學(xué)模型,是一種邏輯單元內(nèi)部的高效編程方法,可以根據(jù)不同狀態(tài)或者消息類型進(jìn)行相應(yīng)的處理邏輯,使得程序邏輯清晰易懂。 函數(shù)指針實(shí)現(xiàn)FSM 使用函數(shù)指針實(shí)現(xiàn)FSM可以分為3個步驟 建立相應(yīng)的狀態(tài)表和動作查詢表 根據(jù)狀態(tài)表、事件、

2020-10-19 09:36:53 2141

2141

“本文主要分享了在Verilog設(shè)計(jì)過程中狀態(tài)機(jī)的一些設(shè)計(jì)方法。 關(guān)于狀態(tài)機(jī) 狀態(tài)機(jī)本質(zhì)是對具有邏輯順序或時序順序事件的一種描述方法,也就是說具有邏輯順序和時序規(guī)律的事情都適用狀態(tài)機(jī)描述。狀態(tài)

2021-06-25 11:04:43 2249

2249 本文將介紹如何使用Icarus Verilog+GTKWave來進(jìn)行verilog文件的編譯和仿真。 Icarus Verilog Icarus Verilog極其小巧,支持全平臺

2021-07-27 09:16:50 4539

4539

VHDL與Verilog硬件描述語言在數(shù)字電路的設(shè)計(jì)中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設(shè)計(jì)復(fù)雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2021-08-04 14:16:44 3307

3307 筆試時也很常見。 [例1] 一個簡單的狀態(tài)機(jī)設(shè)計(jì)--序列檢測器 序列檢測器是時序數(shù)字電路設(shè)計(jì)中經(jīng)典的教學(xué)范例,下面我們將用Verilog HDL語言來描述、仿真、并實(shí)現(xiàn)它。 序列檢測器的邏輯功能描述

2021-08-10 16:33:55 6561

6561

筆試時也很常見。[例1] 一個簡單的狀態(tài)機(jī)設(shè)計(jì)--序列檢測器序列檢測器是時序數(shù)字電路設(shè)計(jì)中經(jīng)典的教學(xué)范例,下面我們將用Verilog HDL語言來描述、仿真、并實(shí)現(xiàn)它。序列檢測器的邏輯功能...

2021-12-17 18:28:40 15

15 綜合工具讀入源文件,通過綜合算法將設(shè)計(jì)轉(zhuǎn)化為網(wǎng)表,比如DC。能夠綜合的特性要求Verilog語言能夠描述信號的各種狀態(tài)(0,1,x,z)、信號和模塊的連接(例化)以及模塊的邏輯(賦值以及各種運(yùn)算符)。

2022-07-07 09:53:52 727

727 Icarus Verilog(以下簡稱iverilog )號稱“全球第四大”數(shù)字芯片仿真器,也是一個完全開源的仿真器。

2022-08-15 09:11:07 4821

4821 TAP 控制器只能在 TCK 的上升沿改變狀態(tài),FSM 接下來跳轉(zhuǎn)到哪個狀態(tài)(next state),由 TMS 的電平以及 FSM 當(dāng)前的狀態(tài)(current state)決定。

2023-02-01 14:23:17 1855

1855 只作為語法設(shè)定來介紹,忽略了Verilog語言的軟件特性和仿真特性。使得初學(xué)者無法理解Verilog語言在行為級語法(過程塊、賦值和延遲)背后隱藏的設(shè)計(jì)思想。本文嘗試從仿真器的角度對Verilog語言的語法規(guī)則進(jìn)行一番解讀。

2023-05-25 15:10:21 642

642

只作為語法設(shè)定來介紹,忽略了Verilog語言的軟件特性和仿真特性。使得初學(xué)者無法理解Verilog語言在行為級語法(過程塊、賦值和延遲)背后隱藏的設(shè)計(jì)思想。本文嘗試從仿真器的角度對Verilog語言的語法規(guī)則進(jìn)行一番解讀。

2023-05-25 15:10:44 576

576

有限狀態(tài)機(jī)(Finite-State Machine,FSM),簡稱狀態(tài)機(jī),是表示有限個狀態(tài)以及在這些狀態(tài)之間的轉(zhuǎn)移和動作等行為的數(shù)學(xué)模型。

2023-06-01 15:23:39 1260

1260

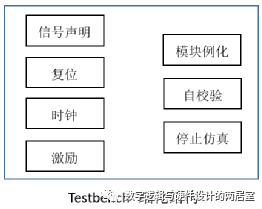

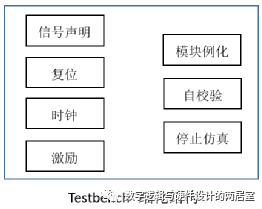

Verilog 代碼設(shè)計(jì)完成后,還需要進(jìn)行重要的步驟,即邏輯功能仿真。仿真激勵文件稱之為 testbench,放在各設(shè)計(jì)模塊的頂層,以便對模塊進(jìn)行系統(tǒng)性的例化調(diào)用進(jìn)行仿真。

2023-06-02 11:35:25 1085

1085

Verilog 是一種用于數(shù)字邏輯電路設(shè)計(jì)的硬件描述語言,可以用來進(jìn)行數(shù)字電路的仿真驗(yàn)證、時序分析、邏輯綜合。

2023-06-10 10:04:44 786

786

電子發(fā)燒友網(wǎng)站提供《在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯.zip》資料免費(fèi)下載

2023-06-15 09:14:49 0

0 電子發(fā)燒友網(wǎng)站提供《基于LSM6DSOX的FSM狀態(tài)機(jī)的腕部動作識別.pdf》資料免費(fèi)下載

2023-07-31 10:23:16 0

0 電子發(fā)燒友網(wǎng)站提供《Unico上FSM的使用.pdf》資料免費(fèi)下載

2023-07-31 15:23:04 0

0 芯片的設(shè)計(jì)規(guī)格和功能要求。根據(jù)這些要求,制定驗(yàn)證計(jì)劃,并編寫測試用例。 邏輯仿真:邏輯仿真是通過軟件工具模擬芯片電路的行為,驗(yàn)證電路的功能是否符合設(shè)計(jì)規(guī)格。在邏輯仿真中,會使用硬件描述語言(如Verilog或VHDL)來描述

2023-09-14 17:11:23 719

719 用邏輯筆測量信號的邏輯狀態(tài)屬于?? 信號的邏輯狀態(tài)是指該信號所表達(dá)的信息在邏輯上的真假性質(zhì),即1或0的狀態(tài)。在數(shù)字電路設(shè)計(jì)中,邏輯狀態(tài)是非常重要的概念,因?yàn)橹挥姓_地確定信號的邏輯狀態(tài),才能正確地

2023-09-19 17:16:11 694

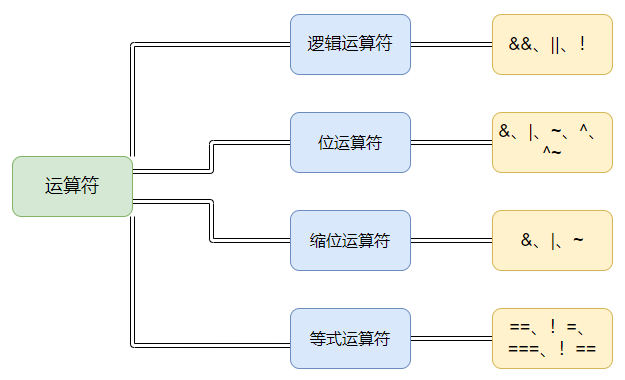

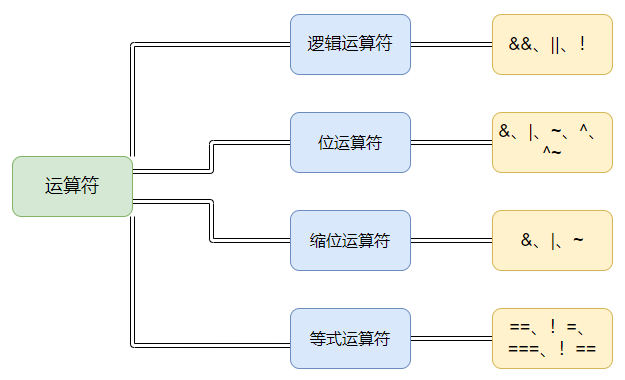

694 寫在前面 之前曾經(jīng)整理過verilog的各類運(yùn)算符的表達(dá)方式,但是在學(xué)習(xí)的過程中并未深入研究關(guān)于邏輯運(yùn)算符的相關(guān)知識,導(dǎo)致在實(shí)際使用過程中錯誤頻出,下面是我從網(wǎng)絡(luò)上整理的相關(guān)verilog的邏輯

2023-09-21 10:07:33 792

792

Verilog語言是一種硬件描述語言(HDL),用于描述數(shù)字邏輯電路和系統(tǒng)。它是一種非常強(qiáng)大且廣泛使用的語言,在數(shù)字電路設(shè)計(jì)中扮演著重要的角色。其中, inout 是Verilog中的一種信號類型

2024-02-23 10:15:48 176

176

電子發(fā)燒友App

電子發(fā)燒友App

評論