ESD(靜電放電)是CMOS電路中最為嚴重的失效機理之一,嚴重的會造成電路自我燒毀。論述了CMOS集成電路ESD保護的必要性,研究了在CMOS電路中ESD保護結(jié)構(gòu)的設(shè)計原理,分析了該結(jié)構(gòu)對版圖的相關(guān)

2017-12-05 09:03:40 12076

12076

靜電放電(ESD),應(yīng)該是造成所有電子元器件或集成電路系統(tǒng)造成過度電應(yīng)力(EOS: Electrical Over Stress)破壞的主要元兇。因為靜電通常瞬間電壓非常高(>幾千伏),所以

2021-08-10 15:54:40

RFX2402E是一個完全集成的、單芯片、單芯片的RFeIC(RF前端集成電路),集成了所有射頻功能今天的無線通信需要。RFX2402E架構(gòu)集成了PA、LNA、傳輸和接收交換電路、相關(guān)匹配網(wǎng)絡(luò)和諧

2019-11-08 17:07:27

CMOS集成CD4013觸摸開關(guān)

2019-05-06 09:47:24

2015年5月6號(周三),林恩咨詢將在上海主辦CMOS集成電路ESD防護設(shè)計課程。希望大家能帶著問題來,可以當場詢問,探討,交流,多與老師互動,同時我們也會考慮對有ESD需求的客戶安排

2015-04-22 22:19:54

1 . GMOS 集成電路輸入端的要求 CMOS 集成電路具有很高的輸入阻抗,其內(nèi)部輸入端接有二極管保護電路,以防范外界干擾、沖擊和靜電擊穿。 CMOS 集成電路的輸入端懸空時輸入阻抗高,易受外界

2018-12-13 09:47:31

最近在做CMOS功率放大器,用片上變壓器作為PA的chock電感,在chock電感的電源輸入端需要加ESD嗎?

2022-06-15 11:13:20

`CMOS射頻集成電路分析與設(shè)計`

2015-10-21 15:06:35

CMOS射頻集成電路功率放大器設(shè)計,CMOS射頻集成電路功率放大器設(shè)計,CMOS射頻集成電路功率放大器設(shè)計

2013-06-15 23:28:18

CMOS數(shù)字集成電路是什么?CMOS數(shù)字集成電路有什么特點?CMOS數(shù)字集成電路的使用注意事項是什么?

2021-06-22 07:46:35

、北橋等超大規(guī)模集成電路芯片廣泛采用CMOS(復(fù)合金屬氧化物半導(dǎo)體)材料,CMOS器件具有集成度高、成本低、速度快、能耗低的優(yōu)點,因此使用范圍很廣。然而,CMOS器件的一個致命的弱點是輸入阻抗很大,很

2013-07-15 09:45:33

靜電和靜電放電(ESD)在我們的日常生活中無處不在,尤其是當手持電子設(shè)備向輕薄小巧方向發(fā)展而且產(chǎn)品功能不斷增加時,它們的輸入/輸出端口也隨之增多,導(dǎo)致靜電放電進入系統(tǒng)并干擾或損壞集成電路,因此如何進

2013-02-21 10:54:18

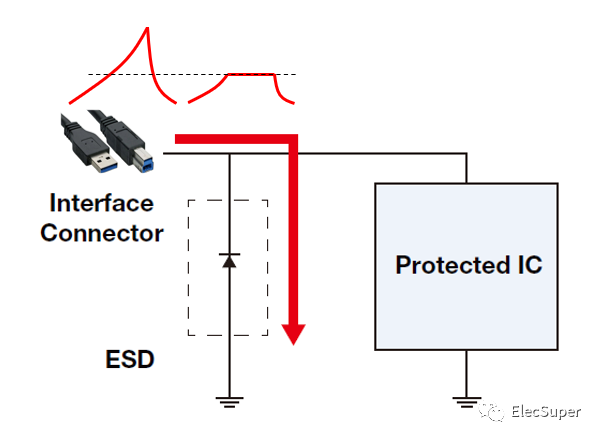

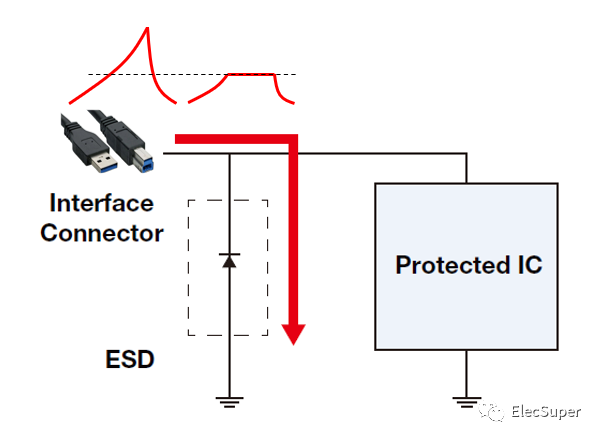

。大多數(shù)USB集成電路都是以CMOS工藝為基礎(chǔ)來設(shè)計和制造的,這導(dǎo)致它們對ESD造成的損害也很敏感,另外,USB端口是熱插拔系統(tǒng),極易受到由用戶或空氣放電造成的ESD影響。用戶在插拔任何USB外設(shè)

2013-11-20 15:43:19

[size=1em]導(dǎo)讀靜電是影響集成電路芯片可靠性的關(guān)鍵因素之一,為保證片上靜電器件有效地保護芯片,其設(shè)計指標需要滿足特定ESD設(shè)計窗口要求,正確理解指標含義有助于明確特定IC對ESD器件提出

2016-02-26 09:46:33

涵蓋:在DRAM、SRAM、CMOS圖像處理芯片、微處理器、模擬產(chǎn)品、射頻模塊中如何集成核心電路、電源總線以及信號引腳,以及這些整合將如何影響ESD的設(shè)計與集成。混合電壓、混合信號的架構(gòu)設(shè)計,以便于RF

2013-09-04 09:17:26

隨著電子技術(shù)的以及集成電路的發(fā)展,電子設(shè)備日趨小型化、多功能及智能化。然而高集成度的電路元件都可能因靜電電場和靜電放電(ESD)引起失效,導(dǎo)致電子設(shè)備鎖死、復(fù)位、數(shù)據(jù)丟失而影響設(shè)備正常工作,使

2021-01-06 17:26:05

一直以來,印刷電路板所扮演的角色都不僅僅是載體材料和元件分配層那么簡單,而是越來越多的功能被直接嵌入到電路板中。目前TDK集團利用CeraPad?成功研發(fā)了專門針對LED并且集成了ESD保護功能的超薄陶瓷基板。

2019-08-12 06:46:48

[size=1em]導(dǎo)讀LDMOS晶體管已廣泛應(yīng)用于電源管理集成電路、LED/LCD驅(qū)動器、手持和汽車電子等高壓功率集成電路。了解LDMOS的靜電防護性能,有益于高壓功率IC的片上靜電防護器件

2016-03-03 17:54:51

負責從同一個源產(chǎn)生所有設(shè)備的時鐘。這讓系統(tǒng)設(shè)計更加靈活,但需為每個給定設(shè)備指定幀時鐘和設(shè)備時鐘之間的關(guān)系。JESD204 – 為什么我們要重視它?就像幾年前LVDS開始取代CMOS成為轉(zhuǎn)換器數(shù)字接口

2019-06-17 05:00:08

LIS9412E特性? 專利的CCM工作模式? 前饋電流采樣,不燒燈珠? 過溫電流折返功能? 最精簡的系統(tǒng)結(jié)構(gòu)? 無輸入/輸出電解工作? 輸入/輸出電壓“零”距離? 集成高壓啟動、高壓供電功能

2019-04-11 10:20:30

設(shè)備(例如脈沖信號發(fā)生器等)在接到CMOS或NMOS集成電路輸入端以前必然讓器件先接通電源,同樣設(shè)備與器件斷開后器件才能斷開電源。 4、包含有CMOS管和NMOS管集成電路的印刷電路板僅僅是一個器件

2018-11-15 11:40:50

比較TTL集成電路與CMOS集成電路元件構(gòu)成高低電平范圍集成度比較:邏輯門電路比較元件構(gòu)成TTL集成電路使用(transistor)晶體管,也就是PN結(jié)。功耗較大,驅(qū)動能力強,一般工作電壓+5V

2021-07-26 07:33:00

TTL集成電路是什么?CMOS電路是什么?TTL集成電路和CMOS電路有哪些區(qū)別?

2021-11-02 07:58:45

目前應(yīng)用最廣泛的數(shù)字電路是什么?TTL電路和CMOS電路是什么?有哪些優(yōu)點?CMOS集成電路的性能特點有哪些?為什么BJT比CMOS速度要快?

2021-04-20 06:19:04

...............................................................................1ESD (Electrostatic Discharge) Protection in CMOS Integrated Circuits ..........................1目錄

2011-02-24 09:55:18

隨著射頻無線通信事業(yè)的發(fā)展和移動通訊技術(shù)的進步,射頻微波器件的性能與速度成為人們關(guān)注的重點,市場對其的需求也日益增多。目前,CMOS工藝是數(shù)字集成電路設(shè)計的主要工藝選擇,對于模擬與射頻集成電路來說,有哪些選擇途徑?為什么要選擇標準CMOS工藝集成肖特基二極管?

2019-08-01 08:18:10

什么是高壓差分探頭?高壓差分探頭具有哪些功能?高壓差分探頭差分放大原理是指什么?

2021-11-05 08:40:23

。不過,日趨縮小的CMOS芯片已經(jīng)越來越不足以承受進行內(nèi)部2 kV等級的ESD保護所需要的面積。安森美半導(dǎo)體標準產(chǎn)品部亞太區(qū)市場營銷副總裁麥滿權(quán)指出:真正有效的ESD保護是不能完全集成到CMOS芯片之中

2013-01-04 14:58:24

的ESD保護是不能完全集成到CMOS芯片之中的! 其次,也可以在物理電路設(shè)計方面下功夫,較敏感的電路元件應(yīng)該盡量遠離通孔或接縫處,如果可能的話,線纜連接器的接地應(yīng)該要在系統(tǒng)信號引腳接觸前連接到系統(tǒng)的接地

2014-02-14 10:30:16

關(guān)于TTL集成電路與CMOS集成電路看完你就懂了

2021-09-28 09:06:34

CMOS模擬集成電路該如何去設(shè)計?這里有一份CMOS模擬集成電路設(shè)計手冊請查收。

2021-06-22 06:27:16

在CMOS集成電路中,小信號大信號分別指的是什么情況?

2023-04-25 09:24:47

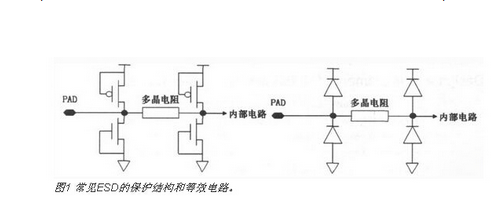

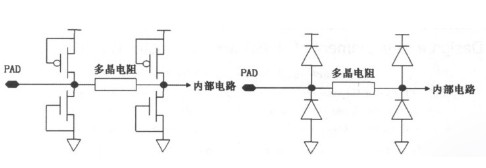

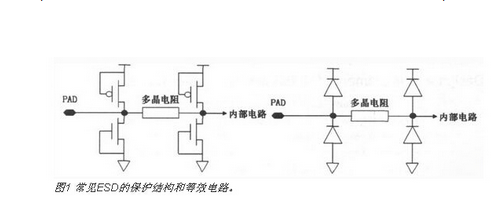

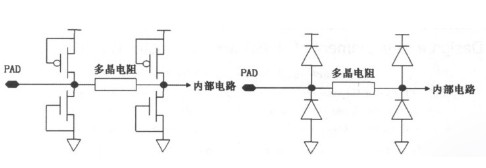

ESD(靜電放電)是CMOS電路中最為嚴重的失效機理之一,嚴重的會造成電路自我燒毀。論述了CMOS集成電路ESD保護的必要性,研究了在CMOS電路中ESD保護結(jié)構(gòu)的設(shè)計原理,分析了該結(jié)構(gòu)對版圖的相關(guān)要求,重點討論了在I/O電路中ESD保護結(jié)構(gòu)的設(shè)計要求。

2021-04-02 06:35:57

基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖該如何去設(shè)計?怎樣去驗證一種基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖?

2021-06-22 06:12:49

在PCB設(shè)計 中,可以通過分層、恰當?shù)牟季植季€和安裝實現(xiàn)PCB的抗ESD設(shè)計。在設(shè)計過程中,通過預(yù)測可以將絕大多數(shù)設(shè)計修改僅限于增減元器件。通過調(diào)整PCB布局布線,能夠很好地防范ESD。 來自人體

2017-04-14 10:50:10

如何在設(shè)計PCB時增強防靜電ESD功能??在PCB設(shè)計中,可以通過分層、恰當?shù)牟季植季€和安裝實現(xiàn)PCB的抗ESD設(shè)計。在設(shè)計過程中,通過預(yù)測可以將絕大多數(shù)設(shè)計修改僅限于增減元器件。通過調(diào)整PCB布局

2014-12-22 11:16:56

隨著CMOS集成電路產(chǎn)業(yè)的高速發(fā)展,越來越多的CMOS芯片應(yīng)用在各種電子產(chǎn)品中,但在電子產(chǎn)品系統(tǒng)的設(shè)計過程中,隨著CMOS工藝尺寸越求越小,單位面積上集成的晶體管越來越多,極大地降低了芯片的成本

2019-08-07 06:24:17

ESD的失效模式是什么?包括哪些?MOS集成電路中常用的提高ESD能力的手段有哪些?

2021-04-12 06:25:45

靜電放電(ESD)會對集成電路會造成什么樣的影響?如何進行ESD測試?

2021-04-07 06:29:14

本文給出了使用CMOS工藝設(shè)計的單片集成超高速4:1復(fù)接器。

2021-04-12 06:55:55

焊接絕緣柵(或雙柵)場效應(yīng)管以及CMOS集成塊時,因其輸入阻抗很高、極間電容小,少量的靜電荷即會感應(yīng)靜電高壓,導(dǎo)致器件擊穿損壞。筆者通過長期實踐摸索出下述焊接方法,取得令人滿意的效果。 1.焊絕緣

2021-05-13 07:27:36

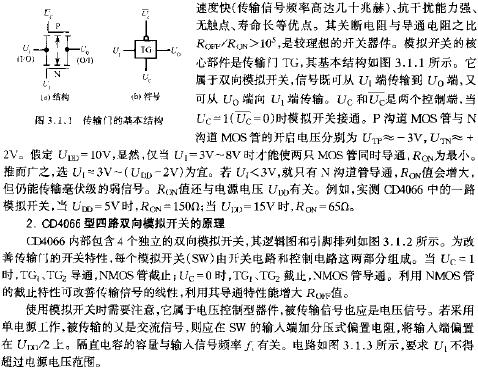

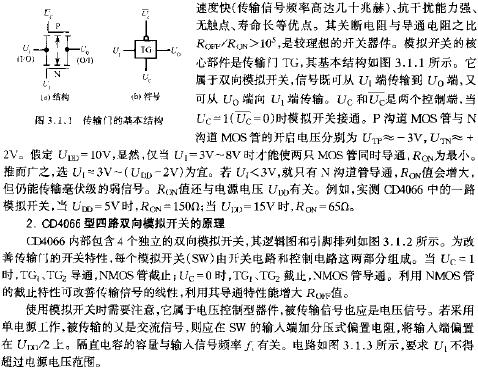

常用CMOS模擬開關(guān)引腳功能和工作原理CMOS模擬開關(guān)典型應(yīng)用舉例

2021-04-23 06:17:43

近年來,有關(guān)將CMOS工藝在射頻(RF)技術(shù)中應(yīng)用的可能性的研究大量增多。深亞微米技術(shù)允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發(fā)展。目前,幾個研究組已利用標準

2019-08-22 06:24:40

, ESD 失效電壓特性有較明顯改善, 可達3000V 以上。This paper proposes a modified Capacitor - Couple CMOS ESD protection

2009-12-23 16:33:58

CMOS模擬集成電路設(shè)計,一共5個部分

2016-05-15 09:30:43

模擬CMOS集成電路設(shè)計(拉扎維)

2020-05-10 09:00:22

模擬CMOS集成電路設(shè)計(拉扎維)

2020-05-13 09:21:13

模擬CMOS集成電路設(shè)計

2019-03-13 15:34:10

,模數(shù)轉(zhuǎn)換器或放大器輸入/輸出),因為這樣可以阻斷過壓、抑制未被TVS分流到地的剩余電流。 圖1. OVP開關(guān)功能框圖 圖1顯示了一個典型過壓保護開關(guān)的功能框圖;注意,該開關(guān)的ESD保護二極管未以其輸入

2021-11-23 13:30:06

VDD 或 VSS,并且要接觸良好。 3 所有低阻抗設(shè)備(例如脈沖信號發(fā)生器等)在接到 CMOS 或 NMOS 集成電路輸入端以前必然讓器件先接通電源,同樣設(shè)備與器件斷開后器件才能斷開電源。 4

2011-08-18 10:15:22

ESD保護,還擁有超低電容,能在GHz頻率范圍內(nèi)運行。NIV1161和NIV2161等器件擁有與前述器件相同的ESD保護硅芯片,同時集成了小信號MOSFET以實現(xiàn)限流功能,可為SoC提供電池短路和接地短路保護。這些集成式MOSFET具有低Rds(on),適用于每秒吉比特高數(shù)據(jù)速率的應(yīng)用。

2018-10-25 08:49:49

`CMOS射頻集成電路分析與設(shè)計`

2017-01-20 18:11:40

PCB抄板如何增強防靜電ESD功能?

2021-04-25 06:47:40

那位高手有CMOS元件國內(nèi)外集成電路對照表?

2013-04-21 22:36:57

摩爾定律對先進CMOS IC的ESD保護的影響 持續(xù)不斷的特征尺寸小型化趨勢,已經(jīng)使半導(dǎo)體制造商能夠在過去幾十年中通過把幾十億三極管集成到單一芯片之中來提高芯片性能、降低功耗及驅(qū)動成本的下降。盡管

2018-12-05 10:39:44

隨著現(xiàn)代社會的飛速發(fā)展,我們對電子設(shè)備的依賴與日俱增.現(xiàn)代電腦越來越多的采用低功率邏輯芯片,由于MOS的電介質(zhì)擊穿和雙極反向結(jié)電流的限制,使這些邏輯芯片對ESD非常敏感。大多數(shù)USB集成電路都是

2019-08-02 17:43:22

靜電放電(ESD,Electrostatic Discharge)給電子器件環(huán)境會帶來破壞性的后果。它是造成集成電路失效的主要原因之一。隨著集成電路工藝不斷發(fā)展,互補金屬氧化物半導(dǎo)體(CMOS,

2008-07-22 14:35:00 0

0 cmos射頻集成電路設(shè)計這本被譽為射頻集成電路設(shè)計指南的書全面深入地介紹了設(shè)計千兆赫(GHz)CMOS射頻集

2008-09-16 15:43:18 312

312 CMOS集成邏輯門的邏輯功能與參數(shù)測試一、實驗?zāi)康?.掌握CMOS集成門電路的邏輯功能和器件的使用規(guī)則;2.學會CMOS與非門主要參數(shù)的測試方法。二、預(yù)習要求1.復(fù)

2009-07-15 18:37:20 0

0 CMOS工藝中GG2NMOS結(jié)構(gòu)ESD保護電路設(shè)計:采用GG2NMOS 結(jié)構(gòu)的ESD 保護電路的工作原理和對其進行的ESD 實驗,提出了一種保護電路的柵耦合技術(shù)方案,并達到了預(yù)期效果. 通過實驗可以看出其性

2009-11-20 14:48:43 41

41 本文研究了在CMOS 工藝中I/O 電路的 ESD 保護結(jié)構(gòu)設(shè)計以及相關(guān)版圖的要求,其中重點討論了PAD 到VSS 電流通路的建立。關(guān)鍵詞:ESD 保護電路,ESD 設(shè)計窗口,ESD 電流通路Constru

2009-12-14 10:45:54 55

55 摘要:在Synopsys TCAD軟件環(huán)境下,結(jié)合中國科學院微電子研究所0.8Um標準CMOS工藝條件對于高壓CMOS器件進行了工藝和器件模擬。由于考慮到與標準CMOS工藝的兼容性,高壓CMOS器件均采

2010-05-06 10:19:31 64

64 摘要:靜電放電(ESD)對CMOS電路的可靠性構(gòu)成了很大威脅。隨著CMOS電路集成度的不斷提高,其對ESD保護的要求也更加嚴格。針對近年來SCR器件更加廣泛地被采用到CMOS靜電保護電路中的

2010-05-11 08:53:19 23

23 本文介紹了一種新穎的集成三漏CMOS磁敏傳感器.報道了該傳感器的電路原理、版圖設(shè)計及其研制結(jié)果.它具有結(jié)構(gòu)簡單、磁靈敏度高和使用方便等特點,且制造工藝與標準鋁柵CMOS工

2010-05-17 09:39:41 10

10 CMOS集成電路的性能及特點有哪些?

CMOS集成電路功耗低

CMOS集成電路采用場效應(yīng)管,且都是互補結(jié)構(gòu),工作時兩

2009-11-30 11:06:29 1212

1212 CMOS 集成電路使用操作準則

CMOS 集成電路使用操作準則 所有 MOS 集成電路 (包括 P 溝道 MOS, N 溝道 MOS, 互補 MOS — CMOS 集成電路) 都有一層絕緣柵,

2009-11-30 11:08:12 824

824 1、CMOS集成模擬開關(guān)的基本原理

CMOS模擬開關(guān)具有電源電壓范圍寬(4000系列

2010-12-06 13:06:53 3991

3991

CMOS工藝發(fā)展到深亞微米階段,芯片的靜電放電(ESD)保護能力受到了更大的限制。因此,需要采取更加有效而且可靠的ESD保護措施。基于改進的SCR器件和STFOD結(jié)構(gòu),本文提出了一種新穎

2012-03-27 16:27:34 4012

4012 TDK集團新近推出全新的超薄陶瓷基板CeraPad?,其采用多層結(jié)構(gòu)設(shè)計,并在其中集成了ESD保護功能,無需其它獨立的ESD元件。這種創(chuàng)新的基板可滿足極致微型化的需求,并且還具有最佳的ESD保護功能,因此在敏感應(yīng)用中可實現(xiàn)最大集成度的ESD保護。

2017-04-10 14:56:08 1417

1417 在智能手機和汽車電子領(lǐng)域,隨著客戶對設(shè)備安全性、可靠性以極致微型化要求的不斷提升,ESD保護技術(shù)也不斷向前發(fā)展,比如汽車頭燈上的先進LED系統(tǒng)以及緊湊的相機閃光燈都需要更好的ESD保護能力,因為汽車ECU、智能手機和平板電腦中的集成電路對靜電非常敏感。

2017-04-11 11:03:40 1077

1077 一直以來,印刷電路板所扮演的角色都不僅僅是載體材料和元件分配層那么簡單,而是越來越多的功能被直接嵌入到電路板中。目前TDK集團利用CeraPad?成功研發(fā)了專門針對LED并且集成了ESD保護功能的超薄陶瓷基板。

2018-05-07 11:51:00 1400

1400

CMOS集成電路使用時的技術(shù)要求,CMOS IC requirements

關(guān)鍵字:CMOS集成電路使用時的技術(shù)要求

CMOS集成

2018-09-20 18:20:38 899

899 ESD保護電路的設(shè)計目的就是要避免工作電路成為ESD的放電通路而遭到損害,保證在任意兩芯片引腳之間發(fā)生的ESD,都有適合的低阻旁路將ESD電流引入電源線。這個低阻旁路不但要能吸收ESD電流,還要能箝位工作電路的電壓,防止工作電路由于電壓過載而受損。

2019-03-04 14:24:01 4168

4168

從電路設(shè)計到芯片完成離不開集成電路的制備工藝,本章主要介紹硅襯底上的CMOS集成電路制造的工藝過程。有些CMOS集成電路涉及到高壓MOS器件(例如平板顯示驅(qū)動芯片、智能功率CMOS集成電路等),因此高低壓電路的兼容性就顯得十分重要,在本章最后將重點說明高低壓兼容的CMOS工藝流程。

2019-07-02 15:37:43 121

121 隨著CMOS集成電路產(chǎn)業(yè)的高速發(fā)展,越來越多的CMOS芯片應(yīng)用在各種電子產(chǎn)品中,但在電子產(chǎn)品系統(tǒng)的設(shè)計過程中,隨著CMOS工藝尺寸越求越小,單位面積上集成的晶體管越來越多,極大地降低了芯片的成本

2020-12-30 10:28:00 2

2 CMOS集成電路設(shè)計基礎(chǔ)免費下載。

2022-03-03 10:06:12 0

0 影響 ESD 保護要求的集成電路趨勢

2022-11-14 21:08:21 2

2 具有集成雙向 ESD 保護功能的差分通道共模 EMI 濾波器-PCMFXHDMI2BA_C_SER

2023-02-20 18:45:04 0

0 具有集成雙向 ESD 保護功能的差分通道共模 EMI 濾波器-PCMFXUSB3BA_C_SER

2023-02-20 18:47:47 0

0 具有集成 ESD 保護功能的差分通道共模 EMI 濾波器-PCMFXUSB3S_SER

2023-02-20 20:07:13 0

0 具有集成雙向 ESD 保護功能的差分通道共模 EMI 濾波器-PCMFXUSB3B_C_SER

2023-02-20 20:19:42 1

1 具有 ESD 保護功能的集成 4、6 和 8 通道無源濾波器網(wǎng)絡(luò)-IP4251_52_53_54-TTL

2023-02-27 18:30:35 0

0 具有集成 ESD 保護功能的差分通道共模 EMI 濾波器-PCMFXUSB30_SER

2023-03-01 18:47:19 0

0 具有集成 ESD 保護功能的差分通道共模 EMI 濾波器-PCMFXHDMI2S_SER

2023-03-01 18:47:31 0

0 具有集成 ESD 保護功能的差分通道共模 EMI 濾波器-PCMFXHDMI14S_SER

2023-03-01 18:47:42 0

0 具有集成 ESD 保護功能的差分通道共模 EMI 濾波器-PCMF2DFN1_PCMF3DFN1

2023-03-03 20:02:55 0

0 什么是CMOS集成電路?CMOS的主要功能是什么? CMOS是一種常見的集成電路技術(shù),其全稱為互補金屬氧化物半導(dǎo)體。CMOS技術(shù)和傳統(tǒng)的TTL集成電路技術(shù)相比,具有功耗低,內(nèi)部電路抗干擾能力強等優(yōu)點

2023-09-07 14:46:36 2193

2193 CMOS集成電路的性能及特點? CMOS(Complementary Metal-Oxide-Semiconductor)是一種廣泛應(yīng)用的集成電路(IC)制造技術(shù),它采用互補性金屬氧化物半導(dǎo)體材料

2023-12-07 11:37:35 668

668 靜電放電(ESD)是電子設(shè)備中一種常見的危害,它可能導(dǎo)致集成電路(IC)的損壞。對于CMOS IC來說,經(jīng)受過嚴重ESD電擊的可靠性會降低。

2023-12-15 15:32:09 219

219 靜電保護器件(ESD) 是由一個或多個 TVS 晶粒采用不同的電路拓撲制成具有特定功能的多路或單路 ESD 保護器件。

2024-02-17 16:01:00 571

571

電子發(fā)燒友App

電子發(fā)燒友App

評論