時鐘振蕩器的原理是將外部時鐘電路跟晶振放在同一個封裝里面,一般都有4個引腳了,兩條電源線為里面的時鐘電路提供電源,又叫做有源晶振,時鐘振蕩器。好多鐘振一般還要做一些溫度補償電路在里面,讓振蕩頻率能更加準確。晶振振蕩器的等效電路也可以認為是一個LCR振蕩電路。

2016-09-24 16:40:21 42695

42695

為設計提供可編程邏輯解決方案所固有的靈活性特點,以及定制門陣列(如ASIC)解決方案所具有的高性能及集成度。 增強DSP處理能力的傳統方法是采用多個處理器。選擇此類方案的缺點是成本昂貴,需要眾多附加

2011-02-17 11:21:37

的FPGA與其CPU結合──無論是以各自獨立的芯片或放在同一個封裝內、甚至同一片裸晶上的形式──以支持高性能運算(HPC)應用。 在2015年初,Lattice收購美商晶鐌(Silicon Image

2016-12-07 15:58:33

` 本帖最后由 OneyacSimon 于 2019-8-12 09:46 編輯

SiT1602B低功耗標準頻率振蕩器具有可編程驅動強度功能,可為特定應用提供簡單,靈活的工具來優化時鐘上升

2019-08-12 09:45:17

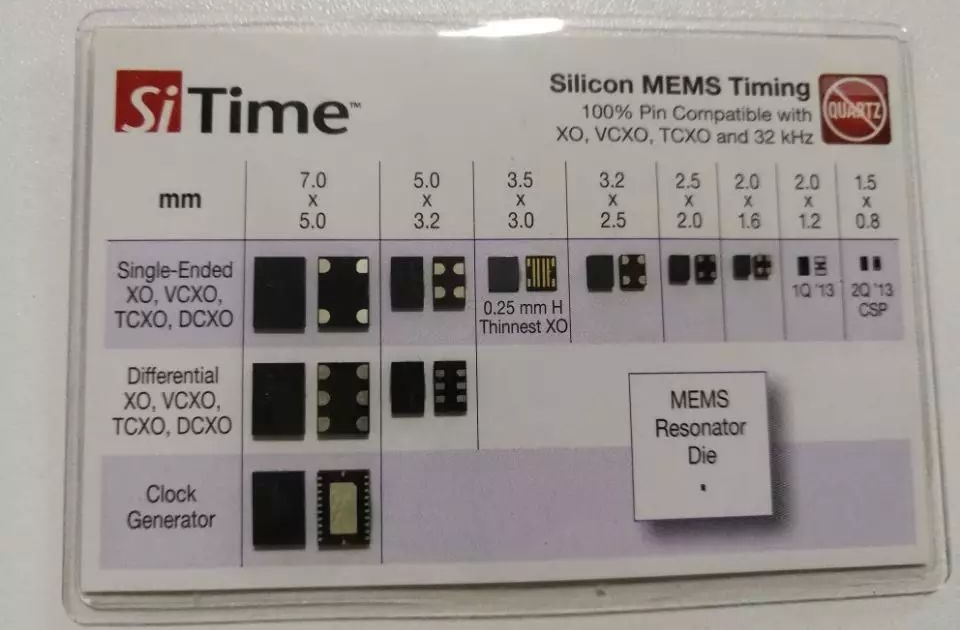

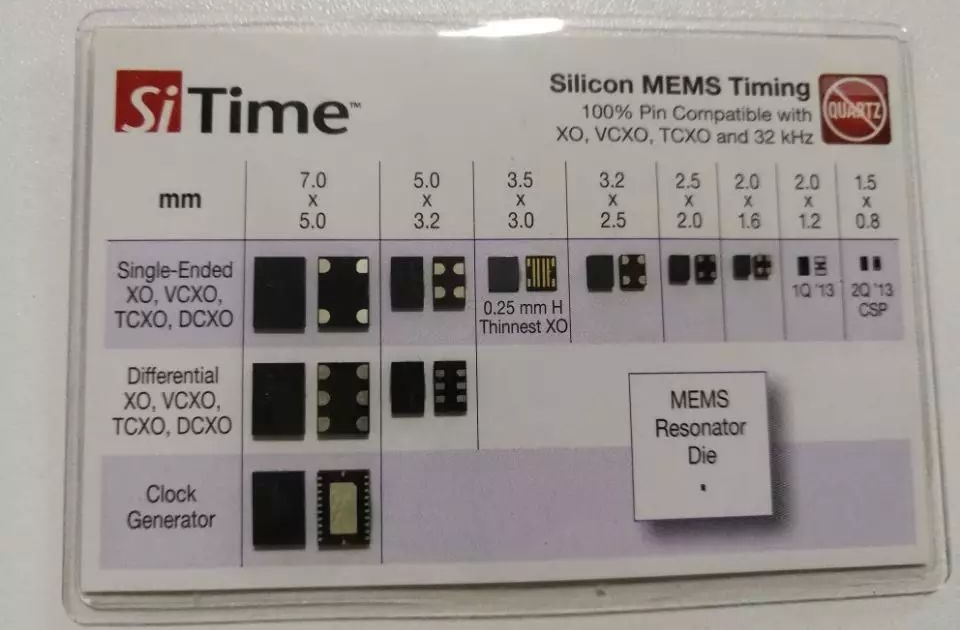

~ 16周。 交貨周期不定:由于生產工序復雜;任何一道工序產生錯誤,該批生產均需從頭來過;造成交期重置。SiTime全硅MEMS振蕩器的制造方式及其優點:1. SITIME的 MEMS振蕩器是由

2011-07-26 14:42:54

:由于生產工序復雜;任何一道工序產生錯誤,該批生產均需從頭來過;造成交期重置。SiTime全硅MEMS振蕩器的制造方式及其優點:1. SITIME的 MEMS振蕩器是由兩顆芯片;一為全硅 MEMS

2011-07-20 09:47:26

`SiTime SiT8008和SiT8008B低功耗可編程振蕩器具有可編程驅動強度功能,以提供簡單,靈活的工具來優化特定應用的時鐘上升/下降時間。可編程的驅動強度通過減慢時鐘的上升/下降時間來改善

2021-01-20 10:02:11

SiTime的產品包括高性能差分振蕩器、擴頻振蕩器、壓控振蕩器和多組輸出式時脈產生器,服務于容錯云端儲存器、企業服務器、10兆以太網交換機等高性能電子系統,及數碼相機、LCD高清晰電視、多功能打印機等大批量消費電子。

2019-10-29 09:01:18

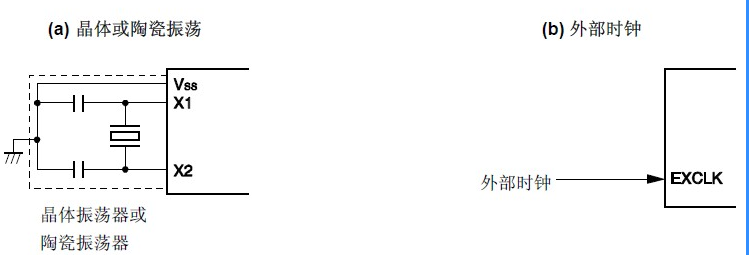

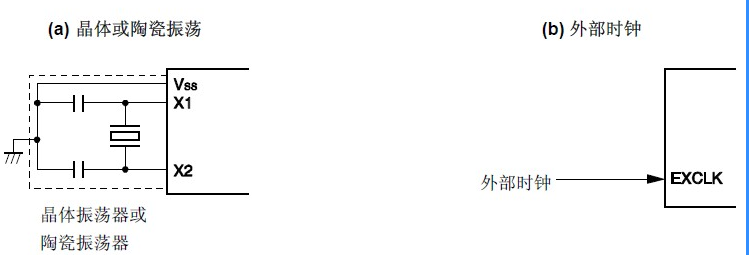

你好我正在設計我的第一個斯巴達6 FPGA板。我對外部振蕩器/時鐘有幾點懷疑。我瀏覽了時鐘資源指南UG382,但它沒有多大幫助,因為它主要描述了FPGA的內部電路,一旦你選擇了振蕩器就會

2019-06-12 14:21:39

的容量,眾多供應商,許多制造設施和兼容的流程 - 目前已經建立了用于生產硅MEMS振蕩器的極其強大的供應鏈。此外,SiTime振蕩器的架構設計為可編程的。生產大量空白MEMS振蕩器,保存在庫存中,并按

2018-10-30 14:30:50

振蕩器頻率和時鐘頻率有什么不同,具體點

2016-06-01 22:02:54

時鐘設備設計使用 I2C 可編程小數鎖相環 (PLL),可滿足高性能時序需求,這樣可以產生零 PPM(百萬分之一)合成誤差的頻率。高性能時鐘 IC 具有多個時鐘輸出,用于驅動打印機、掃描儀和路由器等

2019-08-12 06:50:43

,SiTime資深客戶支持經理。畢業于北京理工大學,獲碩士學位,曾供職于國內研究所,著名通訊設備制造商和半導體公司。 擁有多年的時鐘產品研發,系統方案設計和技術支持相關經驗,多年從事于鎖相環,振蕩器和系統級

2017-09-21 17:03:50

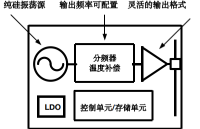

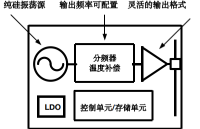

微控制器為高性能時鐘 IC 提供控制邏輯能力,通過減少板載 IC和板上走線使整體設計更加緊湊,并降低最終物料成本。操作理論圖 1 為高性能時鐘設備的基本 PLL 架構。該設計使用比例因子為 PLL 輸出

2018-08-27 09:46:58

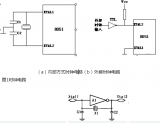

異步SRAM存儲器接口電路設計(Altera FPGA開發板)如圖所示:FLASH存儲器接口電路圖(Altera FPGA開發板)高速SDRAM存儲器接口電路設計(Altera FPGA開發板)如下

2012-08-16 18:49:43

20 MHz),頻率為156.250 MHz。 自1958年以來,CrystekCorporation一直提供頻率產品,包括石英晶體,XO(時鐘振蕩器),TCXO(溫度補償晶體振蕩器),VCO

2019-05-19 11:09:44

的頻率,低相位噪聲,低諧波和出色的線性度。 推動和拉動減少到最低限度。自1958年以來,CrystekCorporation一直提供頻率產品,包括石英晶體,XO(時鐘振蕩器),TCXO(溫度補償

2018-07-13 11:38:15

使用20M-33MHrs后會發生性能穩定性下降的問題,而MEMS振蕩器出現該問題的時間是500MHrs,穩定度提高十倍以上。另外由于采用了SiTime公司擁有專利的穩固封裝,MEMS振蕩器的仿真系數達到-50,000

2016-06-04 10:18:38

N32G430C8L7_STB開發板用于32位MCU N32G430C8L7的開發

2023-03-31 12:05:12

高性能32位N32G4FRM系列芯片的樣片開發,開發板主MCU芯片型號N32G4FRMEL7

2023-03-31 12:05:12

`SM7744HEW時鐘振蕩器產品介紹 SM7744HEW詢價熱線 SM7744HEW現貨 SM7744HEW代理王先生15989509955深圳市首質誠科技有限公司, Pletronics

2019-05-07 18:42:47

TRO系列具有VCO新開發中的最新增強功能。 該系列利用陶瓷諧振器拓撲來提供超低功耗相位噪聲性能,但其緊湊的尺寸使其與其他陶瓷諧振器設計脫穎而出,并樹立了新的標準。 這與其他CRO模型相比,TRO

2021-04-03 16:30:03

精心設計的一款FPGA+USB3.0開發板,主芯片架構為:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2選1)+MT47H64M16HR

2018-10-18 14:46:05

精心設計的一款FPGA+USB3.0開發板,主芯片架構為:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2選1)+MT47H64M16HR

2019-01-08 14:30:50

精心設計的一款FPGA+USB3.0開發板,主芯片架構為:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2選1)+MT47H64M16HR

2018-09-20 15:22:52

的 Artix7FPGA芯片能夠實現更高性能的邏輯,并且能提供更多的容量,更好的性能以及更豐富的資源。 Nexus4DDR開發板集成了USB、以太網和其他端口,能實現從理論型組合電路到強大的嵌入式處理器的多種

2021-07-22 08:34:54

我只做了一塊s3c6410開發板,遇到了一些問題,USB不能正常工作,在板子上測到xu***xti、xu***xto間接到的48M振蕩器只有16M,我是中解決不了,跪求哪位高手幫我解決一下,我的郵箱為N96759@163.COM,在此先謝了{:soso_e179:}

2011-10-09 11:08:20

圖像傳感器寬動態范圍壓縮,以及高精度圖像處理等,這為客戶實現高靈活性、實時的且兼具高性能視頻分析提供了解決方案。而SiTime作為賽靈思方案官方參考設計推薦晶振,和賽靈思FPGA配合無間,相輔相成。具體

2017-09-07 14:44:24

基于Lattice MXO2 LPC的小腳丫FPGA核心板 - Type C接口

開發板的硬件規格如下:

核心器件:Lattice LCMXO2-4000HC-4MG132

132腳BGA封裝

2024-01-31 21:01:32

項目名稱:智能門鎖項目在on Semiconductor BLE5.0開發板的實現試用計劃:已經測試使用了Nordic 52840、Cypress PSoC6項目在智能門鎖的開發。現在希望能展開

2020-06-30 16:22:59

#紫光同創盤古系列FPGA開發板@盤古2K開發板 基于紫光同創Compa系列PGC2KG-LPG100器件,預留豐富的擴展 IO 及數碼管、按鍵、LED 燈,為用戶提供基本的硬件環境 @入門級高性能FPGA開發板#盤古2K開發板。

2023-06-12 17:58:20

的表面貼裝(SMA)連接器、時鐘振蕩器、多電源輸入和各種LED指示器,并配有下載電纜和插墻式電源適配器。此外,像Lattice公司的其它開發板一樣,XP高級評估板也使用ispLEVER和ispVM工具

2012-04-27 14:40:21

。 振蕩器制造商將石英諧振器與振蕩器電路相匹配,從而減輕了電路板設計者的負擔。 由于消除了匹配錯誤,SiTIme 保證了振蕩器的啟動。 簡而言之,振蕩器是一種即插即用的解決方案,可以極大地簡化系統

2021-11-11 08:00:00

不那么敏感。 如下表和圖表所示,SiTIme 振蕩器的靈敏度比晶體諧振器低 11.3 dBm(線性標度為 134 倍)。該測試是根據 IEC 62132-2 標準執行的,該標準將電磁能注入安裝被

2021-11-13 08:00:00

,SiTIme 振蕩器的 DPPM 和 MTBF 比石英好大約 30 倍,提供了一個非常可靠的技術平臺,可以承受惡劣的環境壓力,并為最終用戶提供高質量的產品。3. MEMS 低頻振蕩器占用的電路板空間

2021-11-12 08:00:00

寫在前面:標題“使用內部rc振蕩器做時鐘源”其實不太準確,實際應該是“使用內部rc振蕩器經PLL倍頻后做時鐘源”,為了簡單本文統一用“使用內部rc振蕩器做時鐘源”。在做開發時,一些場合對時鐘要求不是

2021-08-12 08:18:25

我有一位客戶詢問有關在 RT1051 中實現外部 24Mhz 時鐘振蕩器的問題。他們計劃通過將現有的外部 48Mhz 振蕩器分頻為 24Mhz 并使用 RT1051 的外部時鐘振蕩器輸入功能來為

2023-05-18 06:15:20

內部時鐘振蕩器是否穩定?能不能用于產生波特率的時基

2023-11-03 07:31:32

所以我最近購買了ML405開發板,我現在需要找到一個與userclk一起使用的振蕩器。該手冊規定我需要一個“接受3.3V的半插座LVTTL振蕩器”。然而,在我搜索Digikey和Mauser時,我

2019-08-14 07:15:17

有振蕩器,需要使用外部方波驅動,通過編程使方波的工作頻率變化,可以發出不同音調的聲音。下圖是本開發板搭載的無源蜂鳴器,使用FPGA發出方波驅動:對于一段樂譜,具有音調和節拍兩種屬性,音調決定音的高低

2022-08-17 16:14:51

基于FPGA的壓控振蕩器是否能夠實現,相關文獻或論文有沒有,求大神指導

2014-12-02 14:09:21

)的迭代運算,迭代結果輸出的xn和yn就是所需要的三角函數值。數控振蕩器的FPGA實現圖1是數控振蕩器的頂層電路。由圖可見,頻率控制字寄存器將接收到的的頻率控制字送入相位累加器,相位累加器對系統時鐘進行

2021-07-15 08:00:00

通過FPGA來構建一個低成本、高性能、開放架構的數據平面引擎可以為網絡安全設備提供性能提高的動力。隨著互聯網技術的飛速發展,性能成為制約網絡處理的一大瓶頸問題。FPGA作為一種高速可編程器件,為網絡安全流量處理提供了一條低成本、高性能的解決之道。

2019-08-12 08:13:53

時鐘系統存在的意義是什么?常見的振蕩器有哪些?

2022-01-20 06:29:51

,盡管時鐘信號是系統中所有信號賴以存在的“心跳”。為應用選擇正確工作頻率的定時器件可能看起來很簡單,不過仍然有許多影響系統性能的因素需要考慮。那么,最重要的參數和注意事項是什么?下文將對振蕩器的主要參數

2019-05-29 17:39:57

/ GTH收發器。我們的目標數據速率為6.25 Gbps。這是更好的方法嗎?因為大多數設計實例都有專用的板載時鐘振蕩器,用于GPS參考時鐘。請提供建議以獲得更好的性能。

2020-03-18 09:53:15

我正在開發代碼(PIC32 MZ),以便在一系列開發PCB上運行。有些有12MHz的振蕩器和24MHz的振蕩器。有人能建議一種代碼檢測方法嗎?

2019-10-28 13:56:41

怎樣去使用外部時鐘HSE振蕩器呢?STM32F4如何去設置系統容器源為內部HSE呢?

2021-10-19 06:02:07

大家好,我想知道是否可以使用當前為主 MCU (STM32F334) 提供時鐘的單個現有晶體振蕩器為另一個 STM32 MCU (STMF031) 提供時鐘。它真的可以為我節省空間、功耗、成本和電路板上的另一個時鐘源。如果是,如何?

2023-01-12 07:25:54

你好,我現在正在用PIC32MZ1024EFG100處理器為我的新PCB做原理圖。正如我在勘誤表中看到的,晶體振蕩器不能用于次級振蕩器。相反,我必須使用外部時鐘源。勘誤表(#4)指定時鐘源必須提供

2020-03-23 09:33:28

用玻璃殼、陶瓷或塑料封裝的。石英晶體振蕩器是高精度和高穩定度的振蕩器,被廣泛應用于彩電、計算機、遙控器等各類振蕩電路中,以及通信系統中用于頻率發生器、為數據處理設備產生時鐘信號和為特定系統提供基準信號。...

2021-08-09 06:46:27

晶體振蕩器也分為無源晶振和有源晶振兩種類型。無源晶振與有源晶振(諧振)的英文名稱不同,無源晶振為crystal(晶體),而有源晶振則叫做oscillator(振蕩器)。無源晶振需要借助于時鐘電路才能

2013-06-09 11:52:27

設計時鐘振蕩器,給我講講時鐘產生電路、偏置電流產生電路和基準電路的原理,+qq1962548157?

2023-03-19 19:56:12

請問振蕩器如何生成精確時鐘源?振蕩的基本原理以及如何在晶體振蕩器中進行實現

2021-04-09 06:25:01

請問ADS1274的時鐘可以使用外部振蕩器提供嗎,因為看到數據手冊上使用DSP的CLKOUT所以不太確定,感覺應該可以的是嗎?

2019-05-14 12:38:34

如題,內部時鐘振蕩器是否穩定?是否可以用于產生波特率的時基?

2019-09-17 05:55:01

嗨,我有一個關于為Spartan 6 FPGA選擇振蕩器的問題。我已經閱讀了這個主題:http://forums.xilinx.com/t5/Spartan-Family-FPGA

2019-07-10 09:42:08

。 EVAL-AD9832SDZ板與EVAL-SDP-CB1Z板配合使用。使用這款基于Blackfin的開發板完成與AD9832的USB到SPI通信。高性能,板載25 MHz微調通用振蕩器可用作AD9832系統的主時鐘

2019-03-01 10:12:41

億海微6系 EQ6HL45型可編程邏輯芯片開發平臺采用核心板加擴展板的模式,方便用戶對核心板的二次開發利用,為前期驗證和后期應用提供了可能。相信這樣的一款產品非常適合從事FPGA開發的工程師、科研人員等群體。

2022-02-16 17:06:51

-- 今天無數電子線路和應用需要精確定時或時鐘基準信號。晶體時鐘振蕩器極為適 合這方面的許多應用。時鐘振蕩器有多種封裝,它的特點是電氣性能規范多種多樣。它有好幾

2009-12-02 15:35:46 0

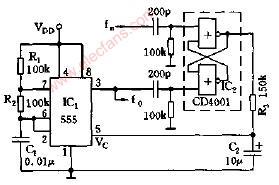

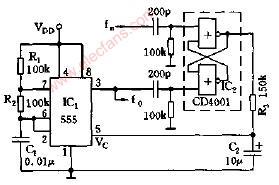

0 摘要:介紹了時鐘振蕩器的結構、特點、原理及應用,給出了實際電路圖,并說明了電路元件參數的選擇.關鍵詞:RC時鐘振蕩器;555時鐘振蕩器;晶體時鐘振蕩器

2010-05-24 09:25:27 36

36 AD841SE/883B: 品質,高性能振蕩器的卓越之選在追求高性能振蕩的領域,一款穩定、可靠的芯片是至關重要的。深圳市華灃恒霖電子科技有限公司為您推薦一款 品質的高性能振蕩芯片——AD841SE

2024-01-19 18:51:03

時鐘振蕩器(PROM) 通過掩膜選項,可以選擇石英晶體振蕩器或RC振蕩器,兩者都可作為系統時鐘。不管用哪種振蕩器,其信號都支持系

2006-04-03 23:13:22 1492

1492

與時鐘同步的振蕩器電路圖

2009-05-16 16:59:03 726

726

SiTime硅振蕩器概況 MEMS(Micro Electromechanical System,即微電子機械系統)是指集微型傳感器、執行器以及信號處理和控制電路、接口電路、通

2009-11-14 15:59:57 1300

1300 以微機電系統(MEMS)技術開發硅振蕩器產品的SiTime公司,自去年推出第一代產品后,已于日前達到每周出貨10萬顆的

2011-01-01 15:09:51 713

713 SiTime Corporation日前推出的SiT8004,是業內功耗最低的高頻振蕩器。SiT8004把振蕩器的功耗降低了66%,最適合高性能網絡、視頻、計算與存儲應用。

2011-03-23 09:26:32 1745

1745 SiTime公司日前宣布針對平板電腦以及電子書產品設計所需的所有時鐘振蕩器,推出完整的解決方案。基于SiTime公司低功耗全硅MEMS振蕩器平臺,

2011-04-12 10:55:50 1049

1049 模擬半導體公司SiTime Corporation今天推出業界性能最強的差分振蕩器,其頻率穩定度達10PPM、相位抖動僅500飛秒(femtosecond),市面上目前僅SiTime實現了這兩項的完美結合。SiT9121和SiT9122系

2011-10-25 09:13:05 1315

1315 電子發燒友網站提供《Lattice_MachXO系列FPGA開發板電路原理圖.zip》資料免費下載

2017-09-15 16:04:00 0

0 ?(溫度補償型振蕩器)和多款振蕩器。這些高精度器件可以用來解決電信與網絡設備存在已久的時鐘問題。即使在有環境壓力的情況下,Elite Platform仍有助于通信設備達到最優異的性能、可靠性及服務質量。

2016-09-26 10:07:49 728

728 據麥姆斯咨詢報道,SiTime公司的高精度振蕩器基于Elite Platform,為小型基站、同步以太網與時鐘同步的動態性能、抗環境壓力和可靠性等方面制定了新標準。

2018-06-20 16:09:21 4971

4971 于是就有了時鐘振蕩器,將外部時鐘電路跟晶振放在同一個封裝里面,一般都有4個引腳了,兩條電源線為里面的時鐘電路提供電源,又叫做有源晶振,時鐘振蕩器,或簡稱鐘振。好多鐘振一般還要做一些溫度補償電路在里面,讓振蕩頻率能更加準確。

2018-08-07 11:51:32 15291

15291

低功耗FPGA大廠萊迪思半導體(Lattice Semiconductor)近日推出全新FPGA軟件解決方案Lattice Propel,提供擴充RISC-V IP及更多類型周邊組件的IP

2020-07-14 16:36:17 1156

1156 220MHz高性能差分振蕩器SiT9121

2021-09-10 16:19:49 4

4 市場的95%以上份額。目前我們的MEMS諧振子技術已經是第三代了,廣泛的應用于消費、汽車、網通、安防、工控、5G通信等多種場合。 ? ? ? ?SiTime的時鐘產品包括32.768KHZ振蕩器

2021-09-16 10:59:15 911

911

1 簡介 半導體組件有望在產品的整個生命周期內可靠地運行。 選擇具有最高可靠性等級的設備可以限制故障組件導致現場產品出現故障的可能性。 SiTime 提供滿足這一目標的振蕩器,超過 2.5

2021-10-27 16:33:42 459

459 為基礎的SiTime硅晶振,在系統運行的關鍵領域提供更高的性能.良好的頻率溫度穩定性SiTime提供0.1至5 ppm的頻率穩定度的TCXO(溫度補償振蕩器)和XO(單端振蕩器)。典型的石英振蕩器

2021-11-17 16:46:15 2531

2531

還有足夠的余量,能夠滿足高性能領域的應用。如下圖所示,SiTime提供的XO振蕩器頻率穩定度達10PPM,這是石英晶振永遠無法企及的精度。事實上,在頻率大于70MHz的MHz振蕩器中,采用SiTime

2021-12-06 17:00:25 1727

1727

極低噪聲和低抖動的時鐘器件,以支持400G 光模塊和Massive MIMO設備。四、“Cascade”系列產品的優勢SiTime可提供完整的MEMS時鐘解決方案,包括低抖動單端及差分振蕩器、高精度

2022-03-11 17:34:50 2102

2102 產品設計中。但如此多的不同的功能模塊,經常使用多個時鐘來驅動。研發人員必須決定如何結合外部振蕩器和內部PLL資源以實現最佳的時鐘樹設計。FPGA具有靈活性高、可配置性強等優點, 可加速產品的設計周期

2022-03-23 15:35:32 1723

1723 www.sitimechina.com,客戶服務熱線400-888-2483。差分振蕩器通常與FPGA搭配,用于高性能系統如 10G/40G/100G 的以太網中來提供高頻信號(100 MHz 或以上)。相對于單端振蕩器,差分振蕩器利用

2022-04-26 13:56:52 3946

3946

32KHz--725MHz任一頻率樣品供應,實現更高性能時鐘樣品的快速交付。SiTime硅晶振以穩定的性能和超高的性價比成為了大多數高性能主控芯片的理想時鐘選擇和強健的心臟。不僅可以縮短研發周期,節約開發調試

2022-06-13 16:29:34 2950

2950 SiTime 為 MEMS 振蕩器與基于石英晶體的時鐘源提供了一個案例。

2022-08-16 11:19:24 1462

1462

比基本器件頻率慢 2052 倍。經濟振蕩器可用于任何類型的時鐘邏輯,包括微處理器、FPGA 和 CPLD 電路,具體取決于系統要求。

2023-03-03 14:29:48 588

588

和設計體驗。萊迪思半導體官方培訓平臺Lattice Insights旨在實現這種體驗,幫助FPGA開發人員充分利用萊迪思FPGA開發他們的解決方案。

2023-06-01 10:08:26 592

592 第12章時鐘振蕩器

2022-12-30 09:21:58 2

2 電子發燒友網站提供《基于FPGA的神經振蕩器設計及優化.pdf》資料免費下載

2023-11-10 09:39:29 0

0 FPGA開發板是一種基于FPGA(現場可編程門陣列)技術的開發平臺,它允許工程師通過編程來定義和配置FPGA芯片上的邏輯電路,以實現各種數字電路和邏輯功能。FPGA開發板通常包括FPGA芯片、時鐘模塊、電源模塊、輸入輸出接口等組件,并提供相應的編程軟件和開發工具,方便工程師進行電路設計和調試。

2024-03-14 18:20:29 553

553 可編程振蕩器助力醫療成像提供準確時序,兼容SiTime

2024-03-18 10:13:26 40

40

替代SiTime,國產可編程MEMS振蕩器可用于POS機

2024-03-21 10:19:23 41

41

電子發燒友App

電子發燒友App

評論