基于DSP與FPGA的光柵地震檢波器的信號處理

0 引 言

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地震波而設計的一種精密的機械、電子組合裝置,是地震勘探數據采集中的重要環節,其性能好壞直接影響地震記錄質量和地震資料的解釋工作。光柵傳感技術的發展為檢波器的設計提供了有力的手段。其光柵信號處理技術仍局限于低速度的信號處理,雖然測量精度較高,但其動態特性難以滿足振動信號檢測等高速變化信號的處理要求,本文設計了一種利用DSP與FPGA結合的光柵振動信號處理系統,它主要完成對光柵震動傳感器輸出的兩路正交的正弦波信號的采集、計數、高倍細分等,從而實現了對快速的振動信號的復現。

1 光柵地震檢波器的工作原理

光柵地震檢波器主要由光源(白光或單色光)、準直鏡、光電池、指示光柵(副光柵)、光柵諧振子(主光柵)組成。光柵諧振子(主光柵)為檢波器的可動部分,由上彈簧片和下彈簧片支撐。工作時,檢波器外殼通過檢波器尾釘與大地連接并固定,當大地受到震源激發后,地震波傳至地面引起地面震動,檢波器外殼也隨之震動。而光柵振子由于彈簧片的彈性和本身的慣性,有保持絕對不動的趨勢,從而產生了光柵振子與外殼的相對運動,也就是說光柵副中的主光柵與裂向式指示光柵之間產生了相對運動。兩塊疊放在一起的光柵具有了相對運動也就會產生與之相對應的莫爾條紋,從而在相位差為90°的四個光電池上產生莫爾條紋的變化,于是光信號被轉化為電信號,再經差分放大后形成兩路相位相差90°的正弦或余弦波信號。

2 光柵震動信號的同步采集

要保證整個系統對振動信號的實時復現,關鍵是要保證對兩路模擬正弦波的同步采集。若使用DSP直接控制多通道的模數轉換器,由于編程語言的順序結構和單個模數轉換器不能同時采樣保持的限制,對于多路信號的采集只能分時多通道順序采集,這樣對同一點的兩路模擬波的采集肯定會產生相位差,這樣對復現出來的原振動信號會造成相當大的失真。但是由于FPGA的編程語言VHDL執行時是并發執行的,并不受到它們在主結構中的編寫順序的影響。根據上述特點,對于本系統的設計可以分成三個并行進程,分別是2個光柵信號采集的進程和一個加減計數器的進程。

AD轉換器選用的是LINEAR公司生產的LTC1606,該器件是具有采樣保持功能的16位250kHzADC。該ADC分辨率高,采樣速率高、功耗小,可在高精度的數據采集系統中廣泛應用。

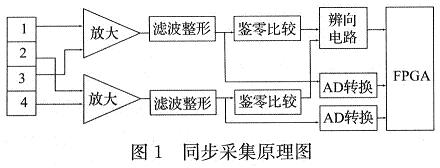

光柵振動莫爾條紋的信號采集采用成直線排列的相位差為90°的四個光電池,分別記為1、2、3和4,如圖1所示。它們接收由被測振動信號調制的莫爾條紋,并通過差動放大器、整形濾波器輸出兩路正交的正弦信號。這兩路信號分成兩組,其中一組經過鑒零比較電路轉換成方波送入辨向電路為FPGA中加減計數器提供計數累加值和辨向信號。另一組則直接將放大的模擬電壓信號送入兩路AD轉換器轉換成數字量并存入FPGA。在FPGA中開辟3個雙口RAM存儲器用來順序存放每一點的整周期計數值和兩路波形的數字量,為DSP進行高倍細分提供基礎數據。

2.1 雙口RAM的設計

雙口RAM是常見的共享式多端口存儲器,雙口RAM最大的特點是存儲數據共享。一個存儲器配備兩套獨立的地址、數據和控制線,允許兩個獨立的CPU或控制器同時異步地訪問存儲單元。由于硬件雙口RAM接口時序復雜,成本高也會給系統帶來不穩定性,因此本文在FPGA中設計了一軟RAM,用來緩沖數據采集與處理之間產生的異步時差。

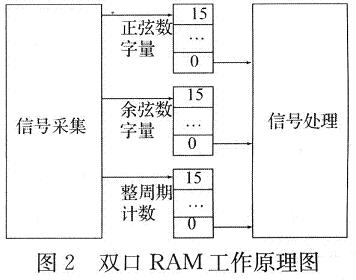

其工作原理如圖2所示,所設計的存儲空間為3個16字容量的雙口RAM,當信號采集部分向新地址寫入每一個振動點的三個信息量時(圖中所示地址為15),信號處理部分則讀取先前振動點的三個信息量進行細分等處理(圖中所示地址為0),當雙口RAM寫滿數據后,寫地址指針又會重新定位到首地址寫入新的數據,這種緩存結構的設立不會丟失信息點,保證了還原信號的連續性和可靠性,雖然還原信號滯后源信號3到4個字的時間,但保證了每一個點三個信息量的同步性,這是C語言等順序結構語言所無法達到的。

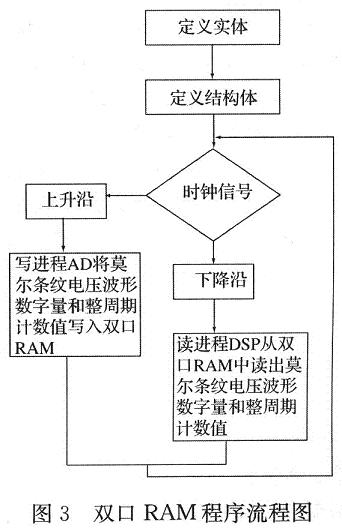

2.2 雙口RAM的流程圖設計

首先是定義實體與外部端口,包括時鐘、輸入輸出、讀寫地址端口。它們的作用分別是:

1)時鐘端口:利用時鐘的脈沖邊沿來觸發讀寫進程,使得新舊數據在雙口RAM中交替進出。

2)輸入輸出端口:分別為16位的位矢量類型,用來保證與16位AD和DSP的數據格式匹配。

3)讀寫地址端口:2位的位矢量類型,用來設置16位字的存儲器容量,并在讀寫RAM操作時提供地址選址信號。

其次是定義結構體,包括定義內部緩沖地址信號,并定義了一個容量為16字的Mem(存儲器類型)型變量。

最后是并發進程的定義,包括寫進程和讀進程的定義,以時鐘的脈沖信號作為敏感信號來觸發進程的啟動,每一個時鐘周期完成一次對RAM的讀寫,其中時鐘頻率由FPGA根據AD的采樣速度和DSP的處理速度來設定,要保證當采集信號寫入尾地址的時刻,至少要保證首地址已經被DSP所讀取。圖3為雙口RAM程序流程圖。

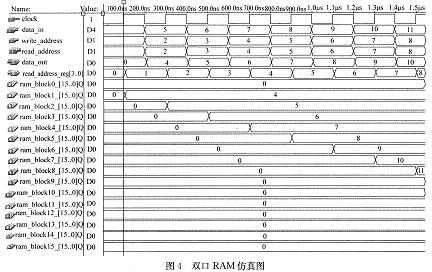

2.3 雙口RAM的仿真結果

圖4為該進程的仿真時序圖,由圖可見第一個時鐘的上升沿數據輸入端口data_in的值為4,這時寫選通端口write_address選通地址1,然后對應著地址1的存儲器模塊ram_block1的內的值在此刻刷新為4,這說明寫進程正確。同時應注意到讀地址選通信號read_address的值被傳遞到讀地址寄存器read_address_reg中,read_address_reg中的值被刷新為1。當第一個時鐘的下降沿到來時,信號輸出端口data_out根據讀地址寄存器read_address_reg中的地址值1選通ram_block1,此時data_out的值刷新為4,這說明讀進程也正確。

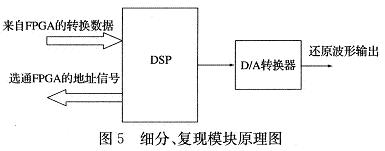

3 DSP的軟件細分

采用大數可逆計數與小數細分計數的軟件細分技術。其中大數計數是對莫爾條紋整周期數進行可逆的加減計數,這部分功能有采集模塊中的FPGA來完成,小數計數是對莫爾條紋不到一個周期信號細分結果進行計數,其功能由DSP來完成。運算的結果為大數計數結果乘以光柵柵距與小數計數結果乘以細分當量之和,其中細分當量為光柵柵距除以細分倍數。該模塊的硬件原理圖如圖5所示。

通過DSP的地址選通線依次選通讀取FPGA中三個數據緩存區中的數據,緩存區分別存放兩路模擬信號的數字量與加減計數器的累加計數值,然后利用公式R=N*w+K*L求出任意一點諧振子的幅值并輸出。式中N為整周期的累加計數值,W為光柵柵距,K為細分計數,L=W/M,M為細分倍數。該細分模塊主要是完成對細分計數K值、和幅值R值的求取,并完成對幅值的數字量轉換并輸出。

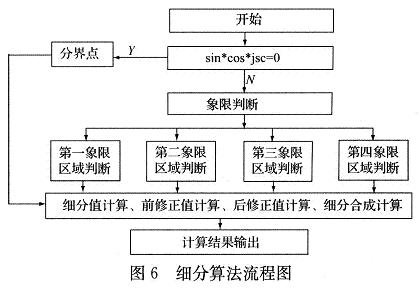

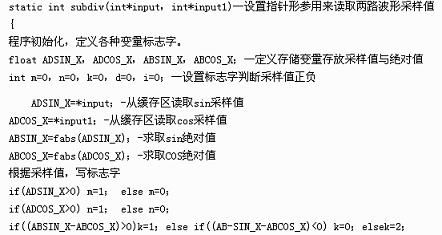

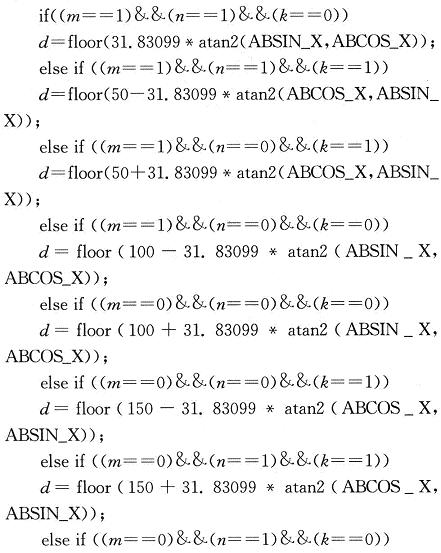

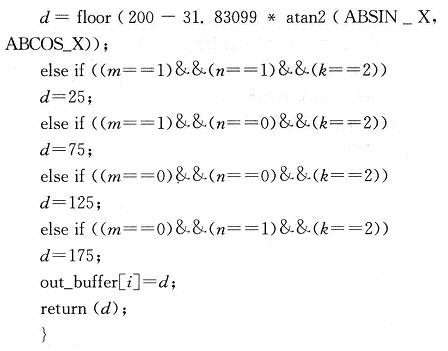

其中細分方法也就是對K值的求取采用了八卦限幅值分割法,根據上述方法設計了細分倍數可變的細分算法,利用DSP C語言的專用庫函數實現了純計算的算法。細分算法流程如圖6所示。

由幅值細分法可知,軟件細分算法設計的關鍵問題是根據兩路信號的比值對該點的相位角的正確定位。該點的位置有兩種情況,一種是落在各象限的邊界上,另一種是落在各象限之中。根據細分邊界條件判斷該點的采樣數據是否發生在四個象限的分界線上,如果判斷此次換向發生在象限的分界線上,則細分數為固定值,并且通過象限的正負關系就可以確定具體細分數值,不需要進行復雜的計算。如果該點不是發生在象限分界線上,則需根據象限正負關系判斷換向發生的具體象限,不同象限對應不同計算公式。細分算法程序如下:

根據標志字判斷相位點的位置,根據相應位置不同公式求取細分值

然后利用公式R=N×ω+d×L求出任意一點諧振子的幅值并輸出。式中N為整周期的累加計數值,W為光柵柵距,d為細分計數,L=ω/m,m為細分倍數。

4 結束語

設計的光柵地震檢波器充分結合了FPGA的強大控制功能和DSP高速運算處理功能,實現了信號的同步采集、高倍細分和實時復現。減少了單一處理器的負荷,提高了系統的速度和穩定性,為光柵震動信號處理提出了一個新思路。由于硬件雙口RAM接口時序復雜,成本高也會給系統帶來不穩定性,因此本文在FPGA中設計了一軟RAM。對于振動信號幅值的計算則是在對整周期的莫爾條紋進行計數的同時,利用軟件細分法實時地計算出非整周期的莫爾條紋信號所代表的小數值,并實時將二者相加后乘以莫爾條紋當量(每個莫爾條紋所代表的位移量),即可得到信號的實時振動幅值。